Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22-e-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                    | Pin Number      | Pin                      | Buffer                              |                                                                                                                              |

|------------------------------------------------------------------------------------|-----------------|--------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                           | QFN/TQFP        | Туре                     | Туре                                | Description                                                                                                                  |

|                                                                                    |                 |                          |                                     | PORTD is a bidirectional I/O port.                                                                                           |

| RD0/PSP0/CTPLS<br>RD0<br>PSP0<br>CTPLS                                             | 58              | I/O<br>I/O<br>O          | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port data.<br>CTMU pulse generator output.                                                    |

| RD1/PSP1/T5CKI/T7G<br>RD1<br>PSP1<br>T5CKI<br>T7G                                  | 55              | I/O<br>I/O<br>I          | ST<br>TTL<br>ST<br>ST               | Digital I/O.<br>Parallel Slave Port.<br>Timer5 clock input.<br>Timer7 external clock gate input.                             |

| RD2/PSP2<br>RD2<br>PSP2                                                            | 54              | I/O<br>O                 | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.                                                                                         |

| RD3/PSP3<br>RD3<br>PSP3                                                            | 53              | I/O<br>I/O               | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.                                                                                         |

| RD4/PSP4/SDO2<br>RD4<br>PSP4<br>SDO2                                               | 52              | I/O<br>I/O<br>O          | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.<br>SPI data out.                                                                        |

| RD5/PSP5/SDI2/SDA2<br>RD5<br>PSP5<br>SDI2<br>SDA2                                  | 51              | I/O<br>I/O<br>I<br>I/O   | ST<br>TTL<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Parallel Slave Port.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                          |

| RD6/PSP6/SCK2/SCL2<br>RD6<br>PSP6<br>SCK2<br>SCL2 <sup>(4)</sup>                   | 50              | I/O<br>I/O<br>I/O<br>I/O | ST<br>TTL<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Parallel Slave Port.<br>Synchronous serial clock.<br>Synchronous serial clock I/O for I <sup>2</sup> C mode. |

| RD7/PSP7/ <mark>SS2</mark><br>RD7<br><u>PSP</u> 7<br>SS2                           | 49              | I/O<br>I/O<br>I          | ST<br>TTL<br>TTL                    | Digital I/O.<br>Parallel Slave Port.<br>SPI slave select input.                                                              |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input<br>P = Power<br>$1^{2}$ CTM (SI | Trigger input w | vith CN                  | IOS levels                          | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)         |

l<sup>2</sup>C = l<sup>2</sup>C™/SMBus

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

### 4.0 POWER-MANAGED MODES

The PIC18F87K22 family of devices offers a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (such as battery-powered devices).

There are three categories of power-managed mode:

- Run modes

- Idle modes

- · Sleep mode

There is an Ultra Low-Power Wake-up (ULPWU) for waking from the Sleep mode.

These categories define which portions of the device are clocked, and sometimes, at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block). The Sleep mode does not use a clock source.

The ULPWU mode, on the RA0 pin, enables a slow falling voltage to generate a wake-up, even from Sleep, without excess current consumption. (See **Section 4.7 "Ultra Low-Power Wake-up"**.)

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices. This feature allows the controller to use the SOSC oscillator instead of the primary one. Another power-saving feature is Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions:

- · Will the CPU be clocked or not

- · What will be the clock source

The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits select one of three clock sources for power-managed modes. Those sources are:

- The primary clock as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the SOSC oscillator)

- The internal oscillator block (for LF-INTOSC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These considerations are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entering the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current and impending mode, a change to a power-managed mode does not always require setting all of the previously discussed bits. Many transitions can be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured as desired, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mada     | Mode OSCCON Bits        |          | Module          | Clocking    | Available Clock and Oscillator Source                                                         |

|----------|-------------------------|----------|-----------------|-------------|-----------------------------------------------------------------------------------------------|

| Mode     | IDLEN<7> <sup>(1)</sup> | SCS<1:0> | CPU             | Peripherals | Available Clock and Oscillator Source                                                         |

| Sleep    | 0                       | N/A      | Off             | Off         | None – All clocks are disabled                                                                |

| PRI_RUN  | N/A                     | 00       |                 |             | Primary – XT, LP, HS, EC, RC and PLL modes.<br>This is the normal, Full-Power Execution mode. |

| SEC_RUN  | N/A                     | 01       | Clocked Clocked |             | Secondary – SOSC Oscillator                                                                   |

| RC_RUN   | N/A                     | 1x       | Clocked Clocked |             | Internal oscillator block <sup>(2)</sup>                                                      |

| PRI_IDLE | 1                       | 00       | Off             | Clocked     | Primary – LP, XT, HS, RC, EC                                                                  |

| SEC_IDLE | 1                       | 01       | Off Clocked     |             | Secondary – SOSC oscillator                                                                   |

| RC_IDLE  | 1                       | lx       | Off             | Clocked     | Internal oscillator block <sup>(2)</sup>                                                      |

TABLE 4-1:POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

<sup>2:</sup> Includes INTOSC (HF-INTOSC and MG-INTOSC) and INTOSC postscaler, as well as the LF-INTOSC source.

### 5.0 RESET

The PIC18F87K22 family of devices differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Configuration Mismatch (CM) Reset

- f) Brown-out Reset (BOR)

- g) RESET Instruction

- h) Stack Full Reset

- i) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR, and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.3.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 28.2 "Watchdog Timer (WDT)".

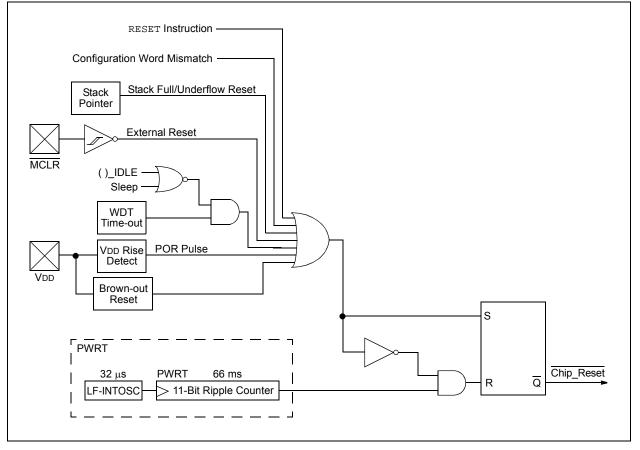

A simplified block diagram of the on-chip Reset circuit is shown in Figure 5-1.

### 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event.

The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.7** "**Reset State of Registers**".

The RCON register also has a control bit for setting interrupt priority (IPEN). Interrupt priority is discussed in **Section 11.0 "Interrupts"**.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 5.7 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register ( $\overline{CM}$ ,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ ) are set or cleared differently in

different Reset situations, as indicated in Table 5-1. These bits are used in software to determine the nature of the Reset.

Table 5-2 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets, and WDT wake-ups.

### TABLE 5-1:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                                        | Program                |    |    | RCON | Register |     |     | STKPTR | Register |

|------------------------------------------------------------------|------------------------|----|----|------|----------|-----|-----|--------|----------|

| Condition                                                        | Counter <sup>(1)</sup> | CM | RI | то   | PD       | POR | BOR | STKFUL | STKUNF   |

| Power-on Reset                                                   | 0000h                  | 1  | 1  | 1    | 1        | 0   | 0   | 0      | 0        |

| RESET instruction                                                | 0000h                  | u  | 0  | u    | u        | u   | u   | u      | u        |

| Brown-out Reset                                                  | 0000h                  | 1  | 1  | 1    | 1        | u   | 0   | u      | u        |

| Configuration Mismatch Reset                                     | 0000h                  | 0  | u  | u    | u        | u   | u   | u      | u        |

| MCLR Reset during power-managed Run modes                        | 0000h                  | u  | u  | 1    | u        | u   | u   | u      | u        |

| MCLR Reset during power-<br>managed Idle modes and<br>Sleep mode | 0000h                  | u  | u  | 1    | 0        | u   | u   | u      | u        |

| MCLR Reset during full-power execution                           | 0000h                  | u  | u  | u    | u        | u   | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                                    | 0000h                  | u  | u  | u    | u        | u   | u   | 1      | u        |

| Stack Underflow Reset<br>(STVREN = 1)                            | 0000h                  | u  | u  | u    | u        | u   | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset, STVREN = 0)          | 0000h                  | u  | u  | u    | u        | u   | u   | u      | 1        |

| WDT time-out during full-power or power-managed Run modes        | 0000h                  | u  | u  | 0    | u        | u   | u   | u      | u        |

| WDT time-out during<br>power-managed Idle or Sleep<br>modes      | PC + 2                 | u  | u  | 0    | 0        | u   | u   | u      | u        |

| Interrupt exit from<br>power-managed modes                       | PC + 2                 | u  | u  | u    | 0        | u   | u   | u      | u        |

Legend: u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

### 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit Program Counter that is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The entire PIC18F87K22 family offers a range of on-chip Flash program memory sizes, from 32 Kbytes (up to 16,384 single-word instructions) to 128 Kbytes (65,536 single-word instructions).

- PIC18F65K22 and PIC18F85K22 32 Kbytes of Flash memory, storing up to 16,384 single-word instructions

- PIC18F66K22 and PIC18F86K22 64 Kbytes of Flash memory, storing up to 32,768 single-word instructions

- PIC18F67K22 and PIC18F87K22 128 Kbytes of Flash memory, storing up to 65,536 single-word instructions

The program memory maps for individual family members are shown in Figure 6-1.

### 6.1.1 HARD MEMORY VECTORS

All PIC18 devices have a total of three hard-coded return vectors in their program memory space. The Reset vector address is the default value to which the Program Counter returns on all device Resets; it is located at 0000h.

PIC18 devices also have two interrupt vector addresses for handling high-priority and low-priority interrupts. The high-priority interrupt vector is located at 0008h and the low-priority interrupt vector is at 0018h. The locations of these vectors are shown, in relation to the program memory map, in Figure 6-2.

### FIGURE 6-2: HARD VECTOR FOR PIC18F87K22 FAMILY DEVICES

|    | Reset Vector                                                                                                              | 0000h                                    |

|----|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|    | High-Priority Interrupt Vector                                                                                            | 0008h                                    |

|    | Low-Priority Interrupt Vector                                                                                             | 0018h                                    |

|    | On-Chip<br>Program Memory                                                                                                 |                                          |

|    | Read '0'                                                                                                                  |                                          |

| Le | gend: (Top of Memory) repr<br>of on-chip program n<br>Figure 6-1 for device<br>Shaded area represe<br>memory. Areas are n | -specific values).<br>ents unimplemented |

|    |                                                                                                                           |                                          |

### 6.3.5 STATUS REGISTER

The STATUS register, shown in Register 6-2, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the write to these five bits is disabled.

These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will set the Z bit but leave the other bits unchanged. The STATUS register then reads back as '000u uluu'.

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions not affecting any Status bits, see the instruction set summaries in Table 29-2 and Table 29-3.

Note: The C and DC bits operate, in subtraction, as borrow and digit borrow bits, respectively.

### REGISTER 6-2: STATUS REGISTER

| U-0                                                                     | U-0                                      | U-0                                                                                                                                                      | R/W-x            | R/W-x             | R/W-x          | R/W-x             | R/W-x            |  |  |  |

|-------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|----------------|-------------------|------------------|--|--|--|

|                                                                         | —                                        | —                                                                                                                                                        | N                | OV                | Z              | DC <sup>(1)</sup> | C <sup>(2)</sup> |  |  |  |

| bit 7                                                                   |                                          |                                                                                                                                                          |                  |                   |                |                   | bit 0            |  |  |  |

| l egend:                                                                |                                          |                                                                                                                                                          |                  |                   |                |                   |                  |  |  |  |

| Legend:       W = Writable bit       U = Unimplemented bit, read as '0' |                                          |                                                                                                                                                          |                  |                   |                |                   |                  |  |  |  |

| -n = Valu                                                               | e at POR                                 | '1' = Bit is set                                                                                                                                         | t                | '0' = Bit is cle  |                | x = Bit is unkr   | nown             |  |  |  |

| bit 7-5                                                                 | Unimplom                                 | ented: Read as '                                                                                                                                         | 0'               |                   |                |                   |                  |  |  |  |

| bit 4                                                                   | -                                        |                                                                                                                                                          | 0                |                   |                |                   |                  |  |  |  |

| DIL 4                                                                   | N: Negative<br>This bit is u<br>(ALU MSB | sed for signed a                                                                                                                                         | rithmetic (2's c | omplement). It    | indicates whet | her the result wa | as negative      |  |  |  |

|                                                                         | 1 = Result v                             | was negative<br>was positive                                                                                                                             |                  |                   |                |                   |                  |  |  |  |

| bit 3                                                                   | OV: Overflo                              | ow bit                                                                                                                                                   |                  |                   |                |                   |                  |  |  |  |

|                                                                         |                                          | sed for signed an<br>which causes the                                                                                                                    |                  |                   |                | verflow of the se | even-bit         |  |  |  |

|                                                                         |                                          | w occurred for si<br>flow occurred                                                                                                                       | gned arithmeti   | c (in this arithm | etic operation | )                 |                  |  |  |  |

| bit 2                                                                   | Z: Zero bit                              |                                                                                                                                                          |                  |                   |                |                   |                  |  |  |  |

|                                                                         |                                          | ult of an arithme<br>ult of an arithme                                                                                                                   | • •              |                   | ro             |                   |                  |  |  |  |

| bit 1                                                                   |                                          | arry/Borrow bit <sup>(1</sup>                                                                                                                            |                  |                   |                |                   |                  |  |  |  |

|                                                                         |                                          | , ADDLW, SUBI                                                                                                                                            |                  |                   |                |                   |                  |  |  |  |

|                                                                         |                                          | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul> |                  |                   |                |                   |                  |  |  |  |

| bit 0                                                                   | C: Carry/Bo                              | C: Carry/Borrow bit <sup>(2)</sup>                                                                                                                       |                  |                   |                |                   |                  |  |  |  |

|                                                                         | For ADDWF                                | For ADDWF, ADDLW, SUBLW and SUBWF instructions:                                                                                                          |                  |                   |                |                   |                  |  |  |  |

|                                                                         |                                          | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                     |                  |                   |                |                   |                  |  |  |  |

|                                                                         | 0 = No carr                              | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                    |                  |                   |                |                   |                  |  |  |  |

| Note 1:                                                                 | For borrow, the operand.                 | For borrow, the polarity is reversed. A subtraction is executed by adding the 2's complement of the second                                               |                  |                   |                |                   |                  |  |  |  |

| 2:                                                                      | ·                                        | For borrow, the polarity is reversed. A subtraction is executed by adding the 2's complement of the second                                               |                  |                   |                |                   |                  |  |  |  |

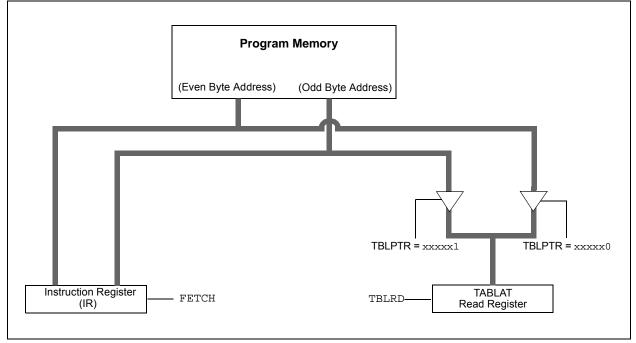

### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed, one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, the TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | BCF     | EECON1, CFGS    | ; point to Flash program memory  |

|-----------|---------|-----------------|----------------------------------|

|           | BSF     | EECON1, EEPGD   | ; access Flash program memory    |

|           | MOVLW   | CODE_ADDR_UPPER | ; Load TBLPTR with the base      |

|           | MOVWF   | TBLPTRU         | ; address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |                                  |

|           | MOVWF   | TBLPTRH         |                                  |

|           | MOVLW   | CODE_ADDR_LOW   |                                  |

|           | MOVWF   | TBLPTRL         |                                  |

| READ_WORD |         |                 |                                  |

|           | TBLRD*- | ÷               | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVWF   | WORD_EVEN       |                                  |

|           | TBLRD*- | ÷               | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVF    | WORD_ODD        |                                  |

|           |         |                 |                                  |

### EXAMPLE 9-1: DATA EEPROM READ

| MOVLW | DATA_EE_ADDRH | ;                                           |

|-------|---------------|---------------------------------------------|

| MOVWF | EEADRH        | ; Upper bits of Data Memory Address to read |

| MOVLW | DATA_EE_ADDR  | i                                           |

| MOVWF | EEADR         | ; Lower bits of Data Memory Address to read |

| BCF   | EECON1, EEPGD | ; Point to DATA memory                      |

| BCF   | EECON1, CFGS  | ; Access EEPROM                             |

| BSF   | EECON1, RD    | ; EEPROM Read                               |

| NOP   |               |                                             |

| MOVF  | EEDATA, W     | ; W = EEDATA                                |

### EXAMPLE 9-2: DATA EEPROM WRITE

|          | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | DATA_EE_ADDRH<br>EEADRH<br>DATA_EE_ADDR<br>EEADR<br>DATA_EE_DATA<br>EEDATA | ;<br>; Upper bits of Data Memory Address to write<br>;<br>; Lower bits of Data Memory Address to write<br>;<br>; Data Memory Value to write |

|----------|----------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|          | BCF                                                | EECON1, EEPGD                                                              | ; Point to DATA memory                                                                                                                      |

|          | BCF                                                | EECON1, CFGS                                                               | ; Access EEPROM                                                                                                                             |

|          | BSF                                                | EECON1, WREN                                                               | ; Enable writes                                                                                                                             |

|          | BCF                                                | INTCON, GIE                                                                | ; Disable Interrupts                                                                                                                        |

|          | MOVLW                                              | 0x55                                                                       | ;                                                                                                                                           |

| Required | MOVWF                                              | EECON2                                                                     | ; Write 55h                                                                                                                                 |

| Sequence | MOVLW                                              | 0xAA                                                                       | i                                                                                                                                           |

|          | MOVWF                                              | EECON2                                                                     | ; Write OAAh                                                                                                                                |

|          | BSF                                                | EECON1, WR                                                                 | ; Set WR bit to begin write                                                                                                                 |

|          | BTFSC                                              | EECON1, WR                                                                 | ; Wait for write to complete GOTO \$-2                                                                                                      |

|          | BSF                                                | INTCON, GIE                                                                | ; Enable Interrupts                                                                                                                         |

|          |                                                    |                                                                            | · Harr godo ovogution                                                                                                                       |

|          | DOD                                                |                                                                            | ; User code execution                                                                                                                       |

|          | BCF                                                | EECON1, WREN                                                               | ; Disable writes on write complete (EEIF set)                                                                                               |

### REGISTER 11-11: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0         | U-0                                                                                 | R/W-0                                                      | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|---------------|-------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|---------|

| OSCFIE        | —                                                                                   | SSP2IE                                                     | BCL2IE          | BCL1IE            | HLVDIE           | TMR3IE          | TMR3GIE |

| bit 7         |                                                                                     |                                                            |                 |                   |                  |                 | bit 0   |

|               |                                                                                     |                                                            |                 |                   |                  |                 |         |

| Legend:       |                                                                                     |                                                            |                 |                   |                  |                 |         |

| R = Readable  | e bit                                                                               | W = Writable b                                             | bit             | U = Unimplem      | nented bit, read | d as '0'        |         |

| -n = Value at | POR                                                                                 | '1' = Bit is set                                           |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 7         | <b>OSCFIE:</b> Osc<br>1 = Enabled<br>0 = Disabled                                   | sillator Fail Inter                                        | rupt Enable bi  | t                 |                  |                 |         |

| bit 6         | Unimplemen                                                                          | ted: Read as 'o                                            | ,               |                   |                  |                 |         |

| bit 5         | SSP2IE: Mas                                                                         | ter Synchronou                                             | s Serial Port 2 | Interrupt Enab    | le bit           |                 |         |

|               |                                                                                     | the MSSP inter<br>the MSSP inter                           |                 |                   |                  |                 |         |

| bit 4         | 1 = Enables                                                                         | Collision Interru<br>the bus collision<br>the bus collisio | interrupt       |                   |                  |                 |         |

| bit 3         | BCL1IE: Bus Collision Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled           |                                                            |                 |                   |                  |                 |         |

| bit 2         | HLVDIE: High/Low-Voltage Detect Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                                                            |                 |                   |                  |                 |         |

| bit 1         | TMR3IE: TMR3 Overflow Interrupt Enable bit                                          |                                                            |                 |                   |                  |                 |         |

|               | 1 = Enabled<br>0 = Disabled                                                         |                                                            |                 |                   |                  |                 |         |

| bit 0         | TMR3GIE: Timer3 Gate Interrupt Enable bit 1 = Enabled 0 = Disabled                  |                                                            |                 |                   |                  |                 |         |

### 12.6 PORTE, TRISE and LATE Registers

PORTE is an eight-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISE and LATE.

All pins on PORTE are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. The RE7 pin is also configurable for open-drain output when ECCP2 is active on this pin. Open-drain configuration is selected by setting the CCP2OD control bit (ODCON1<6>)

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by setting bit, REPU (PADCFG1<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on any device Reset.

PORTE is also multiplexed with Enhanced PWM Outputs, B and C for ECCP1 and ECCP3, for Outputs, B, C and D for ECCP2. For all devices, their default assignments are on PORTE<6:0>.

On 80-pin devices, the multiplexing for the outputs of ECCP1 and ECCP3 is controlled by the ECCPMX Configuration bit. Clearing this bit re-assigns the P1B/P1C and P3B/P3C outputs to PORTH.

For devices operating in Microcontroller mode, the RE7 pin can be configured as the alternate peripheral pin for the ECCP2 module and Enhanced PWM Output 2A. This is done by clearing the CCP2MX Configuration bit. PORTE is also multiplexed with the Parallel Slave Port address lines. RE1 and RE0 are multiplexed with the control signals, WR and RD.

RE3 can also be configured as the Reference Clock Output (REFO) from the system clock. For further details, see **Section 3.7 "Reference Clock Output"**.

| CLRF  | PORTE | ; Initialize PORTE by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATE  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 03h   | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISE | ; Set RE<1:0> as inputs |

|       |       | ; RE<7:2> as outputs    |

| 1     |       |                         |

| Pin Name    | Function                                                                        | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                                        |  |  |  |

|-------------|---------------------------------------------------------------------------------|-----------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| RE0/RD/P2D  | RE0                                                                             | 0               | 0   | DIG         | LATE<0> data output.                                                                                               |  |  |  |

| AD8         | AD8                                                                             |                 |     | ST          | PORTE<0> data input.                                                                                               |  |  |  |

|             | RD         x         O         DIG         Parallel Slave Port read strobe pin. |                 |     |             | Parallel Slave Port read strobe pin.                                                                               |  |  |  |

|             |                                                                                 | x               | Ι   | TTL         | Parallel Slave Port read pin.                                                                                      |  |  |  |

|             | P2D                                                                             | 0               | 0   | —           | <ul> <li>ECCP2 PWM Output D.</li> <li>May be configured for tri-state during Enhanced PWM shutdown even</li> </ul> |  |  |  |

|             | AD8 <sup>(2)</sup>                                                              | x               | 0   | DIG         | G External memory interface, Data Bit 8 output.                                                                    |  |  |  |

|             |                                                                                 | x               | Ι   | TTL         | External memory interface, Data Bit 8 input.                                                                       |  |  |  |

| RE1/P2C/WR/ | RE1                                                                             | 0               | 0   | DIG         | LATE<1> data output.                                                                                               |  |  |  |

| AD9         |                                                                                 | 1               | Ι   | ST          | PORTE<1> data input.                                                                                               |  |  |  |

|             | P2C                                                                             | 0               | 0   | —           | ECCP2 PWM Output C.<br>May be configured for tri-state during Enhanced PWM shutdown events.                        |  |  |  |

|             | WR                                                                              | x               | 0   | DIG         | Parallel Slave Port write strobe pin.                                                                              |  |  |  |

|             |                                                                                 | x               | I   | TTL         | Parallel Slave Port write pin.                                                                                     |  |  |  |

|             | AD9 <sup>(2)</sup>                                                              | x               | 0   | DIG         | External memory interface, Data Bit 9 output.                                                                      |  |  |  |

|             |                                                                                 | x               | Ι   | TTL         | External memory interface, Data Bit 9 input.                                                                       |  |  |  |

### TABLE 12-9: PORTE FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared and in Microcontroller mode.

2: This feature is only available on PIC18F8XKXX devices.

### **19.3 Compare Mode**

In Compare mode, the 16-bit CCPR4 register value is constantly compared against the Timer register pair value selected in the CCPTMR1 register. When a match occurs, the CCP4 pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP4M<3:0>). At the same time, the interrupt flag bit, CCP4IF, is set.

Figure 19-2 gives the Compare mode block diagram

### 19.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP4CON register will force    |

|-------|---------------------------------------------|

|       | the RC1 or RE7 compare output latch         |

|       | (depending on device configuration) to the  |

|       | default low level. This is not the PORTC or |

|       | PORTE I/O data latch.                       |

### 19.3.2 TIMER1/3/5/7 MODE SELECTION

If the CCP module is using the compare feature in conjunction with any of the Timer1/3/5/7 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

| Note: | Details of the timer assignments for the |

|-------|------------------------------------------|

|       | CCP modules are given in Table 19-2 and  |

|       | Table 19-3.                              |

### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP4M<3:0> = 1010), the CCP4 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP4IE bit is set.

### 19.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP4M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP4 cannot start an A/D conversion.

Note: The Special Event Trigger of ECCP2 can start an A/D conversion, but the A/D Converter must be enabled. For more information, see Section 19.0 "Capture/Compare/PWM (CCP) Modules".

### REGISTER 20-2: CCPTMRS0: CCP TIMER SELECT 0 REGISTER

| R/W-0           | R/W-0                                                | R/W-0                                                                                                                                       | R/W-0                                                    | R/W-0            | R/W-0            | R/W-0            | R/W-0           |

|-----------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------------------|------------------|-----------------|

| C3TSEL1         | C3TSEL0                                              | C2TSEL2                                                                                                                                     | C2TSEL1                                                  | C2TSEL0          | C1TSEL2          | C1TSEL1          | C1TSEL0         |

| bit 7           |                                                      |                                                                                                                                             |                                                          |                  |                  |                  | bit (           |

| Legend:         |                                                      |                                                                                                                                             |                                                          |                  |                  |                  |                 |

| R = Readable    | bit                                                  | W = Writable                                                                                                                                | bit                                                      | U = Unimpler     | nented bit, read | as '0'           |                 |

| -n = Value at F | POR                                                  | '1' = Bit is set                                                                                                                            |                                                          | '0' = Bit is cle | ared             | x = Bit is unkr  | nown            |

|                 | 01 = ECCP3<br>10 = ECCP3                             | is based off of<br>is based off of<br>is based off of<br>is based off of                                                                    | TMR3/TMR4<br>TMR3/TMR6                                   |                  |                  |                  |                 |

| bit 5-3         | 000 = ECCP<br>001 = ECCP<br>010 = ECCP<br>011 = ECCP | >: ECCP2 Time<br>2 is based off of<br>2 is based off of | of TMR1/TMR<br>of TMR3/TMR<br>of TMR3/TMR<br>of TMR3/TMR | 2<br>4<br>6<br>8 | ed on the 32-Kb  | yte device varia | ant; do not use |

- 101 = Reserved; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

- bit 2-0 C1TSEL<2:0>: ECCP1 Timer Selection bits

- 000 = ECCP1 is based off of TMR1/TMR2

- 001 = ECCP1 is based off of TMR3/TMR4

- 010 = ECCP1 is based off of TMR3/TMR6

- 011 = ECCP1 is based off of TMR3/TMR8

- 100 = ECCP1 is based off of TMR3/TMR10: option reserved on the 32-Kbyte device variant; do not use

- 101 = ECCP1 is based off of TMR3/TMR12: option reserved on the 32-Kbyte device variant; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

NOTES:

### REGISTER 28-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| U-0   | R/P-1 | U-0 | R/P-1    | R/P-1    | R/P-1     | U-0 | R/P-1 |

|-------|-------|-----|----------|----------|-----------|-----|-------|

| —     | XINST | _   | SOSCSEL1 | SOSCSEL0 | INTOSCSEL | _   | RETEN |

| bit 7 |       |     |          |          |           |     | bit 0 |

| Legend:           | P = Programmable bit |                       |                    |

|-------------------|----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | XINST: Extended Instruction Set Enable bit                                                                                                                                                                                |

|         | <ul> <li>1 = Instruction set extension and Indexed Addressing mode are enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode are disabled (Legacy mode)</li> </ul>                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 4-3 | SOSCSEL<1:0>: SOSC Power Selection and Mode Configuration bits                                                                                                                                                            |

|         | <ul> <li>11 = High-power SOSC circuit is selected</li> <li>10 = Digital (SCLKI) mode; I/O port functionality of RC0 and RC1 is enabled</li> <li>01 = Low-power SOSC circuit is selected</li> <li>00 = Reserved</li> </ul> |

| bit 2   | INTOSCSEL: LF-INTOSC Low-power Enable bit                                                                                                                                                                                 |

|         | <ul> <li>1 = LF-INTOSC is in High-Power mode during Sleep</li> <li>0 = LF-INTOSC is in Low-Power mode during Sleep</li> </ul>                                                                                             |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 0   | RETEN: VREG Sleep Enable bit                                                                                                                                                                                              |

|         | 1 = Regulator power while in Sleep mode is controlled by VREGSLP (WDTCON<7>)<br>0 = Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-pow                                                |

= Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-power regulator is enabled.

NOTES:

| BCF                        | Bit Clear f                          |                                                                                                                                 |                                      | BN    |                                                       | Branch if N                                                                                               | legative                                                  |                        |  |

|----------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------|--|

| Syntax:                    | BCF f, b                             | {,a}                                                                                                                            |                                      | Synt  | ax:                                                   | BN n                                                                                                      |                                                           |                        |  |

| Operands:                  | $0 \leq f \leq 255$                  |                                                                                                                                 |                                      | Oper  | rands:                                                | -128 ≤ n ≤ 1                                                                                              | 127                                                       |                        |  |

|                            | 0 ≤ b ≤ 7<br>a ∈ [0,1]               |                                                                                                                                 |                                      | Oper  | Operation:                                            |                                                                                                           | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC |                        |  |

| Operation:                 | $0 \rightarrow f \le b >$            |                                                                                                                                 |                                      | Statu | Status Affected:                                      |                                                                                                           |                                                           |                        |  |

| Status Affected:           | None                                 | None                                                                                                                            |                                      |       | oding:                                                | 1110                                                                                                      | 0110 nn                                                   | nn nnnn                |  |

| Encoding:                  | 1001                                 | bbba ff                                                                                                                         | ff ffff                              |       | cription:                                             | If the Negat                                                                                              | tive bit is '1', th                                       | nen the                |  |

| Description:               | Bit 'b' in reg                       | gister 'f' is clea                                                                                                              | ared.                                |       |                                                       | program wi                                                                                                |                                                           |                        |  |

|                            | ,                                    |                                                                                                                                 | ank is selected.<br>ed to select the |       |                                                       | added to the incremente                                                                                   | d to fetch the                                            | e PC will have<br>next |  |

|                            | set is enabl                         | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing |                                      |       |                                                       | instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                                                           |                        |  |

|                            | mode whenever f $\leq$ 95 (5Fh). See |                                                                                                                                 | Word                                 | ds:   | 1                                                     |                                                                                                           |                                                           |                        |  |

|                            |                                      | .2.3 "Byte-O                                                                                                                    | riented and                          | Cycl  | es:                                                   | 1(2)                                                                                                      |                                                           |                        |  |

|                            | Literal Offs                         | set Mode" for                                                                                                                   |                                      |       | ycle Activity:<br>ump:                                |                                                                                                           |                                                           |                        |  |

| Words:                     | 1                                    |                                                                                                                                 |                                      |       | Q1                                                    | Q2                                                                                                        | Q3                                                        | Q4                     |  |

| Cycles:                    | 1                                    |                                                                                                                                 |                                      |       | Decode                                                | Read literal                                                                                              | Process                                                   | Write to               |  |

| Q Cycle Activity:          |                                      |                                                                                                                                 |                                      |       |                                                       | ʻn'                                                                                                       | Data                                                      | PC                     |  |

| Q1                         | Q2                                   | Q3                                                                                                                              | Q4                                   | l     | No<br>operation                                       | No<br>operation                                                                                           | No<br>operation                                           | No<br>operation        |  |

| Decode                     | Read<br>register 'f'                 | Process<br>Data                                                                                                                 | Write<br>register 'f'                | If N  | o Jump:                                               | operation                                                                                                 | operation                                                 | operation              |  |

|                            | - 5                                  |                                                                                                                                 | - 3                                  |       | Q1                                                    | Q2                                                                                                        | Q3                                                        | Q4                     |  |

| Example:                   | BCF F                                | LAG_REG,                                                                                                                        | 7, 0                                 |       | Decode                                                | Read literal                                                                                              | Process                                                   | No                     |  |

| Before Instruc             | ction                                |                                                                                                                                 |                                      |       |                                                       | 'n'                                                                                                       | Data                                                      | operation              |  |

| FLAG_R<br>After Instructio | EG = C7h                             |                                                                                                                                 |                                      | Exar  | nnle:                                                 | HERE                                                                                                      | BN Jump                                                   |                        |  |

|                            | FLAG_REG = 47h                       |                                                                                                                                 |                                      |       | Before Instruc<br>PC                                  | ction<br>= ad                                                                                             | dress (HERE)                                              |                        |  |

|                            |                                      |                                                                                                                                 |                                      |       | After Instructi<br>If Negati<br>PC<br>If Negati<br>PC | ve = 1;<br>= ad<br>ve = 0;                                                                                | dress (Jump)<br>dress (HERE                               |                        |  |

| ΜΟν              | 'LW                   | Move L             | Move Literal to W                           |      |                 |    |               |  |  |

|------------------|-----------------------|--------------------|---------------------------------------------|------|-----------------|----|---------------|--|--|

| Synta            | ax:                   | MOVLV              | MOVLW k                                     |      |                 |    |               |  |  |

| Oper             | ands:                 | $0 \le k \le 2$    | 255                                         | 5    |                 |    |               |  |  |

| Oper             | ation:                | $k\toW$            |                                             |      |                 |    |               |  |  |

| Status Affected: |                       | None               |                                             |      |                 |    |               |  |  |

| Encoding:        |                       | 0000               |                                             | 1110 | kkk             | ck | kkkk          |  |  |

| Description:     |                       | The eig            | The eight-bit literal 'k' is loaded into W. |      |                 |    |               |  |  |

| Words:           |                       | 1                  | 1                                           |      |                 |    |               |  |  |

| Cycle            | es:                   | 1                  | 1                                           |      |                 |    |               |  |  |

| QC               | ycle Activity:        |                    |                                             |      |                 |    |               |  |  |

|                  | Q1                    | Q2                 |                                             | Q3   | Q3              |    | Q4            |  |  |

| Decode           |                       | Read<br>literal 'k | ,                                           |      | Process<br>Data |    | /rite to<br>W |  |  |

|                  |                       |                    |                                             |      |                 |    |               |  |  |

| Example:         |                       | MOVLW              |                                             | 5Ah  |                 |    |               |  |  |

|                  | After Instructic<br>W | n<br>= 5Ah         |                                             |      |                 |    |               |  |  |

| MOVWF                                          | Move W to                                                                                               | f                                                                   |                                                                |                                                |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|

| Syntax:                                        | MOVWF                                                                                                   | f {,a}                                                              |                                                                |                                                |

| Operands:                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ a  \in  [0,1] \end{array}$                                       |                                                                     |                                                                |                                                |

| Operation:                                     | $(W) \to f$                                                                                             |                                                                     |                                                                |                                                |

| Status Affected:                               | None                                                                                                    |                                                                     |                                                                |                                                |

| Encoding:                                      | 0110                                                                                                    | 111a                                                                | ffff                                                           | ffff                                           |

| Description:                                   | Move data<br>Location 'f'<br>256-byte ba                                                                | can be a                                                            | 0                                                              |                                                |