Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                    | Pin Number      | Pin                      | Buffer                              |                                                                                                                              |  |  |

|------------------------------------------------------------------------------------|-----------------|--------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                           | QFN/TQFP        | Туре Туре                |                                     | Description                                                                                                                  |  |  |

|                                                                                    |                 |                          |                                     | PORTD is a bidirectional I/O port.                                                                                           |  |  |

| RD0/PSP0/CTPLS<br>RD0<br>PSP0<br>CTPLS                                             | 58              | I/O<br>I/O<br>O          | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port data.<br>CTMU pulse generator output.                                                    |  |  |

| RD1/PSP1/T5CKI/T7G<br>RD1<br>PSP1<br>T5CKI<br>T7G                                  | 55              | I/O<br>I/O<br>I          | ST<br>TTL<br>ST<br>ST               | Digital I/O.<br>Parallel Slave Port.<br>Timer5 clock input.<br>Timer7 external clock gate input.                             |  |  |

| RD2/PSP2<br>RD2<br>PSP2                                                            | 54              | I/O<br>O                 | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.                                                                                         |  |  |

| RD3/PSP3<br>RD3<br>PSP3                                                            | 53              | I/O<br>I/O               | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.                                                                                         |  |  |

| RD4/PSP4/SDO2<br>RD4<br>PSP4<br>SDO2                                               | 52              | I/O<br>I/O<br>O          | ST<br>TTL                           | Digital I/O.<br>Parallel Slave Port.<br>SPI data out.                                                                        |  |  |

| RD5/PSP5/SDI2/SDA2<br>RD5<br>PSP5<br>SDI2<br>SDA2                                  | 51              | I/O<br>I/O<br>I<br>I/O   | ST<br>TTL<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Parallel Slave Port.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                          |  |  |

| RD6/PSP6/SCK2/SCL2<br>RD6<br>PSP6<br>SCK2<br>SCL2 <sup>(4)</sup>                   | 50              | I/O<br>I/O<br>I/O<br>I/O | ST<br>TTL<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Parallel Slave Port.<br>Synchronous serial clock.<br>Synchronous serial clock I/O for I <sup>2</sup> C mode. |  |  |

| RD7/PSP7/ <mark>SS2</mark><br>RD7<br>PSP7<br>SS2                                   | 49              | I/O<br>I/O<br>I          | ST<br>TTL<br>TTL                    | Digital I/O.<br>Parallel Slave Port.<br>SPI slave select input.                                                              |  |  |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input<br>P = Power<br>$1^{2}$ CTM (SI | Trigger input w | vith CN                  | IOS levels                          | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)         |  |  |

l<sup>2</sup>C = l<sup>2</sup>C™/SMBus

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

| Pin Name                                                                            | Pin Number | Pin             | Buffer<br>Type                    | Description                                                                                                                       |  |

|-------------------------------------------------------------------------------------|------------|-----------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                     | TQFP       | Туре            |                                   |                                                                                                                                   |  |

|                                                                                     |            |                 |                                   | PORTH is a bidirectional I/O port.                                                                                                |  |

| RH0/AN23/A16<br>RH0<br>AN23<br>A16                                                  | 79         | I/O<br>I<br>I/O | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 23.<br>External Memory Address/Data 16.                                                              |  |

| RH1/AN22/A17<br>RH1<br>AN22<br>A17                                                  | 80         | I/O<br>I<br>I/O | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 22.<br>External Address/Data 17.                                                                     |  |

| RH2/AN21/A18<br>RH2<br>AN21<br>A18                                                  | 1          | I/O<br>I<br>I/O | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 21.<br>External Address/Data 18.                                                                     |  |

| RH3/AN20/A19<br>RH3<br>AN20<br>A19                                                  | 2          | I/O<br>I<br>I/O | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 20.<br>External Address/Data 19.                                                                     |  |

| RH4/CCP9/P3C/AN12/<br>C2INC<br>RH4<br>CCP9 <sup>(3,5)</sup><br>P3C<br>AN12<br>C2INC | 22         | I/O<br>I/O<br>I | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O.<br>Capture 9 input/Compare 9 output/PWM9 output.<br>ECCP3 PWM Output C.<br>Analog Input 12.<br>Comparator 2 Input C. |  |

| RH5/CCP8/P3B/AN13/<br>C2IND<br>RH5<br>CCP8 <sup>(5)</sup><br>P3B<br>AN13<br>C2IND   | 21         | 1/0<br>1/0<br>1 | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O.<br>Capture 8 input/Compare 8 output/PWM8 output.<br>ECCP3 PWM Output B.<br>Analog Input 13.<br>Comparator 1 Input D. |  |

| RH6/CCP7/P1C/AN14/<br>C1INC<br>RH6<br>CCP7 <sup>(5)</sup><br>P1C<br>AN14<br>C1INC   | 20         | I/O<br>I/O<br>I | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O.<br>Capture 7 input/Compare 7 output/PWM7 output.<br>ECCP1 PWM Output C.<br>Analog Input 14.<br>Comparator 1 Input C. |  |

#### **TABLE 1-4:** PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

- L = Input

- P = Power

Analog Analog Input 0 = Output OD = Open-Drain (no P diode to VDD)

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

| Pin Name                                                          | Pin Number              | Pin      | Buffer  | Description                                                                                                          |  |  |

|-------------------------------------------------------------------|-------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                   | TQFP                    | Туре     | Туре    | Description                                                                                                          |  |  |

|                                                                   |                         |          |         | PORTJ is a bidirectional I/O port.                                                                                   |  |  |

| RJ0/ALE<br>RJ0<br>ALE                                             | 62                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory address latch enable.                                                                |  |  |

| RJ1/OE<br>RJ1<br>OE                                               | 61                      | I/O<br>O | ST      | Digital I/O.<br>External memory output enable.                                                                       |  |  |

| RJ2/WRL<br>RJ2<br>WRL                                             | 60                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory write low control.                                                                   |  |  |

| RJ3/WRH<br>RJ3<br>WRH                                             | 59                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory high control.                                                                        |  |  |

| RJ4/BA0<br>RJ4<br>BA0                                             | 39                      | I/O<br>O | ST<br>— | Digital I/O.<br>External Memory Byte Address 0 control                                                               |  |  |

| RJ5/CE<br>RJ5<br>CE                                               | 40                      | I/O<br>O | ST<br>— | Digital I/O<br>External memory chip enable control.                                                                  |  |  |

| RJ6/LB<br>RJ6<br>LB                                               | 41                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory low byte control.                                                                    |  |  |

| RJ7/UB<br>RJ7<br>UB                                               | 42                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory high byte control.                                                                   |  |  |

| Vss                                                               | 11, 31, 51, 70          | Р        | —       | Ground reference for logic and I/O pins.                                                                             |  |  |

| VDD                                                               | 32, 48, 71              | Р        | —       | Positive supply for logic and I/O pins.                                                                              |  |  |

| AVss                                                              | 26                      | Р        |         | Ground reference for analog modules.                                                                                 |  |  |

| AVDD                                                              | 25                      | P        |         | Positive supply for analog modules.                                                                                  |  |  |

| ENVREG<br>Vddcore/Vcap                                            | 24<br>12                | I        | ST      | Enable for on-chip voltage regulator.<br>Core logic power or external filter capacitor connection.                   |  |  |

| Vddcore<br>Vcap                                                   |                         | Ρ        | _       | External filter capacitor connection (regulator enabled/disabled).                                                   |  |  |

| I = Input<br>P = Power<br>I <sup>2</sup> C = I <sup>2</sup> C™/SM | rigger input wit<br>Bus |          |         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |

#### PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

### 6.1.3.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero.

The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

What happens when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (For a description of the device Configuration bits, see **Section 28.1 "Configuration Bits"**.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and set the STKUNF bit while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | stack conditions can be verified and                                                                                             |

|       | appropriate actions can be taken. This is                                                                                        |

|       | not the same as a Reset as the contents of the SFRs are not affected.                                                            |

### 6.1.3.3 PUSH and POP Instructions

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off of the stack, without disturbing normal program execution, is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

bit 0

#### R/C-0 R/C-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 STKFUL<sup>(1)</sup> STKUNF<sup>(1)</sup> SP4 SP3 SP2 SP1 SP0 bit 7

STKPTR: STACK POINTER REGISTER

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7            | <b>STKFUL:</b> Stack Full Flag bit <sup>(1)</sup><br>1 = Stack has become full or overflowed<br>0 = Stack has not become full or overflowed |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6            | <b>STKUNF:</b> Stack Underflow Flag bit <sup>(1)</sup><br>1 = Stack underflow has occurred<br>0 = Stack underflow did not occur             |

| bit 5<br>bit 4-0 | <b>Unimplemented:</b> Read as '0'<br><b>SP&lt;4:0&gt;:</b> Stack Pointer Location bits                                                      |

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

**REGISTER 6-1:**

| Address | File Name | Bit 7         | Bit 6            | Bit 5                                | Bit 4        | Bit 3            | Bit 2                        | Bit 1        | Bit 0   | Value on POR, BOR |

|---------|-----------|---------------|------------------|--------------------------------------|--------------|------------------|------------------------------|--------------|---------|-------------------|

| F86h    | PORTG     | _             | _                | RG5 <sup>(1)</sup>                   | RG4          | RG3              | RG2                          | RG1          | RG0     | xx xxxx           |

| F85h    | PORTF     | RF7           | RF6              | RF5                                  | RF4          | RF3              | RF2                          | RF1          | —       | xxxx xxx-         |

| F84h    | PORTE     | RE7           | RE6              | RE5                                  | RE4          | RE3              | RE2                          | RE1          | RE0     | XXXX XXXX         |

| F83h    | PORTD     | RD7           | RD6              | RD5                                  | RD4          | RD3              | RD2                          | RD1          | RD0     | XXXX XXXX         |

| F82h    | PORTC     | RC7           | RC6              | RC5                                  | RC4          | RC3              | RC2                          | RC1          | RC0     | XXXX XXXX         |

| F81h    | PORTB     | RB7           | RB6              | RB5                                  | RB4          | RB3              | RB2                          | RB1          | RB0     | XXXX XXXX         |

| F80h    | PORTA     | RA7           | RA6              | RA5                                  | RA4          | RA3              | RA2                          | RA1          | RA0     | XXXX XXXX         |

| F7Fh    | EECON1    | EEPGD         | CFGS             | —                                    | FREE         | WRERR            | WREN                         | WR           | RD      | xx-0 x000         |

| F7Eh    | EECON2    | EEPROM Cor    | ntrol Register 2 | (not a physica                       | al register) |                  |                              |              |         |                   |

| F7Dh    | TMR5H     | Timer5 Regist | er High Byte     |                                      |              |                  |                              |              |         | XXXX XXXX         |

| F7Ch    | TMR5L     | Timer5 Regist | er Low Byte      |                                      |              |                  |                              |              |         | XXXX XXXX         |

| F7Bh    | T5CON     | TMR5CS1       | TMR5CS0          | T5CKPS1                              | T5CKPS0      | SOSCEN           | T5SYNC                       | RD16         | TMR5ON  | 0000 0000         |

| F7Ah    | T5GCON    | TMR5GE        | T5GPOL           | T5GTM                                | T5GSPM       | T5GGO/<br>T5DONE | T5GVAL                       | T5GSS1       | T5GSS0  | 0000 0x00         |

| F79h    | CCPR4H    | Capture/Comp  | bare/PWM Reg     | gister 4 High B                      | yte          |                  |                              |              | •       | XXXX XXXX         |

| F78h    | CCPR4L    | Capture/Comp  | bare/PWM Reg     | gister 4 Low By                      | /te          |                  |                              |              |         | XXXX XXXX         |

| F77h    | CCP4CON   | _             | _                | DC4B1                                | DC4B0        | CCP4M3           | CCP4M2                       | CCP4M1       | CCP4M0  | 00 0000           |

| F76h    | CCPR5H    | Capture/Comp  | bare/PWM Reg     | gister 5 High B                      | yte          |                  |                              |              | •       | XXXX XXXX         |

| F75h    | CCPR5L    | Capture/Comp  | bare/PWM Reg     | gister 5 Low By                      | /te          |                  |                              |              |         | XXXX XXXX         |

| F74h    | CCP5CON   | _             | —                | DC5B1                                | DC5B0        | CCP5M3           | CCP5M2                       | CCP5M1       | CCP5M0  | 00 0000           |

| F73h    | CCPR6H    | Capture/Comp  | bare/PWM Reg     | gister 6 High B                      | yte          |                  |                              |              |         | XXXX XXXX         |

| F72h    | CCPR6L    | Capture/Comp  | bare/PWM Reg     | gister 6 Low By                      | /te          |                  |                              |              |         | XXXX XXXX         |

| F71h    | CCP6CON   | _             | —                | DC6B1                                | DC6B0        | CCP6M3           | CCP6M2                       | CCP6M1       | CCP6M0  | 00 0000           |

| F70h    | CCPR7H    | Capture/Comp  | bare/PWM Reg     | gister 7 High B                      | yte          |                  |                              |              |         | XXXX XXXX         |

| F6Fh    | CCPR7L    | Capture/Comp  | bare/PWM Reg     | gister 7 Low By                      | /te          |                  |                              |              |         | XXXX XXXX         |

| F6Eh    | CCP7CON   | _             | —                | DC7B1                                | DC7B0        | CCP7M3           | CCP7M2                       | CCP7M1       | CCP7M0  | 00 0000           |

| F6Dh    | TMR4      | Timer4 Regist | er               |                                      |              |                  |                              |              |         | XXXX XXXX         |

| F6Ch    | PR4       | Timer4 Period | Register         |                                      |              |                  |                              |              |         | 1111 1111         |

| F6Bh    | T4CON     | _             | T4OUTPS3         | T4OUTPS2                             | T4OUTPS1     | T4OUTPS0         | TMR4ON                       | T4CKPS1      | T4CKPS0 | -111 1111         |

| F6Ah    | SSP2BUF   | MSSP Receiv   | e Buffer/Trans   | mit Register                         |              |                  |                              |              |         | XXXX XXXX         |

| F69h    | SSP2ADD   | MSSP Addres   | s Register in l  | <sup>2</sup> C <sup>™</sup> Slave Mo | de. MSSP1 Ba | ud Rate Reloa    | d Register in I <sup>2</sup> | C Master Mod | e.      | 0000 0000         |

| F68h    | SSP2STAT  | SMP           | CKE              | D/A                                  | Р            | S                | R/W                          | UA           | BF      | 0000 0000         |

| F67h    | SSP2CON1  | WCOL          | SSPOV            | SSPEN                                | CKP          | SSPM3            | SSPM2                        | SSPM1        | SSPM0   | 0000 0000         |

| F66h    | SSP2CON2  | GCEN          | ACKSTAT          | ACKDT                                | ACKEN        | RCEN             | PEN                          | RSEN         | SEN     | 0100 0000         |

| F65h    | BAUDCON1  | ABDOVF        | RCIDL            | RXDTP                                | TXCKP        | BRG16            |                              | WUE          | ABDEN   | 0100 0-00         |

| F64h    | OSCCON2   | _             | SOSCRUN          | _                                    | _            | SOSCGO           | _                            | MFIOFS       | MFIOSEL | -0 0-x0           |

| F63h    | EEADRH    | EEPROM Add    | dress Register   | Hiah Bvte                            |              |                  |                              |              |         | 0000 0000         |

| F62h    | EEADR     |               | dress Register   | • ,                                  |              |                  |                              |              |         | 0000 0000         |

| F61h    | EEDATA    | EEPROM Dat    | Ŭ                | ,                                    |              |                  |                              |              |         | 0000 0000         |

| F60h    | PIE6      | _             |                  | _                                    | EEIE         | _                | CMP3IE                       | CMP2IE       | CMP1IE  | 0 -000            |

| F5Fh    | RTCCFG    | RTCEN         |                  | RTCWREN                              | RTCSYNC      | HALFSEC          | RTCOE                        | RTCPTR1      | RTCPTR0 | 0-00 0000         |

| F5Eh    | RTCCAL    | CAL7          | CAL6             | CAL5                                 | CAL4         | CAL3             | CAL2                         | CAL1         | CALO    | 0000 0000         |

|         | RTCVALH   |               |                  |                                      | on RTCPTR<1  |                  |                              |              |         | xxxx xxxx         |

#### PIC18F87K22 FAMILY REGISTER FILE SUMMARY (CONTINUED) **TABLE 6-2**:

This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented. Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'. Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22). Note 1: 2: 3:

## 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read the 64 or 128 bytes into RAM.

- 2. Update the data values in RAM as necessary.

- 3. Load the Table Pointer register with the address being erased.

- 4. Execute the row erase procedure.

- 5. Load the Table Pointer register with the address of the first byte being written.

- 6. Write the 64 or 128 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- Set the EEPGD bit to point to program memory

- · Clear the CFGS bit to access program memory

- · Set the WREN to enable byte writes

- 8. Disable the interrupts.

- 9. Write 0x55 to EECON2.

- 10. Write 0xAA to EECON2.

- Set the WR bit. This will begin the write cycle. The CPU will stall for duration of the write for Tiw (see Parameter D133A).

- 12. Re-enable the interrupts.

- 13. Verify the memory (table read).

An example of the required code is shown in Example 7-3.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 or 128 bytes in the holding register.

Note: Self-write execution to Flash and EEPROM memory cannot be done while running in LP Oscillator mode (Low-Power mode). Therefore, executing a self-write will put the device into High-Power mode.

### REGISTER 11-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0   |

|--------|-----|--------|--------|--------|--------|--------|---------|

| OSCFIF | —   | SSP2IF | BCL2IF | BCL1IF | HLVDIF | TMR3IF | TMR3GIF |

| bit 7  |     |        |        |        |        |        | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| 1 = Device oscillator failed, clock input has changed to INTOSC (must be cleared in software)         0 = Device clock is operating         bit 6       Unimplemented: Read as '0'         bit 5       SSP2IF: Master Synchronous Serial Port Interrupt Flag bit         1 = The transmission/reception has been completed (must be cleared in software)         0 = Waiting to transmit/receive         bit 4       BCL2IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred         bit 4       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)       0         0 = No bus collision occurred       bit 2         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)       0         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0         0 = TMR3 GiF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interr | bi | t 7 | OSCFIF: Oscillator Fail Interrupt Flag bit                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----------------------------------------------------------|

| bit 5       SSP2IF: Master Synchronous Serial Port Interrupt Flag bit         1 = The transmission/reception has been completed (must be cleared in software)         0 = Waiting to transmit/receive         bit 4       BCL2IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred         bit 4       BCL2IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register did not overflow         0 = TMR3 Gate Interrupt Flag bit       1 = Timer gate interrupt occurred (must be cleared in software)         0 = TMR3 register did not overflow       1 = Timer gate interrupt occurred (must be cleared in software)                                      |    |     |                                                           |

| 1 = The transmission/reception has been completed (must be cleared in software)         0 = Waiting to transmit/receive         bit 4       BCL2IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow       0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)       0 = TMR3 register did not overflow                                                                                                                                                     | bi | t 6 | Unimplemented: Read as '0'                                |

| 0 = Waiting to transmit/receive         bit 4       BCL2IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                     | bi | t 5 | SSP2IF: Master Synchronous Serial Port Interrupt Flag bit |

| 1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)       1 = Timer gate interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |                                                           |

| 0 = No bus collision occurred         bit 3       BCL1IF: Bus Collision Interrupt Flag bit         1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bi | t 4 | BCL2IF: Bus Collision Interrupt Flag bit                  |

| 1 = A bus collision occurred (must be cleared in software)         0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |                                                           |

| 0 = No bus collision occurred         bit 2       HLVDIF: High/Low-Voltage Detect Interrupt Flag bit         1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bi | t 3 | BCL1IF: Bus Collision Interrupt Flag bit                  |

| 1 = A low-voltage condition occurred (must be cleared in software)         0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |                                                           |

| 0 = The device voltage is above the regulator's low-voltage trip point         bit 1       TMR3IF: TMR3 Overflow Interrupt Flag bit         1 = TMR3 register overflowed (must be cleared in software)       0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bi | t 2 | HLVDIF: High/Low-Voltage Detect Interrupt Flag bit        |

| 1 = TMR3 register overflowed (must be cleared in software)         0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |     |                                                           |

| 0 = TMR3 register did not overflow         bit 0       TMR3GIF: TMR3 Gate Interrupt Flag bit         1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bi | t 1 | TMR3IF: TMR3 Overflow Interrupt Flag bit                  |

| 1 = Timer gate interrupt occurred (must be cleared in software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |     |                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bi | t 0 | TMR3GIF: TMR3 Gate Interrupt Flag bit                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |     |                                                           |

### 23.4 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the  $GO/\overline{DONE}$  bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit.

This occurs when the ACQT<2:0> bits (ADCON2<5:3>) remain in their Reset state ('000'), which is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQTx bits can be set to select a programmable acquisition time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

### 23.5 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 14 TAD per 12-bit conversion. The source of the A/D conversion clock is software-selectable.

The possible options for TAD are:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Using the internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD. (For more information, see Parameter 130 in Table 31-28.)

Table 23-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## TABLE 23-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S        | Maximum   |                         |

|-------------------|-----------|-------------------------|

| Operation         | ADCS<2:0> | Device<br>Frequency     |

| 2 Tosc            | 000       | 2.50 MHz                |

| 4 Tosc            | 100       | 5.00 MHz                |

| 8 Tosc            | 001       | 10.00 MHz               |

| 16 Tosc           | 101       | 20.00 MHz               |

| 32 Tosc           | 010       | 40.00 MHz               |

| 64 Tosc           | 110       | 64.00 MHz               |

| RC <sup>(2)</sup> | x11       | 1.00 MHz <sup>(1)</sup> |

Note 1: The RC source has a typical TAD time of  $4 \ \mu$ s.

2: For device frequencies above 1 MHz, the device must be in Sleep mode for the entire conversion or the A/D accuracy may be out of specification.

### 23.6 Configuring Analog Port Pins

The ANCON0, ANCON1, ANCON2, TRISA, TRISF, TRISG and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRISx bits set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRISx bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

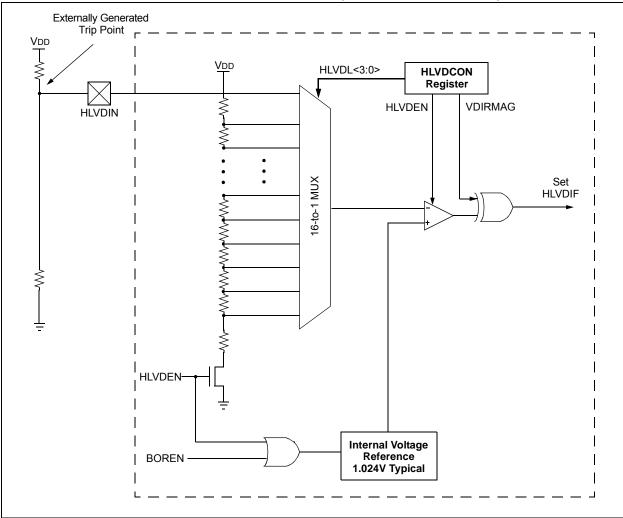

The module is enabled by setting the HLVDEN bit (HLVDCON<4>). Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit (HLVDCON<5>) is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit (HLVDCON<7>) determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

### 26.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated voltage reference as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users the flexibility of configuring the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 26-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

### REGISTER 28-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| U-0   | R/P-1 | U-0 | R/P-1    | R/P-1    | R/P-1     | U-0 | R/P-1 |

|-------|-------|-----|----------|----------|-----------|-----|-------|

| —     | XINST | _   | SOSCSEL1 | SOSCSEL0 | INTOSCSEL | _   | RETEN |

| bit 7 |       |     |          |          |           |     | bit 0 |

| Legend:           | P = Programmable bit |                       |                    |

|-------------------|----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | XINST: Extended Instruction Set Enable bit                                                                                                                                                                                |

|         | <ul> <li>1 = Instruction set extension and Indexed Addressing mode are enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode are disabled (Legacy mode)</li> </ul>                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 4-3 | SOSCSEL<1:0>: SOSC Power Selection and Mode Configuration bits                                                                                                                                                            |

|         | <ul> <li>11 = High-power SOSC circuit is selected</li> <li>10 = Digital (SCLKI) mode; I/O port functionality of RC0 and RC1 is enabled</li> <li>01 = Low-power SOSC circuit is selected</li> <li>00 = Reserved</li> </ul> |

| bit 2   | INTOSCSEL: LF-INTOSC Low-power Enable bit                                                                                                                                                                                 |

|         | <ul> <li>1 = LF-INTOSC is in High-Power mode during Sleep</li> <li>0 = LF-INTOSC is in Low-Power mode during Sleep</li> </ul>                                                                                             |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 0   | RETEN: VREG Sleep Enable bit                                                                                                                                                                                              |

|         | 1 = Regulator power while in Sleep mode is controlled by VREGSLP (WDTCON<7>)<br>0 = Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-pow                                                |

Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-power regulator is enabled.

## 28.3.2 OPERATION OF REGULATOR IN SLEEP

The difference in the two regulators' operation arises with Sleep mode. The ultra low-power regulator gives the device the lowest current in the Regulator Enabled mode.

The on-chip regulator can go into a lower power mode, when the device goes to Sleep, by setting the REGSLP bit (WDTCON<7>). This puts the regulator in a Standby mode so that the device consumes much less current.

The on-chip regulator can also go into the Ultra Low-Power mode, which consumes the lowest current possible with the regulator enabled. This mode is controlled by the RETEN bit (CONFIG1L<0>) and SRETEN bit (WDTCON<4>). The various modes of regulator operation are shown in Table 28-3.

When the ultra low-power regulator is in Sleep mode, the internal reference voltages in the chip will be shut off and any interrupts referring to the internal reference will not wake up the device. If the BOR or LVD is enabled, the regulator will keep the internal references on and the lowest possible current will not be achieved.

When using the ultra low-power regulator in Sleep mode, the device will take about 250  $\mu$ s, typical, to start executing the code after it wakes up.

| TABLE 20-3. SELET MODE REGULATOR SETTINGS A |                                                                                                                                                                           |                                                                                                                                                       |                                                                                                                                                       |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Power Mode                                  | VREGSLP<br>WDTCON<7>                                                                                                                                                      | SRETEN<br>WDTCON<4>                                                                                                                                   | RETEN<br>CONFIG1L<0>                                                                                                                                  |  |  |  |

| Normal Operation (Sleep)                    | 0                                                                                                                                                                         | x                                                                                                                                                     | 1                                                                                                                                                     |  |  |  |

| Low-Power mode (Sleep)                      | 1                                                                                                                                                                         | x                                                                                                                                                     | 1                                                                                                                                                     |  |  |  |

| Normal Operation (Sleep)                    | 0                                                                                                                                                                         | 0                                                                                                                                                     | х                                                                                                                                                     |  |  |  |

| Low-Power mode (Sleep)                      | 1                                                                                                                                                                         | 0                                                                                                                                                     | х                                                                                                                                                     |  |  |  |

| Ultra Low-Power mode (Sleep)                | x                                                                                                                                                                         | 1                                                                                                                                                     | 0                                                                                                                                                     |  |  |  |

|                                             | Power Mode         Normal Operation (Sleep)         Low-Power mode (Sleep)         Normal Operation (Sleep)         Low-Power mode (Sleep)         Low-Power mode (Sleep) | Power ModeVREGSLP<br>WDTCON<7>Normal Operation (Sleep)0Low-Power mode (Sleep)1Normal Operation (Sleep)0Low-Power mode (Sleep)1Low-Power mode (Sleep)1 | Power ModeVREGSLP<br>WDTCON<7>SRETEN<br>WDTCON<4>Normal Operation (Sleep)0×Low-Power mode (Sleep)1×Normal Operation (Sleep)00Low-Power mode (Sleep)10 |  |  |  |

### TABLE 28-3: SLEEP MODE REGULATOR SETTINGS<sup>(1)</sup>

**Note 1:** x = Indicates that VIT status is invalid.

Increment f, Skip if Not 0

INFSNZ f {,d {,a}}

| INCFSZ                 | Increment                                                                          | f, Skip if 0                                                                                                                      |                                                                        | INFSNZ              |

|------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|

| Syntax:                | INCFSZ f                                                                           | {,d {,a}}                                                                                                                         |                                                                        | Syntax:             |

| Operands:              | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ |                                                                                                                                   |                                                                        | Operands:           |

| Operation:             | (f) + 1 $\rightarrow$ de skip if result                                            |                                                                                                                                   |                                                                        | Operation:          |

| Status Affected:       | None                                                                               |                                                                                                                                   |                                                                        | Status Affected:    |

| Encoding:              | 0011                                                                               | 11da fff                                                                                                                          | ff ffff                                                                | Encoding:           |

| Description:           | incremented<br>placed in W                                                         | ts of register 'f<br>d. If 'd' is '0', th<br>f. If 'd' is '1', th<br>c in register 'f'.                                           | ne result is<br>e result is                                            | Description:        |

|                        | which is alread                                                                    | is '0', the next<br>eady fetched is<br>s executed ins<br>e instruction.                                                           | s discarded                                                            |                     |

|                        |                                                                                    |                                                                                                                                   | nk is selected.<br>d to select the                                     |                     |

|                        | set is enable<br>in Indexed L<br>mode when<br>Section 29.<br>Bit-Oriente           | nd the extended<br>ed, this instruct<br>Literal Offset A<br>ever $f \le 95$ (5F<br>2.3 "Byte-Ori<br>d Instruction<br>et Mode" for | ction operates<br>Addressing<br>Fh). See<br>iented and<br>s in Indexed |                     |

| Words:                 | 1                                                                                  |                                                                                                                                   |                                                                        | Words:              |

| Cycles:                |                                                                                    | ycles if skip a<br>a 2-word instr                                                                                                 |                                                                        | Cycles:             |

| Q Cycle Activity:      |                                                                                    |                                                                                                                                   |                                                                        | Q Cycle Activity    |

| Q1                     | Q2                                                                                 | Q3                                                                                                                                | Q4                                                                     | Q1                  |

| Decode                 | Read                                                                               | Process                                                                                                                           | Write to                                                               | Decode              |

| lf skip:               | register 'f'                                                                       | Data                                                                                                                              | destination                                                            | lf skip:            |

| Q1                     | Q2                                                                                 | Q3                                                                                                                                | Q4                                                                     | Q1                  |

| No                     | No                                                                                 | No                                                                                                                                | No                                                                     | No                  |

| operation              | operation                                                                          | operation                                                                                                                         | operation                                                              | operation           |

| If skip and followed   | 3                                                                                  |                                                                                                                                   | 04                                                                     | If skip and follow  |

| Q1<br>No               | Q2<br>No                                                                           | Q3<br>No                                                                                                                          | Q4<br>No                                                               | Q1                  |