What is "Embedded - Microcontrollers"?

Welcome to E-XFL.COM

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

> Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 64MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 32KB (16K x 16)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                          |

| Supplier Device Package    | 64-VQFN (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22-i-mrrsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

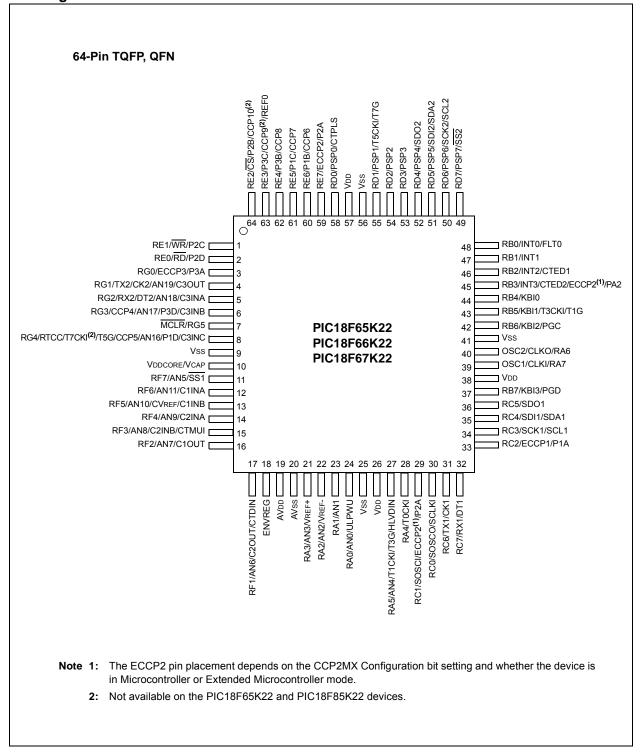

### Pin Diagrams – PIC18F6XK22

#### 3.6 Internal Oscillator Block

The PIC18F87K22 family of devices includes an internal oscillator block which generates two different clock signals. Either clock can be used as the microcontroller's clock source, which may eliminate the need for an external oscillator circuit on the OSC1 and/or OSC2 pins.

The internal oscillator consists of three blocks, depending on the frequency of operation. They are HF-INTOSC, MF-INTOSC and LF-INTRC.

In HF-INTOSC mode, the internal oscillator can provide a frequency ranging from 31 kHz to 16 MHz, with the postscaler deciding the selected frequency (IRCF<2:0>).

The INTSRC bit (OSCTUNE<7>) and MFIOSEL bit (OSCCON2<0>) also decide which INTOSC provides the lower frequency (500 kHz to 31 KHz). For the HF-INTOSC to provide these frequencies, INTSRC = 1 and MFIOSEL = 0.

In HF-INTOSC, the postscaler (IRCF<2:0>) provides the frequency range of 31 kHz to 16 MHz. If HF-INTOSC is used with the PLL, the input frequency to the PLL should be 8 MHz or 16 MHz (IRCF<2:0> = 111 or 110).

For MF-INTOSC mode to provide a frequency range of 500 kHz to 31 kHz, INTSRC = 1 and MFIOSEL = 1. The postscaler (IRCF<2:0>), in this mode, provides the frequency range of 31 kHz to 500 kHz.

The LF-INTRC can provide only 31 kHz if INTSRC = 0.

The LF-INTRC provides 31 kHz and is enabled if it is selected as the device clock source. The mode is enabled automatically when any of the following are enabled:

- · Power-up Timer

- Fail-Safe Clock Monitor

- · Watchdog Timer

- Two-Speed Start-up

These features are discussed in greater detail in Section 28.0 "Special Features of the CPU".

The clock source frequency (HF-INTOSC, MF-INTOSC or LF-INTRC direct) is selected by configuring the IRCF bits of the OSCCON register, as well the INTSRC and MFIOSEL bits. The default frequency on device Resets is 8 MHz.

#### 3.6.1 INTIO MODES

Using the internal oscillator as the clock source eliminates the need for up to two external oscillator pins, which can then be used for digital I/O. Two distinct oscillator configurations, which are determined by the FOSC Configuration bits, are available:

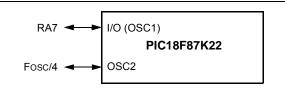

- In INTIO1 mode, the OSC2 pin (RA6) outputs Fosc/4, while OSC1 functions as RA7 (see Figure 3-8) for digital input and output.

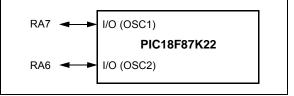

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6 (see Figure 3-9). Both are available as digital input and output ports.

#### FIGURE 3-8: INTIO1 OSCILLATOR MODE

#### FIGURE 3-9: INTIO2 OSCILLATOR MODE

#### 3.6.2 INTPLL MODES

The 4x Phase Lock Loop (PLL) can be used with the HF-INTOSC to produce faster device clock speeds than are normally possible with the internal oscillator sources. When enabled, the PLL produces a clock speed of 32 MHz or 64 MHz.

PLL operation is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation. Additionally, the PLL will only function when the selected HF-INTOSC frequency is either 8 MHz or 16 MHz (OSCCON<6:4> = 111 or 110).

Like the INTIO modes, there are two distinct INTPLL modes available:

- In INTPLL1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output. Externally, this is identical in appearance to INTIO1 (Figure 3-8).

- In INTPLL2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output. Externally, this is identical to INTIO2 (Figure 3-9).

| TABLE 5-2: |                            |                            |           | GISTERS (CONTINU<br>MCLR Resets,                               |                                 |  |

|------------|----------------------------|----------------------------|-----------|----------------------------------------------------------------|---------------------------------|--|

| Register   | Applicabl                  | Applicable Devices         |           | WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| ECCP1AS    | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| ECCP1DEL   | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| CCPR1H     | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCPR1L     | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCP1CON    | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| PIR5       | PIC18F65K22                | PIC18F85K22                | 0 -000    | 0 -000                                                         | u -uuu                          |  |

| PIR5       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| PIE5       | PIC18F65K22                | PIC18F85K22                | 0 0000    | 0 0000                                                         | u uuuu <b>(1)</b>               |  |

| PIE5       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 000  | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| IPR4       | PIC18F65K22                | PIC18F85K22                | 11 1111   | 11 1111                                                        | uu uuuu                         |  |

| IPR4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 1111 1111 | 1111 1111                                                      | uuuu uuuu                       |  |

| PIR4       | PIC18F65K22                | PIC18F85K22                | 00 0000   | 00 0000                                                        | uu uuuu <b>(1)</b>              |  |

| PIR4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000 | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| PIE4       | PIC18F65K22                | PIC18F85K22                | 00 0000   | 00 0000                                                        | uu uuuu                         |  |

| PIE4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| CVRCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| CMSTAT     | PIC18F6XK22                | PIC18F8XK22                | xxx       | xxx                                                            | uuu                             |  |

| TMR3H      | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx | սսսս սսսս                                                      | սսսս սսսս                       |  |

| TMR3L      | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx | սսսս սսսս                                                      | սսսս սսսս                       |  |

| T3CON      | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 00x0 0x00                                                      | սսսս սսսս                       |  |

| T3GCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00 | 0000 0000                                                      | սսսս սսսս                       |  |

| SPBRG1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | uuuu uuuu                       |  |

| RCREG1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000 | 0000 0000                                                      | սսսս սսսս                       |  |

| TXREG1     | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx | xxxx xxxx                                                      | սսսս սսսս                       |  |

| TXSTA1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0010 | 0000 0010                                                      | սսսս սսսս                       |  |

| RCSTA1     | PIC18F6XK22                | PIC18F8XK22                | 0000 000x | 0000 000x                                                      | սսսս սսսս                       |  |

| T1GCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00 | 00x0 0x00                                                      | uuuu -uuu                       |  |

| IPR6       | PIC18F6XK22                | PIC18F8XK22                | 1 -111    | 1 -111                                                         | u -uuu                          |  |

| HLVDCON    | PIC18F6XK22                | PIC18F8XK22                | 0000 0101 | 0000 0101                                                      | uuuu uuuu                       |  |

| PSPCON     | PIC18F6XK22                | PIC18F8XK22                | 0000      | 0000                                                           | uuuu                            |  |

| PIR6       | PIC18F6XK22                | PIC18F8XK22                | 0 -000    | 0 -000                                                         | u -uuu                          |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt, and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

### 8.1 External Memory Bus Control

The operation of the interface is controlled by the MEMCON register (Register 8-1). This register is available in all program memory operating modes except Microcontroller mode. In this mode, the register is disabled and cannot be written to.

The EBDIS bit (MEMCON<7>) controls the operation of the bus and related port functions. Clearing EBDIS enables the interface and disables the I/O functions of the ports, as well as any other functions multiplexed to those pins. Setting the bit enables the I/O ports and other functions, but allows the interface to override everything else on the pins when an external memory operation is required. By default, the external bus is always enabled and disables all other I/O. The operation of the EBDIS bit is also influenced by the program memory mode being used. This is discussed in more detail in Section 8.5 "Program Memory Modes and the External Memory Bus".

The WAIT bits allow for the addition of Wait states to external memory operations. The use of these bits is discussed in **Section 8.3 "Wait States**".

The WM bits select the particular operating mode used when the bus is operating in 16-Bit Data Width mode. These bits are discussed in more detail in **Section 8.6 "16-Bit Data Width Modes"**. These bits have no effect when an 8-Bit Data Width mode is selected.

### REGISTER 8-1: MEMCON: EXTERNAL MEMORY BUS CONTROL REGISTER<sup>(1)</sup>

| R/W-0        | U-0                   | R/W-0             | R/W-0           | U-0               | U-0              | R/W-0           | R/W-0            |

|--------------|-----------------------|-------------------|-----------------|-------------------|------------------|-----------------|------------------|

| EBDIS        |                       | WAIT1             | WAIT0           | _                 | —                | WM1             | WM0              |

| bit 7        |                       | ·                 |                 |                   |                  | -               | bit 0            |

|              |                       |                   |                 |                   |                  |                 |                  |

| Legend:      |                       |                   |                 |                   |                  |                 |                  |

| R = Readal   | ble bit               | W = Writable      | bit             | U = Unimplem      | nented bit, read | 1 as '0'        |                  |

| -n = Value a | at POR                | '1' = Bit is set  |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown             |

|              |                       |                   |                 |                   |                  |                 |                  |

| bit 7        | EBDIS: Exter          | nal Bus Disabl    | e bit           |                   |                  |                 |                  |

|              | 1 = External          | bus is enabled    | when microco    | ontroller access  | es external me   | emory; otherwis | se, all external |

|              |                       | rs are mapped     |                 |                   |                  |                 |                  |

|              | 0 = External          | bus is always e   | enabled, I/O po | orts are disabled | 1                |                 |                  |

| bit 6        | Unimplemen            | ted: Read as '    | )'              |                   |                  |                 |                  |

| bit 5-4      | WAIT<1:0>:            | Table Reads ar    | d Writes Bus    | Cycle Wait Cour   | nt bits          |                 |                  |

|              | 11 = Table rea        | ads and writes    | will wait 0 TCY |                   |                  |                 |                  |

|              | 10 = Table rea        | ads and writes    | will wait 1 TCY |                   |                  |                 |                  |

|              |                       | ads and writes    |                 |                   |                  |                 |                  |

|              | 00 = Table re         | ads and writes    | will wait 3 TCY |                   |                  |                 |                  |

| bit 3-2      | Unimplemen            | ted: Read as '    | )'              |                   |                  |                 |                  |

| bit 1-0      | WM<1:0>: TE           | BLWT Operatior    | with 16-Bit Da  | ata Bus Width S   | elect bits       |                 |                  |

|              | 1x = Word W           | /rite mode: TAE   | BLAT word out   | put; WRH is act   | ive when TABL    | LAT is written  |                  |

|              |                       |                   |                 | pied on both MS   |                  |                 |                  |

|              | 00 = Byte W           | rite mode: TAB    | LAT data is co  | pied on both MS   | SB and LSB; V    | VRH or WRL wi   | ill activate     |

|              | l la incalana anta da | un C.4 min devile |                 |                   | ,                |                 |                  |

Note 1: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

| TABLE 12-9:           | PORTE F             |         |     |      | , ´                                                                                                                                              |  |  |  |

|-----------------------|---------------------|---------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name              | Function            | Setting | I/O | Туре | Description                                                                                                                                      |  |  |  |

| RE2/CS/P2B/           | RE2                 | 0       | 0   | DIG  | LATE<2> data output.                                                                                                                             |  |  |  |

| CCP10/AD10            |                     | 1       | Ι   | ST   | PORTE<2> data input.                                                                                                                             |  |  |  |

|                       | CS                  | x       | Ι   | TTL  | Parallel Slave Port chip select.                                                                                                                 |  |  |  |

|                       | P2B                 | 0       | 0   | —    | ECCP2 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown events                                                       |  |  |  |

|                       | CCP10               | 1       | I/O | ST   | Capture 10 input/Compare 10 output/PWM10 output.                                                                                                 |  |  |  |

|                       | AD10 <sup>(2)</sup> | x       | 0   | DIG  | External memory interface, Address/Data Bit 10 output.                                                                                           |  |  |  |

|                       |                     | x       | -   | TTL  | External memory interface, Data Bit 10 input.                                                                                                    |  |  |  |

| RE3/P3C/              | RE3                 | 0       | 0   | DIG  | LATE<3> data output.                                                                                                                             |  |  |  |

| CCP9/REFO/            |                     | 1       | Ι   | ST   | PORTE<3> data input.                                                                                                                             |  |  |  |

| AD11                  | P3C                 | 0       | 0   | —    | ECCP3 PWM Output C.     May be configured for tri-state during Enhanced PWM shutdown  DIG CCP9 Compare/PWM output: takes priority over port data |  |  |  |

|                       | CCP9                | 0       | 0   | DIG  | CCP9 Compare/PWM output; takes priority over port data.                                                                                          |  |  |  |

|                       |                     | 1       | Ι   | ST   | CCP9 capture input.                                                                                                                              |  |  |  |

|                       | REFO                | x       | 0   | DIG  | Reference output clock.                                                                                                                          |  |  |  |

|                       | AD11 <sup>(2)</sup> | х       | 0   | DIG  | External memory interface, Address/Data Bit 11 output.                                                                                           |  |  |  |

|                       |                     | x       | Ι   | TTL  | External memory interface, Data Bit 11 input.                                                                                                    |  |  |  |

| RE4/P3B/<br>CCP8/AD12 | RE4                 | 0       | 0   | DIG  | LATE<4> data output.                                                                                                                             |  |  |  |

|                       |                     | 1       | Ι   | ST   | PORTE<4> data input.                                                                                                                             |  |  |  |

|                       | P3B                 | 0       | 0   | —    | ECCP3 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown events                                                       |  |  |  |

|                       | CCP8                | 0       | 0   | DIG  | CCP8 compare/PWM output; takes priority over port data.                                                                                          |  |  |  |

|                       |                     | 1       | I   | ST   | CCP8 capture input.                                                                                                                              |  |  |  |

|                       | AD12 <sup>(2)</sup> | x       | 0   | DIG  | External memory interface, Address/Data Bit 12 output.                                                                                           |  |  |  |

|                       |                     | x       | I   | TTL  | External memory interface, Data Bit 12 input.                                                                                                    |  |  |  |

| RE5/P1C/              | RE5                 | 0       | 0   | DIG  | LATE<5> data output.                                                                                                                             |  |  |  |

| CCP7/AD13             |                     | 1       | Ι   | ST   | PORTE<5> data input.                                                                                                                             |  |  |  |

|                       | P1C                 | 0       | 0   | —    | ECCP1 PWM Output C.<br>May be configured for tri-state during Enhanced PWM shutdown events                                                       |  |  |  |

|                       | CCP7                | 0       | 0   | DIG  | CCP7 compare/PWM output; takes priority over port data.                                                                                          |  |  |  |

|                       |                     | 1       | I   | ST   | CCP7 capture input.                                                                                                                              |  |  |  |

|                       | AD13 <sup>(2)</sup> | x       | 0   | DIG  | External memory interface, Address/Data Bit 13 output.                                                                                           |  |  |  |

|                       |                     | x       | 1   | TTL  | External memory interface, Data Bit 13 input.                                                                                                    |  |  |  |

| RE6/P1B/              | RE6                 | 0       | 0   | DIG  | LATE<6> data output.                                                                                                                             |  |  |  |

| CCP6/AD14             |                     | 1       | Ι   | ST   | PORTE<6> data input.                                                                                                                             |  |  |  |

|                       | P1B                 | 0       | 0   | —    | ECCP1 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown event                                                        |  |  |  |

|                       | CCP6                | 0       | 0   | DIG  | CCP6 compare/PWM output; takes priority over port data.                                                                                          |  |  |  |

|                       |                     | 1       | I   | ST   | CCP9 capture input.                                                                                                                              |  |  |  |

|                       | AD14 <sup>(2)</sup> | x       | 0   | DIG  | External memory interface, Address/Data Bit 14 output.                                                                                           |  |  |  |

|                       |                     | x       |     | TTL  | External memory interface, Data Bit 14 input.                                                                                                    |  |  |  |

#### TABLE 12-9: PORTE FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared and in Microcontroller mode.

2: This feature is only available on PIC18F8XKXX devices.

### 13.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-two increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (for example, CLRF TMR0, MOVWF TMR0, BSF TMR0) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 13.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 13.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| TABLE 13-1. REGISTERS ASSOCIATED WITH HIMLERD | TABLE 13-1: | REGISTERS ASSOCIATED WITH TIMER0 |

|-----------------------------------------------|-------------|----------------------------------|

|-----------------------------------------------|-------------|----------------------------------|

| Name   | Bit 7                    | Bit 6                     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |

|--------|--------------------------|---------------------------|--------|--------|-------|--------|--------|-------|--|

| TMR0L  | Timer0 Register Low Byte |                           |        |        |       |        |        |       |  |

| TMR0H  | Timer0 Regis             | Timer0 Register High Byte |        |        |       |        |        |       |  |

| INTCON | GIE/GIEH                 | PEIE/GIEL                 | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |  |

| TOCON  | TMR0ON                   | T08BIT                    | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 |  |

|        | · •                      |                           |        |        |       | •      |        |       |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

## REGISTER 18-17: ALRMHR: ALARM HOURS VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 5-4 | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|---------|------------------------------------------------------------------|

|         | Contains a value from 0 to 2.                                    |

| bit 3-0 | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 18-18: ALRMMIN: ALARM MINUTES VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|-------|----------------------------|

- bit 6-4 **MINTEN<2:0>:** Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5.

- bit 3-0 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits Contains a value from 0 to 9.

#### REGISTER 18-19: ALRMSEC: ALARM SECONDS VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:                       |                                                                     |                  |                        |                    |  |  |

|-------------------------------|---------------------------------------------------------------------|------------------|------------------------|--------------------|--|--|

| R = Reada                     | able bit                                                            | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |  |

| -n = Value                    | n = Value at POR '1' = Bit is set                                   |                  | '0' = Bit is cleared   | x = Bit is unknown |  |  |

| bit 7                         | 7 Unimplemented: Read as '0'                                        |                  |                        |                    |  |  |

|                               | •                                                                   | •                |                        |                    |  |  |

| bit 6-4                       | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |                  |                        |                    |  |  |

| Contains a value from 0 to 5. |                                                                     |                  |                        |                    |  |  |

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9.

#### 18.2.4 LEAP YEAR

Since the year range on the RTCC module is 2000 to 2099, the leap year calculation is determined by any year divisible by four in the above range. Only February is affected in a leap year.

February will have 29 days in a leap year and 28 days in any other year.

#### 18.2.5 GENERAL FUNCTIONALITY

All Timer registers containing a time value of seconds or greater are writable. The user configures the time by writing the required year, month, day, hour, minutes and seconds to the Timer registers, via register pointers. (See Section 18.2.8 "Register Mapping".)

The timer uses the newly written values and proceeds with the count from the required starting point.

The RTCC is enabled by setting the RTCEN bit (RTCCFG<7>). If enabled, while adjusting these registers, the timer still continues to increment. However, any time the MINSEC register is written to, both of the timer prescalers are reset to '0'. This allows fraction of a second synchronization.

The Timer registers are updated in the same cycle as the write instruction's execution by the CPU. The user must ensure that when RTCEN = 1, the updated registers will not be incremented at the same time. This can be accomplished in several ways:

- By checking the RTCSYNC bit (RTCCFG<4>)

- By checking the preceding digits from which a carry can occur

- By updating the registers immediately following the seconds pulse (or an alarm interrupt)

The user has visibility to the half-second field of the counter. This value is read-only and can be reset only by writing to the lower half of the SECONDS register.

#### 18.2.6 SAFETY WINDOW FOR REGISTER READS AND WRITES

The RTCSYNC bit indicates a time window during which the RTCC Clock Domain registers can be safely read and written without concern about a rollover. When RTCSYNC = 0, the registers can be safely accessed by the CPU.

Whether RTCSYNC = 1 or 0, the user should employ a firmware solution to ensure that the data read did not fall on a rollover boundary, resulting in an invalid or partial read. This firmware solution would consist of reading each register twice and then comparing the two values. If the two values matched, then a rollover did not occur.

### 18.2.7 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RTCCFG<5>) must be set.

To avoid accidental writes to the RTCC Timer register, it is recommended that the RTCWREN bit (RTCCFG<5>) be kept clear when not writing to the register. For the RTCWREN bit to be set, there is only one instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN. For that reason, it is recommended that users follow the code example in Example 18-1.

## EXAMPLE 18-1: SETTING THE RTCWREN BIT

| movlw | 0x55            |  |

|-------|-----------------|--|

| movwf | EECON2          |  |

| movlw | 0xAA            |  |

| movwf | EECON2          |  |

| bsf   | RTCCFG, RTCWREN |  |

#### 18.2.8 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Timer registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTRx bits (RTCCFG<1:0>) to select the required Timer register pair.

By reading or writing to the RTCVALH register, the RTCC Pointer value (RTCPTR<1:0>) decrements by '1' until it reaches '00'. When '00' is reached, the MINUTES and SECONDS value is accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 18-3: RTCVALH AND RTCVALL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |         |  |  |  |

|-------------|----------------------------|---------|--|--|--|

| KICFIK(I.0> | RTCVALH                    | RTCVALL |  |  |  |

| 00          | MINUTES                    | SECONDS |  |  |  |

| 01          | WEEKDAY                    | HOURS   |  |  |  |

| 10          | MONTH                      | DAY     |  |  |  |

| 11          | —                          | YEAR    |  |  |  |

The Alarm Value register windows (ALRMVALH and ALRMVALL) use the ALRMPTR bits (ALRMCFG<1:0>) to select the desired alarm register pair.

By reading or writing to the ALRMVALH register, the Alarm Pointer value, ALRMPTR<1:0>, decrements by one until it reaches '00'. When it reaches '00', the ALRMMIN and ALRMSEC values are accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

#### 21.4.3.2 Address Masking Modes

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which greatly expands the number of addresses Acknowledged.

The  $l^2C$  slave behaves the same way whether address masking is used or not. However, when address masking is used, the  $l^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking the SSPxBUF.

The PIC18F87K22 family of devices is capable of using two different Address Masking modes in  $I^2C$  slave operation: 5-Bit Address Masking and 7-Bit Address Masking. The Masking mode is selected at device configuration using the MSSPMSK Configuration bit. The default device configuration is 7-Bit Address Masking.

Both Masking modes, in turn, support address masking of 7-bit and 10-bit addresses. The combination of Masking modes and addresses provides different ranges of Acknowledgable addresses for each combination.

While both Masking modes function in roughly the same manner, the way they use address masks are different.

#### 21.4.3.3 5-Bit Address Masking Mode

As the name implies, 5-Bit Address Masking mode uses an address mask of up to 5 bits to create a range of addresses to be Acknowledged, using bits, 5 through 1, of the incoming address. This allows the module to Acknowledge up to 31 addresses when using 7-bit addressing, or 63 addresses with 10-bit addressing (see Example 21-2). This Masking mode is selected when the MSSPMSK Configuration bit is programmed ('0').

The address mask in this mode is stored in the SSPxCON2 register, which stops functioning as a control register in I<sup>2</sup>C Slave mode (Register 21-6). In 7-Bit Address Masking mode, address mask bits, ADMSK<5:1> (SSPxCON2<5:1>), mask the corresponding address bits in the SSPxADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Address Masking mode, bits, ADMSK<5:2>, mask the corresponding address bits in the SSPxADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPxADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SPxADD<n> = x). Also note, that although in 10-Bit Address Masking mode, the upper address bits reuse part of the SSPxADD register bits. The address mask bits do not interact with those bits; they only affect the lower address bits.

- Note 1: ADMSK1 masks the two Least Significant bits of the address.

- The two Most Significant bits of the address are not affected by address masking.

#### EXAMPLE 21-2: ADDRESS MASKING EXAMPLES IN 5-BIT MASKING MODE

#### 7-Bit Addressing:

SSPxADD<7:1>= A0h (1010000) (SSPxADD<0> is assumed to be '0')

#### ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### **10-Bit Addressing:**

SSPxADD<7:0> = A0h (10100000) (The two MSb of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

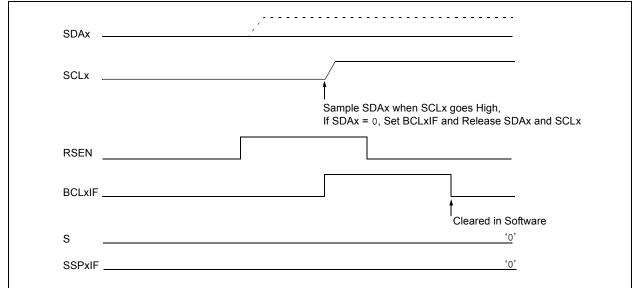

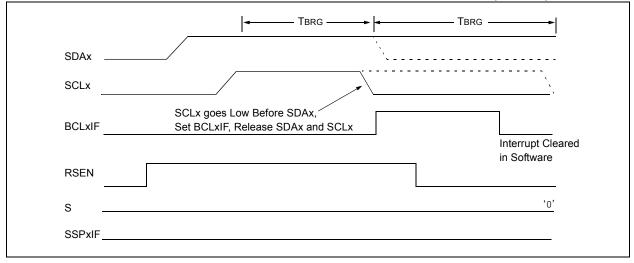

## 21.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDAx when SCLx goes from a low level to a high level.

- b) SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to 0. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 21-31). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 21-32).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

#### FIGURE 21-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 21-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

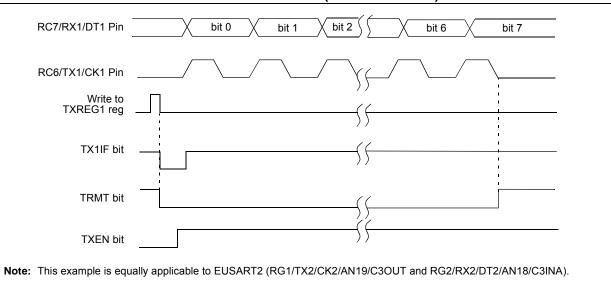

| FIGURE 22-12: STNCHRONOUS IRANSMISSION (INROUGH IAEN) | FIGURE 22-12: | SYNCHRONOUS TRANSMISSION (THROUGH TXEN) |

|-------------------------------------------------------|---------------|-----------------------------------------|

|-------------------------------------------------------|---------------|-----------------------------------------|

| Name     | Bit 7                     | Bit 6         | Bit 5         | Bit 4         | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|----------|---------------------------|---------------|---------------|---------------|---------|---------|--------|--------|

| INTCON   | GIE/GIEH                  | PEIE/GIEL     | TMR0IE        | INT0IE        | RBIE    | TMR0IF  | INT0IF | RBIF   |

| PIR1     | PSPIF                     | ADIF          | RC1IF         | TX1IF         | SSP1IF  | TMR1GIF | TMR2IF | TMR1IF |

| PIE1     | PSPIE                     | ADIE          | RC1IE         | TX1IE         | SSP1IE  | TMR1GIE | TMR2IE | TMR1IE |

| IPR1     | PSPIP                     | ADIP          | RC1IP         | TX1IP         | SSP1IP  | TMR1GIP | TMR2IP | TMR1IP |

| PIR3     | TMR5GIF                   |               | RC2IF         | TX2IF         | CTMUIF  | CCP2IF  | CCP1IF | RTCCIF |

| PIE3     | TMR5GIE                   |               | RC2IE         | TX2IE         | CTMUIE  | CCP2IE  | CCP1IE | RTCCIE |

| IPR3     | TMR5GIP                   | _             | RC2IP         | TX2IP         | CTMUIP  | CCP2IP  | CCP1IP | RTCCIP |

| RCSTA1   | SPEN                      | RX9           | SREN          | CREN          | ADDEN   | FERR    | OERR   | RX9D   |

| TXREG1   | EUSART1 Transmit Register |               |               |               |         |         |        |        |

| TXSTA1   | CSRC                      | TX9           | TXEN          | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |

| BAUDCON1 | ABDOVF                    | RCIDL         | RXDTP         | TXCKP         | BRG16   | _       | WUE    | ABDEN  |

| SPBRGH1  | EUSART1 E                 | aud Rate Ge   | nerator Regis | ster High Byt | е       |         |        |        |

| SPBRG1   | EUSART1 E                 | aud Rate Ge   | nerator Regis | ster          |         |         |        |        |

| RCSTA2   | SPEN                      | RX9           | SREN          | CREN          | ADDEN   | FERR    | OERR   | RX9D   |

| TXREG2   | EUSART2 T                 | ransmit Regis | ster          |               |         |         |        |        |

| TXSTA2   | CSRC                      | TX9           | TXEN          | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |

| BAUDCON2 | ABDOVF                    | RCIDL         | RXDTP         | TXCKP         | BRG16   | _       | WUE    | ABDEN  |

| SPBRGH2  | EUSART2 E                 | aud Rate Ge   | nerator Regis | ster High Byt | e       |         |        |        |

| SPBRG2   | EUSART2 E                 | aud Rate Ge   | nerator Regis | ster          |         |         |        |        |

| ODCON3   | U2OD                      | U10D          | _             |               |         | _       |        | CTMUDS |

| PMD0     | CCP3MD                    | CCP2MD        | CCP1MD        | UART2MD       | UART1MD | SSP2MD  | SSP1MD | ADCMD  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

#### **REGISTER 23-4:** ADRESH: A/D RESULT HIGH BYTE REGISTER, LEFT JUSTIFIED (ADFM = 0)

| R/W-x   | R/W-x   | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| ADRES11 | ADRES10 | ADRES9 | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 |

| bit 7   |         |        |        |        |        |        | bit 0  |

|         |         |        |        |        |        |        |        |

| Legend: |         |        |        |        |        |        |        |

| Logona.           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | d as '0'           |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

|                   |                                                     |                      |                    |

bit 7-0 ADRES<11:4>: A/D Result High Byte bits

#### **REGISTER 23-5:** ADRESL: A/D RESULT HIGH BYTE REGISTER, LEFT JUSTIFIED (ADFM = 0)

| R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|--------|--------|--------|-------|-------|-------|-------|

| ADRES3 | ADRES2 | ADRES1 | ADRES0 | ADSGN | ADSGN | ADSGN | ADSGN |

| bit 7  |        |        |        |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-4 ADRES<3:0>: A/D Result Low Byte bits

bit 3-0 ADSGN: A/D Result Sign bit

1 = A/D result is negative

0 = A/D result is positive

| TADLE 23-2:          | REGISTERS ASSOCIATED WITH A/D MODULE |                       |                    |         |         |         |               |         |

|----------------------|--------------------------------------|-----------------------|--------------------|---------|---------|---------|---------------|---------|

| Name                 | Bit 7                                | Bit 6                 | Bit 5              | Bit 4   | Bit 3   | Bit 2   | Bit 1         | Bit 0   |

| INTCON               | GIE/GIEH                             | PEIE/GIEL             | TMR0IE             | INT0IE  | RBIE    | TMR0IF  | <b>INT0IF</b> | RBIF    |

| PIR1                 | PSPIF                                | ADIF                  | RC1IF              | TX1IF   | SSP1IF  | TMR1GIF | TMR2IF        | TMR1IF  |

| PIE1                 | PSPIE                                | ADIE                  | RC1IE              | TX1IE   | SSP1IE  | TMR1GIE | TMR2IE        | TMR1IE  |

| IPR1                 | PSPIP                                | ADIP                  | RC1IP              | TX1IP   | SSP1IP  | TMR1GIP | TMR2IP        | TMR1IP  |

| PIR3                 | TMR5GIF                              | _                     | RC2IF              | TX2IF   | CTMUIF  | CCP2IF  | CCP1IF        | RTCCIF  |

| PIE3                 | TMR5GIE                              | _                     | RC2IE              | TX2IE   | CTMUIE  | CCP2IE  | CCP1IE        | RTCCIE  |

| IPR3                 | TMR5GIP                              | _                     | RC2IP              | TX2IP   | CTMUIP  | CCP2IP  | CCP1IP        | RTCCIP  |

| ADRESH               | A/D Result                           | Register Higl         | n Byte             |         |         |         |               |         |

| ADRESL               | A/D Result                           | Register Low          | <sup>,</sup> Byte  |         |         |         |               |         |

| ADCON0               | _                                    | CHS4                  | CHS3               | CHS2    | CHS1    | CHS0    | GO/DONE       | ADON    |

| ADCON1               | TRIGSEL1                             | TRIGSEL0              | VCFG1              | VCFG0   | VNCFG   | CHSN2   | CHSN1         | CHSN0   |

| ADCON2               | ADFM                                 | _                     | ACQT2              | ACQT1   | ACQT0   | ADCS2   | ADCS1         | ADCS0   |

| ANCON0               | ANSEL7                               | ANSEL6                | ANSEL5             | ANSEL4  | ANSEL3  | ANSEL2  | ANSEL1        | ANSEL0  |

| ANCON1               | ANSEL15                              | ANSEL14               | ANSEL13            | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9        | ANSEL8  |

| ANCON2               | ANSEL23                              | ANSEL22               | ANSEL21            | ANSEL20 | ANSEL19 | ANSEL18 | ANSEL17       | ANSEL16 |

| CCP2CON              | P2M1                                 | P2M0                  | DC2B1              | DC2B0   | CCP2M3  | CCP2M2  | CCP2M1        | CCP2M0  |

| PORTA                | RA7 <sup>(2)</sup>                   | RA6 <sup>(2)</sup>    | RA5                | RA4     | RA3     | RA2     | RA1           | RA0     |

| TRISA                | TRISA7 <sup>(2)</sup>                | TRISA6 <sup>(2)</sup> | TRISA5             | TRISA4  | TRISA3  | TRISA2  | TRISA1        | TRISA0  |

| PORTF                | RF7                                  | RF6                   | RF5                | RF4     | RF3     | RF2     | RF1           | —       |

| TRISF                | TRISF7                               | TRISF6                | TRISF5             | TRISF4  | TRISF3  | TRISF2  | TRISF1        | —       |

| PORTG                | _                                    | _                     | RG5 <sup>(3)</sup> | RG4     | RG3     | RG2     | RG1           | RG0     |

| TRISG                |                                      |                       |                    | TRISG4  | TRISG3  | TRISG2  | TRISG1        | TRISG0  |

| PORTH <sup>(1)</sup> | RH7                                  | RH6                   | RH5                | RH4     | RH3     | RH2     | RH1           | RH0     |

| TRISH <sup>(1)</sup> | TRISH7                               | TRISH6                | TRISH5             | TRISH4  | TRISH3  | TRISH2  | TRISH1        | TRISH0  |

| PMD0                 | CCP3MD                               | CCP2MD                | CCP1MD             | UART2MD | UART1MD | SSP2MD  | SSP1MD        | ADCMD   |

|                      |                                      | wheel weed on         |                    |         |         |         |               |         |

#### TABLE 23-2: REGISTERS ASSOCIATED WITH A/D MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: This register is not implemented on 64-pin devices.

**2:** These bits are available only in certain oscillator modes, when the FOSC2 Configuration bit = 0. If that Configuration bit is cleared, this signal is not implemented.

**3:** This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented.

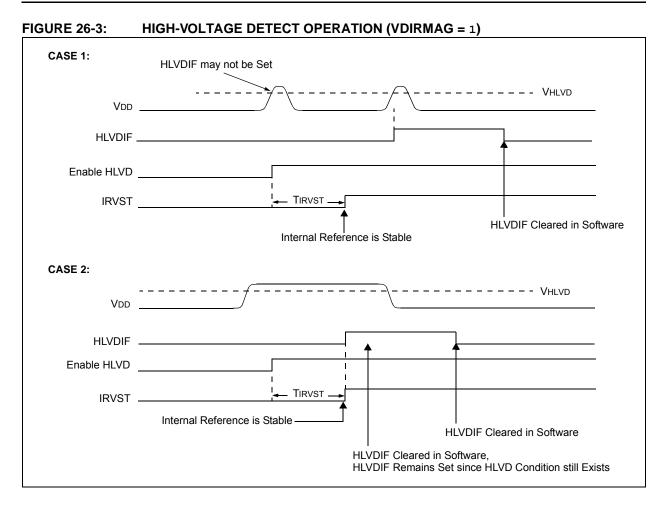

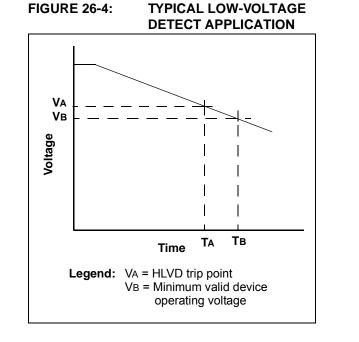

#### 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an Interrupt Service Routine (ISR), which would allow the application to perform "housekeeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

### EXAMPLE 27-1: SETUP FOR CTMU CALIBRATION ROUTINES

```

#include "pl8cxxx.h"

void setup(void)

{ //CTMUCON - CTMU Control register

CTMUCONH = 0 \times 00;

//make sure CTMU is disabled

CTMUCONL = 0X90;

//CTMU continues to run when emulator is stopped,CTMU continues

//to run in idle mode, Time Generation mode disabled, Edges are blocked

//No edge sequence order, Analog current source not grounded, trigger

//output disabled, Edge2 polarity = positive level, Edge2 source =

//source 0, Edgel polarity = positive level, Edgel source = source 0,

// Set Edge status bits to zero

//CTMUICON - CTMU Current Control Register

CTMUICON = 0 \times 01;

//0.55uA, Nominal - No Adjustment

//Setup AD converter;

TRISA=0x04;

//set channel 2 as an input

// Configured AN2 as an analog channel

// ANCONO

ANCON0 = 0 \times 04;

// ANCON1

ANCON1 = 0 XE0;

// ADCON2

// Resulst format 1= Right justified

ADCON2bits.ADFM=1;

// Acquition time 7 = 20TAD 2 = 4TAD 1=2TAD

ADCON2bits.ACQT=1;

ADCON2bits.ADCS=2;

// Clock conversion bits 6= FOSC/64 2=FOSC/32

// ADCON0

// Vref+ = AVdd

ADCON1bits.VCFG0 =0;

// Vref+ = AVdd

ADCON0bits.VCFG1 =0;

ADCON0bits.VCFG = 0;

// Vref- = AVss

ADCON0bits.CHS=2;

// Select ADC channel

// Turn on ADC

ADCON0bits.ADON=1;

}

```

## REGISTER 28-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| U-0   | R/P-1 | U-0 | R/P-1    | R/P-1    | R/P-1     | U-0 | R/P-1 |

|-------|-------|-----|----------|----------|-----------|-----|-------|

| —     | XINST | _   | SOSCSEL1 | SOSCSEL0 | INTOSCSEL | _   | RETEN |

| bit 7 |       |     |          |          |           |     | bit 0 |

| Legend:           | P = Programmable bit |                       |                    |

|-------------------|----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | XINST: Extended Instruction Set Enable bit                                                                                                                                                                                |

|         | <ul> <li>1 = Instruction set extension and Indexed Addressing mode are enabled</li> <li>0 = Instruction set extension and Indexed Addressing mode are disabled (Legacy mode)</li> </ul>                                   |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 4-3 | SOSCSEL<1:0>: SOSC Power Selection and Mode Configuration bits                                                                                                                                                            |

|         | <ul> <li>11 = High-power SOSC circuit is selected</li> <li>10 = Digital (SCLKI) mode; I/O port functionality of RC0 and RC1 is enabled</li> <li>01 = Low-power SOSC circuit is selected</li> <li>00 = Reserved</li> </ul> |

| bit 2   | INTOSCSEL: LF-INTOSC Low-power Enable bit                                                                                                                                                                                 |

|         | <ul> <li>1 = LF-INTOSC is in High-Power mode during Sleep</li> <li>0 = LF-INTOSC is in Low-Power mode during Sleep</li> </ul>                                                                                             |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 0   | RETEN: VREG Sleep Enable bit                                                                                                                                                                                              |

|         | 1 = Regulator power while in Sleep mode is controlled by VREGSLP (WDTCON<7>)<br>0 = Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-pow                                                |

= Regulator power while in Sleep mode is controlled by SRETEN (WDTCON<4>). Ultra low-power regulator is enabled.

## 28.6 Program Verification and Code Protection

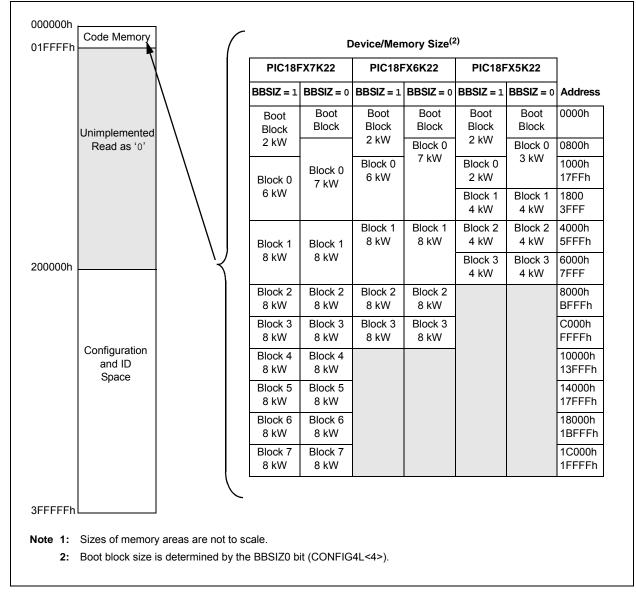

The user program memory is divided into four blocks for the PIC18FX5K22 and PIC18FX6K22 devices, and eight blocks for PIC18FX7K22 devices. One of these is a boot block of 1 or 2 Kbytes. The remainder of the memory is divided into blocks on binary boundaries. Each of the blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPx)

- Write-Protect bit (WRTx)

- External Block Table Read bit (EBTRx)

Figure 28-6 shows the program memory organization for 48, 64, 96 and 128 Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 28-4.

## FIGURE 28-6: CODE-PROTECTED PROGRAM MEMORY FOR THE PIC18F87K22 FAMILY<sup>(1)</sup>

| Param.<br>No. | Symbol    | Charac           | teristic                  | Min              | Max  | Units                    | Conditions                   |

|---------------|-----------|------------------|---------------------------|------------------|------|--------------------------|------------------------------|

| 100           | Тнідн     | Clock High       | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | _                        |                              |

|               |           | Time             | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | _                        |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | _                        |                              |

| 101           | TLOW      | Clock Low Time   | 100 kHz mode              | 2(Tosc)(BRG + 1) | —    |                          |                              |

|               |           |                  | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | _                        |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | _                        |                              |

| 102           | TR        | SDAx and         | 100 kHz mode              | _                | 1000 | ns                       | CB is specified to be from   |

|               |           | SCLx Rise        | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns                       | 10 to 400 pF                 |

|               |           | Time             | 1 MHz mode <sup>(1)</sup> |                  | 300  | ns                       |                              |

| 103           | TF        | SDAx and         | 100 kHz mode              | _                | 300  | ns                       | CB is specified to be from   |

|               |           | SCLx Fall Time   | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns                       | 10 to 400 pF                 |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns                       |                              |

| 90            | TSU:STA   | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | —                        | Only relevant for Repeated   |

|               | Setup Tin | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | —                        | Start condition              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | —                        |                              |

| 91 Thd:sta    | THD:STA   | Start Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | —                        | After this period, the first |

|               | Hold Time | 400 kHz mode     | 2(Tosc)(BRG + 1)          | _                | —    | clock pulse is generated |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | —                        |                              |

| 106           | THD:DAT   | Data Input       | 100 kHz mode              | 0                | _    | ns                       |                              |

|               |           | Hold Time        | 400 kHz mode              | 0                | 0.9  | μS                       |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | _                | _    | ns                       |                              |

| 107           | TSU:DAT   | Data Input       | 100 kHz mode              | 250              |      | ns                       | (Note 2)                     |

|               |           | Setup Time       | 400 kHz mode              | 100              | _    | ns                       |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | _                | _    | ns                       |                              |

| 92            | Tsu:sto   | Stop Condition   | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | —                        |                              |

|               |           | Setup Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | —                        |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _    | —                        |                              |

| 109           | ΤΑΑ       | Output Valid     | 100 kHz mode              | _                | 3500 | ns                       |                              |

|               |           | from Clock       | 400 kHz mode              | _                | 1000 | ns                       |                              |

|               |           |                  | 1 MHz mode <sup>(1)</sup> |                  |      | ns                       |                              |

| 110           | TBUF      | Bus Free Time    | 100 kHz mode              | 4.7              |      | μS                       | Time the bus must be free    |

|               |           |                  | 400 kHz mode              | 1.3              |      | μS                       | before a new transmission    |

|               |           |                  | 1 MHz mode <sup>(1)</sup> |                  |      | μS                       | can start                    |

| D102          | Св        | Bus Capacitive L | oading                    | —                | 400  | pF                       |                              |

| TABLE 31-24: M | ISSP I <sup>2</sup> C™ BUS DATA | REQUIREMENTS |

|----------------|---------------------------------|--------------|

|----------------|---------------------------------|--------------|

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{\text{TM}}$  pins.

2: A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but Parameter #107 ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCLx signal. If such a device does stretch the LOW period of the SCLx signal, it must output the next data bit to the SDAx line, Parameter #102 + Parameter #107 = 1000 + 250 = 1250 ns (for 100 kHz mode), before the SCLx line is released.

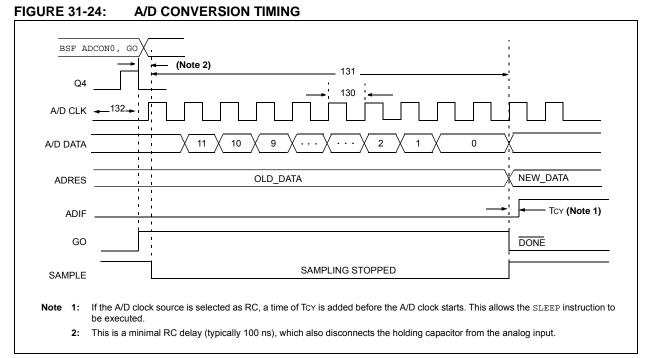

| TABLE 31-28: | A/D CONVERSION REQUIREMENTS |

|--------------|-----------------------------|

| Param<br>No. | Symbol | Characteristic                                                     | Min | Max                 | Units | Conditions                                 |

|--------------|--------|--------------------------------------------------------------------|-----|---------------------|-------|--------------------------------------------|

| 130          | Tad    | A/D Clock Period                                                   | 0.8 | 12.5 <sup>(1)</sup> | μs    | Tosc-based, VREF $\geq$ 3.0V               |

|              |        |                                                                    | 1.4 | 25 <sup>(1)</sup>   | μs    | VDD = 3.0V; TOSC-based,<br>VREF full range |

|              |        |                                                                    |     | 1                   | μs    | A/D RC mode                                |

|              |        |                                                                    |     | 3                   | μs    | VDD = 3.0V; A/D RC mode                    |

| 131          | TCNV   | Conversion Time<br>(not including acquisition time) <sup>(2)</sup> | 14  | 15                  | Tad   |                                            |

| 132          | TACQ   | Acquisition Time <sup>(3)</sup>                                    | 1.4 |                     | μs    | -40°C to +125°C                            |

| 135          | Tswc   | Switching Time from Convert $\rightarrow$ Sample                   |     | (Note 4)            |       |                                            |

| 137          | TDIS   | Discharge Time                                                     | 0.2 | —                   | μs    | -40°C to +125°C                            |

Note 1: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

2: ADRES registers may be read on the following TCY cycle.

**3:** The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD). The source impedance (Rs) on the input channels is 50 $\Omega$ .

4: On the following cycle of the device clock.

| Transition for Two-Speed Start-up                      |

|--------------------------------------------------------|

| (INTOSC to HSPLL)                                      |

| Transition for Wake from Idle to Run Mode              |

| Transition for Wake from Sleep (HSPLL)                 |

| Transition from RC_RUN Mode to                         |

| PRI_RUN Mode61                                         |

| Transition from SEC_RUN Mode to                        |

| PRI_RUN Mode (HSPLL)                                   |

| Transition to RC RUN Mode                              |

| Timing Diagrams and Specifications                     |

| Capture/Compare/PWM Requirements                       |

| CLKO and I/O Requirements                              |

| EUSART/AUSART Synchronous Receive                      |

| Requirements                                           |

| EUSART/AUSART Synchronous Transmission                 |

| Requirements                                           |

| Example SPI Mode Requirements (Master Mode,            |

| CKE = 0)                                               |

| Example SPI Mode Requirements (Master Mode,            |

| CKE = 1)515                                            |

| Example SPI Mode Requirements (Slave Mode,             |

| CKE = 0)                                               |

| Example SPI Slave Mode Requirements                    |

| (CKE = 1)517                                           |

| External Clock Requirements 503                        |

| HLVD Characteristics511                                |

| I <sup>2</sup> C Bus Data Requirements (Slave Mode)519 |

| I <sup>2</sup> C Bus Start/Stop Bits Requirements      |

| (Slave Mode)518                                        |

| Internal RC Accuracy (INTOSC) 504                      |

| MSSP I <sup>2</sup> C Bus Data Requirements521         |

| MSSP I <sup>2</sup> C Bus Start/Stop Bits Requirements |

| PLL Clock504                                           |

| Program Memory Fetch Requirements (8-bit) 506          |

| Program Memory Write Requirements508                   |

| Reset, Watchdog Timer, Oscillator Start-up             |

| Timer, Power-up Timer and Brown-out                    |

| Reset Requirements510                                  |

| Timer0 and Timer1 External Clock Requirements 512      |

| Top-of-Stack Access                                    |

| TSTFSZ                                                 |

| Two-Speed Start-up                                     |

| IESO (CONFIG1H, Internal/External Oscillator           |

| Switchover Bit406                                      |

| Two-Word Instructions                                  |

| Example Cases                                          |

| TXSTAx Register                                        |

| BRGH Bit331                                            |

## U

| Ultra Low-Power Wake-up          |     |

|----------------------------------|-----|

| Exit Delay                       | 71  |

| Overview                         | 70  |

| v                                |     |

| Voltage Reference Specifications | 500 |

## W

| ••                         |                    |

|----------------------------|--------------------|

| Watchdog Timer (WDT)       |                    |

| Associated Registers       |                    |

| Control Register           |                    |

| During Oscillator Failure  |                    |

| Programming Considerations |                    |

| WCOL                       | 315, 316, 317, 320 |

| WCOL Status Flag           | 315, 316, 317, 320 |

| WWW Address                |                    |

| WWW, On-Line Support       |                    |

| x                          |                    |

| Λ                          |                    |

|                            | 474                |

| XORLW | 471 |

|-------|-----|

| XORWF | 472 |