Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 64MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 32KB (16K x 16)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22-i-ptrsl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 64/80-Pin, High-Performance, 1-Mbit Enhanced Flash MCUs with 12-Bit A/D and nanoWatt XLP Technology

### Low-Power Features:

- · Power-Managed modes:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- · Two-Speed Oscillator Start-up

- · Fail-Safe Clock Monitor

- Power-Saving Peripheral Module Disable (PMD)

- · Ultra Low-Power Wake-up

- Fast Wake-up, 1 μs Typical

- · Low-Power WDT, 300 nA Typical

- · Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 5.5 μA, Typical

- Idle mode Currents Down to 1.7 μA Typical

- Sleep mode Currents Down to Very Low 20 nA, Typical

- RTCC Current Downs to Very Low 700 nA, Typical

### **Special Microcontroller Features:**

- · Operating Voltage Range: 1.8V to 5.5V

- · On-Chip 3.3V Regulator

- · Operating Speed up to 64 MHz

- Up to 128 Kbytes On-Chip Flash Program Memory

- · Data EEPROM of 1,024 Bytes

- 4K x 8 General Purpose Registers (SRAM)

- 10,000 Erase/Write Cycle Flash Program Memory, Minimum

- 1,000,000 Erase/write Cycle Data EEPROM Memory, Typical

- · Flash Retention: 40 Years, Minimum

- Three Internal Oscillators: LF-INTRC (31 kHz), MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

- Self-Programmable under Software Control

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- · Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s (about 70 minutes)

- In-Circuit Serial Programming™ (ICSP™) via Two Pins

- · In-Circuit Debug via Two Pins

- · Programmable:

- BOR

- LVD

|             | Program Memory   |                               | Data Memory     |                   |     | 12-Bit      | CCP/          |   | MSSP |                             |       | tors        | ب ي                | Bus      |      |      |

|-------------|------------------|-------------------------------|-----------------|-------------------|-----|-------------|---------------|---|------|-----------------------------|-------|-------------|--------------------|----------|------|------|

| Device      | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D<br>(ch) | ECCP<br>(PWM) |   | SPI  | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External | СТМО | RTCC |

| PIC18F65K22 | 32K              | 16,383                        | 2K              | 1K                | 53  | 16          | 5/3           | 2 | Υ    | Υ                           | 2     | 3           | 4/4                | N        | Υ    | Υ    |

| PIC18F66K22 | 64K              | 32,768                        | 4K              | 1K                | 53  | 16          | 7/3           | 2 | Υ    | Υ                           | 2     | 3           | 6/5                | N        | Υ    | Υ    |

| PIC18F67K22 | 128K             | 65,536                        | 4K              | 1K                | 53  | 16          | 7/3           | 2 | Υ    | Y                           | 2     | 3           | 6/5                | N        | Υ    | Υ    |

| PIC18F85K22 | 32K              | 16,383                        | 2K              | 1K                | 69  | 24          | 5/3           | 2 | Υ    | Υ                           | 2     | 3           | 4/4                | Υ        | Υ    | Υ    |

| PIC18F86K22 | 64K              | 32,768                        | 4K              | 1K                | 69  | 24          | 7/3           | 2 | Υ    | Y                           | 2     | 3           | 6/5                | Υ        | Υ    | Υ    |

| PIC18F87K22 | 128K             | 65,536                        | 4K              | 1K                | 69  | 24          | 7/3           | 2 | Υ    | Υ                           | 2     | 3           | 6/5                | Υ        | Υ    | Υ    |

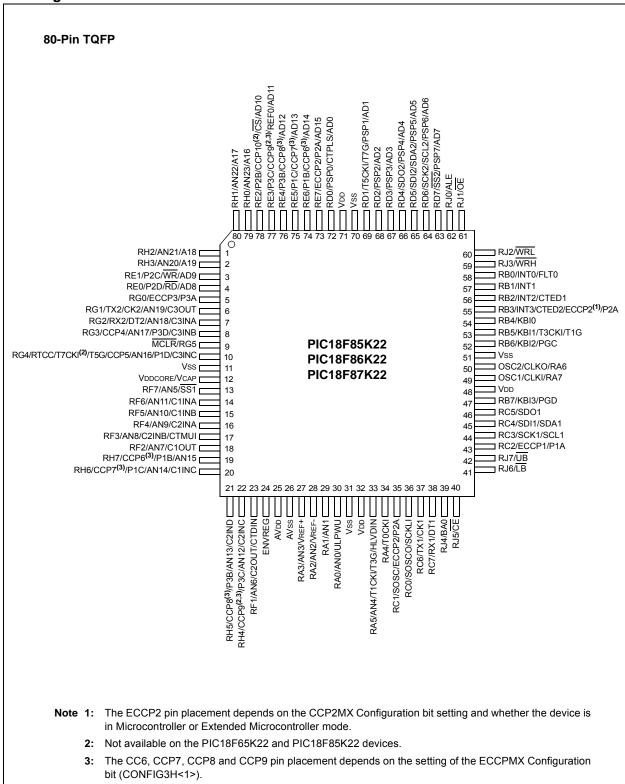

### Pin Diagrams – PIC18F8XK22

TABLE 1-4: PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                                                            | Pin Number | Pin                  | Buffer                            | Description                                                                                                           |

|-------------------------------------------------------------------------------------|------------|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                            | TQFP       | Туре                 | Туре                              | Description                                                                                                           |

|                                                                                     |            |                      |                                   | PORTH is a bidirectional I/O port.                                                                                    |

| RH0/AN23/A16<br>RH0<br>AN23<br>A16                                                  | 79         | I/O<br>I<br>I/O      | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 23.<br>External Memory Address/Data 16.                                                  |

| RH1/AN22/A17<br>RH1<br>AN22<br>A17                                                  | 80         | I/O<br>I<br>I/O      | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 22.<br>External Address/Data 17.                                                         |

| RH2/AN21/A18<br>RH2<br>AN21<br>A18                                                  | 1          | I/O<br>I<br>I/O      | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 21.<br>External Address/Data 18.                                                         |

| RH3/AN20/A19<br>RH3<br>AN20<br>A19                                                  | 2          | I/O<br>I<br>I/O      | ST<br>Analog<br>TTL               | Digital I/O.<br>Analog Input 20.<br>External Address/Data 19.                                                         |

| RH4/CCP9/P3C/AN12/<br>C2INC<br>RH4<br>CCP9 <sup>(3,5)</sup><br>P3C<br>AN12<br>C2INC | 22         | I/O<br>I/O<br>O<br>I | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O. Capture 9 input/Compare 9 output/PWM9 output. ECCP3 PWM Output C. Analog Input 12. Comparator 2 Input C. |

| RH5/CCP8/P3B/AN13/<br>C2IND<br>RH5<br>CCP8 <sup>(5)</sup><br>P3B<br>AN13<br>C2IND   | 21         | I/O<br>I/O<br>O<br>I | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O. Capture 8 input/Compare 8 output/PWM8 output. ECCP3 PWM Output B. Analog Input 13. Comparator 1 Input D. |

| RH6/CCP7/P1C/AN14/<br>C1INC<br>RH6<br>CCP7 <sup>(5)</sup><br>P1C<br>AN14<br>C1INC   | 20         | I/O<br>I/O<br>O<br>I | ST<br>ST<br>—<br>Analog<br>Analog | Digital I/O. Capture 7 input/Compare 7 output/PWM7 output. ECCP1 PWM Output C. Analog Input 14. Comparator 1 Input C. |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

I = Input

O = Output

OD = Open-Drain (no P diode to VDD)

P = Power  $I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

- **2:** Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

- 3: Not available on PIC18F65K22 and PIC18F85K22 devices.

- 4: PSP is available only in Microcontroller mode.

- 5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

### 4.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable. The HF-INTOSC and MF-INTOSC are termed as INTOSC in this chapter.

Three bits indicate the current clock source and its status, as shown in Table 4-2. The three bits are:

- OSTS (OSCCON<3>)

- HFIOFS (OSCCON<2>)

- SOSCRUN (OSCCON2<6>)

TABLE 4-2: SYSTEM CLOCK INDICATOR

| Main Clock Source                                    | osts | HFIOFS or MFIOFS | SOSCRUN |

|------------------------------------------------------|------|------------------|---------|

| Primary Oscillator                                   | 1    | 0                | 0       |

| INTOSC (HF-INTOSC or MF-INTOSC)                      | 0    | 1                | 0       |

| Secondary Oscillator                                 | 0    | 0                | 1       |

| MF-INTOSC or<br>HF-INTOSC as Primary<br>Clock Source | 1    | 1                | 0       |

| LF-INTOSC is Running or INTOSC is Not Yet Stable     | 0    | 0                | 0       |

When the OSTS bit is set, the primary clock is providing the device clock. When the HFIOFS or MFIOFS bit is set, the INTOSC output is providing a stable 16 MHz clock source to a divider that actually drives the device clock. When the SOSCRUN bit is set, the SOSC oscillator is providing the clock. If none of these bits are set, either the LF-INTOSC clock source is clocking the device or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC<3:0> Configuration bits (CONFIG1H<3:0>), then the OSTS and HFIOFS or MFIOFS bits can be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 16 MHz output. Entering another INTOSC power-managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. At a lower VDD, it is possible to select a higher clock speed than is supportable by that VDD. Improper device operation may result if the VDD/FOSC specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode or one of the Idle modes, depending on the setting of the IDLEN bit.

#### 4.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting.

#### 4.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

### 4.2.1 PRI RUN MODE

The PRI\_RUN mode is the normal, Full-Power Execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled. (For details, see **Section 28.4** "**Two-Speed Start-up"**.) In this mode, the OSTS bit is set. The HFIOFS or MFIOFS bit may be set if the internal oscillator block is the primary clock source. (See **Section 3.2** "Control Registers".)

### 4.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock-switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the SOSC oscillator. This enables lower power consumption while retaining a high-accuracy clock source.

SEC\_RUN mode is entered by setting the SCS<1:0> bits to '01'. The device clock source is switched to the SOSC oscillator (see Figure 4-1), the primary oscillator is shut down, the SOSCRUN bit (OSCCON2<6>) is set and the OSTS bit is cleared.

Note: The SOSC oscillator can be enabled by setting the SOSCGO bit (OSCCON2<3>). If this bit is set, the clock switch to the SEC\_RUN mode can switch immediately once SCS<1:0> are set to '01'.

On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the SOSC oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the SOSCRUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up and the SOSC oscillator continues to run.

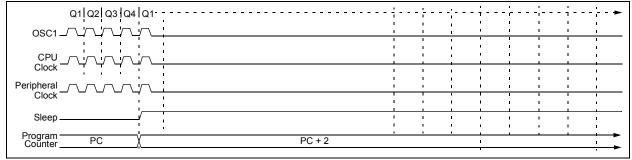

### 4.3 Sleep Mode

The power-managed Sleep mode in the PIC18F87K22 family of devices is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

Entering Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the LF-INTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

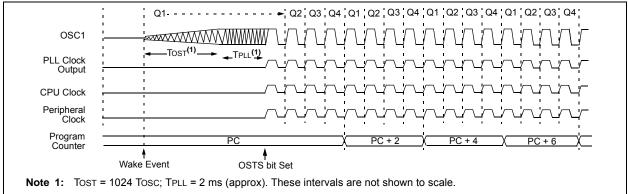

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6). Alternately, the device will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor is enabled (see **Section 28.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

#### 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits. The CPU, however, will not be clocked. The clock source status bits are not affected. This approach is a quick method to switch from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the LF-INTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TcsD (Parameter 38, Table 31-13) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or Sleep mode, a WDT timeout will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

FIGURE 4-6: TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

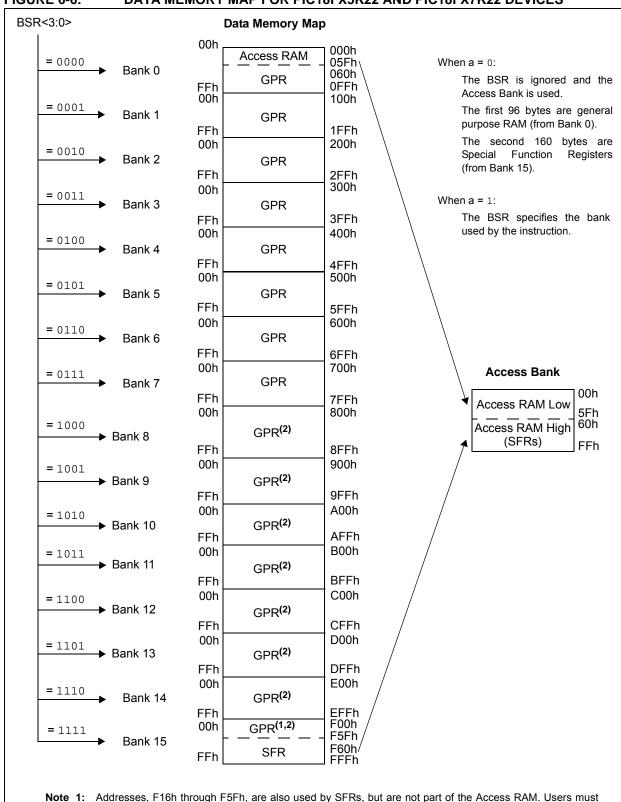

FIGURE 6-6: DATA MEMORY MAP FOR PIC18FX5K22 AND PIC18FX7K22 DEVICES

always use the complete address, or load the proper BSR value, to access these registers.

Example 10-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 10-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

# EQUATION 10-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

```

RES3:RES0 = ARG1H:ARG1L \bullet ARG2H:ARG2L

= (ARG1H \bullet ARG2H \bullet 2<sup>16</sup>) +

(ARG1H \bullet ARG2L \bullet 2<sup>8</sup>) +

(ARG1L \bullet ARG2H \bullet 2<sup>8</sup>) +

(ARG1L \bullet ARG2L)

```

### EXAMPLE 10-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

```

ARG1L,

MOVE

MULWF

ARG2L

; ARG1L * ARG2L->

; PRODH:PRODL

PRODH, RES1

MOVFF

MOVFF

PRODL, RESO

;

ARG1H, W

MOVF

; ARG1H * ARG2H->

MULWF

ARG2H

; PRODH:PRODL

MOVFF

PRODH, RES3

;

PRODL, RES2

MOVFF

;

MOVF

ARG1L, W

MULWF

ARG2H

; ARG1L * ARG2H->

; PRODH:PRODL

MOVF

PRODL, W

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC RES2, F

WREG

CLRF

ADDWFC RES3, F

ARG1H, W

MOVF

; ARG1H * ARG2L->

{\tt MULWF}

ARG2L

; PRODH:PRODL

PRODL, W

MOVF

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC RES2, F

CLRF

WREG

;

ADDWFC RES3, F

```

Example 10-4 shows the sequence to do a 16 x 16 signed multiply. Equation 10-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

# EQUATION 10-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

```

RES3:RES0= ARG1H:ARG1L • ARG2H:ARG2L

(ARG1H • ARG2H • 2<sup>16</sup>) +

(ARG1H • ARG2L • 2<sup>8</sup>) +

(ARG1L • ARG2H • 2<sup>8</sup>) +

(ARG1L • ARG2L) +

(-1 • ARG2H<7> • ARG1H:ARG1L • 2<sup>16</sup>) +

(-1 • ARG1H<7> • ARG2H:ARG2L • 2<sup>16</sup>)

```

### EXAMPLE 10-4: 16 x 16 SIGNED MULTIPLY ROUTINE

```

MOVE

ARG1L.

MULWF

ARG2L

; ARG1L * ARG2L ->

; PRODH:PRODL

MOVFF

PRODH, RES1 ;

PRODL, RESO ;

MOVEE

MOVF

ARG1H, W

ARG2H

MULWF

; ARG1H * ARG2H ->

; PRODH: PRODL

MOVFF

PRODH, RES3 ;

PRODL, RES2 ;

MOVFF

MOVE

ARG1L, W

ARG2H

; ARG1L * ARG2H ->

MULWF

; PRODH: PRODI.

MOVF

PRODL, W

RES1, F

ADDWF

; Add cross

MOVF

PRODH, W

; products

ADDWFC

RES2, F

CLRF

WREG

ADDWFC

RES3, F

ARG1H, W

MOVF

MULWF

ARG2L

; ARG1H * ARG2L ->

; PRODH:PRODL

MOVE

PRODL, W

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC

RES2, F

CLRF

WREG

ADDWFC

RES3, F

ARG2H, 7

; ARG2H:ARG2L neg?

BTFSS

SIGN_ARG1

; no, check ARG1

BRA

MOVF

ARG1L, W

SUBWF

RES2

MOVF

ARG1H, W

; SIGN ARG1

SUBWFB

RES3

BTFSS

ARG1H, 7

; ARG1H:ARG1L neg?

CONT_CODE

; no, done

BRA

MOVE

ARG2L, W

SUBWE

RES2

MOVF

ARG2H, W

SUBWFB

RES3

CONT_CODE

:

```

#### REGISTER 11-17: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| R/W-1  | 1 U-0 R/W-1 |        | R/W-1  | R/W-1  | R/W-1 R/W-1 |        | R/W-1   |

|--------|-------------|--------|--------|--------|-------------|--------|---------|

| OSCFIP | _           | SSP2IP | BCL2IP | BCL1IP | HLVDIP      | TMR3IP | TMR3GIP |

| bit 7  |             |        |        |        |             |        | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIP: Oscillator Fail Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 **Unimplemented:** Read as '0'

bit 5 SSP2IP: Master Synchronous Serial Port 2 Interrupt Priority bit

1 = High priority0 = Low priority

bit 4 BCL2IP: Bus Collision Interrupt priority bit (MSSP)

1 = High priority0 = Low priority

bit 3 **BCL1IP:** Bus Collision Interrupt Priority bit

1 = High priority0 = Low priority

bit 2 HLVDIP: High/Low-Voltage Detect Interrupt Priority bit

1 = High priority0 = Low priority

bit 1 TMR3IP: TMR3 Overflow Interrupt Priority bit

1 = High priority0 = Low priority

bit 0 TMR3GIP: TMR3 Gate Interrupt Priority bit

1 = High priority0 = Low priority

### REGISTER 12-5: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|---------|-----|-----|-----|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | _   | _   | _     |

| bit 7 |     |       |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 IBF: Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 **OBF:** Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 **IBOV:** Input Buffer Overflow Detect bit

1 = A write occurred when a previously input word had not been read (must be cleared in software)

0 = No overflow occurred

bit 4 **PSPMODE:** Parallel Slave Port Mode Select bit

1 = Parallel Slave Port mode0 = General Purpose I/O mode

bit 3-0 **Unimplemented:** Read as '0'

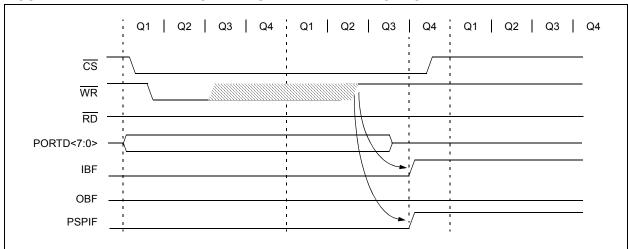

#### FIGURE 12-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

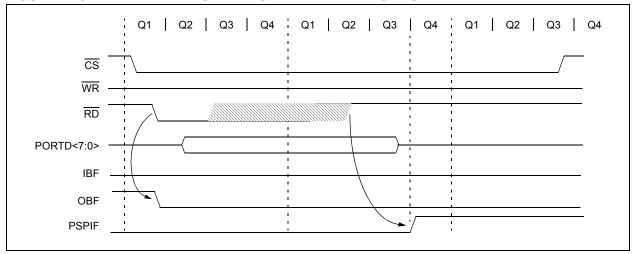

FIGURE 12-5: PARALLEL SLAVE PORT READ WAVEFORMS

TABLE 12-19: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4   | Bit 3  | Bit 2   | Bit 1  | Bit 0  |

|--------|----------|-----------|--------|---------|--------|---------|--------|--------|

| PORTD  | RD7      | RD6       | RD5    | RD4     | RD3    | RD2     | RD1    | RD0    |

| LATD   | LATD7    | LATD6     | LATD5  | LATD4   | LATD3  | LATD2   | LATD1  | LATD0  |

| TRISD  | TRISD7   | TRISD6    | TRISD5 | TRISD4  | TRISD3 | TRISD2  | TRISD1 | TRISD0 |

| PORTE  | RE7      | RE6       | RE5    | RE4     | RE3    | RE2     | RE1    | RE0    |

| LATE   | LATE7    | LATE6     | LATE5  | LATE4   | LATE3  | LATE2   | LATE1  | LATE0  |

| TRISE  | TRISE7   | TRISE6    | TRISE5 | TRISE4  | TRISE3 | TRISE2  | TRISE1 | TRISE0 |

| PSPCON | IBF      | OBF       | IBOV   | PSPMODE | _      | _       | _      | _      |

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE  | RBIE   | TMR0IF  | INT0IF | RBIF   |

| PIR1   | PSPIF    | ADIF      | RC1IF  | TX1IF   | SSP1IF | TMR1GIF | TMR2IF | TMR1IF |

| PIE1   | PSPIE    | ADIE      | RC1IE  | TX1IE   | SSP1IE | TMR1GIE | TMR2IE | TMR1IE |

| IPR1   | PSPIP    | ADIP      | RC1IP  | TX1IP   | SSP1IP | TMR1GIP | TMR2IP | TMR1IP |

| PMD1   | PSPMD    | CTMUMD    | RTCCMD | TMR4MD  | TMR3MD | TMR2MD  | TMR1MD | EMBDM  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

The Lower Drive Level mode is highly optimized for extremely low-power consumption. It is not intended to drive all types of 32.768 kHz crystals. In the Low Drive Level mode, the crystal oscillator circuit may not work correctly if excessively large discrete capacitors are placed on the SOSCO and SOSCI pins. This mode is designed to work only with discrete capacitances of approximately 3 pF-10 pF on each pin.

Crystal manufacturers usually specify a CL (Capacitance Load) rating for their crystals. This value is related to, but not necessarily the same as, the values that should be used for C1 and C2 in Figure 14-2.

For more details on selecting the optimum C1 and C2 for a given crystal, see the crystal manufacturer's applications information. The optimum value depends, in part, on the amount of parasitic capacitance in the circuit, which is often unknown. For that reason, it is highly recommended that thorough testing and validation of the oscillator be performed after values have been selected.

### 14.5.1 USING SOSC AS A CLOCK SOURCE

The SOSC oscillator is also available as a clock source in power-managed modes. By setting the System Clock Select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode, and both the CPU and peripherals are clocked from the SOSC oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in Section 4.0 "Power-Managed Modes".

Whenever the SOSC oscillator is providing the clock source, the SOSC System Clock Status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor (FSCM).

If the Clock Monitor is enabled and the SOSC oscillator fails while providing the clock, polling the SOCSRUN bit will indicate whether the clock is being provided by the SOSC oscillator or another source.

### 14.5.2 SOSC OSCILLATOR LAYOUT CONSIDERATIONS

The SOSC oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode, SOSCSEL<1:0> (CONFIG1L<4:3>) = 01.

The oscillator circuit, displayed in Figure 14-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

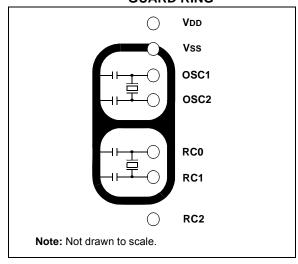

If a high-speed circuit must be located near the oscillator, it may help to have a grounded guard ring around the oscillator circuit. The guard, as displayed in Figure 14-3, could be used on a single-sided PCB or in addition to a ground plane. (Examples of a high-speed circuit include the ECCP1 pin, in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin.)

FIGURE 14-3: OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

In the Low Drive Level mode, SOSCSEL<1:0> = 01, it is critical that RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with a relatively good PCB layout. If possible, either leave RC2 unused or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL<1:0> = 11) with many PCB layouts.

Even in the Higher Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is important to ensure that the circuit board is clean. Even a very small amount of conductive soldering flux residue can cause PCB leakage currents that can overwhelm the oscillator circuit.

#### 14.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

### 16.5.2 TIMER3/5/7 GATE SOURCE SELECTION

The Timer3/5/7 gate source can be selected from one of four different sources. Source selection is controlled by the TxGSS<1:0> bits (TxGCON<1:0>). The polarity for each available source is also selectable and is controlled by the TxGPOL bit (TxGCON <6>).

TABLE 16-2: TIMER3/5/7 GATE SOURCES

| TxGSS<1:0> | Timerx Gate Source                                                     |

|------------|------------------------------------------------------------------------|

| 00         | Timerx Gate Pin                                                        |

| 01         | TMR(x+1) to Match PR(x+1)<br>(TMR(x+1) increments to match<br>PR(x+1)) |

| 10         | Comparator 1 Output (comparator logic high output)                     |

| 11         | Comparator 2 Output (comparator logic high output)                     |

#### 16.5.2.1 TxG Pin Gate Operation

The TxG pin is one source for Timer3/5/7 gate control. It can be used to supply an external source to the Timerx gate circuitry.

#### 16.5.2.2 Timer4/6/8 Match Gate Operation

The TMR(x+1) register will increment until it matches the value in the PR(x+1) register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timerx gate circuitry. The pulse will remain high for one instruction cycle and will return back to a low state until the next match.

Depending on TxGPOL, Timerx increments differently when TMR(x+1) matches PR(x+1). When TxGPOL = 1, Timerx increments for a single instruction

cycle following a TMR(x+1) match with PR(x+1). When TxGPOL = 0, Timerx increments continuously, except for the cycle following the match, when the gate signal goes from low-to-high.

### 16.5.2.3 Comparator 1 Output Gate Operation

The output of Comparator 1 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 1 with the CM1CON register, Timerx will increment depending on the transitions of the CMP1OUT (CMSTAT<5>) bit.

### 16.5.2.4 Comparator 2 Output Gate Operation

The output of Comparator 2 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 2 with the CM2CON register, Timerx will increment depending on the transitions of the CMP2OUT (CMSTAT<6>) bit.

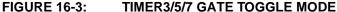

#### 16.5.3 TIMER3/5/7 GATE TOGGLE MODE

When Timer3/5/7 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3/5/7 gate signal, as opposed to the duration of a single level pulse.

The Timerx gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 16-3.)

The TxGVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3/5/7 Gate Toggle mode is enabled by setting the TxGTM bit (TxGCON<5>). When the TxGTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 18-6: TIMER PULSE GENERATION

### 18.4 Sleep Mode

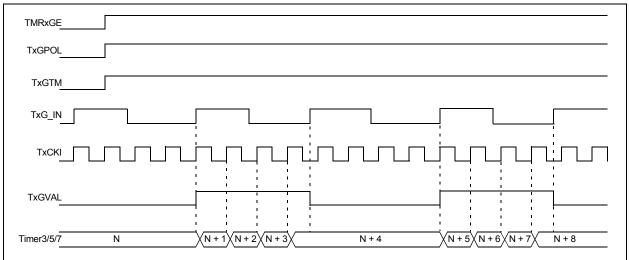

The timer and alarm continue to operate while in Sleep mode. The operation of the alarm is not affected by Sleep, as an alarm event can always wake up the CPU.

The Idle mode does not affect the operation of the timer or alarm.

#### 18.5 Reset

#### 18.5.1 DEVICE RESET

When a device Reset occurs, the ALRMRPT register is forced to its Reset state, causing the alarm to be disabled (if enabled prior to the Reset). If the RTCC was enabled, it will continue to operate when a basic device Reset occurs.

### 18.5.2 POWER-ON RESET (POR)

The RTCCFG and ALRMRPT registers are reset only on a POR. Once the device exits the POR state, the clock registers should be reloaded with the desired values.

The timer prescaler values can be reset only by writing to the SECONDS register. No device Reset can affect the prescalers.

### 19.3 Compare Mode

In Compare mode, the 16-bit CCPR4 register value is constantly compared against the Timer register pair value selected in the CCPTMR1 register. When a match occurs, the CCP4 pin can be:

- · Driven high

- · Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP4M<3:0>). At the same time, the interrupt flag bit, CCP4IF, is set.

Figure 19-2 gives the Compare mode block diagram

#### 19.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

Note: Clearing the CCP4CON register will force the RC1 or RE7 compare output latch (depending on device configuration) to the default low level. This is not the PORTC or PORTE I/O data latch.

#### 19.3.2 TIMER1/3/5/7 MODE SELECTION

If the CCP module is using the compare feature in conjunction with any of the Timer1/3/5/7 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

Note: Details of the timer assignments for the CCP modules are given in Table 19-2 and Table 19-3.

#### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP4M<3:0> = 1010), the CCP4 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP4IE bit is set.

#### 19.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP4M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

The Special Event Trigger for CCP4 cannot start an A/D conversion.

Note:

The Special Event Trigger of ECCP2 can start an A/D conversion, but the A/D Converter must be enabled. For more information, see Section 19.0 "Capture/Compare/PWM (CCP) Modules".

# 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex, asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

All members of the PIC18F87K22 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- · Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1) and PORTG (RG1/TX2/CK2/AN19/C3OUT and RG2/RX2/DT2/AN18/C3INA), respectively. In order to configure these pins as an EUSART:

- · For EUSART1:

- Bit, SPEN (RCSTA1<7>), must be set (= 1)

- Bit, TRISC<7>, must be set (= 1)

- Bit, TRISC<6>, must be cleared (= 0) for Asynchronous and Synchronous Master modes

- Bit, TRISC<6>, must be set (= 1) for Synchronous Slave mode

- · For EUSART2:

- Bit, SPEN (RCSTA2<7>), must be set (= 1)

- Bit, TRISG<2>, must be set (= 1)

- Bit TRISG<1> must be cleared (= 0) for Asynchronous and Synchronous Master modes

- Bit, TRISC<6>, must be set (= 1) for Synchronous Slave mode

**Note:** The EUSART control will automatically reconfigure the pin from input to output as needed.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed on the following pages in Register 22-1, Register 22-2 and Register 22-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

TABLE 28-1: CONFIGURATION BITS AND DEVICE IDs

| File    | Name                  | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                 | Bit 2     | Bit 1                 | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|-----------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------|-----------------------|--------|-----------------------------------|

| 300000h | CONFIG1L              |                      | XINST                |                      | SOSCSEL1             | SOSCSEL0              | INTOSCSEL |                       | RETEN  | -1-1 11                           |

| 300001h | CONFIG1H              | IESO                 | FCMEN                | -                    | PLLCFG               | FOSC3                 | FOSC2     | FOSC1                 | FOSC0  | 00-0 1000                         |

| 300002h | CONFIG2L              | 1                    | BORPWR1              | BORWPR0              | BORV1                | BORV0                 | BOREN1    | BOREN0                | PWRTEN | -111 1111                         |

| 300003h | CONFIG2H              | _                    | WDTPS4               | WDTPS3               | WDTPS2               | WDTPS1                | WDTPS0    | WDTEN1                | WDTEN0 | -111 1111                         |

| 300004h | CONFIG3L              | WAIT <sup>(2)</sup>  | BW <sup>(2)</sup>    | ABW1 <sup>(2)</sup>  | ABW0 <sup>(2)</sup>  | EASHFT <sup>(2)</sup> | _         | _                     | RTCOSC | 1                                 |

| 300005h | CONFIG3H              | MCLRE                | -                    |                      | -                    | MSSPMSK               |           | ECCPMX <sup>(2)</sup> | CCP2MX | 1 1-11                            |

| 300006h | CONFIG4L              | DEBUG                | 1                    | 1                    | BBSIZ0               | _                     | -         | 1                     | STVREN | 111                               |

| 300008h | CONFIG5L              | CP7 <sup>(1)</sup>   | CP6 <sup>(1)</sup>   | CP5 <sup>(1)</sup>   | CP4 <sup>(1)</sup>   | CP3                   | CP2       | CP1                   | CP0    | 1111 1111                         |

| 300009h | CONFIG5H              | CPD                  | CPB                  | -                    | _                    | _                     | _         | -                     | _      | 11                                |

| 30000Ah | CONFIG6L              | WRT7 <sup>(1)</sup>  | WRT6 <sup>(1)</sup>  | WRT5 <sup>(1)</sup>  | WRT4 <sup>(1)</sup>  | WRT3                  | WRT2      | WRT1                  | WRT0   | 1111 1111                         |

| 30000Bh | CONFIG6H              | WRTD                 | WRTB                 | WRTC                 | _                    | _                     | _         | _                     | _      | 111                               |

| 30000Ch | CONFIG7L              | EBTR7 <sup>(1)</sup> | EBTR6 <sup>(1)</sup> | EBTR5 <sup>(1)</sup> | EBTR4 <sup>(1)</sup> | EBTR3                 | EBTR2     | EBTR1                 | EBTR0  | 1111 1111                         |

| 30000Dh | CONFIG7H              | 1                    | EBTRB                | -                    | _                    | _                     | _         | -                     | _      | -1                                |

| 3FFFEh  | DEVID1 <sup>(3)</sup> | DEV2                 | DEV1                 | DEV0                 | REV4                 | REV3                  | REV2      | REV1                  | REV0   | xxxx xxxx                         |

| 3FFFFFh | DEVID2 <sup>(3)</sup> | DEV10                | DEV9                 | DEV8                 | DEV7                 | DEV6                  | DEV5      | DEV4                  | DEV3   | xxxx xxxx                         |

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown}, \textbf{u} = \text{unchanged}, - = \text{unimplemented}, \textbf{q} = \text{value depends on condition}. \\ \textbf{Shaded cells are unimplemented}, \textbf{read as '0'}.$

Note 1: Implemented only on the PIC18F67K22 and PIC18F87K22 devices.

<sup>2:</sup> Implemented only on the 80-pin devices (PIC18F8XK22).

<sup>3:</sup> See Register 28-14 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

#### REGISTER 28-14: DEVID1: DEVICE ID REGISTER 1 FOR THE PIC18F87K22 FAMILY

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 **DEV<2:0>:** Device ID bits

Devices with DEV<10:3> of '0101 0010' (see DEVID2):

010 = PIC18F65K22 000 = PIC18F66K22 101 = PIC18F85K22 011 = PIC18F86K22

Devices with DEV<10:3> of '0101 0001':

000 = PIC18F67K22 010 = PIC18F87K22

bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to indicate the device revision.

#### REGISTER 28-15: DEVID2: DEVICE ID REGISTER 2 FOR THE PIC18F87K22 FAMILY

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **DEV<10:3>:** Device ID bits<sup>(1)</sup>

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

0101 0010 = PIC18F65K22, PIC18F66K22, PIC18F85K22 and PIC18F86K22

0101 0001 = PIC18F67K22 and PIC18F87K22

**Note 1:** These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

| COMF              | Complement                                                                                                                                                                                                                                            | f f     |      |      |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|--|--|

| Syntax:           | COMF f {,c                                                                                                                                                                                                                                            | l {,a}} |      |      |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                   |         |      |      |  |  |

| Operation:        | $\overline{f} \to dest$                                                                                                                                                                                                                               |         |      |      |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                                                                                  |         |      |      |  |  |

| Encoding:         | 0001 1                                                                                                                                                                                                                                                | .1da    | ffff | ffff |  |  |

| Description:      | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'.  If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank |         |      |      |  |  |

|                   | If 'a' is '0' and the extended instruset is enabled, this instruction ope in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 29.2.3 "Byte-Oriented a Bit-Oriented Instructions in Indexiteral Offset Mode" for details.     |         |      |      |  |  |

| Words:            | 1                                                                                                                                                                                                                                                     |         |      |      |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                     |         |      |      |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                       |         |      |      |  |  |

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

|        |              |         |             |

Example:

COMF

REG, 0, 0

0

Before Instruction

REG = 13h

4fter Instruction

REG = 13h

4fter Instruction

REG = 12h

4fter Instruction

4fter In

| CPF       | SEQ                           | Compare f with W, Skip if f = W                                                                                                                                                                                                                                    |                                                                                                               |     |                |  |  |  |

|-----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|----------------|--|--|--|

| Synta     | ax:                           | CPFSEQ f {,a}                                                                                                                                                                                                                                                      |                                                                                                               |     |                |  |  |  |

| Oper      | ands:                         | $0 \le f \le 255$<br>$a \in [0,1]$                                                                                                                                                                                                                                 |                                                                                                               |     |                |  |  |  |

| Oper      | ation:                        | (f) – (W),<br>skip if (f) = (W)<br>(unsigned comparison)                                                                                                                                                                                                           |                                                                                                               |     |                |  |  |  |

| Statu     | s Affected:                   | None                                                                                                                                                                                                                                                               |                                                                                                               |     |                |  |  |  |

| Enco      | oding:                        | 0110                                                                                                                                                                                                                                                               | 001a f                                                                                                        | fff | ffff           |  |  |  |

| Desc      | cription:                     | location 'f' t                                                                                                                                                                                                                                                     | Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction. |     |                |  |  |  |

|           |                               | If 'f' = W, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction.                                                                                                                                          |                                                                                                               |     |                |  |  |  |

|           |                               | If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.                                                                                                                                                                 |                                                                                                               |     |                |  |  |  |

|           |                               | If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                                                                                                               |     |                |  |  |  |

| Word      | ds:                           | 1                                                                                                                                                                                                                                                                  |                                                                                                               |     |                |  |  |  |

| Cycle     | es:                           | 1(2)  Note: 3 cycles if skip and followed by a 2-word instruction.                                                                                                                                                                                                 |                                                                                                               |     |                |  |  |  |

| QC        | ycle Activity:                |                                                                                                                                                                                                                                                                    |                                                                                                               |     |                |  |  |  |

|           | Q1                            | Q2                                                                                                                                                                                                                                                                 | Q3                                                                                                            |     | Q4             |  |  |  |

|           | Decode                        | Read                                                                                                                                                                                                                                                               | Process                                                                                                       |     | No             |  |  |  |

| If sk     | in:                           | register 'f'                                                                                                                                                                                                                                                       | Data                                                                                                          | op  | eration        |  |  |  |

| 11 31     | .ιρ.<br>Q1                    | Q2                                                                                                                                                                                                                                                                 | Q3                                                                                                            |     | Q4             |  |  |  |

|           |                               |                                                                                                                                                                                                                                                                    | No                                                                                                            |     |                |  |  |  |

| operation |                               | operation                                                                                                                                                                                                                                                          |                                                                                                               |     |                |  |  |  |

| If sk     | ip and followed               | •                                                                                                                                                                                                                                                                  |                                                                                                               |     |                |  |  |  |

|           | Q1                            | Q2                                                                                                                                                                                                                                                                 | Q3                                                                                                            |     | Q4             |  |  |  |

|           | No                            | No                                                                                                                                                                                                                                                                 | No                                                                                                            |     | No             |  |  |  |

|           | operation<br>No               | operation<br>No                                                                                                                                                                                                                                                    | operation<br>No                                                                                               | ot  | neration<br>No |  |  |  |

|           | operation operation operation |                                                                                                                                                                                                                                                                    |                                                                                                               |     |                |  |  |  |

HERE

NEQUAL EQUAL

Example:

CPFSEQ REG, 0

#### 29.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, the PIC18F87K22 family of devices also provides an optional extension to the core CPU functionality. The added features include eight additional instructions that augment Indirect and Indexed Addressing operations and the implementation of Indexed Literal Offset Addressing for many of the standard PIC18 instructions.

The additional features of the extended instruction set are enabled by default on unprogrammed devices. Users must properly set or clear the XINST Configuration bit during programming to enable or disable these features.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- Dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- · Function Pointer invocation

- · Software Stack Pointer manipulation

- Manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 29-3. Detailed descriptions are provided in **Section 29.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 29-1 (page 432) apply to both the standard and extended PIC18 instruction sets.

Note:

The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

#### 29.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of Indexed Addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM™ Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 29.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

TABLE 29-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

| Mnemonic, |               | Description                              | Cycles 16-Bit Instruction Word |      |      | Status |          |      |

|-----------|---------------|------------------------------------------|--------------------------------|------|------|--------|----------|------|

| Operai    | nds           | Description                              | Cycles                         | MSb  |      | LSb    | Affected |      |

| ADDFSR    | f, k          | Add Literal to FSR                       | 1                              | 1110 | 1000 | ffkk   | kkkk     | None |

| ADDULNK   | k             | Add Literal to FSR2 and Return           | 2                              | 1110 | 1000 | 11kk   | kkkk     | None |

| CALLW     |               | Call Subroutine using WREG               | 2                              | 0000 | 0000 | 0001   | 0100     | None |

| MOVSF     | $z_s$ , $f_d$ | Move z <sub>s</sub> (source) to 1st word | 2                              | 1110 | 1011 | 0zzz   | ZZZZ     | None |

|           |               | f <sub>d</sub> (destination) 2nd word    |                                | 1111 | ffff | ffff   | ffff     |      |

| MOVSS     | $z_s, z_d$    | Move z <sub>s</sub> (source) to 1st word | 2                              | 1110 | 1011 | 1zzz   | ZZZZ     | None |

|           |               | z <sub>d</sub> (destination) 2nd word    |                                | 1111 | xxxx | XZZZ   | ZZZZ     |      |

| PUSHL     | k             | Store Literal at FSR2,<br>Decrement FSR2 | 1                              | 1110 | 1010 | kkkk   | kkkk     | None |

| SUBFSR    | f, k          | Subtract Literal from FSR                | 1                              | 1110 | 1001 | ffkk   | kkkk     | None |

| SUBULNK   | k             | Subtract Literal from FSR2 and return    | 2                              | 1110 | 1001 | 11kk   | kkkk     | None |

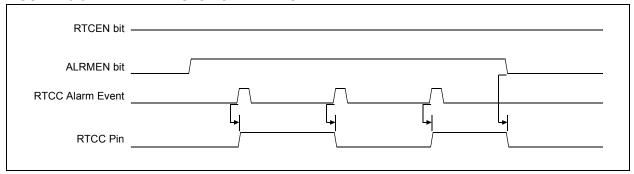

FIGURE 31-13: CAPTURE/COMPARE/PWM TIMINGS (ECCP1, ECCP2 MODULES)

TABLE 31-16: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP1, ECCP2 MODULES)

| Param<br>No. | Symbol    | С                     | haracteristic  | Min             | Max | Units | Conditions                         |

|--------------|-----------|-----------------------|----------------|-----------------|-----|-------|------------------------------------|

| 50           | TccL      | CCPx Input Low        | No prescaler   | 0.5 Tcy + 20    | -   | ns    |                                    |

|              | Time      | Time                  | With prescaler | 10              | _   | ns    |                                    |

| 51           | TccH      | CCPx Input            | No prescaler   | 0.5 Tcy + 20    | _   | ns    |                                    |

|              | High Time | With prescaler        | 10             | _               | ns  |       |                                    |

| 52           | TCCP      | CCPx Input Period     |                | 3 Tcy + 40<br>N | _   | ns    | N = prescale<br>value (1, 4 or 16) |

| 53           | TccR      | CCPx Output Fall Time |                | _               | 25  | ns    |                                    |

| 54           | TccF      | CCPx Output Fall Time |                | _               | 25  | ns    |                                    |