Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

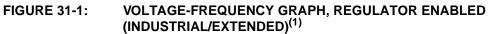

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 64/80-Pin, High-Performance, 1-Mbit Enhanced Flash MCUs with 12-Bit A/D and nanoWatt XLP Technology

#### Low-Power Features:

- Power-Managed modes:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- Two-Speed Oscillator Start-up

- Fail-Safe Clock Monitor

- Power-Saving Peripheral Module Disable (PMD)

- Ultra Low-Power Wake-up

- Fast Wake-up, 1 μs Typical

- · Low-Power WDT, 300 nA Typical

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 5.5 μA, Typical

- Idle mode Currents Down to 1.7 μA Typical

- Sleep mode Currents Down to Very Low 20 nA, Typical

- RTCC Current Downs to Very Low 700 nA, Typical

#### **Special Microcontroller Features:**

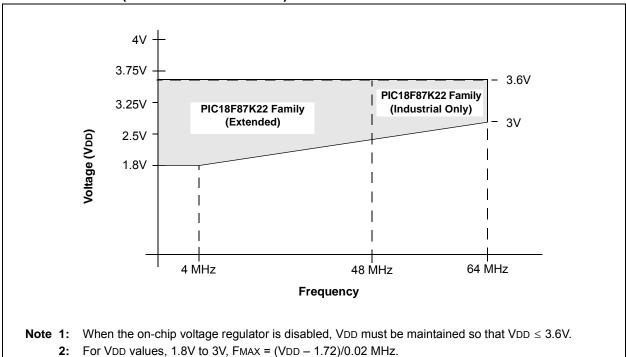

- Operating Voltage Range: 1.8V to 5.5V

- On-Chip 3.3V Regulator

- · Operating Speed up to 64 MHz

- Up to 128 Kbytes On-Chip Flash Program Memory

- Data EEPROM of 1,024 Bytes

- 4K x 8 General Purpose Registers (SRAM)

- 10,000 Erase/Write Cycle Flash Program Memory, Minimum

- 1,000,000 Erase/write Cycle Data EEPROM Memory, Typical

- · Flash Retention: 40 Years, Minimum

- Three Internal Oscillators: LF-INTRC (31 kHz), MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

- Self-Programmable under Software Control

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s (about 70 minutes)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug via Two Pins

- Programmable:

- BOR

- LVD

|             | Prog             | Program Memory                |                 | Data Memory       |     | 12-Bit      | CCP/ | MSSP |     |                             | Е     | tors        | t, e               | Bus        | _    | 0    |

|-------------|------------------|-------------------------------|-----------------|-------------------|-----|-------------|------|------|-----|-----------------------------|-------|-------------|--------------------|------------|------|------|

| Device      | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D<br>(ch) | ECCP |      | SPI | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External I | CTMU | RTCC |

| PIC18F65K22 | 32K              | 16,383                        | 2K              | 1K                | 53  | 16          | 5/3  | 2    | Y   | Y                           | 2     | 3           | 4/4                | Ν          | Y    | Y    |

| PIC18F66K22 | 64K              | 32,768                        | 4K              | 1K                | 53  | 16          | 7/3  | 2    | Y   | Y                           | 2     | 3           | 6/5                | Ν          | Y    | Y    |

| PIC18F67K22 | 128K             | 65,536                        | 4K              | 1K                | 53  | 16          | 7/3  | 2    | Y   | Y                           | 2     | 3           | 6/5                | Ν          | Y    | Y    |

| PIC18F85K22 | 32K              | 16,383                        | 2K              | 1K                | 69  | 24          | 5/3  | 2    | Y   | Y                           | 2     | 3           | 4/4                | Y          | Y    | Y    |

| PIC18F86K22 | 64K              | 32,768                        | 4K              | 1K                | 69  | 24          | 7/3  | 2    | Y   | Y                           | 2     | 3           | 6/5                | Y          | Y    | Y    |

| PIC18F87K22 | 128K             | 65,536                        | 4K              | 1K                | 69  | 24          | 7/3  | 2    | Y   | Y                           | 2     | 3           | 6/5                | Y          | Y    | Y    |

#### 3.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the SOSC oscillator is operating and providing the device clock. The SOSC oscillator may also run in all power-managed modes if required to clock SOSC.

In RC\_RUN and RC\_IDLE modes, the internal oscillator provides the device clock source. The 31 kHz LF-INTOSC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 28.2 "Watchdog Timer (WDT)" through Section 28.5 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

If Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTOSC is required to support WDT operation. The SOSC oscillator may be operating to support a Real-Time Clock (RTC). Other features may be operating that do not require a device clock source (i.e., MSSP slave, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F87K22 Family (Industrial/ Extended)".

### 3.9 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.6 "Power-up Timer (PWRT)**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on a power-up time of about 64 ms (Parameter 33, Table 31-13); it is always enabled.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS, XT or LP modes). The OST does this by counting 1,024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval, TCSD (Parameter 38, Table 31-13), following POR, while the controller becomes ready to execute instructions.

TABLE 3-4:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| Oscillator Mode   | OSC1 Pin                                                 | OSC2 Pin                                                    |

|-------------------|----------------------------------------------------------|-------------------------------------------------------------|

| EC, ECPLL         | Floating, pulled by external clock                       | At logic low (clock/4 output)                               |

| HS, HSPLL         | Feedback inverter is disabled at quiescent voltage level | Feedback inverter is disabled at quiescent<br>voltage level |

| INTOSC, INTPLL1/2 | I/O pin, RA6, direction is controlled by TRISA<6>        | I/O pin, RA6, direction is controlled by TRISA<7>           |

Note: See Section 5.0 "Reset" for time-outs due to Sleep and MCLR Reset.

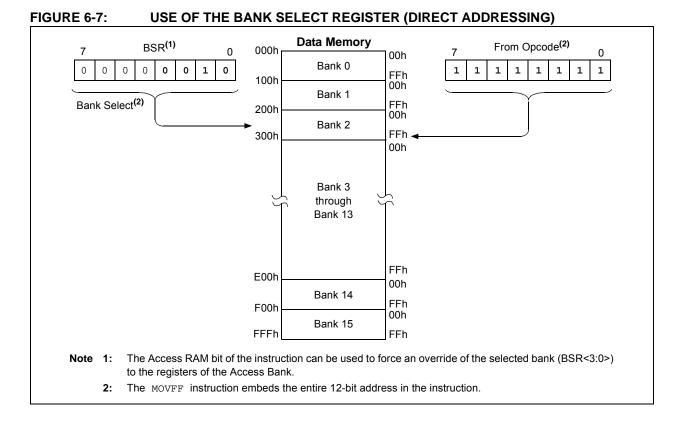

### 6.3.2 ACCESS BANK

While the use of the BSR, with an embedded 8-bit address, allows users to address the entire range of data memory, it also means that the user must ensure that the correct bank is selected. If not, data may be read from, or written to, the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an eight-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map. In that case, the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables.

Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy all of Bank 15 (F00h to FFFh) and the top part of Bank 14 (EF4h to EFFh).

A list of these registers is given in Table 6-1 and Table 6-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

| Addr. | Name                    | Addr. | Name                    | Addr. | Name     | Addr. | Name                 | Addr. | Name     | Addr. | Name <sup>(4)</sup>     |

|-------|-------------------------|-------|-------------------------|-------|----------|-------|----------------------|-------|----------|-------|-------------------------|

| FFFh  | TOSU                    | FDFh  | INDF2 <sup>(1)</sup>    | FBFh  | ECCP1AS  | F9Fh  | IPR1                 | F7Fh  | EECON1   | F5Fh  | RTCCFG                  |

| FFEh  | TOSH                    | FDEh  | POSTINC2(1)             | FBEh  | ECCP1DEL | F9Eh  | PIR1                 | F7Eh  | EECON2   | F5Eh  | RTCCAL                  |

| FFDh  | TOSL                    | FDDh  | POSTDEC2 <sup>(1)</sup> | FBDh  | CCPR1H   | F9Dh  | PIE1                 | F7Dh  | TMR5H    | F5Dh  | RTCVALH                 |

| FFCh  | STKPTR                  | FDCh  | PREINC2 <sup>(1)</sup>  | FBCh  | CCPR1L   | F9Ch  | PSTR1CON             | F7Ch  | TMR5L    | F5Ch  | RTCVALL                 |

| FFBh  | PCLATU                  | FDBh  | PLUSW2 <sup>(1)</sup>   | FBBh  | CCP1CON  | F9Bh  | OSCTUNE              | F7Bh  | T5CON    | F5Bh  | ALRMCFG                 |

| FFAh  | PCLATH                  | FDAh  | FSR2H                   | FBAh  | PIR5     | F9Ah  | TRISJ <sup>(2)</sup> | F7Ah  | T5GCON   | F5Ah  | ALRMRPT                 |

| FF9h  | PCL                     | FD9h  | FSR2L                   | FB9h  | PIE5     | F99h  | TRISH <sup>(2)</sup> | F79h  | CCPR4H   | F59h  | ALRMVALH                |

| FF8h  | TBLPTRU                 | FD8h  | STATUS                  | FB8h  | IPR4     | F98h  | TRISG                | F78h  | CCPR4L   | F58h  | ALRMVALL                |

| FF7h  | TBLPTRH                 | FD7h  | TMR0H                   | FB7h  | PIR4     | F97h  | TRISF                | F77h  | CCP4CON  | F57h  | CTMUCONH                |

| FF6h  | TBLPTRL                 | FD6h  | TMR0L                   | FB6h  | PIE4     | F96h  | TRISE                | F76h  | CCPR5H   | F56h  | CTMUCONL                |

| FF5h  | TABLAT                  | FD5h  | T0CON                   | FB5h  | CVRCON   | F95h  | TRISD                | F75h  | CCPR5L   | F55h  | CTMUICONH               |

| FF4h  | PRODH                   | FD4h  | SPBRGH1                 | FB4h  | CMSTAT   | F94h  | TRISC                | F74h  | CCP5CON  | F54h  | CM1CON                  |

| FF3h  | PRODL                   | FD3h  | OSCCON                  | FB3h  | TMR3H    | F93h  | TRISB                | F73h  | CCPR6H   | F53h  | PADCFG1                 |

| FF2h  | INTCON                  | FD2h  | IPR5                    | FB2h  | TMR3L    | F92h  | TRISA                | F72h  | CCPR6L   | F52h  | ECCP2AS                 |

| FF1h  | INTCON2                 | FD1h  | WDTCON                  | FB1h  | T3CON    | F91h  | LATJ <sup>(2)</sup>  | F71h  | CCP6CON  | F51h  | ECCP2DEL                |

| FF0h  | INTCON3                 | FD0h  | RCON                    | FB0h  | T3GCON   | F90h  | LATH <sup>(2)</sup>  | F70h  | CCPR7H   | F50h  | CCPR2H                  |

| FEFh  | INDF0 <sup>(1)</sup>    | FCFh  | TMR1H                   | FAFh  | SPBRG1   | F8Fh  | LATG                 | F6Fh  | CCPR7L   | F4Fh  | CCPR2L                  |

|       | POSTINC0 <sup>(1)</sup> | FCEh  | TMR1L                   | FAEh  | RCREG1   | F8Eh  | LATF                 | F6Eh  | CCP7CON  | F4Eh  | CCP2CON                 |

| FEDh  | POSTDEC0 <sup>(1)</sup> | FCDh  | T1CON                   | FADh  | TXREG1   | F8Dh  | LATE                 | F6Dh  | TMR4     | F4Dh  | ECCP3AS                 |

| FECh  | PREINC0 <sup>(1)</sup>  | FCCh  | TMR2                    | FACh  | TXSTA1   | F8Ch  | LATD                 | F6Ch  | PR4      | F4Ch  | ECCP3DEL                |

| FEBh  | PLUSW0 <sup>(1)</sup>   | FCBh  | PR2                     | FABh  | RCSTA1   | F8Bh  | LATC                 | F6Bh  | T4CON    | F4Bh  | CCPR3H                  |

| FEAh  | FSR0H                   | FCAh  | T2CON                   | FAAh  | T1GCON   | F8Ah  | LATB                 | F6Ah  | SSP2BUF  | F4Ah  | CCPR3L                  |

| FE9h  | FSR0L                   | FC9h  | SSP1BUF                 | FA9h  | IPR6     | F89h  | LATA                 | F69h  | SSP2ADD  | F49h  | CCP3CON                 |

| FE8h  | WREG                    | FC8h  | SSP1ADD                 | FA8h  | HLVDCON  | F88h  | PORTJ <sup>(2)</sup> | F68h  | SSP2STAT | F48h  | CCPR8H                  |

| FE7h  | INDF1 <sup>(1)</sup>    | FC7h  | SSP1STAT                | FA7h  | PSPCON   | F87h  | PORTH <sup>(2)</sup> | F67h  | SSP2CON1 | F47h  | CCPR8L                  |

| FE6h  | POSTINC1 <sup>(1)</sup> | FC6h  | SSP1CON1                | FA6h  | PIR6     | F86h  | PORTG                | F66h  | SSP2CON2 | F46h  |                         |

| FE5h  | POSTDEC1 <sup>(1)</sup> | FC5h  | SSP1CON2                | FA5h  | IPR3     | F85h  | PORTF                | F65h  | BAUDCON1 | F45h  | CCPR9H <sup>(3)</sup>   |

| FE4h  | PREINC1 <sup>(1)</sup>  | FC4h  | ADRESH                  | FA4h  | PIR3     | F84h  | PORTE                | F64h  | OSCCON2  | F44h  | CCPR9L <sup>(3)</sup>   |

| FE3h  | PLUSW1 <sup>(1)</sup>   | FC3h  | ADRESL                  | FA3h  | PIE3     | F83h  | PORTD                | F63h  | EEADRH   | F43h  | CCP9CON <sup>(3)</sup>  |

| FE2h  | FSR1H                   | FC2h  | ADCON0                  | FA2h  | IPR2     | F82h  | PORTC                | F62h  | EEADR    | F42h  |                         |

| FE1h  | FSR1L                   | FC1h  | ADCON1                  | FA1h  | PIR2     | F81h  | PORTB                | F61h  | EEDATA   | F41h  |                         |

| FE0h  | BSR                     | FC0h  | ADCON2                  | FA0h  | PIE2     | F80h  | PORTA                | F60h  | PIE6     | F40h  | CCP10CON <sup>(3)</sup> |

TABLE 6-1:

SPECIAL FUNCTION REGISTER MAP FOR PIC18F87K22 FAMILY

**Note 1:** This is not a physical register.

2: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

3: This register is not available on devices with a program memory of 32 Kbytes (PIC18FX5K22).

4: Addresses, F16h through F5Fh, are also used by SFRs, but are not part of the Access RAM. To access these registers, users must always load the proper BSR value.

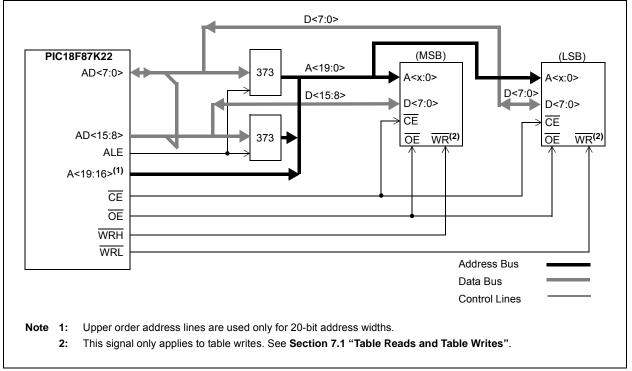

#### 8.6.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F87K22 family devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

#### REGISTER 11-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1      | R/W-1                                                            | R/W-0                                                 | R/W-0                          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|------------|------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|--------|

| INT2IP     | INT1IP                                                           | INT3IE                                                | INT2IE                         | INT1IE           | INT3IF          | INT2IF          | INT1IF |

| bit 7      |                                                                  |                                                       |                                |                  |                 |                 | bit (  |

| Legend:    |                                                                  |                                                       |                                |                  |                 |                 |        |

| R = Reada  | able bit                                                         | W = Writable                                          | bit                            | U = Unimpler     | nented bit, rea | d as '0'        |        |

| -n = Value | at POR                                                           | '1' = Bit is set                                      |                                | '0' = Bit is cle |                 | x = Bit is unkr | nown   |

| bit 7      | 1 = High prio                                                    | ,                                                     | upt Priority bit               |                  |                 |                 |        |

| bit 6      | 0 = Low prior<br>INT1IP: INT1<br>1 = High prio<br>0 = Low prior  | External Interr                                       | upt Priority bit               |                  |                 |                 |        |

| bit 5      | INT3IE: INT3<br>1 = Enables 1                                    | External Interr<br>the INT3 exterr<br>the INT3 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 4      | 1 = Enables                                                      | External Interr<br>the INT2 exterr<br>the INT2 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 3      | 1 = Enables                                                      | External Interr<br>the INT1 exterr<br>the INT1 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 2      | 1 = The INT3                                                     | External Interr<br>external interr<br>external interr | upt occurred (                 | must be cleared  | d in software)  |                 |        |

| bit 1      | INT2IF: INT2<br>1 = The INT2                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

| bit 0      | INT1IF: INT1<br>1 = The INT1                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

|            | Interrupt flag bits<br>enable bit or the 0<br>are clear prior to | Global Interrupt                                      | Enable bit. Us                 | ser software sho | ould ensure the | appropriate int |        |

#### 12.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISD and LATD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by setting bit, RDPU (PADCFG1<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

On 80-pin devices, PORTD is multiplexed with the system bus as part of the external memory interface. The I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled, PORTD is the low-order byte of the multiplexed address/data bus (AD<7:0>). The TRISD bits are also overridden.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. For additional information, see Section 12.11 "Parallel Slave Port".

The PORTD also has the I<sup>2</sup>C and SPI functionality on RD4, RD5 and RD6. The pins for SPI are also configurable for open-drain output. Open-drain configuration is selected by setting bit, SSP2OD (ODCON1<0>).

RD0 has a CTMU functionality. RD1 has the functionality for the Timer5 clock input and Timer7 external clock gate input.

| EXAMP | LE 12-4: | INITIALIZING PORTD      |

|-------|----------|-------------------------|

| CLRF  | PORTD    | ; Initialize PORTD by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATD     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 0CFh     | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISD    | ; Set RD<3:0> as inputs |

|       |          | ; RD<5:4> as outputs    |

|       |          | ; RD<7:6> as inputs     |

| Pin Name     | Function            | TRIS<br>Setting | I/O | l/O<br>Type | Description                       |  |  |  |  |

|--------------|---------------------|-----------------|-----|-------------|-----------------------------------|--|--|--|--|

| RD0/PSP0/    | RD0                 | 0               | 0   | DIG         | LATD<0> data output.              |  |  |  |  |

| AD0/CTPLS    |                     | 1               | Ι   | ST          | PORTD<0> data input.              |  |  |  |  |

|              | PSP0 <sup>(1)</sup> | x               | I/O | TTL         | Parallel Slave Port data.         |  |  |  |  |

|              | AD0 <sup>(2)</sup>  | х               | I/O | TTL         | External Memory Address/Data 0.   |  |  |  |  |

|              | CTPLS               | х               | 0   | DIG         | CTMU pulse generator output.      |  |  |  |  |

| RD1/PSP1/    | RD1                 | 0               | 0   | DIG         | LATD<1> data output.              |  |  |  |  |

| AD1/T5CKI/   |                     | 1               | Ι   | ST          | PORTD<1> data input.              |  |  |  |  |

| T7G          | PSP1 <sup>(1)</sup> | х               | I/O | TTL         | Parallel Slave Port data.         |  |  |  |  |

|              | AD1 <sup>(2)</sup>  | х               | I/O | TTL         | External Memory Address/Data 1.   |  |  |  |  |

|              | T5CKI               | х               | Ι   | ST          | Timer5 clock input.               |  |  |  |  |

|              | T7G                 | х               | Ι   | ST          | Timer7 external clock gate input. |  |  |  |  |

| RD2/PSP2/AD2 | RD2                 | 0               | 0   | DIG         | LATD<2> data output.              |  |  |  |  |

|              |                     | 1               | Ι   | ST          | PORTD<2> data input.              |  |  |  |  |

|              | PSP2 <sup>(1)</sup> | х               | I/O | TTL         | Parallel Slave Port data.         |  |  |  |  |

|              | AD2 <sup>(2)</sup>  | x               | I/O | TTL         | External Memory Address/Data 2.   |  |  |  |  |

#### TABLE 12-7 PORTD FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,  $I^2C = I^2C^{\text{TM}}/\text{SMBus Buffer Input}$ , x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: The Parallel Slave Port (PSP) is available only in Microcontroller mode.

2: This feature is available only on PIC18F8XK22 devices.

### 15.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- Eight-bit Timer and Period registers (TMR2 and PR2, respectively)

- Both registers are readable and writable

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 15-1) that enables or disables the timer, and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 15-1.

#### 15.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A four-bit counter/prescaler on the clock input gives the prescale options of direct input, divide-by-4 or divide-by-16. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>).

The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler. (See **Section 15.2 "Timer2 Interrupt**".)

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR)

TMR2 is not cleared when T2CON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 20-2, Register 19-2 and Register 19-3.

#### REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0 R/W-0 R/W-0          |  | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------------------------|--|----------|----------|--------|---------|---------|

| —     | - T2OUTPS3 T2OUTPS2 T2OUTP |  | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |                            |  |          |          |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7<br>bit 6-3 | Unimplemented: Read as '0'<br>T2OUTPS<3:0>: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>• |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                  | •<br>1111 = 1:16 Postscale                                                                                                           |

| bit 2            | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                       |

| bit 1-0          | <b>T2CKPS&lt;1:0&gt;:</b> Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16    |

| IADLE 10-             | ABLE 16-5: REGISTERS ASSOCIATED WITH TIMER3/5/7 AS A TIMER/COUNTER |                        |                        |               |                       |        |        |         |  |  |

|-----------------------|--------------------------------------------------------------------|------------------------|------------------------|---------------|-----------------------|--------|--------|---------|--|--|

| Name                  | Bit 7                                                              | Bit 6                  | Bit 5                  | Bit 4         | Bit 3                 | Bit 2  | Bit 1  | Bit 0   |  |  |

| INTCON                | GIE/GIEH                                                           | PEIE/GIEL              | TMR0IE                 | <b>INTOIE</b> | RBIE                  | TMR0IF | INT0IF | RBIF    |  |  |

| PIR5                  | TMR7GIF <sup>(1)</sup>                                             | TMR12IF <sup>(1)</sup> | TMR10IF <sup>(1)</sup> | TMR8IF        | TMR7IF <sup>(1)</sup> | TMR6IF | TMR5IF | TMR4IF  |  |  |

| IPR5                  | TMR7GIP <sup>(1)</sup>                                             | TMR12IP <sup>(1)</sup> | TMR10IP <sup>(1)</sup> | TMR8IP        | TMR7IP <sup>(1)</sup> | TMR6IP | TMR5IP | TMR4IP  |  |  |

| PIE5                  | TMR7GIE <sup>(1)</sup>                                             | TMR12IE <sup>(1)</sup> | TMR10IE <sup>(1)</sup> | TMR8IE        | TMR7IE <sup>(1)</sup> | TMR6IE | TMR5IE | TMR4IE  |  |  |

| PIE3                  | TMR5GIE                                                            | _                      | RC2IE                  | TX2IE         | CTMUIE                | CCP2IE | CCP1IE | RTCCIE  |  |  |

| IPR3                  | TMR5GIP                                                            | _                      | RC2IP                  | TX2IP         | CTMUIP                | CCP2IP | CCP1IP | RTCCIP  |  |  |

| PIR3                  | TMR5GIF                                                            | _                      | RC2IF                  | TX2IF         | CTMUIF                | CCP2IF | CCP1IF | RTCCIF  |  |  |

| PIE2                  | OSCFIE                                                             | _                      | SSP2IE                 | BCL2IE        | BCL1IE                | HLVDIE | TMR3IE | TMR3GIE |  |  |

| PIR2                  | OSCFIF                                                             | —                      | SSP2IF                 | BCL2IF        | BCL1IF                | HLVDIF | TMR3IF | TMR3GIF |  |  |

| IPR2                  | OSCFIP                                                             | _                      | SSP2IP                 | BCL2IP        | BCL1IP                | HLVDIP | TMR3IP | TMR3GIP |  |  |

| TMR3H                 | Timer3 Regist                                                      | er High Byte           |                        |               |                       |        |        |         |  |  |

| TMR3L                 | Timer3 Regist                                                      | er Low Byte            |                        |               |                       |        |        |         |  |  |

| T3GCON                | TMR3GE                                                             | T3GPOL                 | T3GTM                  | T3GSPM        | T3GGO/<br>T3DONE      | T3GVAL | T3GSS1 | T3GSS0  |  |  |

| T3CON                 | TMR3CS1                                                            | TMR3CS0                | T3CKPS1                | T3CKPS0       | SOSCEN                | T3SYNC | RD16   | TMR3ON  |  |  |

| TMR5H                 | Timer5 Regist                                                      | er High Byte           |                        |               |                       |        |        |         |  |  |

| TMR5L                 | Timer5 Regist                                                      | er Low Byte            |                        |               |                       |        |        |         |  |  |

| T5GCON                | TMR5GE                                                             | T5GPOL                 | T5GTM                  | T5GSPM        | T5GGO/<br>T5DONE      | T5GVAL | T5GSS1 | T5GSS0  |  |  |

| T5CON                 | TMR5CS1                                                            | TMR5CS0                | T5CKPS1                | T5CKPS0       | SOSCEN                | T5SYNC | RD16   | TMR5ON  |  |  |

| TMR7H <sup>(1)</sup>  | Timer7 Regist                                                      | er High Byte           |                        |               |                       |        |        |         |  |  |

| TMR7L <sup>(1)</sup>  | Timer7 Regist                                                      | er Low Byte            |                        |               |                       |        |        |         |  |  |

| T7GCON <sup>(1)</sup> | TMR7GE                                                             | T7GPOL                 | T7GTM                  | T7GSPM        | T7GGO/<br>T7DONE      | T7GVAL | T7GSS1 | T7GSS0  |  |  |

| T7CON <sup>(1)</sup>  | TMR7CS1                                                            | TMR7CS0                | T7CKPS1                | T7CKPS0       | SOSCEN                | T7SYNC | RD16   | TMR7ON  |  |  |

| OSCCON2               | —                                                                  | SOSCRUN                | —                      |               | SOSCGO                | —      | MFIOFS | MFIOSEL |  |  |

| PMD1                  | PSPMD                                                              | CTMUMD                 | RTCCMD                 | TMR4MD        | TMR3MD                | TMR2MD | TMR1MD | EMBMD   |  |  |

| PMD2                  | TMR10MD <sup>(1)</sup>                                             | TMR8MD                 | TMR7MD <sup>(1)</sup>  | TMR6MD        | TMR5MD                | CMP3MD | CMP2MD | CMP2MD  |  |  |

|                       |                                                                    |                        |                        |               | •                     |        |        |         |  |  |

#### TABLE 16-5: REGISTERS ASSOCIATED WITH TIMER3/5/7 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3/5/7 module.

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

#### REGISTER 18-17: ALRMHR: ALARM HOURS VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | _   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 5-4 | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits |

|---------|------------------------------------------------------------------|

|         | Contains a value from 0 to 2.                                    |

| bit 3-0 | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits |

Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 18-18: ALRMMIN: ALARM MINUTES VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|-------|----------------------------|

- bit 6-4 **MINTEN<2:0>:** Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5.

- bit 3-0 MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits Contains a value from 0 to 9.

#### REGISTER 18-19: ALRMSEC: ALARM SECONDS VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |          |                           |                               |                    |

|-------------------|----------|---------------------------|-------------------------------|--------------------|

| R = Reada         | able bit | W = Writable bit          | U = Unimplemented bit,        | read as '0'        |

| -n = Value at POR |          | '1' = Bit is set          | '0' = Bit is cleared          | x = Bit is unknown |

| bit 7             | Unimple  | mented: Read as '0'       |                               |                    |

|                   | •        |                           |                               |                    |

| bit 6-4           | SECTEN   | <2:0>: Binary Coded Decim | al Value of Second's Tens Dig | it bits            |

|                   | Contains | a value from 0 to 5.      |                               |                    |

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9.

### TABLE 18-4:ALRMVAL REGISTER<br/>MAPPING

| ALRMPTR<1:0>    | Alarm Value Register Window |          |  |  |  |

|-----------------|-----------------------------|----------|--|--|--|

| ALRIVIPIR (1.0> | ALRMVALH                    | ALRMVALL |  |  |  |

| 0 0             | ALRMMIN                     | ALRMSEC  |  |  |  |

| 01              | ALRMWD                      | ALRMHR   |  |  |  |

| 10              | ALRMMNTH                    | ALRMDAY  |  |  |  |

| 11              | —                           | —        |  |  |  |

#### 18.2.9 CALIBRATION

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than three seconds per month.

To perform this calibration, find the number of error clock pulses and store the value into the lower half of the RTCCAL register. The eight-bit, signed value, loaded into RTCCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute.

To calibrate the RTCC module:

- 1. Use another timer resource on the device to find the error of the 32.768 kHz crystal.

- 2. Convert the number of error clock pulses per minute (see Equation 18-1).

#### EQUATION 18-1: CONVERTING ERROR CLOCK PULSES

(Ideal Frequency (32,758) – Measured Frequency) \* 60 = Error Clocks per Minute

- If the oscillator is *faster* than ideal (negative result from Step 2), the RCFGCALL register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

- If the oscillator is *slower* than ideal (positive result from Step 2), the RCFGCALL register value needs to be positive. This causes the specified number of clock pulses to be added to the timer counter, once every minute.

- 3. Load the RTCCAL register with the correct value.

Writes to the RTCCAL register should occur only when the timer is turned off or immediately after the rising edge of the seconds pulse.

| Note: | In determining the crystal's error value, it |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | is the user's responsibility to include the  |  |  |  |  |  |  |  |

|       | crystal's initial error from drift due to    |  |  |  |  |  |  |  |

|       | temperature or crystal aging.                |  |  |  |  |  |  |  |

#### 18.3 Alarm

The Alarm features and characteristics are:

- Configurable from half a second to one year

- Enabled using the ALRMEN bit (ALRMCFG<7>, Register 18-4)

- · Offers one-time and repeat alarm options

#### 18.3.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. The bit will not be cleared if the CHIME bit =  $1 \text{ or if ALRMRPT} \neq 0$ .

The interval selection of the alarm is configured through the ALRMCFG bits (AMASK<3:0>); see Figure 18-5. These bits determine which, and how many, digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The number of times this occurs, after the alarm is enabled, is stored in the ALRMRPT register.

**Note:** While the alarm is enabled (ALRMEN = 1), changing any of the registers, other than the RTCCAL, ALRMCFG and ALRMRPT registers and the CHIME bit, can result in a false alarm event leading to a false alarm interrupt. To avoid this, only change the timer and alarm values while the alarm is disabled (ALRMEN = 0). It is recommended that the ALRMCFG and ALRMRPT registers and CHIME bit be changed when RTCSYNC = 0.

#### REGISTER 20-2: CCPTMRS0: CCP TIMER SELECT 0 REGISTER

| R/W-0           | R/W-0                                                | R/W-0                                                                                                                                       | R/W-0                                                    | R/W-0            | R/W-0            | R/W-0            | R/W-0           |

|-----------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------------------|------------------|-----------------|

| C3TSEL1         | C3TSEL0                                              | C2TSEL2                                                                                                                                     | C2TSEL1                                                  | C2TSEL0          | C1TSEL2          | C1TSEL1          | C1TSEL0         |

| bit 7           |                                                      |                                                                                                                                             |                                                          |                  |                  |                  | bit (           |

| Legend:         |                                                      |                                                                                                                                             |                                                          |                  |                  |                  |                 |

| R = Readable    | bit                                                  | W = Writable                                                                                                                                | bit                                                      | U = Unimpler     | nented bit, read | as '0'           |                 |

| -n = Value at F | POR                                                  | '1' = Bit is set                                                                                                                            |                                                          | '0' = Bit is cle | ared             | x = Bit is unkr  | nown            |

|                 | 01 = ECCP3<br>10 = ECCP3                             | is based off of<br>is based off of<br>is based off of<br>is based off of                                                                    | TMR3/TMR4<br>TMR3/TMR6                                   |                  |                  |                  |                 |

| bit 5-3         | 000 = ECCP<br>001 = ECCP<br>010 = ECCP<br>011 = ECCP | >: ECCP2 Time<br>2 is based off of<br>2 is based off of | of TMR1/TMR<br>of TMR3/TMR<br>of TMR3/TMR<br>of TMR3/TMR | 2<br>4<br>6<br>8 | ed on the 32-Kb  | yte device varia | ant; do not use |

- 101 = Reserved; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

- bit 2-0 C1TSEL<2:0>: ECCP1 Timer Selection bits

- 000 = ECCP1 is based off of TMR1/TMR2

- 001 = ECCP1 is based off of TMR3/TMR4

- 010 = ECCP1 is based off of TMR3/TMR6

- 011 = ECCP1 is based off of TMR3/TMR8

- 100 = ECCP1 is based off of TMR3/TMR10: option reserved on the 32-Kbyte device variant; do not use

- 101 = ECCP1 is based off of TMR3/TMR12: option reserved on the 32-Kbyte device variant; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

| R/W-0         | R/W-0                                                                                              | R/W-0            | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|------------------|--------------------|-------|--|--|--|

| TRIGSEL1      | TRIGSEL0                                                                                           | VCFG1            | VCFG0            | VNCFG             | CHSN2            | CHSN1              | CHSN0 |  |  |  |

| bit 7         |                                                                                                    |                  |                  |                   |                  |                    | bit 0 |  |  |  |

|               |                                                                                                    |                  |                  |                   |                  |                    |       |  |  |  |

| Legend:       |                                                                                                    |                  |                  |                   |                  |                    |       |  |  |  |

| R = Readable  | e bit                                                                                              | W = Writable     | bit              | U = Unimplem      | nented bit, read | d as '0'           |       |  |  |  |

| -n = Value at | POR                                                                                                | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |  |  |

|               |                                                                                                    |                  | anan Calant hita |                   |                  |                    |       |  |  |  |

| bit 7-6       |                                                                                                    |                  | ger Select bits  |                   |                  |                    |       |  |  |  |

|               | 11 = Selects the special trigger from the RTCC                                                     |                  |                  |                   |                  |                    |       |  |  |  |

|               | 10 = Selects the special trigger from the Timer1<br>01 = Selects the special trigger from the CTMU |                  |                  |                   |                  |                    |       |  |  |  |

|               |                                                                                                    |                  |                  |                   |                  |                    |       |  |  |  |

| bit 5-4       | 00 = Selects the special trigger from the ECCP2<br>VCFG<1:0>: A/D VREF+ Configuration bits         |                  |                  |                   |                  |                    |       |  |  |  |

|               | 11 = Internal VREF+ (4.096V)                                                                       |                  |                  |                   |                  |                    |       |  |  |  |

|               | 10 = Internal VREF+ (2.048V)                                                                       |                  |                  |                   |                  |                    |       |  |  |  |

|               | 01 = External VREF+                                                                                |                  |                  |                   |                  |                    |       |  |  |  |

|               | 00 <b>= AV</b> DD                                                                                  |                  |                  |                   |                  |                    |       |  |  |  |

| bit 3         | VNCFG: A/D                                                                                         | VREF- Configu    | ation bit        |                   |                  |                    |       |  |  |  |

|               | 1 = External VREF                                                                                  |                  |                  |                   |                  |                    |       |  |  |  |

|               | 0 = AVss                                                                                           |                  |                  |                   |                  |                    |       |  |  |  |

| bit 2-0       | CHSN<2:0>: Analog Negative Channel Select bits                                                     |                  |                  |                   |                  |                    |       |  |  |  |

|               | 111 = Channel 07 (AN6)                                                                             |                  |                  |                   |                  |                    |       |  |  |  |

|               | 110 = Channel 06 (AN5)                                                                             |                  |                  |                   |                  |                    |       |  |  |  |

|               | 101 = Channel 05 (AN4)                                                                             |                  |                  |                   |                  |                    |       |  |  |  |

|               | 100 = Channel 04 (AN3)                                                                             |                  |                  |                   |                  |                    |       |  |  |  |

|               | 011 = Channe                                                                                       |                  |                  |                   |                  |                    |       |  |  |  |

|               | 010 = Channe<br>001 = Channe                                                                       |                  |                  |                   |                  |                    |       |  |  |  |

|               | 000 = Channel                                                                                      | . ,              |                  |                   |                  |                    |       |  |  |  |

#### REGISTER 23-2: ADCON1: A/D CONTROL REGISTER 1

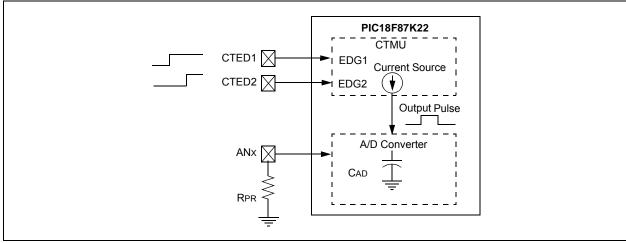

### 27.5 Measuring Capacitance with the CTMU

There are two ways to measure capacitance with the CTMU. The absolute method measures the actual capacitance value. The relative method only measures for any change in the capacitance.

#### 27.5.1 ABSOLUTE CAPACITANCE MEASUREMENT

For absolute capacitance measurements, both the current and capacitance calibration steps found in **Section 27.4 "Calibrating the CTMU Module"** should be followed.

To perform these measurements:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- 3. Set EDG1STAT.

- 4. Wait for a fixed delay, T.

- 5. Clear EDG1STAT.

- 6. Perform an A/D conversion.

- 7. Calculate the total capacitance, CTOTAL = (I \* T)/V, where:

- I is known from the current source measurement step (Section 27.4.1 "Current Source Calibration")

- · T is a fixed delay

- V is measured by performing an A/D conversion

- 8. Subtract the stray and A/D capacitance (COFFSET from Section 27.4.2 "Capacitance Calibration") from CTOTAL to determine the measured capacitance.

#### 27.5.2 RELATIVE CHARGE MEASUREMENT

Not all applications require precise capacitance measurements. When detecting a valid press of a capacitance-based switch, only a relative change of capacitance needs to be detected.

In such an application, when the switch is open (or not touched), the total capacitance is the capacitance of the combination of the board traces, the A/D Converter and other elements. A larger voltage will be measured by the A/D Converter. When the switch is closed (or touched), the total capacitance is larger due to the addition of the capacitance of the human body to the above listed capacitances and a smaller voltage will be measured by the A/D Converter.

To detect capacitance changes simply:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Wait for a fixed delay.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

The voltage measured by performing the A/D conversion is an indication of the relative capacitance. In this case, no calibration of the current source or circuit capacitance measurement is needed. (For a sample software routine for a capacitive touch switch, see Example 27-4.)

### 27.6 Measuring Time with the CTMU Module

Time can be precisely measured after the ratio  $({\rm C/I})$  is measured from the current and capacitance calibration step. To do that:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Set EDG2STAT.

- 4. Perform an A/D conversion.

- 5. Calculate the time between edges as T = (C/I) \* V, where:

- I is calculated in the current calibration step (Section 27.4.1 "Current Source Calibration")

- C is calculated in the capacitance calibration step (Section 27.4.2 "Capacitance Calibration")

- V is measured by performing the A/D conversion

It is assumed that the time measured is small enough that the capacitance, COFFSET, provides a valid voltage to the A/D Converter. For the smallest time measurement, always set the A/D Channel Select register (AD1CHS) to an unused A/D channel, the corresponding pin for which is not connected to any circuit board trace. This minimizes added stray capacitance, keeping the total circuit capacitance close to that of the A/D Converter itself (25 pF).

To measure longer time intervals, an external capacitor may be connected to an A/D channel and that channel selected whenever making a time measurement.

### FIGURE 27-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

| R/C-1                              | R/C-1                                                                                              | R/C-1                              | R/C-1                | R/C-1                                                                       | R/C-1         | R/C-1            | R/C-1 |  |

|------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|----------------------|-----------------------------------------------------------------------------|---------------|------------------|-------|--|

| CP7 <sup>(1)</sup>                 | CP6 <sup>(1)</sup>                                                                                 | CP5 <sup>(1)</sup>                 | CP4 <sup>(1)</sup>   | CP3                                                                         | CP2           | CP1              | CP0   |  |

| bit 7                              |                                                                                                    |                                    |                      |                                                                             |               |                  | bit 0 |  |

| Legend:                            |                                                                                                    | C = Clearable                      | hit                  |                                                                             |               |                  |       |  |

| R = Readabl                        | lo hit                                                                                             | W = Writable                       |                      | II – Unimploy                                                               | montod bit ro | nd as '0'        |       |  |

| -n = Value at POR '1' = Bit is set |                                                                                                    |                                    |                      | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unkno |               |                  |       |  |

|                                    | IFUK                                                                                               |                                    |                      |                                                                             | areu          | X – DIL IS ULIKI | IOWII |  |

| bit 7                              | CP7: Code F                                                                                        | Protection bit <sup>(1)</sup>      |                      |                                                                             |               |                  |       |  |

|                                    | 1 = Block 7 i                                                                                      | s not code-prot                    | ected <sup>(2)</sup> |                                                                             |               |                  |       |  |

|                                    | 0 = Block 7 i                                                                                      | s code-protecte                    | ed(2)                |                                                                             |               |                  |       |  |

| bit 6                              | CP6: Code Protection bit <sup>(1)</sup>                                                            |                                    |                      |                                                                             |               |                  |       |  |

|                                    | 1 = Block 6 is not code-protected <sup>(2)</sup>                                                   |                                    |                      |                                                                             |               |                  |       |  |

|                                    |                                                                                                    | s code-protecte                    | ed <sup>(2)</sup>    |                                                                             |               |                  |       |  |

| bit 5                              | <b>CP5:</b> Code Protection bit <sup>(1)</sup>                                                     |                                    |                      |                                                                             |               |                  |       |  |

|                                    | 1 = Block 5 is not code-protected <sup>(2)</sup><br>0 = Block 5 is code-protected <sup>(2)</sup>   |                                    |                      |                                                                             |               |                  |       |  |

| <b>b</b> :t 4                      |                                                                                                    |                                    |                      |                                                                             |               |                  |       |  |

| bit 4                              | <b>CP4:</b> Code Protection bit <sup>(1)</sup><br>1 = Block 4 is not code-protected <sup>(2)</sup> |                                    |                      |                                                                             |               |                  |       |  |

|                                    |                                                                                                    | s code-protecte                    |                      |                                                                             |               |                  |       |  |

| bit 3                              | CP3: Code F                                                                                        | Protection bit                     |                      |                                                                             |               |                  |       |  |

|                                    | 1 = Block 3 i                                                                                      | s not code-prot                    | ected <sup>(2)</sup> |                                                                             |               |                  |       |  |

|                                    | 0 = Block 3 i                                                                                      | s code-protecte                    | ed <sup>(2)</sup>    |                                                                             |               |                  |       |  |

| bit 2                              | CP2: Code F                                                                                        |                                    |                      |                                                                             |               |                  |       |  |

|                                    | 1 = Block 2 is not code-protected <sup>(2)</sup>                                                   |                                    |                      |                                                                             |               |                  |       |  |

|                                    |                                                                                                    | s code-protecte                    | ed(2)                |                                                                             |               |                  |       |  |

| bit 1                              | CP1: Code F                                                                                        |                                    | (2)                  |                                                                             |               |                  |       |  |

|                                    |                                                                                                    | s not code-prot<br>s code-protecte |                      |                                                                             |               |                  |       |  |

| bit 0                              | CP0: Code F                                                                                        | Protection bit                     |                      |                                                                             |               |                  |       |  |

|                                    |                                                                                                    | s not code-prot                    |                      |                                                                             |               |                  |       |  |

|                                    | 0 = Block 0 i                                                                                      | s code-protecte                    | ed <sup>(2)</sup>    |                                                                             |               |                  |       |  |

| Note 1: T                          | his bit is availab                                                                                 | le only on PIC1                    | 8F67K22 and          | I PIC18F87K22                                                               | devices.      |                  |       |  |

#### REGISTER 28-8: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

- This bit is available only on PIC18F67K22 and PIC18F87K22 devices. NOTE 1:

- 2: For the memory size of the blocks, see Figure 28-6.

#### REGISTER 28-9: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1                              | R/C-1       | U-0            | U-0                                     | U-0 | U-0 | U-0 | U-0   |  |

|------------------------------------|-------------|----------------|-----------------------------------------|-----|-----|-----|-------|--|

| CPD                                | CPB         | —              | _                                       | —   | _   | _   | —     |  |

| bit 7                              | ·           |                |                                         |     | •   | ·   | bit 0 |  |

|                                    |             |                |                                         |     |     |     |       |  |

| Legend: C = Clearable bit          |             |                |                                         |     |     |     |       |  |

| R = Readable bit W = Writable bit  |             |                | U = Unimplemented bit, read as '0'      |     |     |     |       |  |

| -n = Value at POR '1' = Bit is set |             |                | '0' = Bit is cleared x = Bit is unknown |     |     |     |       |  |

|                                    |             |                |                                         |     |     |     |       |  |

| bit 7                              | CPD: Data E | EPROM Code I   | Protection bit                          |     |     |     |       |  |

|                                    | 1 = Data EE | PROM is not co | de-protected                            |     |     |     |       |  |

- 0 = Data EEPROM is code-protected

- bit 6 **CPB:** Boot Block Code Protection bit 1 = Boot block is not code-protected<sup>(1)</sup> 0 = Boot block is code-protected<sup>(1)</sup>

- bit 5-0 Unimplemented: Read as '0'

Note 1: For the memory size of the blocks, see Figure 28-6. The boot block size changes with BBSIZO.

| BTFS         | SC                                                                                                                                                  | Bit Test File                                                                  | , Skip if Clear                                                                                                             |                                                                  | BTFS  | SS                                                                           | Bit Test File                                                                                                                                                                                                                                                          | , Skip if Set                                                                                                                   |                                                              |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| Synta        | ax:                                                                                                                                                 | BTFSC f, b                                                                     | {,a}                                                                                                                        |                                                                  | Synta | ax:                                                                          | BTFSS f, b {                                                                                                                                                                                                                                                           | ,a}                                                                                                                             |                                                              |  |

| Opera        | ands:                                                                                                                                               | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0, 1]$                         |                                                                                                                             | Oper                                                             | ands: | $0 \le f \le 255$<br>$0 \le b < 7$                                           |                                                                                                                                                                                                                                                                        |                                                                                                                                 |                                                              |  |