Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65k22t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                              | Pin Number              | Pin                | Buffer                           | Description                                                                                                                 |  |  |  |

|-------------------------------------------------------|-------------------------|--------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                              | QFN/TQFP                | Туре Туре          |                                  | Description                                                                                                                 |  |  |  |

|                                                       |                         |                    |                                  | PORTF is a bidirectional I/O port.                                                                                          |  |  |  |

| RF1/AN6/C2OUT/CTDIN<br>RF1<br>AN6<br>C2OUT<br>CTDIN   | 17                      | I/O<br> <br>0<br>  | ST<br>Analog<br>—<br>ST          | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.<br>CTMU pulse delay input.                                          |  |  |  |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT                  | 16                      | I/O<br>I<br>O      | ST<br>Analog<br>—                | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                                                                     |  |  |  |

| RF3/AN8/C2INB/CTMUI<br>RF3<br>AN8<br>C2INB<br>CTMUI   | 15                      | I/O<br> <br> <br>0 | ST<br>Analog<br>Analog<br>—      | Digital I/O.<br>Analog Input 8.<br>Comparator 2 Input B.<br>CTMU pulse generator charger for the C2INB<br>comparator input. |  |  |  |

| RF4/AN9/C2INA<br>RF4<br>AN9<br>C2INA                  | 14                      | I/O<br> <br>       | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog Input 9.<br>Comparator 2 Input A.                                                                    |  |  |  |

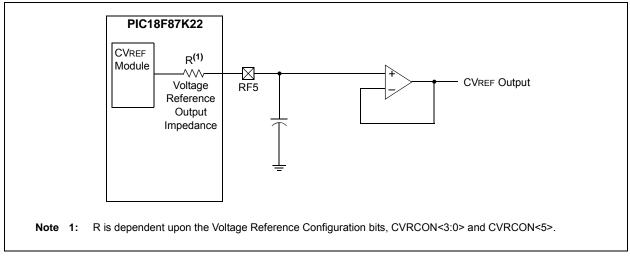

| RF5/AN10/CVREF/C1INB<br>RF5<br>AN10<br>CVREF<br>C1INB | 13                      | I/O<br> <br>0<br>  | ST<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.<br>Comparator 1 Input B.                           |  |  |  |

| RF6/AN11/C1INA<br>RF6<br>AN11<br>C1INA                | 12                      | I/O<br> <br>       | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog Input 11.<br>Comparator 1 Input A.                                                                   |  |  |  |

| RF7/AN5/SS1<br>RF7<br><u>AN5</u><br>SS1               | 11                      | I/O<br>O<br>I      | ST<br>Analog<br>TTL              | Digital I/O.<br>Analog Input 5.<br>SPI1 slave select input.                                                                 |  |  |  |

| I = Input<br>P = Power<br>$I^2C = I^2C^{TM}/SI$       | Trigger input w<br>MBus |                    |                                  | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)        |  |  |  |

| TABLE 1-3: | PIC18F6XK22 PINOUT I/O DESCRIPTIONS ( | CONTINUED) | ١ |

|------------|---------------------------------------|------------|---|

|            |                                       |            | , |

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

| Pin Name                                                          | Pin Number              | Pin Bu    | Buffer  | Description                                                                                                          |  |  |  |

|-------------------------------------------------------------------|-------------------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                   | TQFP                    | Туре Туре |         | Description                                                                                                          |  |  |  |

|                                                                   |                         |           |         | PORTJ is a bidirectional I/O port.                                                                                   |  |  |  |

| RJ0/ALE<br>RJ0<br>ALE                                             | 62                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External memory address latch enable.                                                                |  |  |  |

| RJ1/OE<br>RJ1<br>OE                                               | 61                      | I/O<br>O  | ST      | Digital I/O.<br>External memory output enable.                                                                       |  |  |  |

| RJ2/WRL<br>RJ2<br>WRL                                             | 60                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External memory write low control.                                                                   |  |  |  |

| RJ3/WRH<br>RJ3<br>WRH                                             | 59                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External memory high control.                                                                        |  |  |  |

| RJ4/BA0<br>RJ4<br>BA0                                             | 39                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External Memory Byte Address 0 control                                                               |  |  |  |

| RJ5/CE<br>RJ5<br>CE                                               | 40                      | I/O<br>O  | ST<br>— | Digital I/O<br>External memory chip enable control.                                                                  |  |  |  |

| RJ6/LB<br>RJ6<br>LB                                               | 41                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External memory low byte control.                                                                    |  |  |  |

| RJ7/UB<br>RJ7<br>UB                                               | 42                      | I/O<br>O  | ST<br>— | Digital I/O.<br>External memory high byte control.                                                                   |  |  |  |

| Vss                                                               | 11, 31, 51, 70          | Р         | —       | Ground reference for logic and I/O pins.                                                                             |  |  |  |

| VDD                                                               | 32, 48, 71              | Р         | —       | Positive supply for logic and I/O pins.                                                                              |  |  |  |

| AVss                                                              | 26                      | Р         |         | Ground reference for analog modules.                                                                                 |  |  |  |

| AVDD                                                              | 25                      | P         |         | Positive supply for analog modules.                                                                                  |  |  |  |

| ENVREG<br>Vddcore/Vcap                                            | 24<br>12                | I         | ST      | Enable for on-chip voltage regulator.<br>Core logic power or external filter capacitor connection.                   |  |  |  |

| Vddcore<br>Vcap                                                   |                         | Ρ         | _       | External filter capacitor connection (regulator enabled/disabled).                                                   |  |  |  |

| I = Input<br>P = Power<br>I <sup>2</sup> C = I <sup>2</sup> C™/SM | rigger input wit<br>Bus |           |         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |  |

#### PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

### 6.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit (CONFIG4L<0>). When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

### 6.1.4 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR                               |

|-----------------|--------------------------------------------------|

| •               | ;SAVED IN FAST REGISTER                          |

| SUB1 •          | ;STACK                                           |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK |

### 6.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 6.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the Program Counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value, 'nn', to the calling function.

The offset value (in WREG) specifies the number of bytes that the Program Counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

### 6.1.5.2 Table Reads

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored, two bytes per program word, while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory, one byte at a time.

The table read operation is discussed further in **Section 7.1 "Table Reads and Table Writes**".

### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. For more information, see         |

|       | Section 6.6 "Data Memory and the           |

|       | Extended Instruction Set"                  |

While the program memory can be addressed in only one way, through the Program Counter, information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). For details on this mode's operation, see **Section 6.6.1 "Indexed Addressing with Literal Offset**".

### 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all. They either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples of this mode include SLEEP, RESET and DAW.

Other instructions work in a similar way, but require an additional explicit argument in the opcode. This method is known as the Literal Addressing mode because the instructions require some literal value as an argument. Examples of this include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byte-oriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies the instruction's data source as either a register address in one of the banks of data RAM (see Section 6.3.3 "General Purpose Register File") or a location in the Access Bank (see Section 6.3.2 "Access Bank").

The Access RAM bit, 'a', determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit, 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction, either the target register being operated on or the W register.

### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code using loops, such as the example of clearing an entire RAM bank in Example 6-5. It also enables users to perform Indexed Addressing and other Stack Pointer operations for program memory in data memory.

### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0, 100h | ; |                |

|---------|-------|------------|---|----------------|

| NEXT    | CLRF  | POSTINC0   | ; | Clear INDF     |

|         |       |            | ; | register then  |

|         |       |            | ; | inc pointer    |

|         | BTFSS | FSROH, 1   | ; | All done with  |

|         |       |            | ; | Bank1?         |

|         | BRA   | NEXT       | ; | NO, clear next |

| CONTINU | JE    |            | ; | YES, continue  |

|         |       |            |   |                |

### 8.6.4 16-BIT MODE TIMING

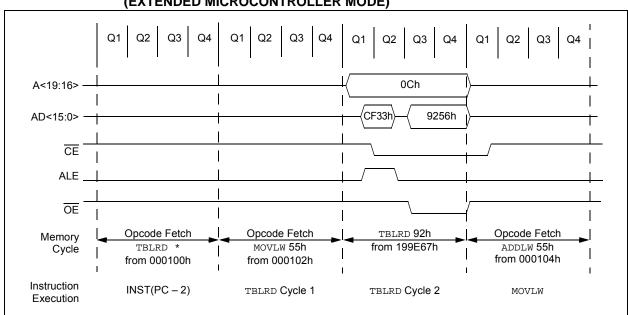

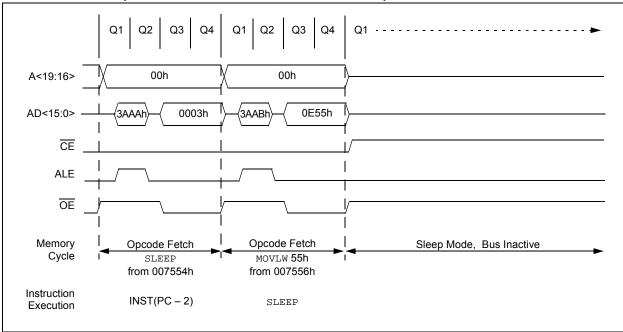

The presentation of control signals on the External Memory Bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 8-4 and Figure 8-5.

### FIGURE 8-4: EXTERNAL MEMORY BUS TIMING FOR TBLRD (EXTENDED MICROCONTROLLER MODE)

### FIGURE 8-5: EXTERNAL MEMORY BUS TIMING FOR SLEEP (EXTENDED MICROCONTROLLER MODE)

| R/W-0                                                  | U-0                                      | R-0              | R-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------------------------------------------------|------------------------------------------|------------------|-----------------|-------------------|-----------------|-----------------|--------|

| TMR5GIE                                                | —                                        | RC2IE            | TX2IE           | CTMUIE            | CCP2IE          | CCP1IE          | RTCCIE |

| bit 7                                                  |                                          |                  |                 |                   |                 |                 | bit 0  |

|                                                        |                                          |                  |                 |                   |                 |                 |        |

| Legend:                                                |                                          |                  |                 |                   |                 |                 |        |

| R = Readable                                           | e bit                                    | W = Writable     | bit             | U = Unimplem      | nented bit, rea | d as '0'        |        |

| -n = Value at                                          | POR                                      | '1' = Bit is set |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |

| bit 7                                                  | TMR5GIF: Tir                             | ner5 Gate Inter  | rupt Enable bit | ·                 |                 |                 |        |

|                                                        | 1 = Enabled                              |                  |                 |                   |                 |                 |        |

|                                                        | 0 = Disabled                             |                  |                 |                   |                 |                 |        |

| bit 6                                                  | Unimplement                              | ted: Read as '   | כי              |                   |                 |                 |        |

| bit 5                                                  | RC2IE: EUSA                              | RT Receive In    | terrupt Enable  | bit               |                 |                 |        |

|                                                        | 1 = Enabled                              |                  |                 |                   |                 |                 |        |

|                                                        | 0 = Disabled                             |                  |                 |                   |                 |                 |        |

| bit 4                                                  |                                          | RT Transmit Ir   | iterrupt Enable | e bit             |                 |                 |        |

|                                                        | 1 = Enabled<br>0 = Disabled              |                  |                 |                   |                 |                 |        |

| bit 3                                                  | CTMUIE: CTMU Interrupt Enable bit        |                  |                 |                   |                 |                 |        |

|                                                        | 1 = Enabled                              |                  |                 |                   |                 |                 |        |

|                                                        | 0 = Disabled                             |                  |                 |                   |                 |                 |        |

| bit 2                                                  | CCP2IE: ECC                              | P2 Interrupt E   | nable bit       |                   |                 |                 |        |

| 1 = Enabled                                            |                                          |                  |                 |                   |                 |                 |        |

|                                                        | 0 = Disabled                             |                  |                 |                   |                 |                 |        |

| bit 1                                                  | bit 1 CCP1IE: ECCP1 Interrupt Enable bit |                  |                 |                   |                 |                 |        |

|                                                        | 1 = Enabled<br>0 = Disabled              |                  |                 |                   |                 |                 |        |

| bit 0 RTCCIE: RTCC Interrupt Enable bit<br>1 = Enabled |                                          |                  |                 |                   |                 |                 |        |

|                                                        |                                          |                  |                 |                   |                 |                 |        |

|                                                        | 0 = Disabled                             |                  |                 |                   |                 |                 |        |

|                                                        |                                          |                  |                 |                   |                 |                 |        |

### REGISTER 11-12: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

### REGISTER 11-13: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| R/W-0                              | R/W-0                 | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|------------------------------------|-----------------------|-----------------------------------------|------------------------------------|--------|--------|--------|--------|

| CCP10IE <sup>(1)</sup>             | CCP9IE <sup>(1)</sup> | CCP8IE                                  | CCP7IE                             | CCP6IE | CCP5IE | CCP4IE | CCP3IE |

| bit 7                              | •                     | •                                       |                                    | •      |        | •      | bit 0  |

|                                    |                       |                                         |                                    |        |        |        |        |

| Legend:                            |                       |                                         |                                    |        |        |        |        |

| R = Readable bit W = Writable bit  |                       |                                         | U = Unimplemented bit, read as '0' |        |        |        |        |

| -n = Value at POR '1' = Bit is set |                       | '0' = Bit is cleared x = Bit is unknown |                                    |        |        |        |        |

bit 7-0 CCP<10:3>IE: CCP<10:3> Interrupt Enable bits<sup>(1)</sup>

- 1 = Enabled

- 0 = Disabled

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

### 12.3 PORTB, TRISB and LATB Registers

PORTB is an eight-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISB and LATB. All pins on PORTB are digital only.

| CLRF PORTB  | ; Initialize PORTB by<br>; clearing output<br>; data latches |

|-------------|--------------------------------------------------------------|

| CLRF LATB   | ; Alternate method                                           |

| -           | ; to clear output                                            |

|             | ; data latches                                               |

| MOVLW 0CFh  | ; Value used to                                              |

|             | ; initialize data                                            |

|             | ; direction                                                  |

| MOVWF TRISB | ; Set RB<3:0> as inputs                                      |

|             | ; RB<5:4> as outputs                                         |

|             | ; RB<7:6> as inputs                                          |

|             |                                                              |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur. Any RB<7:4> pin configured as an output will be excluded from the interrupt-on-change comparison.

Comparisons with the input pins (of RB<7:4>) are made with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. To clear the interrupt in the Interrupt Service Routine:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Wait one instruction cycle (such as executing a NOP instruction).

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared after one Tcy delay.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

The RB<3:2> pins are multiplexed as CTMU edge inputs. RB5 has an additional function for Timer3 and Timer1. It can be configured for Timer3 clock input or Timer1 external clock gate input.

| Pin Name       | Function         | TRIS<br>Setting | I/O                                               | I/O<br>Type                            | Description                                                 |  |  |

|----------------|------------------|-----------------|---------------------------------------------------|----------------------------------------|-------------------------------------------------------------|--|--|

| RB0/INT0/FLT0  | RB0              | 0               | 0                                                 | DIG                                    | LATB<0> data output.                                        |  |  |

|                |                  | 1               | I TTL PORTB<0> data input; weak pull-up when RBPL |                                        | PORTB<0> data input; weak pull-up when RBPU bit is cleared. |  |  |

| INTO           |                  | 1               | I                                                 | ST                                     | External Interrupt 0 input.                                 |  |  |

|                | FLT0             | x               | Ι                                                 | ST Enhanced PWM Fault input for ECCPx. |                                                             |  |  |

| RB1/INT1       | RB1 0 O DIG LATB |                 | DIG                                               | LATB<1> data output.                   |                                                             |  |  |

|                |                  | 1               | Ι                                                 | TTL                                    | PORTB<1> data input; weak pull-up when RBPU bit is cleared. |  |  |

|                | INT1             | 1               | Ι                                                 | ST                                     | External Interrupt 1 input.                                 |  |  |

| RB2/INT2/CTED1 | RB2              | 0               | 0                                                 | DIG                                    | LATB<2> data output.                                        |  |  |

|                |                  | 1               | Ι                                                 | TTL                                    | PORTB<2> data input; weak pull-up when RBPU bit is cleared. |  |  |

|                | INT2             | 1               | Ι                                                 | ST                                     | External Interrupt 2 input.                                 |  |  |

|                | CTED1            | x               | Ι                                                 | ST                                     | CTMU Edge 1 input.                                          |  |  |

### TABLE 12-3: PORTB FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,

TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared and in Extended Microcontroller mode.

## 12.4 PORTC, TRISC and LATC Registers

PORTC is an eight-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISC and LATC. Only PORTC pins, RC2 through RC7, are digital only pins.

PORTC is multiplexed with ECCP, MSSP and EUSART peripheral functions (Table 12-5). The pins have Schmitt Trigger input buffers. The pins for ECCP, SPI and EUSART are also configurable for open-drain output whenever these functions are active. Open-drain configuration is selected by setting the SPIOD, CCPxOD and U1OD control bits in the registers, ODCON1 and ODCON3.

RC1 is normally configured as the default peripheral pin for the ECCP2 module. The assignment of ECCP2 is controlled by Configuration bit, CCP2MX (default state, CCP2MX = 1). When enabling peripheral functions, use care in defining TRIS bits for each PORTC pin. Some peripherals can override the TRIS bit to make a pin an output or input. Consult the corresponding peripheral section for the correct TRIS bit settings.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

| EXAMPLE 12-3: | INITIALIZING PORTC |

|---------------|--------------------|

|               |                    |

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATC  | ; Alternate method                         |

| CLRF  | LAIC  | , Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                    |

|       |       | ; RC<5:4> as outputs                       |

|       |       | ; RC<7:6> as inputs                        |

|       |       |                                            |

| Pin Name    | Function | TRIS<br>Setting | I/O | I/O<br>Type                                                              | Description                                                                                                                                     |  |  |  |

|-------------|----------|-----------------|-----|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RC0/SOSCO/  | RC0      | 0               | 0   | DIG                                                                      | LATC<0> data output.                                                                                                                            |  |  |  |

| SCLKI/      |          | 1               | Ι   | ST                                                                       | PORTC<0> data input.                                                                                                                            |  |  |  |

|             | SOSCO    | 1               | Ι   | ST                                                                       | SOSC oscillator output.                                                                                                                         |  |  |  |

| SCLKI 1     |          |                 | Ι   | ST                                                                       | Digital clock input; enabled when SOSC oscillator is disabled.                                                                                  |  |  |  |

|             |          |                 |     | DIG                                                                      | LATC<1> data output.                                                                                                                            |  |  |  |

| ECCP2/P2A 1 |          |                 | Ι   | ST                                                                       | PORTC<1> data input.                                                                                                                            |  |  |  |

|             | x        | Ι               | ANA | SOSC oscillator input.                                                   |                                                                                                                                                 |  |  |  |

|             | 0        | 0               | DIG | ECCP2 compare output and ECCP2 PWM output; takes priority over port data |                                                                                                                                                 |  |  |  |

|             |          | 1               | Ι   | ST                                                                       | ECCP2 capture input.                                                                                                                            |  |  |  |

|             | P2A      | 0               | 0   | DIG                                                                      | ECCP2 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown events; takes<br>priority over port data. |  |  |  |

| RC2/ECCP1/  | RC2      | 0               | 0   | DIG                                                                      | LATC<2> data output.                                                                                                                            |  |  |  |

| P1A         |          | 1               | Ι   | ST                                                                       | PORTC<2> data input.                                                                                                                            |  |  |  |

|             | ECCP1    | 0               | 0   | DIG                                                                      | ECCP1 compare output and ECCP1 PWM output; takes priority over port data.                                                                       |  |  |  |

|             |          | 1               | Ι   | ST                                                                       | ECCP1 capture input.                                                                                                                            |  |  |  |

|             | P1A      | 0               | 0   | DIG                                                                      | ECCP1 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown events; takes<br>priority over port data. |  |  |  |

### TABLE 12-5: PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $I^2C = I^2C^{TM}$ /SMBus Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

### 16.1 Timer3/5/7 Gate Control Register

The Timer3/5/7 Gate Control register (TxGCON), provided in Register 14-2, is used to control the Timerx gate.

### REGISTER 16-2: TxGCON: TIMERx GATE CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0        | R-x    | R/W-0  | R/W-0  |

|--------|--------|-------|--------|--------------|--------|--------|--------|

| TMRxGE | TxGPOL | TxGTM | TxGSPM | TxGGO/TxDONE | TxGVAL | TxGSS1 | TxGSS0 |

| bit 7  | •      |       |        |              |        |        | bit 0  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| Note 1: | Programming the TxGCON prior to TxCON is recommended.                                                                                                                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Comparator 2 output</li> <li>10 = Comparator 1 output</li> <li>01 = TMR(x+1) to match PR(x+1) output<sup>(2)</sup></li> <li>00 = Timer1 gate pin</li> <li>The Watchdog Timer oscillator is turned on if TMRxGE = 1, regardless of the state of TMRxON.</li> </ul> |

| bit 1-0 | TxGSS<1:0>: Timerx Gate Source Select bits                                                                                                                                                                                                                                      |

| bit 2   | <b>TxGVAL:</b> Timerx Gate Current State bit<br>Indicates the current state of the Timerx gate that could be provided to TMRxH:TMRxL. Unaffected by the<br>Timerx Gate Enable (TMRxGE) bit.                                                                                     |

|         | <ul> <li>1 = Timerx gate single pulse acquisition is ready, waiting for an edge</li> <li>0 = Timerx gate single pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when TxGSPM is cleared.</li> </ul>                           |

| bit 3   | TxGGO/TxDONE: Timerx Gate Single Pulse Acquisition Status bit                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Timerx Gate Single Pulse mode is enabled and is controlling Timerx gate</li> <li>0 = Timerx Gate Single Pulse mode is disabled</li> </ul>                                                                                                                          |

| bit 4   | TxGSPM: Timerx Gate Single Pulse Mode bit                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Timerx Gate Toggle mode is enabled.</li> <li>0 = Timerx Gate Toggle mode is disabled and toggle flip-flop is cleared</li> <li>Timerx gate flip-flop toggles on every rising edge.</li> </ul>                                                                       |

| bit 5   | TxGTM: Timerx Gate Toggle Mode bit                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Timerx gate is active-high (Timerx counts when gate is high)</li> <li>0 = Timerx gate is active-low (Timerx counts when gate is low)</li> </ul>                                                                                                                    |

| bit 6   | TxGPOL: Timerx Gate Polarity bit                                                                                                                                                                                                                                                |

|         | This bit is ignored.<br><u>If TMRxON = 1:</u><br>1 = Timerx counting is controlled by the Timerx gate function<br>0 = Timerx counts regardless of Timerx gate function                                                                                                          |

| DIT /   | If TMRxON = 0:                                                                                                                                                                                                                                                                  |

| bit 7   | TMRxGE: Timerx Gate Enable bit                                                                                                                                                                                                                                                  |

2: Timer(x+1) will be Timer4/6/8 for Timerx (Timer3/5/7), respectively.

### 16.5 Timer3/5/7 Gates

Timer3/5/7 can be configured to count freely or the count can be enabled and disabled using the Timer3/5/7 gate circuitry. This is also referred to as the Timer3/5/7 gate count enable.

The Timer3/5/7 gate can also be driven by multiple selectable sources.

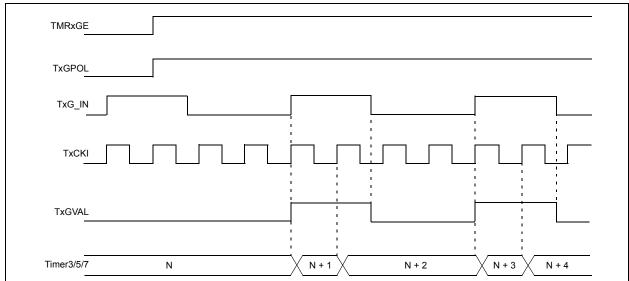

### 16.5.1 TIMER3/5/7 GATE COUNT ENABLE

The Timerx Gate Enable mode is enabled by setting the TMRxGE bit (TxGCON<7>). The polarity of the Timerx Gate Enable mode is configured using the TxGPOL bit (TxGCON<6>).

When Timerx Gate Enable mode is enabled, Timer3/5/7 will increment on the rising edge of the Timer3/5/7 clock source. When Timerx Gate Enable mode is disabled, no incrementing will occur and Timer3/5/7 will hold the current count. See Figure 16-2 for timing details.

### TABLE 16-1: TIMER3/5/7 GATE ENABLE SELECTIONS

| TxCLK <sup>(†)</sup> | TxGPOL<br>(TxGCON<6>) | TxG Pin | Timerx<br>Operation |  |

|----------------------|-----------------------|---------|---------------------|--|

| 1                    | 0                     | 0       | Counts              |  |

| $\uparrow$           | 0                     | 1       | Holds Count         |  |

| $\uparrow$           | 1                     | 0       | Holds Count         |  |

| $\uparrow$           | 1                     | 1       | Counts              |  |

† The clock on which TMR3/5/7 is running. For more information, see TxCLK in Figure 16-1.

### FIGURE 16-2: TIMER3/5/7 GATE COUNT ENABLE MODE

### TABLE 20-4: REGISTERS ASSOCIATED WITH ECCP1/2/3 MODULE AND TIMER1/2/3/4/6/8/10/12 (CONTINUED)

| File Name             | Bit 7         | Bit 6                                                               | Bit 5          | Bit 4     | Bit 3     | Bit 2   | Bit 1    | Bit 0    |  |  |  |

|-----------------------|---------------|---------------------------------------------------------------------|----------------|-----------|-----------|---------|----------|----------|--|--|--|

| T1CON                 | TMR1CS1       | TMR1CS0                                                             | T1CKPS1        | T1CKPS0   | SOSCEN    | T1SYNC  | RD16     | TMR10N   |  |  |  |

| T2CON                 | _             | T2OUTPS3                                                            | T2OUTPS2       | T2OUTPS1  | T2OUTPS0  | TMR2ON  | T2CKPS1  | T2CKPS0  |  |  |  |

| T3CON                 | TMR3CS1       | TMR3CS0                                                             | T3CKPS1        | T3CKPS0   | SOSCEN    | T3SYNC  | RD16     | TMR3ON   |  |  |  |

| T4CON                 | —             | T4OUTPS3                                                            | T4OUTPS2       | T4OUTPS1  | T4OUTPS0  | TMR4ON  | T4CKPS1  | T4CKPS0  |  |  |  |

| T6CON                 | _             | T6OUTPS3                                                            | T6OUTPS2       | T6OUTPS1  | T6OUTPS0  | TMR6ON  | T6CKPS1  | T6CKPS0  |  |  |  |

| T8CON                 | —             | T8OUTPS3                                                            | T8OUTPS2       | T8OUTPS1  | T8OUTPS0  | TMR8ON  | T8CKPS1  | T8CKPS0  |  |  |  |

| T10CON <sup>(1)</sup> | —             | T10OUTPS3                                                           | T10OUTPS2      | T10OUTPS1 | T10OUTPS0 | TMR100N | T10CKPS1 | T10CKPS0 |  |  |  |

| T12CON <sup>(1)</sup> |               | - T120UTPS3 T120UTPS2 T120UTPS1 T120UTPS0 TMR120N T12CKPS1 T12CKPS0 |                |           |           |         |          |          |  |  |  |

| CCPR1H                | Capture/Compa | re/PWM Regis                                                        | ter 1 High Byt | e         |           |         |          |          |  |  |  |

| CCPR1L                | Capture/Compa | re/PWM Regis                                                        | ter 1 Low Byte | е         |           |         |          |          |  |  |  |

| CCPR2H                | Capture/Compa | re/PWM Regis                                                        | ter 2 High Byt | e         |           |         |          |          |  |  |  |

| CCPR2L                | Capture/Compa | re/PWM Regis                                                        | ter 2 Low Byte | е         |           |         |          |          |  |  |  |

| CCPR3H                | Capture/Compa | re/PWM Regis                                                        | ter 3 High Byt | e         |           |         |          |          |  |  |  |

| CCPR3L                | Capture/Compa | re/PWM Regis                                                        | ter 3 Low Byte | е         |           |         |          |          |  |  |  |

| CCP1CON               | P1M1          | P1M0                                                                | DC1B1          | DC1B0     | CCP1M3    | CCP1M2  | CCP1M1   | CCP1M0   |  |  |  |

| CCP2CON               | P2M1          | P2M0                                                                | DC2B1          | DC2B0     | CCP2M3    | CCP2M2  | CCP2M1   | CCP2M0   |  |  |  |

| CCP3CON               | CCP3MD        | CCP2MD                                                              | CCP1MD         | UART2MD   | UART1MD   | SSP2MD  | SSP1MD   | ADCMD    |  |  |  |

| PMD0                  | CCP3MD        | CCP2MD                                                              | CCP1MD         | UART2MD   | UART1MD   | SSP2MD  | SSP1MD   | ADCMD    |  |  |  |

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18F65K22 and PIC18F85K22).

2: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

### 21.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

### REGISTER 21-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

|            |                                                   |                                                          |                | <b>\</b> -       | ,                          |                 |               |

|------------|---------------------------------------------------|----------------------------------------------------------|----------------|------------------|----------------------------|-----------------|---------------|

| R/W-0      | R/W-0                                             | R-0                                                      | R-0            | R-0              | R-0                        | R-0             | R-0           |

| SMP        | CKE <sup>(1)</sup>                                | D/A                                                      | Р              | S                | R/W                        | UA              | BF            |

| bit 7      |                                                   |                                                          |                |                  |                            |                 | bit (         |

|            |                                                   |                                                          |                |                  |                            |                 |               |

| Legend:    |                                                   |                                                          |                |                  |                            |                 |               |

| R = Reada  |                                                   | W = Writable                                             |                |                  | mented bit, rea            |                 |               |

| -n = Value | at POR                                            | '1' = Bit is set                                         |                | '0' = Bit is cle | ared                       | x = Bit is unkr | nown          |

| bit 7      | 0 = Input dat<br><u>SPI Slave m</u>               | <u>node:</u><br>a is sampled at<br>a is sampled at       | the middle of  | data output tim  | e                          |                 |               |

| bit 6      |                                                   | ock Select bit <sup>(1)</sup>                            |                |                  |                            |                 |               |

| bit 5      | 1 = Transmit                                      | occurs on the t<br>occurs on the t<br>ddress bit         | ransition from |                  |                            |                 |               |

| bit 4      | P: Stop bit                                       |                                                          | bit is cleared | when the MSSI    | <sup>o</sup> x module is d | isabled; SSPEN  | l is cleared. |

| bit 3      | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C r |                                                          |                |                  |                            |                 |               |

| bit 2      | <b>R/W:</b> Read/V<br>Used in I <sup>2</sup> C r  | Vrite Information mode only.                             | n bit          |                  |                            |                 |               |

| bit 1      | <b>UA:</b> Update<br>Used in I <sup>2</sup> C r   |                                                          |                |                  |                            |                 |               |

| bit 0      | <b>BF:</b> Buffer Fi                              | ull Status bit (Re<br>is complete, SS<br>is not complete | PxBUF is full  | • •              |                            |                 |               |

| Note di    |                                                   |                                                          |                |                  |                            |                 |               |

**Note 1:** Polarity of clock state is set by the CKP bit (SSPxCON1<4>).

### 21.4.10 I<sup>2</sup>C<sup>™</sup> MASTER MODE TRANSMISSION

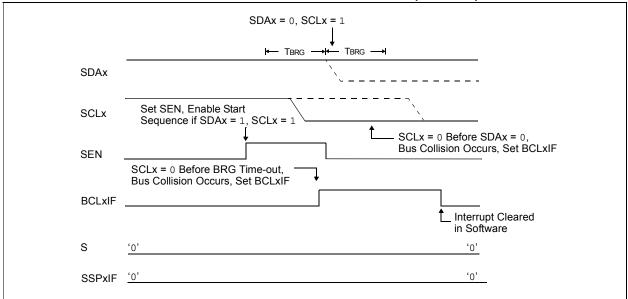

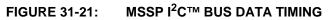

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted (see data hold time specification Parameter 106). SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high (see data setup time specification Parameter 107). When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 21-23).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPxCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPxIF flag is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

### 21.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPxSTAT<0>) is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

### 21.4.10.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TCY after the SSPxBUF write. If SSPxBUF is rewritten within 2 TCY, the WCOL bit is set and SSPxBUF is updated. This may result in a corrupted transfer.

The user should verify that the WCOL bit is clear after each write to SSPxBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

### 21.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPxCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

### 21.4.11 I<sup>2</sup>C<sup>™</sup> MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPxCON2<3>).

Note: The MSSP module must be in an inactive state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting, and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPxCON2<4>).

### 21.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

### 21.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

### 21.4.11.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

# PIC18F87K22 FAMILY

| R/W-0             | R-1                                          | R/W-0                                                  | R/W-0            | R/W-0                             | U-0             | R/W-0           | R/W-0           |  |  |  |

|-------------------|----------------------------------------------|--------------------------------------------------------|------------------|-----------------------------------|-----------------|-----------------|-----------------|--|--|--|

| ABDOVF            | RCIDL                                        | RXDTP                                                  | TXCKP            | BRG16                             | _               | WUE             | ABDEN           |  |  |  |

| bit 7             |                                              |                                                        |                  |                                   |                 |                 | bit             |  |  |  |

| Legend:           |                                              |                                                        |                  |                                   |                 |                 |                 |  |  |  |

| R = Readabl       | e bit                                        | W = Writable                                           | bit              | U = Unimplem                      | ented bit, read | d as '0'        |                 |  |  |  |

| -n = Value at POR |                                              | '1' = Bit is set                                       |                  | ʻ0' = Bit is clea                 | red             | x = Bit is unki | nown            |  |  |  |

| bit 7             |                                              | to-Baud Acquis                                         |                  | Status bit<br>uto-Baud Rate I     | Detect mode (I  | must be cleare  | d in software)  |  |  |  |

|                   | 0 = No BRG                                   | rollover has oc                                        | curred           |                                   |                 |                 |                 |  |  |  |

| bit 6             |                                              | ive Operation I                                        |                  |                                   |                 |                 |                 |  |  |  |

|                   |                                              | peration is Idle                                       |                  |                                   |                 |                 |                 |  |  |  |

| bit 5             | RXDTP: Data                                  | /Receive Polar                                         | ity Select bit   |                                   |                 |                 |                 |  |  |  |

|                   |                                              | <u>s mode:</u><br>lata (RXx) is in<br>lata (RXx) is no |                  |                                   |                 |                 |                 |  |  |  |

|                   |                                              | mode:<br><) is inverted (a<br><) is not inverte        |                  |                                   |                 |                 |                 |  |  |  |

| bit 4             | TXCKP: Synchronous Clock Polarity Select bit |                                                        |                  |                                   |                 |                 |                 |  |  |  |

|                   | Asynchronous<br>1 = Idle state               |                                                        | (x) is a low lev | el                                |                 |                 |                 |  |  |  |

|                   |                                              | <u>mode:</u><br>for clock (CKx)<br>for clock (CKx)     |                  |                                   |                 |                 |                 |  |  |  |

| bit 3             | <b>BRG16:</b> 16-B                           | it Baud Rate R                                         | egister Enable   | bit                               |                 |                 |                 |  |  |  |

|                   |                                              |                                                        |                  | Hx and SPBRGA                     |                 | RGHx value ig   | nored           |  |  |  |

| bit 2             | Unimplemen                                   | ted: Read as '                                         | )'               |                                   |                 |                 |                 |  |  |  |

| bit 1             | WUE: Wake-u                                  | up Enable bit                                          |                  |                                   |                 |                 |                 |  |  |  |

|                   | hardware                                     |                                                        | sing edge        | RXx pin – interru<br>letected     | ipt generated   | on falling edge | ; bit cleared i |  |  |  |

|                   | Synchronous<br>Unused in this                |                                                        |                  |                                   |                 |                 |                 |  |  |  |

| bit 0             |                                              | -Baud Detect I                                         | -<br>nable bit   |                                   |                 |                 |                 |  |  |  |

|                   | Asynchronous<br>1 = Enable b<br>cleared ir   | <u>s mode:</u><br>aud rate meas<br>ı hardware upo      | urement on the   | e next character<br>has completed | r. Requires re  | ception of a Sy | ync field (55h  |  |  |  |

|                   | Synchronous<br>Unused in this                |                                                        |                  |                                   |                 |                 |                 |  |  |  |

### FIGURE 25-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### TABLE 25-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|--------|---------|---------|---------|---------|---------|---------|--------|--------|

| CVRCON | CVREN   | CVROE   | CVRSS   | CVR4    | CVR3    | CVR2    | CVR1   | CVR0   |

| CM1CON | CON     | COE     | CPOL    | EVPOL1  | EVPOL0  | CREF    | CCH1   | CCH0   |

| CM2CON | CON     | COE     | CPOL    | EVPOL1  | EVPOL0  | CREF    | CCH1   | CCH0   |

| CM3CON | CON     | COE     | CPOL    | EVPOL1  | EVPOL0  | CREF    | CCH1   | CCH0   |

| TRISF  | TRISF7  | TRISF6  | TRISF5  | TRISF4  | TRISF3  | TRISF2  | TRISF1 | —      |

| TRISA  | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1 | TRISA0 |

| ANCON0 | ANSEL7  | ANSEL6  | ANSEL5  | ANSEL4  | ANSEL3  | ANSEL2  | ANSEL1 | ANSEL0 |

| ANCON1 | ANSEL15 | ANSEL14 | ANSEL13 | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9 | ANSEL8 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

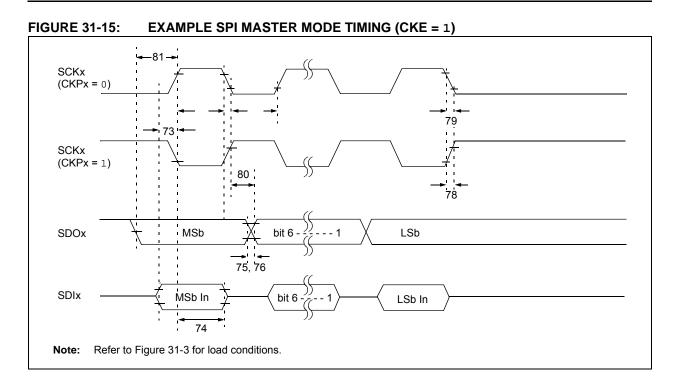

| Param.<br>No. | Symbol                | Characteristic                                            | Min          | Max | Units | Conditions |

|---------------|-----------------------|-----------------------------------------------------------|--------------|-----|-------|------------|

| 73            | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                | 20           | —   | ns    |            |

| 73A           | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2 | 1.5 Tcy + 40 | _   | ns    |            |

| 74            | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge                 | 40           | _   | ns    |            |

| 75            | TDOR                  | SDOx Data Output Rise Time                                | —            | 25  | ns    |            |

| 76            | TDOF                  | SDOx Data Output Fall Time                                | _            | 25  | ns    |            |

| 78            | TscR                  | SCKx Output Rise Time (Master mode)                       | _            | 25  | ns    |            |

| 79            | TscF                  | SCKx Output Fall Time (Master mode)                       | _            | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                    | —            | 50  | ns    |            |

| 81            | TDOV2scH,<br>TDOV2scL | SDOx Data Output Setup to SCKx Edge                       | Тсү          | _   | ns    |            |

### TABLE 31-18: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

## PIC18F87K22 FAMILY

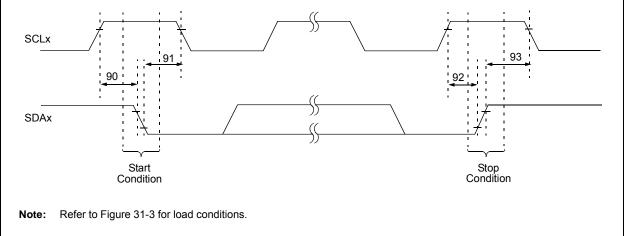

| TABLE 31-23: MSSP I <sup>2</sup> C <sup>™</sup> BUS START/STOP BITS REQUIREM | ENTS |

|------------------------------------------------------------------------------|------|

|------------------------------------------------------------------------------|------|

| Param.<br>No.                           | Symbol  | Characte        | eristic Min               |                  | Max | Units | Conditions                          |

|-----------------------------------------|---------|-----------------|---------------------------|------------------|-----|-------|-------------------------------------|

| 90                                      | TSU:STA | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) |     | ns    | Only relevant for<br>Repeated Start |

|                                         |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       |                                     |

|                                         |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       | condition                           |

| 91 THD:STA Start Condition<br>Hold Time |         | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | After this period, the              |

|                                         |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | first clock pulse is<br>generated   |

|                                         |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —   |       |                                     |

| 92                                      | Tsu:sto | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                                     |

|                                         |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       |                                     |

|                                         |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |     |       |                                     |

| 93                                      | THD:STO | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                                     |

|                                         |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   | 1     |                                     |

|                                         |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |     | 1     |                                     |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

| Param<br>No. | Sym           | Characteristic                                       | Min        | Тур | Мах        | Units    | Conditions                                             |

|--------------|---------------|------------------------------------------------------|------------|-----|------------|----------|--------------------------------------------------------|

| A01          | NR            | Resolution                                           | —          | —   | 12         | bit      | $\Delta VREF \ge 5.0V$                                 |

| A03          | EIL           | Integral Linearity Error                             | —          | ±1  | ±6.0       | LSB      | ΔVREF = 5.0V                                           |