Welcome to E-XFL.COM

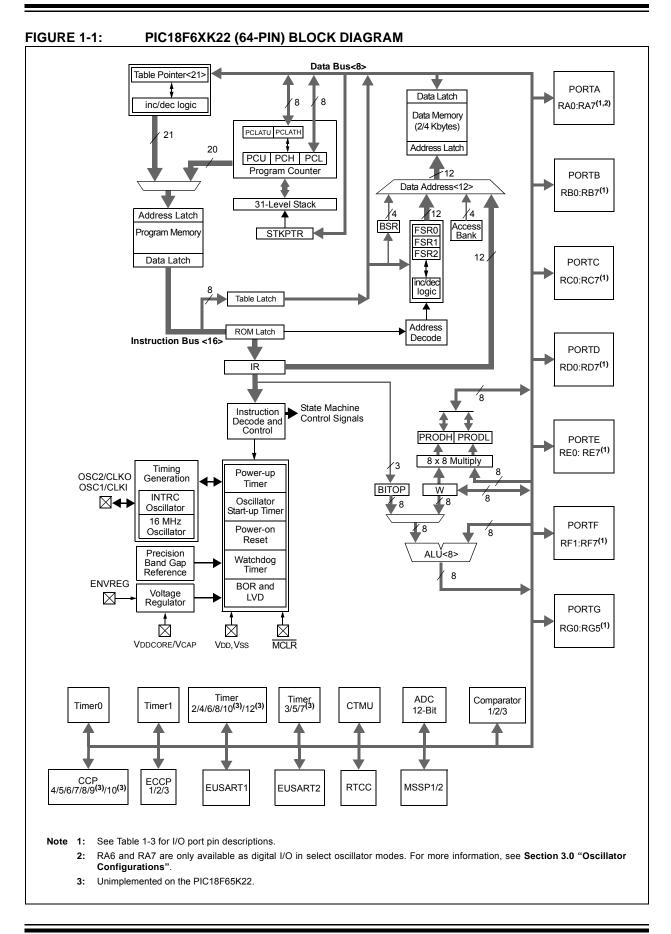

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k22-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                          | Pin Number              | Pin      | Buffer  | Description                                                                                                          |  |  |  |

|-------------------------------------------------------------------|-------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                   | TQFP                    | Туре     | Туре    | Description                                                                                                          |  |  |  |

|                                                                   |                         |          |         | PORTJ is a bidirectional I/O port.                                                                                   |  |  |  |

| RJ0/ALE<br>RJ0<br>ALE                                             | 62                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory address latch enable.                                                                |  |  |  |

| RJ1/OE<br>RJ1<br>OE                                               | 61                      | I/O<br>O | ST      | Digital I/O.<br>External memory output enable.                                                                       |  |  |  |

| RJ2/WRL<br>RJ2<br>WRL                                             | 60                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory write low control.                                                                   |  |  |  |

| RJ3/WRH<br>RJ3<br>WRH                                             | 59                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory high control.                                                                        |  |  |  |

| RJ4/BA0<br>RJ4<br>BA0                                             | 39                      | I/O<br>O | ST<br>— | Digital I/O.<br>External Memory Byte Address 0 control                                                               |  |  |  |

| RJ5/CE<br>RJ5<br>CE                                               | 40                      | I/O<br>O | ST<br>— | Digital I/O<br>External memory chip enable control.                                                                  |  |  |  |

| RJ6/LB<br>RJ6<br>LB                                               | 41                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory low byte control.                                                                    |  |  |  |

| RJ7/UB<br>RJ7<br>UB                                               | 42                      | I/O<br>O | ST<br>— | Digital I/O.<br>External memory high byte control.                                                                   |  |  |  |

| Vss                                                               | 11, 31, 51, 70          | Р        | —       | Ground reference for logic and I/O pins.                                                                             |  |  |  |

| VDD                                                               | 32, 48, 71              | Р        | —       | Positive supply for logic and I/O pins.                                                                              |  |  |  |

| AVss                                                              | 26                      | Р        |         | Ground reference for analog modules.                                                                                 |  |  |  |

| AVDD                                                              | 25                      | P        |         | Positive supply for analog modules.                                                                                  |  |  |  |

| ENVREG<br>Vddcore/Vcap                                            | 24<br>12                | I        | ST      | Enable for on-chip voltage regulator.<br>Core logic power or external filter capacitor connection.                   |  |  |  |

| Vddcore<br>Vcap                                                   |                         | Ρ        | _       | External filter capacitor connection (regulator enabled/disabled).                                                   |  |  |  |

| I = Input<br>P = Power<br>I <sup>2</sup> C = I <sup>2</sup> C™/SM | rigger input wit<br>Bus |          |         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |  |

#### PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

### 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

The PIC18F87K22 family of devices can be operated in the following oscillator modes:

- EC External clock, RA6 available

- ECIO External clock, clock out RA6 (Fosc/4 on RA6)

- HS High-Speed Crystal/Resonator

- XT Crystal/Resonator

- LP Low-Power Crystal

- RC External Resistor/Capacitor, RA6 available

- RCIO External Resistor/Capacitor, clock out RA6 (Fosc/4 on RA6)

- INTIO2 Internal Oscillator with I/O on RA6 and RA7

- INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

There is also an option for running the 4xPLL on any of the clock sources in the input frequency range of 4 to 16 MHz.

The PLL is enabled by setting the PLLCFG bit (CONFIG1H<4>) or the PLLEN bit (OSCTUNE<6>).

For the EC and HS mode, the PLLEN (software) or PLLCFG (CONFIG) bit can be used to enable the PLL.

For the INTIOx modes (HF-INTOSC):

- Only the PLLEN can enable the PLL (PLLCFG is ignored).

- When the oscillator is configured for the internal oscillator (FOSC<3:0> = 100x), the PLL can be enabled only when the HF-INTOSC frequency is 8 or 16 MHz.

When the RA6 and RA7 pins are not used for an oscillator function or CLKOUT function, they are available as general purpose I/Os. To optimize power consumption when using EC/HS/ XT/LP/RC as the primary oscillator, the frequency input range can be configured to yield an optimized power bias:

- Low-Power Bias External frequency less than 160 kHz

- Medium Power Bias External frequency between 160 kHz and 16 MHz

- High-Power Bias External frequency greater than 16 MHz

All of these modes are selected by the user by programming the FOSC<3:0> Configuration bits (CONFIG1H<3:0>). In addition, PIC18F87K22 family devices can switch between different clock sources, either under software control or, under certain conditions, automatically. This allows for additional power savings by managing device clock speed in real time without resetting the application. The clock sources for the PIC18F87K22 family of devices are shown in Figure 3-1.

For the HS and EC mode, there are additional power modes of operation – depending on the frequency of operation.

HS1 is the Medium Power mode with a frequency range of 4 MHz to 16 MHz. HS2 is the High-Power mode, where the oscillator frequency can go from 16 MHz to 25 MHz. HS1 and HS2 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 406.)

EC mode has these modes of operation:

- EC1 For low power with a frequency range up to 160 kHz

- EC2 Medium power with a frequency range of 160 kHz to 16 MHz

- EC3 High power with a frequency range of 16 MHz to 64 MHz

EC1, EC2 and EC3 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 406.)

Table 3-1 shows the HS and EC modes' frequency range and FOSC<3:0> settings.

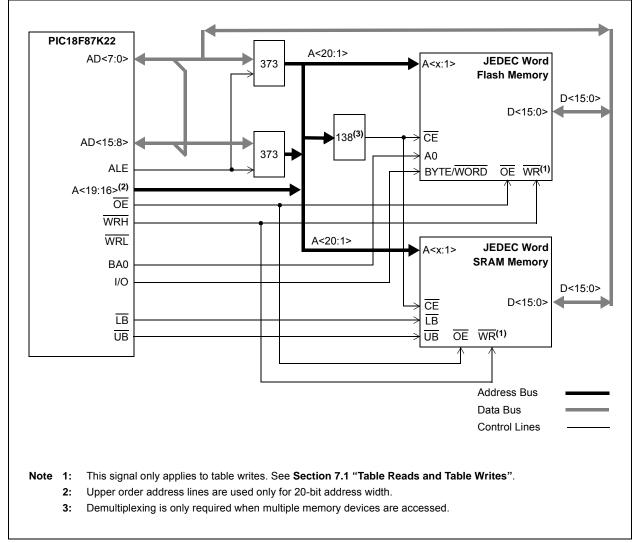

#### 8.6.3 16-BIT BYTE SELECT MODE

Figure 8-3 shows an example of 16-Bit Byte Select mode. This mode allows table write operations to word-wide external memories with byte selection capability. This generally includes both word-wide Flash and SRAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH signal is strobed for each write cycle; the WRL pin is not used. The BA0 or UB/LB signals are used to select the byte to be written, based on the Least Significant bit of the TBLPTR register. Flash and SRAM devices use different control signal combinations to implement Byte Select mode. JEDEC standard Flash memories require that a controller I/O port pin be connected to the memory's BYTE/WORD pin to provide the select signal. They also use the BA0 signal from the controller as a byte address. JEDEC standard static RAM memories, on the other hand, use the UB or LB signals to select the byte.

## 13.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 13-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 13-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 13-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 13-1: TOCON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                                                                             |                                                      |                                |                    |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|--------------------|--|--|--|--|--|

| R = Reada  | ble bit                                                                     | W = Writable bit                                     | U = Unimplemented bit          | , read as '0'      |  |  |  |  |  |

| -n = Value | at POR                                                                      | '1' = Bit is set                                     | '0' = Bit is cleared           | x = Bit is unknown |  |  |  |  |  |

|            |                                                                             |                                                      |                                |                    |  |  |  |  |  |

| bit 7      | TMR0ON                                                                      | : Timer0 On/Off Control bit                          |                                |                    |  |  |  |  |  |

|            | 1 = Enabl                                                                   | es Timer0                                            |                                |                    |  |  |  |  |  |

|            | 0 = Stops                                                                   | Timer0                                               |                                |                    |  |  |  |  |  |

| bit 6      | <b>T08BIT</b> : T                                                           | ïmer0 8-Bit/16-Bit Control b                         | it                             |                    |  |  |  |  |  |

|            | 1 = Timer                                                                   | 0 is configured as an 8-bit ti                       | mer/counter                    |                    |  |  |  |  |  |

|            | 0 = Timer                                                                   | 0 is configured as a 16-bit ti                       | mer/counter                    |                    |  |  |  |  |  |

| bit 5      | TOCS: Tir                                                                   | ner0 Clock Source Select bi                          | t                              |                    |  |  |  |  |  |

|            | 1 = Trans                                                                   | ition on TOCKI pin input edg                         | le                             |                    |  |  |  |  |  |

|            | 0 = Intern                                                                  | al clock (Fosc/4)                                    |                                |                    |  |  |  |  |  |

| bit 4      | T0SE: Tin                                                                   | ner0 Source Edge Select bit                          | t                              |                    |  |  |  |  |  |

|            | 1 = Increr                                                                  | 1 = Increment on high-to-low transition on T0CKI pin |                                |                    |  |  |  |  |  |

|            | 0 = Increr                                                                  | ment on low-to-high transitio                        | n on T0CKI pin                 |                    |  |  |  |  |  |

| bit 3      | PSA: Tim                                                                    | er0 Prescaler Assignment b                           | it                             |                    |  |  |  |  |  |

|            | 1 = Timer0 prescaler is not assigned; Timer0 clock input bypasses prescaler |                                                      |                                |                    |  |  |  |  |  |

|            | 0 = Timer                                                                   | 0 prescaler is assigned; Tim                         | ner0 clock input comes from pr | escaler output     |  |  |  |  |  |

| bit 2-0    | T0PS<2:0                                                                    | T0PS<2:0>: Timer0 Prescaler Select bits              |                                |                    |  |  |  |  |  |

|            | 111 = 1:256 Prescale value                                                  |                                                      |                                |                    |  |  |  |  |  |

|            | 110 <b>= 1</b> :1                                                           | 110 = 1:128 Prescale value                           |                                |                    |  |  |  |  |  |

|            | 101 <b>= 1</b> :6                                                           | 4 Prescale value                                     |                                |                    |  |  |  |  |  |

|            |                                                                             | 2 Prescale value                                     |                                |                    |  |  |  |  |  |

|            |                                                                             | 6 Prescale value                                     |                                |                    |  |  |  |  |  |

|            |                                                                             | Prescale value                                       |                                |                    |  |  |  |  |  |

|            | 001 = 1:4                                                                   | <ul> <li>Prescale value</li> </ul>                   |                                |                    |  |  |  |  |  |

#### 16.5.2 TIMER3/5/7 GATE SOURCE SELECTION

The Timer3/5/7 gate source can be selected from one of four different sources. Source selection is controlled by the TxGSS<1:0> bits (TxGCON<1:0>). The polarity for each available source is also selectable and is controlled by the TxGPOL bit (TxGCON <6>).

| TABLE 16-2: | <b>TIMER3/5/7 GATE SOURCES</b> |

|-------------|--------------------------------|

|             |                                |

| TxGSS<1:0> | Timerx Gate Source                                                     |

|------------|------------------------------------------------------------------------|

| 00         | Timerx Gate Pin                                                        |

| 01         | TMR(x+1) to Match PR(x+1)<br>(TMR(x+1) increments to match<br>PR(x+1)) |

| 10         | Comparator 1 Output<br>(comparator logic high output)                  |

| 11         | Comparator 2 Output<br>(comparator logic high output)                  |

16.5.2.1 TxG Pin Gate Operation

The TxG pin is one source for Timer3/5/7 gate control. It can be used to supply an external source to the Timerx gate circuitry.

#### 16.5.2.2 Timer4/6/8 Match Gate Operation

The TMR(x+1) register will increment until it matches the value in the PR(x+1) register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timerx gate circuitry. The pulse will remain high for one instruction cycle and will return back to a low state until the next match.

Depending on TxGPOL, Timerx increments differently when TMR(x+1) matches PR(x+1). When TxGPOL = 1, Timerx increments for a single instruction

cycle following a TMR(x+1) match with PR(x+1). When TxGPOL = 0, Timerx increments continuously, except for the cycle following the match, when the gate signal goes from low-to-high.

#### 16.5.2.3 Comparator 1 Output Gate Operation

The output of Comparator 1 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 1 with the CM1CON register, Timerx will increment depending on the transitions of the CMP1OUT (CMSTAT<5>) bit.

#### 16.5.2.4 Comparator 2 Output Gate Operation

The output of Comparator 2 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 2 with the CM2CON register, Timerx will increment depending on the transitions of the CMP2OUT (CMSTAT<6>) bit.

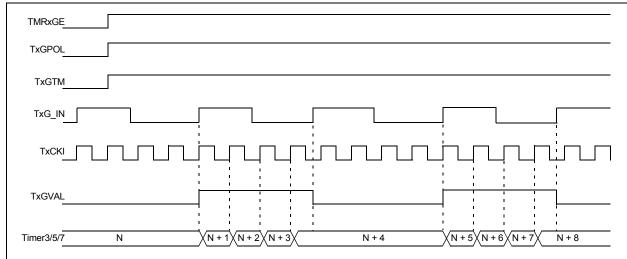

#### 16.5.3 TIMER3/5/7 GATE TOGGLE MODE

When Timer3/5/7 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3/5/7 gate signal, as opposed to the duration of a single level pulse.

The Timerx gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 16-3.)

The TxGVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3/5/7 Gate Toggle mode is enabled by setting the TxGTM bit (TxGCON<5>). When the TxGTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 16-3: TIMER3/5/7 GATE TOGGLE MODE

| R/W-0           | R/W-0                                                                                                                                         | R/W-0                                                                                      | R/W-0         | R/W-0             | R/W-0                         | R/W-0                      | R/W-0    |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------|-------------------|-------------------------------|----------------------------|----------|

| ALRMEN          | CHIME                                                                                                                                         | AMASK3                                                                                     | AMASK2        | AMASK1            | AMASK0                        | ALRMPTR1                   | ALRMPTR0 |

| bit 7           | OTIME                                                                                                                                         | /                                                                                          | 7 11/7 10/12  |                   | / 10/ 10/ 10                  |                            | bit 0    |

|                 |                                                                                                                                               |                                                                                            |               |                   |                               |                            |          |

| Legend:         |                                                                                                                                               |                                                                                            |               |                   |                               |                            |          |

| R = Readable    | bit                                                                                                                                           | W = Writable                                                                               | bit           | U = Unimpler      | mented bit, rea               | d as '0'                   |          |

| -n = Value at F | POR                                                                                                                                           | '1' = Bit is set                                                                           |               | '0' = Bit is cle  | ared                          | x = Bit is unkr            | IOWN     |

| bit 7           | ALRMEN: A                                                                                                                                     | larm Enable bit                                                                            |               |                   |                               |                            |          |

|                 |                                                                                                                                               | enabled (cleare<br>ME = 0)                                                                 | ed automatica | lly after an alaı | rm event when                 | ever ARPT<7:0              | > = 00   |

| bit 6           | CHIME: Chin                                                                                                                                   | ne Enable bit                                                                              |               |                   |                               |                            |          |

|                 |                                                                                                                                               | s enabled; ALRI<br>s disabled; ALR                                                         |               |                   |                               | m 00h to FFh               |          |

|                 | 0001 = Even<br>0010 = Even<br>0011 = Even<br>0100 = Even<br>0101 = Even<br>0110 = Onc<br>0111 = Onc<br>1000 = Onc<br>1001 = Onc<br>101x = Res | ry 10 seconds<br>ry minute<br>ry 10 minutes<br>ry hour<br>e a day<br>e a week<br>e a month | use           | ured for Febru    | ary 29 <sup>th</sup> , once o | every four years           | ;)       |

| bit 1-0         | ALRMPTR<                                                                                                                                      | 1:0>: Alarm Val                                                                            | ue Register W | indow Pointer     | bits                          |                            |          |

|                 | registers. The '00'.                                                                                                                          |                                                                                            |               |                   |                               | ALRMVALH an<br>of ALRMVALH |          |

|                 | ALRMVALH:<br>00 = ALRMM<br>01 = ALRMM<br>10 = ALRMM<br>11 = Unimple                                                                           | VD<br>INTH                                                                                 |               |                   |                               |                            |          |

|                 | ALRMVALL:<br>00 = ALRMS<br>01 = ALRMH<br>10 = ALRMD                                                                                           |                                                                                            |               |                   |                               |                            |          |

### REGISTER 18-4: ALRMCFG: ALARM CONFIGURATION REGISTER

| REGISTER 21-2: | SSPxCON1: MSSPx CONTROL F | REGISTER 1 (SPI MODE) |

|----------------|---------------------------|-----------------------|

|----------------|---------------------------|-----------------------|

| R/W-0      | R/W-0                                                                                        | R/W-0                                                     | R/W-0                                                                                            | R/W-0                                                            | R/W-0                        | R/W-0                | R/W-0                |

|------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------|----------------------|----------------------|

| WCOL       | SSPOV <sup>(1)</sup>                                                                         | SSPEN <sup>(2)</sup>                                      | CKP                                                                                              | SSPM3 <sup>(3)</sup>                                             | SSPM2 <sup>(3)</sup>         | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7      |                                                                                              |                                                           |                                                                                                  |                                                                  |                              |                      | bit (                |

| Legend:    |                                                                                              |                                                           |                                                                                                  |                                                                  |                              |                      |                      |

| R = Reada  | ıble bit                                                                                     | W = Writable                                              | bit                                                                                              | U = Unimplen                                                     | nented bit, rea              | d as '0'             |                      |

| -n = Value | at POR                                                                                       | '1' = Bit is set                                          |                                                                                                  | '0' = Bit is clea                                                | ared                         | x = Bit is unkr      | nown                 |

| bit 7      |                                                                                              | )                                                         |                                                                                                  | e it is still transm                                             | nitting the prev             | ious word (mus       | t be cleared i       |

| bit 6      | <u>SPI Slave mo</u><br>1 = A new by<br>overflow,                                             | yte is received<br>the data in SSI<br>xBUF, even if<br>). | while the SSF<br>PxSR is lost. (                                                                 | PxBUF register<br>Overflow can on<br>tting data, to a            | ly occur in Sla              | ve mode. The u       | user must rea        |

| bit 5      | 1 = Enables                                                                                  |                                                           | onfigures SC                                                                                     | Enable bit <sup>(2)</sup><br>Kx, SDOx, SDIx<br>ese pins as I/O p |                              | erial port pins      |                      |

| bit 4      | <b>CKP:</b> Clock F<br>1 = Idle state                                                        | Polarity Select b<br>for the clock is<br>for the clock is | it<br>a high level                                                                               |                                                                  | ·                            |                      |                      |

| bit 3-0    | 1010 = SPI N<br>0101 = SPI S<br>0100 = SPI S<br>0011 = SPI N<br>0010 = SPI N<br>0001 = SPI N | laster mode: cl                                           | ock = Fosc/8<br>ck = SCKx pir<br>ck = SCKx pir<br>ock = TMR2 c<br>ock = Fosc/64<br>ock = Fosc/16 | 4                                                                | ol disabled; $\overline{SS}$ | ox can be used       | as I/O pin           |

|            | In Master mode, a writing to the SSF                                                         |                                                           | is not set sind                                                                                  | ce each new rec                                                  | eption (and tra              | ansmission) is i     | nitiated by          |

|            | When enabled th                                                                              | •                                                         | ha proparly a                                                                                    | onfigured on inn                                                 | uto or outouto               |                      |                      |

2: When enabled, these pins must be properly configured as inputs or outputs.

**3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

| GCEN<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at bit 7 |                                   | ACKDT <sup>(1)</sup><br>W = Writable<br>'1' = Bit is set | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup><br>bit ( |

|-----------------------------------------------------------------|-----------------------------------|----------------------------------------------------------|----------------------|-----------------------------|--------------------|---------------------|-----------------------------|

| <b>Legend:</b><br>R = Readable<br>-n = Value at l               |                                   |                                                          | bit                  |                             |                    |                     | bit                         |

| R = Readable<br>-n = Value at                                   |                                   |                                                          | oit                  |                             |                    |                     |                             |

| R = Readable<br>-n = Value at                                   |                                   |                                                          | bit                  |                             |                    |                     |                             |

|                                                                 | POR                               | '1' = Bit is set                                         |                      | U = Unimplen                | nented bit, rea    | d as '0'            |                             |

| bit 7                                                           |                                   |                                                          |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                         |

|                                                                 | GCEN: Gener                       | ral Call Enable                                          | bit                  |                             |                    |                     |                             |

|                                                                 | Unused in Ma                      | ster mode.                                               |                      |                             |                    |                     |                             |

| bit 6                                                           | ACKSTAT: Ad                       | knowledge Sta                                            | itus bit (Master     | Transmit mod                | e only)            |                     |                             |

|                                                                 |                                   | dge was not re<br>dge was receiv                         |                      | ave                         |                    |                     |                             |

| bit 5                                                           | ACKDT: Ackr                       | owledge Data                                             | bit (Master Red      | ceive mode onl              | y) <sup>(1)</sup>  |                     |                             |

|                                                                 | 1 = Not Ackno<br>0 = Acknowle     | •                                                        |                      |                             |                    |                     |                             |

| bit 4                                                           | ACKEN: Ackr                       | nowledge Sequ                                            | ence Enable b        | oit <sup>(2)</sup>          |                    |                     |                             |

|                                                                 | Automati                          | Acknowledge<br>cally cleared by<br>edge sequence         | hardware.            | SDAx and SO                 | CLx pins and       | transmits ACk       | KDT data bi                 |

| bit 3                                                           |                                   |                                                          |                      | e mode only) <sup>(2)</sup> |                    |                     |                             |

|                                                                 |                                   | Receive mode f                                           |                      |                             |                    |                     |                             |

| bit 2                                                           | PEN: Stop Co                      | ndition Enable                                           | bit <sup>(2)</sup>   |                             |                    |                     |                             |

|                                                                 | -                                 | top condition o                                          |                      | CLx pins. Autor             | matically clear    | ed by hardware.     |                             |

| bit 1                                                           | RSEN: Repea                       | ated Start Cond                                          | ition Enable bi      | t <sup>(2)</sup>            |                    |                     |                             |

|                                                                 |                                   | Repeated Start<br>Start condition                        |                      | DAx and SCLx                | pins. Automa       | tically cleared by  | y hardware.                 |

| bit 0                                                           | SEN: Start Co                     | ondition Enable                                          | bit <sup>(2)</sup>   |                             |                    |                     |                             |

|                                                                 | 1 = Initiates S<br>0 = Start conc |                                                          | n SDAx and S         | CLx pins. Auto              | matically clear    | ed by hardware.     |                             |

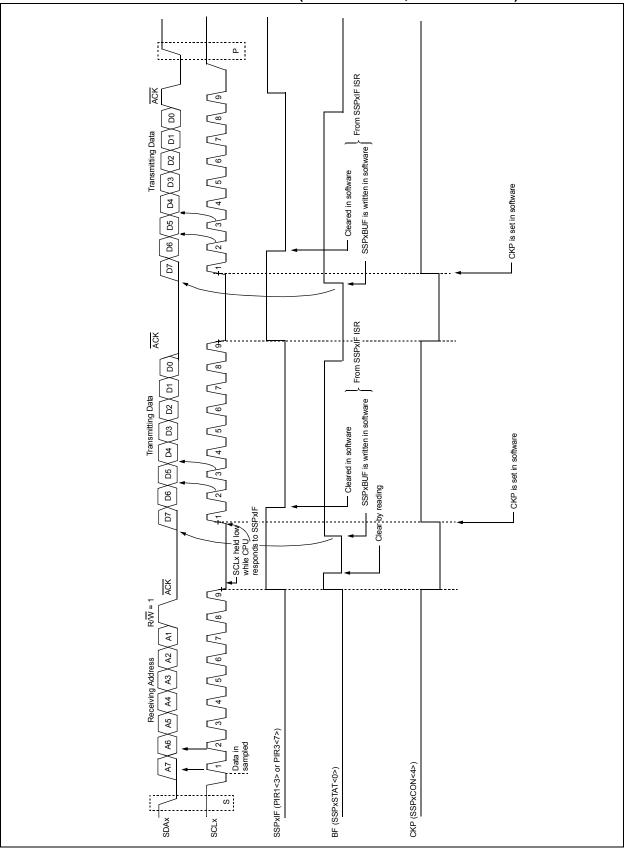

## REGISTER 21-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

2: If the l<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

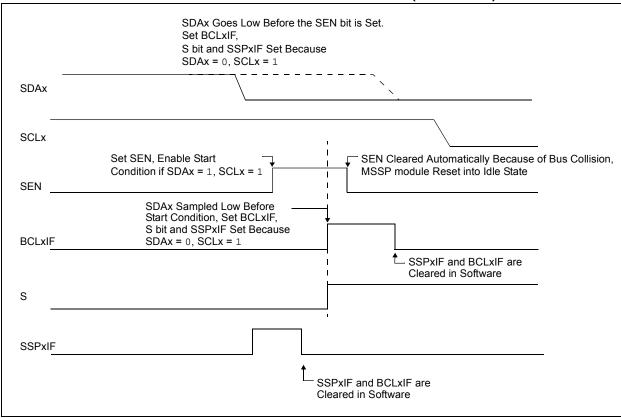

#### 21.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx is sampled low at the beginning of the Start condition (Figure 21-28).

- b) SCLx is sampled low before SDAx is asserted low (Figure 21-29).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- · The Start condition is aborted

- · The BCLxIF flag is set

- The MSSP module is reset to its inactive state (Figure 21-28)

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded from SSPxADD<6:0> and counts down to 0. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 21-30). If, however, a '1' is sampled on the SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0. If the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that a bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 21-28: BUS COLLISION DURING START CONDITION (SDAx ONLY)

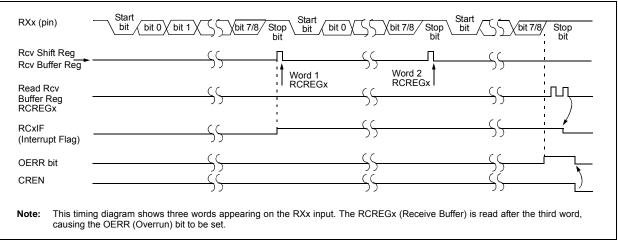

#### FIGURE 22-7: ASYNCHRONOUS RECEPTION

#### TABLE 22-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name     | Bit 7                    | Bit 6          | Bit 5         | Bit 4          | Bit 3   | Bit 2   | Bit 1  | Bit 0  |  |

|----------|--------------------------|----------------|---------------|----------------|---------|---------|--------|--------|--|

| INTCON   | GIE/GIEH                 | PEIE/GIEL      | TMR0IE        | INT0IE         | RBIE    | TMR0IF  | INT0IF | RBIF   |  |

| PIR1     | PSPIF                    | ADIF           | RC1IF         | TX1IF          | SSP1IF  | TMR1GIF | TMR2IF | TMR1IF |  |

| PIE1     | PSPIE                    | ADIE           | RC1IE         | TX1IE          | SSP1IE  | TMR1GIE | TMR2IE | TMR1IE |  |

| IPR1     | PSPIP                    | ADIP           | RC1IP         | TX1IP          | SSP1IP  | TMR1GIP | TMR2IP | TMR1IP |  |

| PIR3     | TMR5GIF                  | —              | RC2IF         | TX2IF          | CTMUIF  | CCP2IF  | CCP1IF | RTCCIF |  |

| PIE3     | TMR5GIE                  | _              | RC2IE         | TX2IE          | CTMUIE  | CCP2IE  | CCP1IE | RTCCIE |  |

| IPR3     | TMR5GIP                  | —              | RC2IP         | TX2IP          | CTMUIP  | CCP2IP  | CCP1IP | RTCCIP |  |

| RCSTA1   | SPEN                     | RX9            | SREN          | CREN           | ADDEN   | FERR    | OERR   | RX9D   |  |

| RCREG1   | EUSART1 Receive Register |                |               |                |         |         |        |        |  |

| TXSTA1   | CSRC                     | TX9            | TXEN          | SYNC           | SENDB   | BRGH    | TRMT   | TX9D   |  |

| BAUDCON1 | ABDOVF                   | RCIDL          | RXDTP         | TXCKP          | BRG16   | —       | WUE    | ABDEN  |  |

| SPBRGH1  | EUSART1 E                | aud Rate Ger   | nerator Regis | ster High Byte | 9       |         |        |        |  |

| SPBRG1   | EUSART1 E                | aud Rate Ger   | nerator Regis | ster           |         |         |        |        |  |

| RCSTA2   | SPEN                     | RX9            | SREN          | CREN           | ADDEN   | FERR    | OERR   | RX9D   |  |

| RCREG2   | EUSART2 F                | Receive Regist | er            |                |         |         |        |        |  |

| TXSTA2   | CSRC                     | TX9            | TXEN          | SYNC           | SENDB   | BRGH    | TRMT   | TX9D   |  |

| BAUDCON2 | ABDOVF                   | RCIDL          | RXDTP         | TXCKP          | BRG16   | _       | WUE    | ABDEN  |  |

| SPBRGH2  | EUSART2 E                | aud Rate Ger   | nerator Regis | ster High Byte | 9       |         |        |        |  |

| SPBRG2   | EUSART2 E                | aud Rate Ger   | nerator Regis | ster           |         |         |        |        |  |

| ODCON3   | U2OD                     | U10D           | _             | —              | _       | _       | —      | CTMUDS |  |

| PMD0     | CCP3MD                   | CCP2MD         | CCP1MD        | UART2MD        | UART1MD | SSP2MD  | SSP1MD | ADCMD  |  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

### 23.0 12-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module in the PIC18F87K22 family of devices has 16 inputs for the 64-pin devices and 24 inputs for the 80-pin devices. This module allows conversion of an analog input signal to a corresponding 12-bit digital number.

The module has these registers:

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

- A/D Port Configuration Register 0 (ANCON0)

- A/D Port Configuration Register 1 (ANCON1)

- A/D Port Configuration Register 2 (ANCON2)

- ADRESH (the upper, A/D Results register)

- ADRESL (the lower, A/D Results register)

The ADCON0 register, shown in Register 23-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 23-2, configures the voltage reference and special trigger selection. The ADCON2 register, shown in Register 23-3, configures the A/D clock source and programmed acquisition time and justification.

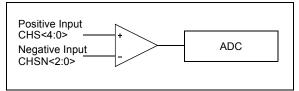

### 23.1 Differential A/D Converter

The converter in PIC18F87K22 family devices is implemented as a differential A/D where the differential voltage between two channels is measured and converted to digital values (see Figure 23-1).

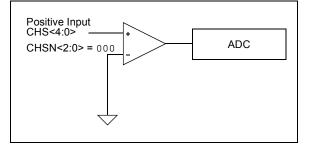

The converter can also be configured to measure a voltage from a single input by clearing the CHSN bits (ADCON1<2:0>). With this configuration, the negative channel input is connected internally to AVss (see Figure 23-2).

## FIGURE 23-1: DIFFERENTIAL CHANNEL MEASUREMENT

Differential conversion feeds the two input channels to a unity gain differential amplifier. The positive channel input is selected using the CHS bits (ADCON0<6:2>) and the negative channel input is selected using the CHSN bits (ADCON1<2:0>).

The output from the amplifier is fed to the A/D Converter, as shown in Figure 23-1. The 12-bit result is available on the ADRESH and ADRESL registers. An additional bit indicates if the 12-bit result is a positive or negative value.

FIGURE 23-2:

#### SINGLE CHANNEL MEASUREMENT

In the Single Channel Measurement mode, the negative input is connected to Avss by clearing the CHSN bits (ADCON1<2:0>).

#### EXAMPLE 27-1: SETUP FOR CTMU CALIBRATION ROUTINES

```

#include "pl8cxxx.h"

void setup(void)

{ //CTMUCON - CTMU Control register

CTMUCONH = 0 \times 00;

//make sure CTMU is disabled

CTMUCONL = 0X90;

//CTMU continues to run when emulator is stopped,CTMU continues

//to run in idle mode, Time Generation mode disabled, Edges are blocked

//No edge sequence order, Analog current source not grounded, trigger

//output disabled, Edge2 polarity = positive level, Edge2 source =

//source 0, Edgel polarity = positive level, Edgel source = source 0,

// Set Edge status bits to zero

//CTMUICON - CTMU Current Control Register

CTMUICON = 0 \times 01;

//0.55uA, Nominal - No Adjustment

//Setup AD converter;

TRISA=0x04;

//set channel 2 as an input

// Configured AN2 as an analog channel

// ANCONO

ANCON0 = 0 \times 04;

// ANCON1

ANCON1 = 0 XE0;

// ADCON2

// Resulst format 1= Right justified

ADCON2bits.ADFM=1;

// Acquition time 7 = 20TAD 2 = 4TAD 1=2TAD

ADCON2bits.ACQT=1;

ADCON2bits.ADCS=2;

// Clock conversion bits 6= FOSC/64 2=FOSC/32

// ADCON0

// Vref+ = AVdd

ADCON1bits.VCFG0 =0;

// Vref+ = AVdd

ADCON0bits.VCFG1 =0;

ADCON0bits.VCFG = 0;

// Vref- = AVss

ADCON0bits.CHS=2;

// Select ADC channel

// Turn on ADC

ADCON0bits.ADON=1;

}

```

#### REGISTER 28-11: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| R/C-1                             | R-1                 | U-0                                                          | U-0                                                                    | U-0                                                                                                         | U-0                                                                                                                        | U-0                                                                                                                                     |  |

|-----------------------------------|---------------------|--------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| WRTB                              | WRTC <sup>(1)</sup> | —                                                            | —                                                                      | —                                                                                                           | —                                                                                                                          | —                                                                                                                                       |  |

|                                   |                     |                                                              | •                                                                      |                                                                                                             |                                                                                                                            | bit 0                                                                                                                                   |  |

|                                   |                     |                                                              |                                                                        |                                                                                                             |                                                                                                                            |                                                                                                                                         |  |

| .egend: C = Clearable bit         |                     |                                                              |                                                                        |                                                                                                             |                                                                                                                            |                                                                                                                                         |  |

| Readable bit W = Writable bit     |                     |                                                              | U = Unimplemented bit, read as '0'                                     |                                                                                                             |                                                                                                                            |                                                                                                                                         |  |

| n = Value at POR '1' = Bit is set |                     |                                                              | '0' = Bit is cleared                                                   |                                                                                                             | x = Bit is unkr                                                                                                            | nown                                                                                                                                    |  |

|                                   | WRTB                | WRTB WRTC <sup>(1)</sup><br>C = Clearable<br>it W = Writable | WRTB WRTC <sup>(1)</sup> —<br>C = Clearable bit<br>it W = Writable bit | WRTB     WRTC <sup>(1)</sup> —     —       C = Clearable bit       it     W = Writable bit     U = Unimpler | WRTB     WRTC <sup>(1)</sup> —     —       C = Clearable bit       it     W = Writable bit     U = Unimplemented bit, real | WRTB     WRTC <sup>(1)</sup> —     —     —       C = Clearable bit       it     W = Writable bit     U = Unimplemented bit, read as '0' |  |

| bit 7   | WRTD: Data EEPROM Write Protection bit<br>1 = Data EEPROM is not write-protected<br>0 = Data EEPROM is write-protected                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | WRTB: Boot Block Write Protection bit<br>1 = Boot block is not write-protected <sup>(2)</sup><br>0 = Boot block is write-protected <sup>(2)</sup>                                                        |

| bit 5   | WRTC: Configuration Register Write Protection bit <sup>(1)</sup><br>1 = Configuration registers are not write-protected <sup>(2)</sup><br>0 = Configuration registers are write-protected <sup>(2)</sup> |

| bit 4-0 | Unimplemented: Read as '0'                                                                                                                                                                               |

**Note 1:** This bit is read-only in normal Execution mode; it can be written only in Program mode.

2: For the memory size of the blocks, see Figure 28-6.

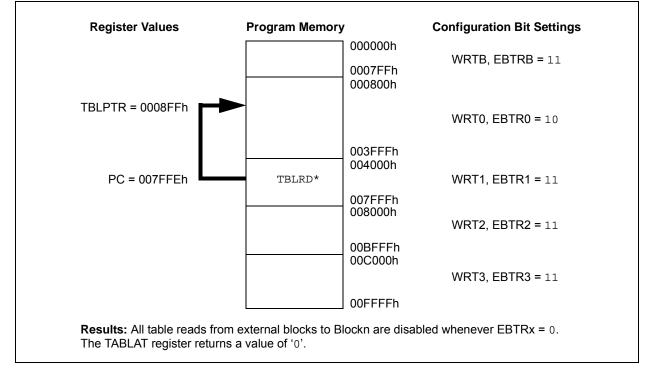

#### FIGURE 28-8: EXTERNAL BLOCK TABLE READ (EBTRx) DISALLOWED

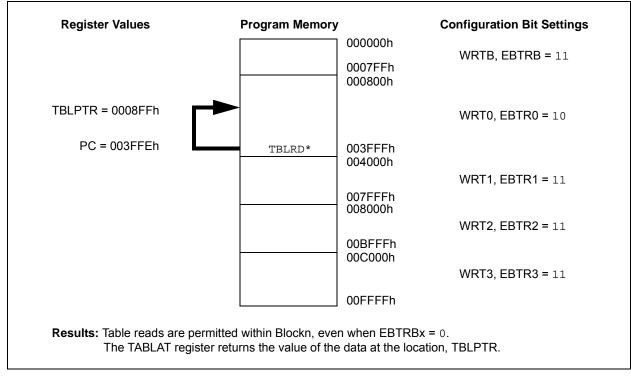

#### FIGURE 28-9: EXTERNAL BLOCK TABLE READ (EBTRx) ALLOWED

| BCF               | Bit Clear f                                                   |                     |                                                 | BN    |                                                                | Branch if N                 | legative                                         |                        |  |

|-------------------|---------------------------------------------------------------|---------------------|-------------------------------------------------|-------|----------------------------------------------------------------|-----------------------------|--------------------------------------------------|------------------------|--|

| Syntax:           | BCF f, b {,a}                                                 |                     |                                                 | Synt  | ax:                                                            | BN n                        | BN n                                             |                        |  |

| Operands:         | $0 \leq f \leq 255$                                           |                     |                                                 | Oper  | ands:                                                          | -128 ≤ n ≤ ′                | 127                                              |                        |  |

|                   | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$ |                     |                                                 | Oper  | ation:                                                         | if Negative<br>(PC) + 2 + 2 | ,                                                |                        |  |

| Operation:        | $0 \rightarrow f \le b >$                                     |                     |                                                 | Statu | is Affected:                                                   | None                        |                                                  |                        |  |

| Status Affected:  | None                                                          |                     |                                                 | Enco  | oding:                                                         | 1110                        | 0110 nn                                          | nn nnnn                |  |

| Encoding:         | 1001                                                          | bbba ff             | ff ffff                                         |       | cription:                                                      | If the Nega                 | tive bit is '1', th                              | nen the                |  |

| Description:      | Bit 'b' in reg                                                | gister 'f' is clea  | ared.                                           |       |                                                                | program wi                  |                                                  |                        |  |

|                   | ,                                                             |                     | ink is selected.<br>ed to select the            |       |                                                                | added to the incremente     | d to fetch the                                   | e PC will have<br>next |  |

|                   | set is enabl                                                  |                     | led instruction<br>ction operates<br>Addressing |       |                                                                | ,                           | the new addre<br>a. This instruct<br>astruction. |                        |  |

|                   |                                                               | ever f $\leq$ 95 (5 |                                                 | Word  | ds:                                                            | 1                           |                                                  |                        |  |

|                   |                                                               | .2.3 "Byte-Or       | riented and                                     | Cycl  | es:                                                            | 1(2)                        |                                                  |                        |  |

|                   | Literal Offs                                                  | set Mode" for       |                                                 |       | ycle Activity:                                                 |                             |                                                  |                        |  |

| Words:            | 1                                                             |                     |                                                 |       | Q1                                                             | Q2                          | Q3                                               | Q4                     |  |

| Cycles:           | 1                                                             |                     |                                                 |       | Decode                                                         | Read literal                | Process                                          | Write to               |  |

| Q Cycle Activity: |                                                               |                     |                                                 |       |                                                                | 'n'                         | Data                                             | PC                     |  |

| Q1                | Q2                                                            | Q3                  | Q4                                              |       | No<br>operation                                                | No<br>operation             | No<br>operation                                  | No<br>operation        |  |

| Decode            | Read<br>register 'f'                                          | Process<br>Data     | Write<br>register 'f'                           | lf N  | o Jump:                                                        | operation                   | operation                                        | operation              |  |

| L                 | regiotor r                                                    | Data                | regiotor r                                      |       | Q1                                                             | Q2                          | Q3                                               | Q4                     |  |

| Example:          | BCF F                                                         | LAG_REG,            | 7, 0                                            |       | Decode                                                         | Read literal                | Process                                          | No                     |  |

| Before Instruc    | tion                                                          |                     |                                                 |       |                                                                | 'n'                         | Data                                             | operation              |  |

|                   | EG = C7h                                                      |                     |                                                 |       |                                                                |                             |                                                  |                        |  |

| After Instruction |                                                               |                     |                                                 | Exar  | <u>nple:</u>                                                   | HERE                        | BN Jump                                          |                        |  |

| FLAG_R            | - 4/II                                                        |                     |                                                 |       | Before Instruction<br>PC = address (HERE)<br>After Instruction |                             |                                                  |                        |  |

|                   |                                                               |                     |                                                 |       | lf Negati<br>PC                                                |                             | dress (Jump)                                     |                        |  |

|                   |                                                               |                     |                                                 |       | If Negative = 0;                                               |                             |                                                  |                        |  |

|                   |                                                               |                     |                                                 |       | PC                                                             | = ad                        | dress (HERE                                      | + 2)                   |  |

### 30.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 30.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 30.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K22 Family (Industrial/Extended) (Continued)

| PIC18F87K22 Family<br>(Industrial/Extended) |                          |           |           |       |            |                                                                                                    |                            |  |  |

|---------------------------------------------|--------------------------|-----------|-----------|-------|------------|----------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Param<br>No.                                | Device                   | Тур       | Max       | Units | Conditions |                                                                                                    |                            |  |  |

| D025                                        | Real-Time Clock/Calendar | with SOSC | : Oscilla | tor   |            |                                                                                                    |                            |  |  |

| $(\Delta IRTCC)$                            | All devices              | 0.7       | 2.7       | μA    | -40°C      |                                                                                                    | 32.768 kHz,<br>SOSCRUN = 1 |  |  |

|                                             |                          | 0.7       | 2.8       | μA    | +25°C      | VDD = 1.8V <sup>(4)</sup>                                                                          |                            |  |  |

|                                             |                          | 1.1       | 2.8       | μA    | +60°C      | VDD = 1.8V <sup>(4)</sup><br>Regulator Disabled<br>VDD = 3.3V <sup>(4)</sup><br>Regulator Disabled |                            |  |  |

|                                             |                          | 1.1       | 2.9       | μA    | +85°C      |                                                                                                    |                            |  |  |

|                                             |                          | 2.2       | 4.4       | μA    | +125°C     |                                                                                                    |                            |  |  |

|                                             | All devices              | 1.2       | 2.9       | μA    | -40°C      |                                                                                                    |                            |  |  |

|                                             |                          | 1.1       | 2.8       | μA    | +25°C      |                                                                                                    |                            |  |  |

|                                             |                          | 2         | 4.6       | μA    | +60°C      |                                                                                                    |                            |  |  |

|                                             |                          | 2         | 4.8       | μA    | +85°C      |                                                                                                    |                            |  |  |

|                                             |                          | 4         | 6.5       | μA    | +125°C     |                                                                                                    |                            |  |  |

|                                             | All devices              | 1.5       | 4.4       | μA    | -40°C      |                                                                                                    |                            |  |  |

|                                             |                          | 1.5       | 4.4       | μA    | +25°C      | V <sub>DD</sub> = 5V <sup>(5)</sup><br>Regulator Enabled                                           |                            |  |  |

|                                             |                          | 1.7       | 4.7       | μA    | +60°C      |                                                                                                    |                            |  |  |

|                                             |                          | 1.7       | 4.7       | μA    | +85°C      |                                                                                                    |                            |  |  |

|                                             |                          | 3.5       | 6.9       | μA    | +125°C     |                                                                                                    |                            |  |  |

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or Vss, and all features that add delta current are disabled (such as WDT, SOSC oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in Active Operation mode are:

OSC1 = External square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: Voltage regulator disabled (ENVREG = 0, tied to Vss, RETEN (CONFIG1L<0>) = 1).

- 5: Voltage regulator enabled (ENVREG = 1, tied to VDD, SRETEN (WDTCON<4>) = 1 and RETEN (CONFIG1L<0>) = 0).

- 6: 48 MHz, maximum frequency at +125°C.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line