Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 64MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (32K x 16)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k22-i-ptrsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F65K22 PIC18F85K22

- PIC18F66K22 PIC18F86K22

- PIC18F67K22 PIC18F87K22

This family combines the traditional advantages of all PIC18 microcontrollers – namely, high computational performance and a rich feature set – with an extremely competitive price point. These features make the PIC18F87K22 family a logical choice for many high-performance applications where price is a primary consideration.

## 1.1 Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F87K22 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the Internal RC oscillator, power consumption during code execution can be reduced.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further.

- **On-the-Fly Mode Switching:** The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- nanoWatt XLP: An extra low-power Sleep, BOR, RTCC and Watchdog Timer

# 1.1.2 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F87K22 family offer different oscillator options, allowing users a range of choices in developing application hardware. These include:

- External Resistor/Capacitor (RC); RA6 available

- External Resistor/Capacitor with Clock Out (RCIO)

- Three External Clock modes:

- External Clock (EC); RA6 available

- External Clock with Clock Out (ECIO)

- External Crystal (XT, HS, LP)

- A Phase Lock Loop (PLL) frequency multiplier, available to the External Oscillator modes, which allows clock speeds of up to 64 MHz. PLL can also be used with the internal oscillator.

- An internal oscillator block that provides a 16 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD)

- Operates as HF-INTOSC or MF-INTOSC when block selected for 16 MHz or 500 kHz

- Frees the two oscillator pins for use as additional general purpose I/O

The internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

### 1.1.3 MEMORY OPTIONS

The PIC18F87K22 family provides ample room for application code, from 32 Kbytes to 128 Kbytes of code space. The Flash cells for program memory are rated to last up to 10,000 erase/write cycles. Data retention without refresh is conservatively estimated to be greater than 40 years.

The Flash program memory is readable and writable. During normal operation, the PIC18F87K22 family also provides plenty of room for dynamic application data with up to 3,862 bytes of data RAM.

### 1.1.4 EXTERNAL MEMORY BUS

Should 128 Kbytes of memory be inadequate for an application, the 80-pin members of the PIC18F87K22 family have an External Memory Bus (EMB) enabling the controller's internal Program Counter to address a memory space of up to 2 Mbytes. This is a level of data access that few 8-bit devices can claim and enables:

- Using combinations of on-chip and external memory of up to 2 Mbytes

- Using external Flash memory for reprogrammable application code or large data tables

- Using external RAM devices for storing large amounts of variable data

### 1.1.5 EXTENDED INSTRUCTION SET

The PIC18F87K22 family implements the optional extension to the PIC18 instruction set, adding eight new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as 'C'.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "**Power-Managed Modes**".

- Note 1: The Timer1/3/5/7 oscillator must be enabled to select the secondary clock source. The Timerx oscillator is enabled by setting the SOSCEN bit in the Timerx Control register (TxCON<3>). If the Timerx oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timerx oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timerx oscillator starts.

#### 3.3.2.1 System Clock Selection and Device Resets

Since the SCS bits are cleared on all forms of Reset, this means the primary oscillator, defined by the FOSC<3:0> Configuration bits, is used as the primary clock source on device Resets. This could either be the internal oscillator block by itself, or one of the other primary clock source (HS, EC, XT, LP, External RC and PLL-Enabled modes).

In those cases when the internal oscillator block, without PLL, is the default clock on Reset, the Fast RC oscillator (INTOSC) will be used as the device clock source. It will initially start at 8 MHz; the postscaler selection that corresponds to the Reset value of the IRCF<2:0> bits ('110').

Regardless of which primary oscillator is selected, INTRC will always be enabled on device power-up. It serves as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSC Configuration bits are read and the oscillator selection of the operational mode is made.

Note that either the primary clock source or the internal oscillator will have two bit setting options for the possible values of the SCS<1:0> bits, at any given time.

# 3.3.3 OSCILLATOR TRANSITIONS

PIC18F87K22 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in Section 4.1.2 "Entering Power-Managed Modes".

# 3.4 RC Oscillator

For timing-insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- Supply Voltage

- Values of the External Resistor (REXT) and Capacitor (CEXT)

- Operating Temperature

Given the same device, operating voltage and temperature, and component values, there will also be unit to unit frequency variations. These are due to factors, such as:

- Normal manufacturing variation

- Difference in lead frame capacitance between package types (especially for low CEXT values)

- Variations within the tolerance of limits of  $\ensuremath{\mathsf{Rext}}$  and  $\ensuremath{\mathsf{Cext}}$

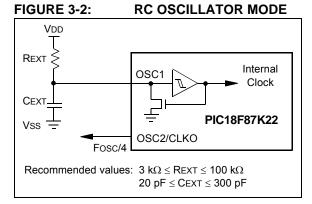

In the RC Oscillator mode, the oscillator frequency, divided by 4, is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-2 shows how the R/C combination is connected.

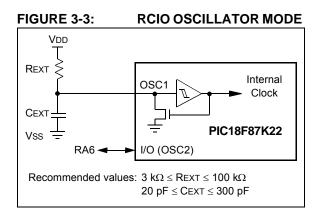

The RCIO Oscillator mode (Figure 3-3) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

### 4.7 Ultra Low-Power Wake-up

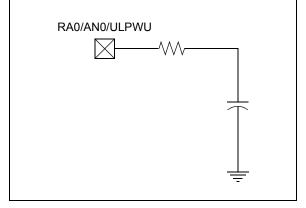

The Ultra Low-Power Wake-up (ULPWU) on pin, RA0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RA0 by configuring the RA0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RA0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the WDTCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RA0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RA0.

When the ULPWU module wakes the device from Sleep mode, the ULPLVL bit (WDTCON<5>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 4-1 for initializing the ULPWU module.

#### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

PORTAbits.RA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor

//on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power

//Wakeup module and allow

//capacitor discharge

WDTCONbits ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep

OSCCONbits.IDLEN = 0;

//Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RA0 and the external capacitor, provides overcurrent protection for the RA0/AN0/ ULPWU pin and enables software calibration of the time-out (see Figure 4-9).

#### FIGURE 4-9: ULTRA LOW-POWER WAKE-UP INITIALIZATION

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

Note: For more information, see AN879, "Using the Microchip Ultra Low-Power Wake-up Module" (DS00879).

### 6.2 PIC18 Instruction Cycle

#### 6.2.1 CLOCKING SCHEME

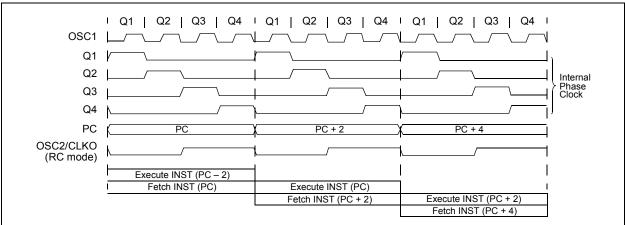

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping, quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the Program Counter is incremented on every Q1, with the instruction fetched from the program memory and latched into the Instruction Register (IR) during Q4.

The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 6-4.

#### 6.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction (such as GOTO) causes the Program Counter to change, two cycles are required to complete the instruction. (See Example 6-3.)

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

| Тсу0                            | TCY1      | Tcy2      | Tcy3      | TcY4        | TCY5          |

|---------------------------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h Fetch 1            | Execute 1 |           | _         |             |               |

| 2. MOVWF PORTB                  | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA SUB_1                    |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (Forced NOP) |           |           | Fetch 4   | Flush (NOP) |               |

| 5. Instruction @ address SUB_1  |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|                                 |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

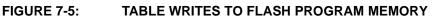

## 7.5 Writing to Flash Program Memory

The programming blocks are:

- PIC18FX5K22 and PIC18FX6K22 32 words or 64 bytes

- PIC18FX7K22 64 words or 128 bytes

Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. The number of holding registers used for programming by the table writes are:

- PIC18FX5K22 and PIC18FX6K22 64

- PIC18FX7K22 128

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 or 128 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write is terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets, and after write operations, is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 or 128 holding registers before executing a write operation.

#### REGISTER 11-14: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W-0                  | R/W-0                                                                                                                 | R/W-0                            | R/W-0         | R/W-0                 | R/W-0            | R/W-0           | R/W-0  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|-----------------------|------------------|-----------------|--------|--|

| TMR7GIE <sup>(1)</sup> | TMR12IE <sup>(1)</sup>                                                                                                | TMR10IE <sup>(1)</sup>           | TMR8IE        | TMR7IE <sup>(1)</sup> | TMR6IE           | TMR5IE          | TMR4IE |  |

| bit 7                  |                                                                                                                       |                                  |               | 1                     |                  |                 | bit C  |  |

|                        |                                                                                                                       |                                  |               |                       |                  |                 |        |  |

| Legend:                |                                                                                                                       |                                  |               |                       |                  |                 |        |  |

| R = Readable           | bit                                                                                                                   | W = Writable I                   | bit           | U = Unimplem          | nented bit, read | l as '0'        |        |  |

| -n = Value at F        | POR                                                                                                                   | '1' = Bit is set                 |               | '0' = Bit is clea     | ared             | x = Bit is unkr | nown   |  |

|                        |                                                                                                                       |                                  |               |                       |                  |                 |        |  |

| bit 7                  |                                                                                                                       | MR7 Gate Inter                   | upt Enable b  | <sub>it</sub> (1)     |                  |                 |        |  |

|                        | 1 = Enabled                                                                                                           |                                  |               |                       |                  |                 |        |  |

| <b>h</b> :+ C          | 0 = Disabled                                                                                                          |                                  | latab lataway | at ⊑aabla bit(1)      |                  |                 |        |  |

| bit 6                  |                                                                                                                       | IR12 to PR12 M<br>the TMR12 to F |               |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR12 to I                   |               |                       |                  |                 |        |  |

| bit 5                  |                                                                                                                       | 1R10 to PR10 N                   |               | •                     |                  |                 |        |  |

|                        |                                                                                                                       | the TMR10 to F                   |               |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR10 to I                   |               | •                     |                  |                 |        |  |

| bit 4                  |                                                                                                                       | R8 to PR8 Matc                   |               |                       |                  |                 |        |  |

|                        | <ul> <li>1 = Enables the TMR8 to PR8 match interrupt</li> <li>0 = Disables the TMR8 to PR8 match interrupt</li> </ul> |                                  |               |                       |                  |                 |        |  |

| bit 3                  |                                                                                                                       | R7 Overflow Int                  |               |                       |                  |                 |        |  |

| bit 5                  |                                                                                                                       | the TMR7 over                    | •             |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR7 over                    |               |                       |                  |                 |        |  |

| bit 2                  | TMR6IE: TMF                                                                                                           | R6 to PR6 Matc                   | h Interrupt E | nable bit             |                  |                 |        |  |

|                        | 1 = Enables the TMR6 to PR6 match interrupt                                                                           |                                  |               |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR6 to P                    |               | •                     |                  |                 |        |  |

| bit 1                  | TMR5IE: TMR5 Overflow Interrupt Enable bit                                                                            |                                  |               |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR5 over<br>the TMR5 over   |               |                       |                  |                 |        |  |

| bit 0                  |                                                                                                                       | R4 to PR4 Matc                   |               |                       |                  |                 |        |  |

|                        |                                                                                                                       | the TMR4 to PF                   |               |                       |                  |                 |        |  |

|                        | 0 = Disables                                                                                                          |                                  |               |                       |                  |                 |        |  |

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

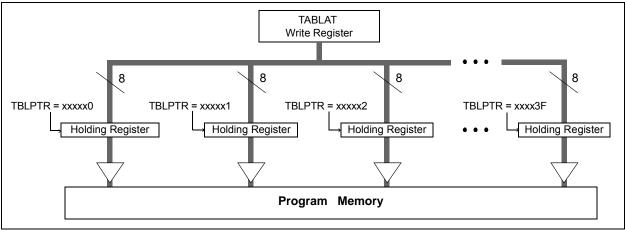

#### 12.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISD and LATD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by setting bit, RDPU (PADCFG1<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

On 80-pin devices, PORTD is multiplexed with the system bus as part of the external memory interface. The I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled, PORTD is the low-order byte of the multiplexed address/data bus (AD<7:0>). The TRISD bits are also overridden.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. For additional information, see Section 12.11 "Parallel Slave Port".

The PORTD also has the I<sup>2</sup>C and SPI functionality on RD4, RD5 and RD6. The pins for SPI are also configurable for open-drain output. Open-drain configuration is selected by setting bit, SSP2OD (ODCON1<0>).

RD0 has a CTMU functionality. RD1 has the functionality for the Timer5 clock input and Timer7 external clock gate input.

| EXAMP | LE 12-4: | INITIALIZING PORTD      |

|-------|----------|-------------------------|

| CLRF  | PORTD    | ; Initialize PORTD by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATD     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 0CFh     | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISD    | ; Set RD<3:0> as inputs |

|       |          | ; RD<5:4> as outputs    |

|       |          | ; RD<7:6> as inputs     |

| Pin Name     | Function            | TRIS<br>Setting | I/O                       | l/O<br>Type | Description                       |

|--------------|---------------------|-----------------|---------------------------|-------------|-----------------------------------|

| RD0/PSP0/    | RD0                 | 0               | 0                         | DIG         | LATD<0> data output.              |

| AD0/CTPLS    |                     | 1               | Ι                         | ST          | PORTD<0> data input.              |

|              | PSP0 <sup>(1)</sup> | x               | Parallel Slave Port data. |             |                                   |

|              | AD0 <sup>(2)</sup>  | х               | I/O                       | TTL         | External Memory Address/Data 0.   |

|              | CTPLS               | х               | 0                         | DIG         | CTMU pulse generator output.      |

| RD1/PSP1/    | RD1                 | 0               | 0                         | DIG         | LATD<1> data output.              |

| AD1/T5CKI/   |                     | 1               | Ι                         | ST          | PORTD<1> data input.              |

| T7G          | PSP1 <sup>(1)</sup> | х               | I/O                       | TTL         | Parallel Slave Port data.         |

|              | AD1 <sup>(2)</sup>  | х               | I/O                       | TTL         | External Memory Address/Data 1.   |

|              | T5CKI               | х               | Ι                         | ST          | Timer5 clock input.               |

|              | T7G                 | х               | Ι                         | ST          | Timer7 external clock gate input. |

| RD2/PSP2/AD2 | RD2                 | 0               | 0                         | DIG         | LATD<2> data output.              |

|              |                     | 1               | Ι                         | ST          | PORTD<2> data input.              |

|              | PSP2 <sup>(1)</sup> | х               | I/O                       | TTL         | Parallel Slave Port data.         |

|              | AD2 <sup>(2)</sup>  | x               | I/O                       | TTL         | External Memory Address/Data 2.   |

### TABLE 12-7 PORTD FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,  $I^2C = I^2C^{\text{TM}}/\text{SMBus Buffer Input}$ , x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: The Parallel Slave Port (PSP) is available only in Microcontroller mode.

2: This feature is available only on PIC18F8XK22 devices.

# 12.11 Parallel Slave Port

PORTD can function as an 8-bit-wide Parallel Slave Port (PSP), or microprocessor port, when control bit, PSPMODE (PSPCON<4>), is set. The port is asynchronously readable and writable by the external world through the RD control input pin (RE0/P2D/RD/AD8) and WR control input pin (RE1/P2C/WR/AD9).

| Note: | The Parallel Slave Port is available only in |

|-------|----------------------------------------------|

|       | Microcontroller mode.                        |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an eight-bit latch.

Setting bit, PSPMODE, enables port pin, RE0/P2D/RD/AD8, to be the RD input, RE1/P2C/WR/AD9 to be the WR input and RE2/P2B/CCP10/CS/AD10 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (= 111).

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits (PIR1<7> and PSPCON<7>, respectively) are set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit (PSPCON<6>) is set. If the user writes new data to PORTD to set OBF, the data is immediately read out, but the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  line is detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 12-4 and Figure 12-5, respectively.

# FIGURE 12-3: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

#### REGISTER 19-3: CCPTMRS2: CCP TIMER SELECT REGISTER 2

| U-0   | U-0 | U-0 | R/W-0                   | U-0 | R/W-0                  | R/W-0   | R/W-0   |

|-------|-----|-----|-------------------------|-----|------------------------|---------|---------|

| —     | —   | —   | C10TSEL0 <sup>(1)</sup> | —   | C9TSEL0 <sup>(1)</sup> | C8TSEL1 | C8TSEL0 |

| bit 7 |     |     |                         |     |                        |         | bit 0   |

| Legend:           |                     |                                         |             |

|-------------------|---------------------|-----------------------------------------|-------------|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit,                  | read as '0' |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared x = Bit is unknown |             |

|                   |                     |                                         |             |

| bit 7-5 Unimple   | mented: Read as '0' |                                         |             |

| DIT 7-5 | Unimplemented: Read as 10                                 |

|---------|-----------------------------------------------------------|

| bit 4   | C10TSEL0: CCP10 Timer Selection bit <sup>(1)</sup>        |

|         | 0 = CCP10 is based off of TMR1/TMR2                       |

|         | 1 = CCP10 is based off of TMR7/TMR2                       |

| bit 3   | Unimplemented: Read as '0'                                |

| bit 2   | C9TSEL0: CCP9 Timer Selection bit <sup>(1)</sup>          |

|         | 0 = CCP9 is based off of TMR1/TMR2                        |

|         | 1 = CCP9 is based off of TMR7/TMR4                        |

| bit 1-0 | C8TSEL<1:0>: CCP8 Timer Selection bits                    |

|         | On Non 32-Byte Device Variants:                           |

|         | 00 = CCP8 is based off of TMR1/TMR2                       |

|         | 01 = CCP8 is based off of TMR7/TMR4                       |

|         | 10 = CCP8 is based off of TMR7/TMR6                       |

|         | 11 = Reserved; do not use                                 |

|         | On 32-Byte Device Variants (PIC18F65K22 and PIC18F85K22): |

|         | 00 = CCP8 is based off of TMR1/TMR2                       |

|         | 01 = CCP8 is based off of TMR1/TMR4                       |

|         | 10 = CCP8 is based off of TMR1/TMR6                       |

|         | 11 - Decembed de petuse                                   |

- 11 = Reserved; do not use

- Note 1: This bit is unimplemented and reads as '0' on devices with 32 Kbytes of program memory (PIC18FX5K22).

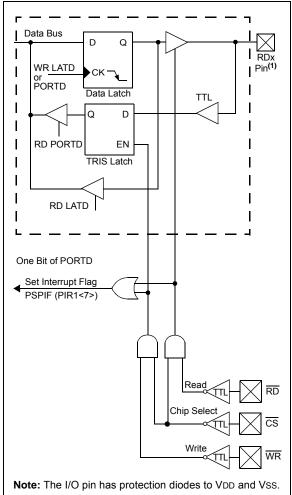

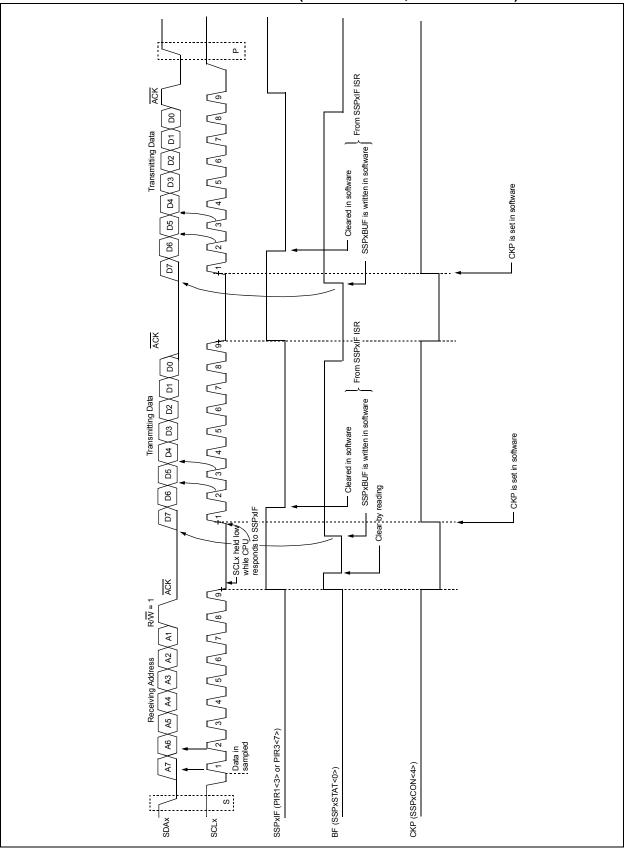

# **PIC18F87K22 FAMILY** I<sup>2</sup>C<sup>TM</sup> SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01011 (RECEPTION, 7-BIT ADDRESS)

FIGURE 21-9:

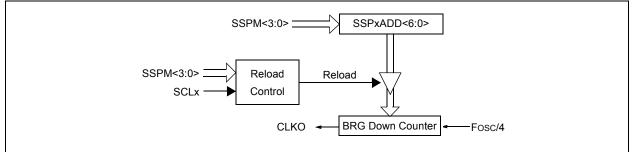

### 21.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 21-19). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by  $\overline{ACK}$ ), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 21-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD. The SSPxADD BRG value of  $0 \ge 00$  is not supported.

### 21.4.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in  $I^2C$  Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

## FIGURE 21-19: BAUD RATE GENERATOR BLOCK DIAGRAM

## TABLE 21-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** A minimum of 16 MHz Fosc is required to get 1 MHz  $I^2C$ .

#### REGISTER 23-10: ANCON2: A/D PORT CONFIGURATION REGISTER 2

| R/W-1                  | R/W-1                  | R/W-1                  | R/W-1                  | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|------------------------|------------------------|------------------------|------------------------|---------|---------|---------|---------|

| ANSEL23 <sup>(1)</sup> | ANSEL22 <sup>(1)</sup> | ANSEL21 <sup>(1)</sup> | ANSEL20 <sup>(1)</sup> | ANSEL19 | ANSEL18 | ANSEL17 | ANSEL16 |

| bit 7                  |                        |                        |                        |         |         |         | bit 0   |

|                        |                        |                        |                        |         |         |         |         |

| Leaend:                |                        |                        |                        |         |         |         |         |

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-0 ANSEL<23:16>: Analog Port Configuration bits (AN23 through AN16)<sup>(1)</sup>

- 1 = Pin is configured as an analog channel; digital input is disabled and any inputs read as '0'

0 = Pin is configured as a digital port

- **Note 1:** AN15 through AN12 and AN23 through AN20 are implemented only on 80-pin devices. For 64-pin devices, the corresponding ANSELx bits are still implemented for these channels, but have no effect.

The analog reference voltage is software-selectable to either the device's positive and negative supply voltage (AVDD and AVSS) or the voltage level on the RA3/AN3/VREF+ and RA2/AN2/VREF- pins. VREF+ has two additional Internal Reference Voltage selections: 2.048V and 4.096V.

The A/D Converter can uniquely operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D Converter's internal RC oscillator.

The output of the Sample-and-Hold (S/H) is the input into the converter, which generates the result via successive approximation.

Each port pin associated with the A/D Converter can be configured as an analog input or a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0<1>) is cleared and the A/D Interrupt Flag bit, ADIF (PIR1<6>), is set.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted. The value in the ADRESH:ADRESL register pair is not modified for a Power-on Reset. These registers will contain unknown data after a Power-on Reset.

The block diagram of the A/D module is shown in Figure 23-4.

### 24.6 Comparator Interrupts

The comparator interrupt flag is set whenever any of the following occurs:

- · Low-to-high transition of the comparator output

- High-to-low transition of the comparator output

- Any change in the comparator output

The comparator interrupt selection is done by the EVPOL<1:0> bits in the CMxCON register (CMxCON<4:3>).

In order to provide maximum flexibility, the output of the comparator may be inverted using the CPOL bit in the CMxCON register (CMxCON<5>). This is functionally identical to reversing the inverting and non-inverting inputs of the comparator for a particular mode.

An interrupt is generated on the low-to-high or high-tolow transition of the comparator output. This mode of interrupt generation is dependent on EVPOL<1:0> in the CMxCON register. When EVPOL<1:0> = 01 or 10, the interrupt is generated on a low-to-high or high-tolow transition of the comparator output. Once the interrupt is generated, it is required to clear the interrupt flag by software. When EVPOL<1:0> = 11, the comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMSTAT<7:5>, to determine the actual change that occurred.

The CMPxIF bits (PIR6<2:0>) are the Comparator Interrupt Flags. The CMPxIF bits must be reset by clearing them. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated. Table 24-2 shows the interrupt generation with respect to comparator input voltages and EVPOL bit settings.

Both the CMPxIE bits (PIE6<2:0>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMPxIF bits will still be set if an interrupt condition occurs.

A simplified diagram of the interrupt section is shown in Figure 24-3.

Note: The CMPxIF bits will not be set when EVPOL<1:0> = 00.

| CPOL | EVPOL<1:0> | Comparator<br>Input Change | CxOUT Transition | Interrupt<br>Generated |

|------|------------|----------------------------|------------------|------------------------|

|      | 0.0        | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 00         | VIN+ < VIN-                | High-to-Low      | No                     |

|      | 01         | VIN+ > VIN-                | Low-to-High      | Yes                    |

| 0    | UL         | Vin+ < Vin-                | High-to-Low      | No                     |

| 0    | 1.0        | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 10         | Vin+ < Vin-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ > VIN-                | Low-to-High      | Yes                    |

|      | 11         | VIN+ < VIN-                | High-to-Low      | Yes                    |

|      | 00         | VIN+ > VIN-                | High-to-Low      | No                     |

|      | 00         | VIN+ < VIN-                | Low-to-High      | No                     |

|      | 01         | VIN+ > VIN-                | High-to-Low      | No                     |

| 1    | UL         | VIN+ < VIN-                | Low-to-High      | Yes                    |

| 1    | 1.0        | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 10         | VIN+ < VIN-                | Low-to-High      | No                     |

|      | 11         | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ < VIN-                | Low-to-High      | Yes                    |

TABLE 24-2:

COMPARATOR INTERRUPT GENERATION

# 28.0 SPECIAL FEATURES OF THE CPU

The PIC18F87K22 family of devices includes several features intended to maximize reliability and minimize cost through elimination of external components. These include:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT) and On-chip Regulator

- · Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, the PIC18F87K22 family of devices has a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator (LF-INTOSC) also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

# 28.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location, 300000h.

The user will note that address, 300000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Software programming of the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal Operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 7.5 "Writing to Flash Program Memory".

#### TABLE 29-2: PIC18F87K22 FAMILY INSTRUCTION SET

| Operands         Lsb         Arrected           BTTE-ORIENTED OPERATIONS           ADDWF         f, d, a         Add WREG and f         1         0010         00da         ffff         ffff         C, D, C, Z, OV, N         1, 2           ADDWF         f, d, a         Add WREG and Carry bit to f         1         0010         00da         ffff         ffff         C, D, C, Z, OV, N         1, 2           ANDWF         f, d, a         Add WREG and G         1         0010         00da         ffff         ffff         C, D, C, Z, OV, N         1, 2           CLRF         f, a         Clear f         1         0110         101a         fffff         Ffff         Z         2           COMF         f, d, a         Compare f with WREG, Skip >         1 (2 or 3)         0110         010a         ffff         ffff         None         4           CPFSSEQ         f, d, a         Decrement f, Skip if 0         1 (2 or 3)         0110         010a         ffff         ffff         None         1, 2         3           DECFSZ         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0101         1da         ffff         ffff         None         1, 2           INCF <th>Mnem</th> <th>onic,</th> <th>Description</th> <th>Cualas</th> <th>16-E</th> <th>Bit Instr</th> <th>uction V</th> <th>Vord</th> <th>Status</th> <th>Natas</th> | Mnem     | onic,                           | Description                              | Cualas     | 16-E | Bit Instr | uction V | Vord | Status          | Natas      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| ADDWFf, d, aAdd WREG and f1001001dafffffffffC, DC, Z, OV, N1, 2ADDWFCf, d, aAdd WREG with f1001000dafffffffffC, DC, Z, OV, N1, 2ANDWFf, d, aAND WREG with f1001001dafffffffffZ, N1, 2CRFf, aClear f10010101affffffffZ, N1, 2COMFf, aCompare f with WREG, Skip >110010101affffNone4CPFSQTf, aCompare f with WREG, Skip >110000101affffNone4CPFSQTf, d, aDecrement f, Skip if 0110000101affffffffNone1, 2, 3DECFSZf, d, aDecrement f, Skip if Not 0112 or 30110100affffffffNone1, 2, 3NICFSZf, d, aIncrement f, Skip if Not 0112 or 3010111daffffffffNone1, 2, 3NICFSZf, d, aIncrement f, Skip if Not 0112 or 3010110daffffffffNone1, 2, 3NINCFSZf, d, aIncrement f, Skip if Not 0112 or 3010110daffffffffNone1, 2, 3NOVFf, d, aIncrement f, Skip if Not 0110 or 3010110daffffNone1, 2 <tr< th=""><th>Opera</th><th>Inds</th><th>Description</th><th>Cycles</th><th>MSb</th><th></th><th></th><th>LSb</th><th>Affected</th><th>Notes</th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Opera    | Inds                            | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BYTE-ORI | ENTED O                         | OPERATIONS                               |            |      |           |          |      |                 |            |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1, 2       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CLRF     | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMF     | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSLT         f, a         Compare f with WREG, Skip <         1 (2 or 3)         0110         000a         ffff         ffff         None         1, 2           DECF         f, d, a         Decrement f         Skip if 0         1         (2 or 3)         0110         000a         ffff         ffff         ffff         None         1, 2, 3,           DECFSZ         f, d, a         Decrement f, Skip if 0         1 (2 or 3)         0010         11da         ffff         None         1, 2, 3,           DCFSNZ         f, d, a         Increment f         Increment f         1         0010         11da         ffff         None         1, 2, 3,           INCF         f, d, a         Increment f, Skip if 0         1 (2 or 3)         0101         11da         ffff         ffff         None         1, 2, 3,           INCFSZ         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0101         10da         ffff         ffff         None         1, 2, 3,           INCFSZ         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0100         10da         ffff         ffff         None         1, 2         3,           INCF         f, d, a         Move f         1                                                                                                                                                | CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| DECF         f, d, a         Decrement f         1         0000         01da         ffff         ffff         C, D, C, Z, OV, N         1, 2, 3,           DECFSZ         f, d, a         Decrement f, Skip if 0         1 (2 or 3)         0101         11da         ffff         ffff         None         1, 2, 3,           INCF         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0101         11da         ffff         ffff         None         1, 2, 3,           INCFS         f, d, a         Increment f, Skip if 0         1 (2 or 3)         0010         10da         ffff         ffff         None         1, 2, 3,           INCFSZ         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0010         10da         ffff         ffff         None         1, 2, 3,           INCFSZ         f, d, a         Increment f, Skip if Not 0         1 (2 or 3)         0100         10da         ffff         ffff         None         1, 2, 3,           INCFS         f, d, a         Move f         Nove f         1 (2 or 3)         0100         10da         ffff         ffff         None         1, 2           MOVF         f, d, a         Move f (source) to 1st word         1         01010                                                                                                                              | CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DECF     | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFf, d, a<br>Increment fIncrement f1001010daffffffffC, DC, Z, OV, N1, 2, 3,<br>4INCFSZf, d, a<br>Increment f, Skip if Not 01 (2 or 3)001111daffffffffNone1, 2INFSNZf, d, a<br>Inclusive OR WREG with f1000100daffffffffNone1, 2IORWFf, d, a<br>MOVFMove f1000100daffffffffNone1, 2MOVFf, d, a<br>Move fs (source) to1st word<br>f_d (destination) 2nd word1001000dafffffffffNone1, 2MOVWFf, a<br>Move fs (source) to1st word<br>f_d (destination) 2nd word10110111affffffffNone1, 2MOUWFf, a<br>Multiply WREG with f10000001affffffffNone1, 2NEGFf, a<br>Rotate Left f through Carry10110110affffffffNone1, 2RRCFf, d, a<br>Rotate Left f (No Carry)10101010affffffffZ, N1, 2RRNCFf, d, a<br>Subtract MREG from f10101100affffffffZ, N1, 2SUBWFf, d, a<br>Subtract WREG from f1010111daffffffffC, DC, Z, OV, N1, 2SUBWFBf, d, a<br>Swap Nibbles in f1010110daffffffffC, DC, Z, OV, N1, 2SWAPFf, d, a<br>F, d, a <td< td=""><td>DECFSZ</td><td>f, d, a</td><td>Decrement f, Skip if 0</td><td>1 (2 or 3)</td><td>0010</td><td>11da</td><td>ffff</td><td>ffff</td><td>None</td><td>1, 2, 3, 4</td></td<>                                                                                                                                                                                                                                                                                                   | DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INFSNZf, d, a<br>Increment f, Skip if Not 01 (2 or 3)<br>(2 or 3)010010daffffffffNone1, 2IORWFf, d, a<br>MOVFInclusive OR WREG with f1000100daffffffffZ, N1, 2MOVFf, d, a<br>Move fMove fMove f1010100daffffffffZ, N1, 2MOVFf, d, a<br>Move fMove fSource) to1st word<br>f1010100daffffffffZ, N1MOVFf, a<br>fMove fMove f1010100daffffffffNone1, 2MOVFf, a<br>Move fMove f101010101ffffffffNone1, 2MOVWFf, a<br>Multiply WREG to fMove WREG to f10110111affffffffNone1, 2MEGFf, a<br>Negate fNegate f10110110afffffffffNone1, 2RLCFf, d, a<br>Rotate Left f through Carry1001101daffffffffZ, N1, 2RRCFf, d, a<br>Subtract f from WREG with<br>SUBWFRotate Right f (No Carry)10101010affffffffZ, N1, 2SUBWFf, d, a<br>Subtract WREG from f10101100affffffffC, DC, Z, OV, N1, 2SUBWFf, d, a<br>Swap Nibbles in f1010110daffffffffC, DC, Z, OV, N1, 2SWAPF <td>INCF</td> <td>f, d, a</td> <td>Increment f</td> <td>1</td> <td>0010</td> <td>10da</td> <td>ffff</td> <td>ffff</td> <td>C, DC, Z, OV, N</td> <td>1, 2, 3, 4</td>                                                                                                                                                                                                                                                                                                                                                                                | INCF     | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |