Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 64MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (32K x 16)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66k22t-i-mrrsl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.3 Details on Individual Family Members

Devices in the PIC18F87K22 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in these ways:

- Flash Program Memory:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – 32 Kbytes

- PIC18FX6K22 (PIC18F66K22 and PIC18F86K22) 64 Kbytes

- PIC18FX7K22 (PIC18F67K22 and PIC18F87K22) 128 Kbytes

- Data RAM:

- All devices except PIC18FX5K22 4 Kbytes

- PIC18FX5K22 2 Kbytes

- I/O Ports:

- PIC18F6XK22 (64-pin devices) 7 bidirectional ports

- PIC18F8XK22 (80-pin devices) 9 bidirectional ports

- CCP modules:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – 5 CCP modules

- PIC18FX6K22 and PIC18FX7K22 (PIC18F66K22, PIC18F86K22, PIC18F67K22, and PIC18F87K22) – 7 CCP modules

- · Timer modules:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – Four 8-bit timer/counters and four 16-bit timer/counters

- PIC18FX6K22 and PIC18FX7K22 (PIC18F66K22, PIC18F86K22, PIC18F67K22, and PIC18F87K22) – Six 8-bit timer/counters and five 16-bit timer/counters

- A/D Channels:

- PIC18F6XK22 (64-pin devices) 24 channels

- PIC18F8XK22 (80-pin devices) 16 channels

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

= Open-Drain (no P diode to VDD)

#### TABLE 1-4: PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name              | Pin Number       | Pin   | Buffer    | Description                                   |

|-----------------------|------------------|-------|-----------|-----------------------------------------------|

|                       | TQFP             | Туре  | Туре      | Description                                   |

| RH7/CCP6/P1B/AN15     | 19               |       |           |                                               |

| RH7                   |                  | I/O   | ST        | Digital I/O.                                  |

| CCP6 <sup>(5)</sup>   |                  | I/O   | ST        | Capture 6 input/Compare 6 output/PWM6 output. |

| P1B                   |                  | 0     | —         | ECCP1 PWM Output B.                           |

| AN15                  |                  | I.    | Analog    | Analog Input 15.                              |

| Legend: TTL = TTL com | patible input    |       |           | CMOS = CMOS compatible input or output        |

| ST = Schmitt T        | rigger input wit | h CMC | OS levels | Analog = Analog input                         |

| I = Input             |                  |       |           | O = Output                                    |

= Power Ρ

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

OD

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

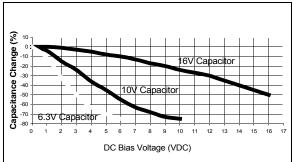

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

| R/W-0         | R/W-0                                           | R/W-0                      | R/W-0            | R/W-0                                                | R/W-0            | R/W-0           | R/W-0         |

|---------------|-------------------------------------------------|----------------------------|------------------|------------------------------------------------------|------------------|-----------------|---------------|

| INTSRC        | PLLEN                                           | TUN5                       | TUN4             | TUN3                                                 | TUN2             | TUN1            | TUN0          |

| bit 7         |                                                 |                            |                  |                                                      |                  |                 | bit 0         |

| Legend:       |                                                 |                            |                  |                                                      |                  |                 |               |

| R = Readable  | e bit                                           | W = Writable               | bit              | U = Unimplem                                         | nented bit, read | l as '0'        |               |

| -n = Value at | POR                                             | '1' = Bit is set           |                  | '0' = Bit is clea                                    | ared             | x = Bit is unkr | iown          |

| bit 7         | 1 = 31.25 k⊦                                    | z device clock             | derived from 1   | y Source Select<br>6 MHz INTOSC :<br>RC 31 kHz oscil | source (divide-  |                 | I, HF-INTOSC) |

| bit 6         |                                                 | quency Multiplie<br>nabled |                  |                                                      |                  | ,               |               |

| bit 5-0       | 011111 = Ma<br>0000001<br>000000 = Ce<br>111111 | aximum frequer<br>•<br>•   | ; fast RC oscill | Frequency Tunir                                      | -                | d frequency     |               |

### REGISTER 3-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| R/W-0        | U-0                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                     | R/W-0                                            | R/W-0           | R/W-0            | R/W-0      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|------------------|------------|

| ROON         |                                                                                                                                                                                                                                                                                           | ROSSLP                                                                                                                                                                                                                                                                                                                                          | ROSEL <sup>(1)</sup>                                                                                                                                                                                                                                                                      | RODIV3                                           | RODIV2          | RODIV1           | RODIV0     |

| bit 7        |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                  |                 |                  | bit        |

| Legend:      |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                  |                 |                  |            |

| R = Readab   | ole bit                                                                                                                                                                                                                                                                                   | W = Writable                                                                                                                                                                                                                                                                                                                                    | bit                                                                                                                                                                                                                                                                                       | U = Unimpler                                     | nented bit, rea | id as '0'        |            |

| -n = Value a | at POR                                                                                                                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                           | '0' = Bit is cle                                 | ared            | x = Bit is unkr  | nown       |

| bit 7        | ROON: Refer                                                                                                                                                                                                                                                                               | rence Oscillato                                                                                                                                                                                                                                                                                                                                 | r Output Enabl                                                                                                                                                                                                                                                                            | e bit                                            |                 |                  |            |

|              |                                                                                                                                                                                                                                                                                           | e oscillator out <sub>l</sub><br>e oscillator out                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                           | on REFO pin                                      |                 |                  |            |

| bit 6        | Unimplemen                                                                                                                                                                                                                                                                                | ted: Read as '                                                                                                                                                                                                                                                                                                                                  | 0'                                                                                                                                                                                                                                                                                        |                                                  |                 |                  |            |

| bit 5        | ROSSLP: Re                                                                                                                                                                                                                                                                                | ference Oscilla                                                                                                                                                                                                                                                                                                                                 | ator Output Sto                                                                                                                                                                                                                                                                           | p in Sleep bit                                   |                 |                  |            |

|              |                                                                                                                                                                                                                                                                                           | e oscillator con<br>e oscillator is d                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                           |                                                  |                 |                  |            |

| bit 4        | ROSEL: Refe                                                                                                                                                                                                                                                                               | erence Oscillato                                                                                                                                                                                                                                                                                                                                | or Source Sele                                                                                                                                                                                                                                                                            | ect bit <sup>(1)</sup>                           |                 |                  |            |

|              | 1 = Primary of                                                                                                                                                                                                                                                                            | scillator (EC or                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                           | o the here ale                                   | ck              |                  |            |

|              |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                           |                                                  |                 | ock switching of | the device |

| bit 3-0      | 0 = System c                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                 | the base clock                                                                                                                                                                                                                                                                            | k; base clock r                                  |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1110 = Base                                                                                                                                                                                                                                  | lock is used as<br>Reference Os<br>clock value div<br>clock value div                                                                                                                                                                                                                                                                           | the base clock<br>cillator Divisor<br>rided by 32,768<br>rided by 16,384                                                                                                                                                                                                                  | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br><b>RODIV&lt;3:0&gt;</b><br>1111 = Base<br>1110 = Base<br>1101 = Base                                                                                                                                                                                                      | lock is used as<br>Reference Os<br>clock value div<br>clock value div<br>clock value div                                                                                                                                                                                                                                                        | the base clock<br>cillator Divisor<br>vided by 32,764<br>vided by 16,384<br>vided by 8,192                                                                                                                                                                                                | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br><b>RODIV&lt;3:0&gt;</b><br>1111 = Base<br>1110 = Base<br>1101 = Base<br>1100 = Base                                                                                                                                                                                       | lock is used as<br>Reference Os<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                                                                                                                                                     | the base clock<br>cillator Divisor<br>vided by 32,764<br>vided by 16,384<br>vided by 8,192<br>vided by 4,096                                                                                                                                                                              | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br><b>RODIV&lt;3:0&gt;</b><br>1111 = Base<br>1110 = Base<br>1101 = Base<br>1100 = Base<br>1011 = Base                                                                                                                                                                        | lock is used as<br>Reference Os<br>clock value div<br>clock value div<br>clock value div                                                                                                                                                                                                                                                        | the base clock<br>cillator Divisor<br>vided by 32,768<br>vided by 16,384<br>vided by 8,192<br>vided by 4,096<br>vided by 2,048                                                                                                                                                            | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1010 = Base<br>1001 = Base                                                                                                                                                       | lock is used as<br>Reference Os<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                                                                                            | the base clock<br>cillator Divisor<br>vided by 32,764<br>vided by 16,384<br>vided by 8,192<br>vided by 4,096<br>vided by 2,048<br>vided by 1,024<br>vided by 512                                                                                                                          | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1110 = Base<br>1101 = Base<br>1010 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base                                                                                                                                        | lock is used as<br>Reference Os<br>clock value div<br>clock value div                                                                                                                                                         | the base clock<br>cillator Divisor<br>rided by 32,764<br>rided by 16,384<br>rided by 8,192<br>rided by 4,096<br>rided by 2,048<br>rided by 1,024<br>rided by 512<br>rided by 256                                                                                                          | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1001 = Base<br>1010 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0111 = Base                                                                                                                         | lock is used as<br>Reference Os<br>clock value div<br>clock value div                                                                                                                   | the base clock<br>cillator Divisor<br>rided by 32,764<br>rided by 16,384<br>rided by 8,192<br>rided by 4,096<br>rided by 2,048<br>rided by 1,024<br>rided by 512<br>rided by 256<br>rided by 128                                                                                          | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1001 = Base<br>1010 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0111 = Base<br>0110 = Base                                                                                                          | lock is used as<br>Reference Os<br>clock value div<br>clock value div                                                                                                                                                         | the base clock<br>cillator Divisor<br>rided by 32,764<br>rided by 16,384<br>rided by 8,192<br>rided by 4,096<br>rided by 2,048<br>rided by 2,048<br>rided by 1,024<br>rided by 512<br>rided by 256<br>rided by 128<br>rided by 64                                                         | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1001 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0101 = Base<br>0111 = Base<br>0110 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base                                              | lock is used as<br>Reference Os<br>clock value div<br>clock value div                    | the base clock<br>cillator Divisor<br>rided by 32,764<br>rided by 16,384<br>rided by 8,192<br>rided by 4,096<br>rided by 2,048<br>rided by 1,024<br>rided by 512<br>rided by 512<br>rided by 256<br>rided by 128<br>rided by 64<br>rided by 32<br>rided by 16                             | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1001 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base                               | lock is used as<br>Reference Os<br>clock value div<br>clock value div | the base clock<br>cillator Divisor<br>vided by 32,764<br>vided by 16,384<br>vided by 8,192<br>vided by 4,096<br>vided by 2,048<br>vided by 1,024<br>vided by 512<br>vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8               | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

| bit 3-0      | 0 = System c<br>RODIV<3:0><br>1111 = Base<br>1100 = Base<br>1001 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0011 = Base | lock is used as<br>Reference Os<br>clock value div<br>clock value div                    | the base clock<br>cillator Divisor<br>vided by 32,764<br>vided by 16,384<br>vided by 8,192<br>vided by 4,096<br>vided by 2,048<br>vided by 1,024<br>vided by 512<br>vided by 512<br>vided by 256<br>vided by 128<br>vided by 64<br>vided by 32<br>vided by 16<br>vided by 8<br>vided by 4 | k; base clock r<br><sup>-</sup> Select bits<br>8 |                 | ock switching of | the device |

### REGISTER 3-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

**Note 1:** For ROSEL (REVOCON<4>), the primary oscillator is available only when configured as the default via the FOSC settings. This is regardless of whether the device is in Sleep mode.

| TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS |                    |             |                                    |                                                                                |                                 |  |  |  |

|--------------------------------------------------------|--------------------|-------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Register                                               | Applicable Devices |             | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| TOSU                                                   | PIC18F6XK22        | PIC18F8XK22 | 0 0000                             | 0 0000                                                                         | 0 uuuu <b>(1)</b>               |  |  |  |

| TOSH                                                   | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(1)</b>            |  |  |  |

| TOSL                                                   | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(1)</b>            |  |  |  |

| STKPTR                                                 | PIC18F6XK22        | PIC18F8XK22 | 00-0 0000                          | uu-0 0000                                                                      | uu-u uuuu <b>(1)</b>            |  |  |  |

| PCLATU                                                 | PIC18F6XK22        | PIC18F8XK22 | 0 0000                             | 0 0000                                                                         | u uuuu                          |  |  |  |

| PCLATH                                                 | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| PCL                                                    | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | PC + 2 <sup>(2)</sup>           |  |  |  |

| TBLPTRU                                                | PIC18F6XK22        | PIC18F8XK22 | 00 0000                            | 00 0000                                                                        | uu uuuu                         |  |  |  |

| TBLPTRH                                                | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| TBLPTRL                                                | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| TABLAT                                                 | PIC18F6XK22        | PIC18F8XK22 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| PRODH                                                  | PIC18F6XK22        | PIC18F8XK22 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| PRODL                                                  | PIC18F6XK22        | PIC18F8XK22 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| INTCON                                                 | PIC18F6XK22        | PIC18F8XK22 | 0000 000x                          | 0000 000u                                                                      | uuuu uuuu <b>(3)</b>            |  |  |  |

| INTCON2                                                | PIC18F6XK22        | PIC18F8XK22 | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu <b>(3)</b>            |  |  |  |

| INTCON3                                                | PIC18F6XK22        | PIC18F8XK22 | 1100 0000                          | 1100 0000                                                                      | uuuu uuuu <sup>(3)</sup>        |  |  |  |

| INDF0                                                  | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| POSTINC0                                               | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| POSTDEC0                                               | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| PREINC0                                                | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| PLUSW0                                                 | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| FSR0H                                                  | PIC18F6XK22        | PIC18F8XK22 | 0000                               | 0000                                                                           | uuuu                            |  |  |  |

| FSR0L                                                  | PIC18F6XK22        | PIC18F8XK22 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| WREG                                                   | PIC18F6XK22        | PIC18F8XK22 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| INDF1                                                  | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| POSTINC1                                               | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| POSTDEC1                                               | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| PREINC1                                                | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| PLUSW1                                                 | PIC18F6XK22        | PIC18F8XK22 | N/A                                | N/A                                                                            | N/A                             |  |  |  |

| FSR1H                                                  | PIC18F6XK22        | PIC18F8XK22 | 0000                               | 0000                                                                           | uuuu                            |  |  |  |

| FSR1L                                                  | PIC18F6XK22        | PIC18F8XK22 | XXXX XXXX                          | սսսս սսսս                                                                      | uuuu uuuu                       |  |  |  |

| BSR                                                    | PIC18F6XK22        | PIC18F8XK22 | 0000                               | 0000                                                                           | uuuu                            |  |  |  |

### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt, and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

| TABLE 5-2:      |                            |                            |                                    | GISTERS (CONTINU<br>MCLR Resets,                               |                                 |  |

|-----------------|----------------------------|----------------------------|------------------------------------|----------------------------------------------------------------|---------------------------------|--|

| Register Applic |                            | e Devices                  | Power-on Reset,<br>Brown-out Reset | WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| ECCP1AS         | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| ECCP1DEL        | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CCPR1H          | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCPR1L          | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCP1CON         | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| PIR5            | PIC18F65K22                | PIC18F85K22                | 0 -000                             | 0 -000                                                         | u -uuu                          |  |

| PIR5            | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| PIE5            | PIC18F65K22                | PIC18F85K22                | 0 0000                             | 0 0000                                                         | u uuuu <b>(1)</b>               |  |

| PIE5            | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 000                           | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| IPR4            | PIC18F65K22                | PIC18F85K22                | 11 1111                            | 11 1111                                                        | uu uuuu                         |  |

| IPR4            | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 1111 1111                          | 1111 1111                                                      | uuuu uuuu                       |  |

| PIR4            | PIC18F65K22                | PIC18F85K22                | 00 0000                            | 00 0000                                                        | uu uuuu <b>(1)</b>              |  |

| PIR4            | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| PIE4            | PIC18F65K22                | PIC18F85K22                | 00 0000                            | 00 0000                                                        | uu uuuu                         |  |

| PIE4            | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CVRCON          | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CMSTAT          | PIC18F6XK22                | PIC18F8XK22                | xxx                                | xxx                                                            | uuu                             |  |

| TMR3H           | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx                          | սսսս սսսս                                                      | սսսս սսսս                       |  |

| TMR3L           | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx                          | սսսս սսսս                                                      | սսսս սսսս                       |  |

| T3CON           | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 00x0 0x00                                                      | սսսս սսսս                       |  |

| T3GCON          | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00                          | 0000 0000                                                      | սսսս սսսս                       |  |

| SPBRG1          | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| RCREG1          | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | սսսս սսսս                       |  |

| TXREG1          | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | xxxx xxxx                                                      | սսսս սսսս                       |  |

| TXSTA1          | PIC18F6XK22                | PIC18F8XK22                | 0000 0010                          | 0000 0010                                                      | սսսս սսսս                       |  |

| RCSTA1          | PIC18F6XK22                | PIC18F8XK22                | 0000 000x                          | 0000 000x                                                      | սսսս սսսս                       |  |

| T1GCON          | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00                          | 00x0 0x00                                                      | uuuu -uuu                       |  |

| IPR6            | PIC18F6XK22                | PIC18F8XK22                | 1 -111                             | 1 -111                                                         | u -uuu                          |  |

| HLVDCON         | PIC18F6XK22                | PIC18F8XK22                | 0000 0101                          | 0000 0101                                                      | uuuu uuuu                       |  |

| PSPCON          | PIC18F6XK22                | PIC18F8XK22                | 0000                               | 0000                                                           | uuuu                            |  |

| PIR6            | PIC18F6XK22                | PIC18F8XK22                | 0 -000                             | 0 -000                                                         | u -uuu                          |  |

### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt, and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

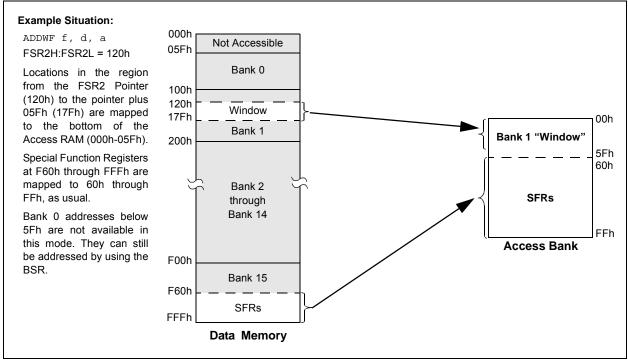

### 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space.

The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described. (See **Section 6.3.2 "Access Bank"**.) An example of Access Bank remapping in this addressing mode is shown in Figure 6-10. Remapping the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit = 1) will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

### 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

### FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

### 8.0 EXTERNAL MEMORY BUS

| Note: | The   | External  | Memory     | Bus    | is | not |

|-------|-------|-----------|------------|--------|----|-----|

|       | imple | mented on | 64-pin dev | vices. |    |     |

The External Memory Bus (EMB) allows the device to access external memory devices (such as Flash, EPROM or SRAM) as program or data memory. It supports both 8 and 16-Bit Data Width modes and three address widths of up to 20 bits.

The bus is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals.

A list of the pins and their functions is provided in Table 8-1.

| TABLE 8-1: | PIC18F87K22 FAMILY EXTERNAL BUS – I/O PORT FUNCTIONS |

|------------|------------------------------------------------------|

| Name     | Port  | Bit | External Memory Bus Function           |

|----------|-------|-----|----------------------------------------|

| RD0/AD0  | PORTD | 0   | Address Bit 0 or Data Bit 0            |

| RD1/AD1  | PORTD | 1   | Address Bit 1 or Data Bit 1            |

| RD2/AD2  | PORTD | 2   | Address Bit 2 or Data Bit 2            |

| RD3/AD3  | PORTD | 3   | Address Bit 3 or Data Bit 3            |

| RD4/AD4  | PORTD | 4   | Address Bit 4 or Data Bit 4            |

| RD5/AD5  | PORTD | 5   | Address Bit 5 or Data Bit 5            |

| RD6/AD6  | PORTD | 6   | Address Bit 6 or Data Bit 6            |

| RD7/AD7  | PORTD | 7   | Address Bit 7 or Data Bit 7            |

| RE0/AD8  | PORTE | 0   | Address Bit 8 or Data Bit 8            |

| RE1/AD9  | PORTE | 1   | Address Bit 9 or Data Bit 9            |

| RE2/AD10 | PORTE | 2   | Address Bit 10 or Data Bit 10          |

| RE3/AD11 | PORTE | 3   | Address Bit 11 or Data Bit 11          |

| RE4/AD12 | PORTE | 4   | Address Bit 12 or Data Bit 12          |

| RE5/AD13 | PORTE | 5   | Address Bit 13 or Data Bit 13          |

| RE6/AD14 | PORTE | 6   | Address Bit 14 or Data Bit 14          |

| RE7/AD15 | PORTE | 7   | Address Bit 15 or Data Bit 15          |

| RH0/A16  | PORTH | 0   | Address Bit 16                         |

| RH1/A17  | PORTH | 1   | Address Bit 17                         |

| RH2/A18  | PORTH | 2   | Address Bit 18                         |

| RH3/A19  | PORTH | 3   | Address Bit 19                         |

| RJ0/ALE  | PORTJ | 0   | Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | 1   | Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | 2   | Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | 3   | Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | 4   | Byte Address Bit 0 (BA0)               |

| RJ5/CE   | PORTJ | 5   | Chip Enable (CE) Control pin           |

| RJ6/LB   | PORTJ | 6   | Lower Byte Enable (IB) Control pin     |

| RJ7/UB   | PORTJ | 7   | Upper Byte Enable (UB) Control pin     |

**Note:** For the sake of clarity, only I/O port and external bus assignments are shown here. One or more additional multiplexed features may be available on some pins.

### 8.2 Address and Data Width

The PIC18F87K22 family of devices can be independently configured for different address and data widths on the same memory bus. Both address and data width are set by Configuration bits in the CONFIG3L register. As Configuration bits, this means that these options can only be configured by programming the device and are not controllable in software.

The BW bit selects an 8-bit or 16-bit data bus width. Setting this bit (default) selects a data width of 16 bits.

The ABW<1:0> bits determine both the program memory operating mode and the address bus width. The available options are 20-bit, 16-bit and 12-bit, as well as Microcontroller mode (external bus is disabled). Selecting a 16-bit or 12-bit width makes a corresponding number of high-order lines available for I/O functions. These pins are no longer affected by the setting of the EBDIS bit. For example, selecting a 16-Bit Addressing mode (ABW<1:0> = 01) disables A<19:16> and allows PORTH<3:0> to function without interruptions from the bus. Using the smaller address widths allows users to tailor the memory bus to the size of the external memory space for a particular design while freeing up pins for dedicated I/O operation.

Because the ABW bits have the effect of disabling pins for memory bus operations, it is important to always select an address width at least equal to the data width. If a 12-bit address width is used with a 16-bit data width, the upper four bits of data will not be available on the bus.

All combinations of address and data widths require multiplexing of address and data information on the same lines. The address and data multiplexing, as well as I/O ports made available by the use of smaller address widths, are summarized in Table 8-2.

### 8.2.1 ADDRESS SHIFTING ON THE EXTERNAL BUS

By default, the address presented on the external bus is the value of the PC. In practical terms, this means that addresses in the external memory device, below the top of on-chip memory, are unavailable to the microcontroller. To access these physical locations, the glue logic between the microcontroller and the external memory must somehow translate addresses.

To simplify the interface, the external bus offers an extension of Extended Microcontroller mode that automatically performs address shifting. This feature is controlled by the EASHFT Configuration bit. Setting this bit offsets addresses on the bus by the size of the microcontroller's on-chip program memory and sets the bottom address at 0000h. This allows the device to use the entire range of physical addresses of the external memory.

### 8.2.2 21-BIT ADDRESSING

As an extension of 20-bit address width operation, the External Memory Bus can also fully address a 2-Mbyte memory space. This is done by using the Bus Address Bit 0 (BA0) control line as the Least Significant bit of the address. The UB and LB control signals may also be used with certain memory devices to select the upper and lower bytes within a 16-bit wide data word.

This addressing mode is available in both 8-Bit and certain 16-Bit Data Width modes. Additional details are provided in Section 8.6.3 "16-Bit Byte Select Mode" and Section 8.7 "8-Bit Data Width Mode".

| TABLE 0-2. AL | DRESS AND DATA                                                             | A LINES FOR DIFFERE         | INT ADDRESS AND D                                  |                             |

|---------------|----------------------------------------------------------------------------|-----------------------------|----------------------------------------------------|-----------------------------|

| Data Width    | Address Width Multiplexed Data and Address Lines (and Corresponding Ports) |                             | Address Only Lines<br>(and Corresponding<br>Ports) | Ports Available<br>for I/O  |

|               | 12-bit                                                                     |                             | AD<11:8><br>(PORTE<3:0>)                           | PORTE<7:4>,<br>All of PORTH |

| 8-bit         | 16-bit                                                                     | AD<7:0><br>(PORTD<7:0>)     | AD<15:8><br>(PORTE<7:0>)                           | All of PORTH                |

|               | 20-bit                                                                     |                             | A<19:16>, AD<15:8><br>(PORTH<3:0>,<br>PORTE<7:0>)  | _                           |

|               | 16-bit                                                                     | AD<15:0>                    | —                                                  | All of PORTH                |

| 16-bit        | 20-bit                                                                     | (PORTD<7:0>,<br>PORTE<7:0>) | A<19:16><br>(PORTH<3:0>)                           | _                           |

### TABLE 8-2: ADDRESS AND DATA LINES FOR DIFFERENT ADDRESS AND DATA WIDTHS

### 11.0 INTERRUPTS

Members of the PIC18F87K22 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

The registers for controlling interrupt operation are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit Indicating that an interrupt event occurred

- Enable bit Enabling program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit Specifying high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits that enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) and GIEH bit (INTCON<7>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable bit are set, the interrupt will vector immediately to address, 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit that enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit that enables/disables all interrupt sources. All interrupts branch to address, 0008h, in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software, before re-enabling interrupts, to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) that re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

### REGISTER 11-11: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0         | U-0                                             | R/W-0                                                           | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|---------------|-------------------------------------------------|-----------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|---------|

| OSCFIE        | _                                               | SSP2IE                                                          | BCL2IE          | BCL1IE            | HLVDIE          | TMR3IE          | TMR3GIE |

| bit 7         |                                                 |                                                                 |                 |                   |                 |                 | bit 0   |

|               |                                                 |                                                                 |                 |                   |                 |                 |         |

| Legend:       |                                                 |                                                                 |                 |                   |                 |                 |         |

| R = Readable  | e bit                                           | W = Writable I                                                  | bit             | U = Unimplem      | ented bit, read | d as '0'        |         |

| -n = Value at | POR                                             | '1' = Bit is set                                                |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| bit 7         | <b>OSCFIE:</b> Os<br>1 = Enableo<br>0 = Disable |                                                                 | rupt Enable bi  | t                 |                 |                 |         |

| bit 6         | Unimpleme                                       | nted: Read as '0                                                | )'              |                   |                 |                 |         |

| bit 5         | SSP2IE: Ma                                      | ster Synchronou                                                 | s Serial Port 2 | Interrupt Enab    | le bit          |                 |         |

|               |                                                 | s the MSSP inter<br>s the MSSP inter                            |                 |                   |                 |                 |         |

| bit 4         | 1 = Enables                                     | s Collision Interr<br>s the bus collision<br>s the bus collisio | n interrupt     |                   |                 |                 |         |

| bit 3         | BCL1IE: Bu<br>1 = Enablec<br>0 = Disable        | -                                                               | upt Enable bit  |                   |                 |                 |         |

| bit 2         | HLVDIE: Hig<br>1 = Enablec<br>0 = Disable       | -                                                               | Detect Interrup | t Enable bit      |                 |                 |         |

| bit 1         | TMR3IE: TM<br>1 = Enablec<br>0 = Disable        |                                                                 | errupt Enable   | bit               |                 |                 |         |

| bit 0         | <b>TMR3GIE:</b> 1<br>1 = Enabled<br>0 = Disable | -                                                               | rupt Enable b   | it                |                 |                 |         |

### 15.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- Eight-bit Timer and Period registers (TMR2 and PR2, respectively)

- Both registers are readable and writable

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 15-1) that enables or disables the timer, and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 15-1.

### 15.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A four-bit counter/prescaler on the clock input gives the prescale options of direct input, divide-by-4 or divide-by-16. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>).

The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler. (See **Section 15.2 "Timer2 Interrupt**".)

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR)

TMR2 is not cleared when T2CON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 20-2, Register 19-2 and Register 19-3.

### REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7<br>bit 6-3 | Unimplemented: Read as '0'<br>T2OUTPS<3:0>: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>• |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                  | •<br>1111 = 1:16 Postscale                                                                                                           |

| bit 2            | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                       |