Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

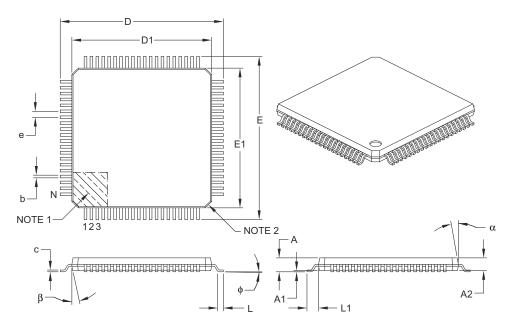

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k22-e-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 5.0 RESET

The PIC18F87K22 family of devices differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Configuration Mismatch (CM) Reset

- f) Brown-out Reset (BOR)

- g) RESET Instruction

- h) Stack Full Reset

- i) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR, and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.3.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 28.2 "Watchdog Timer (WDT)".

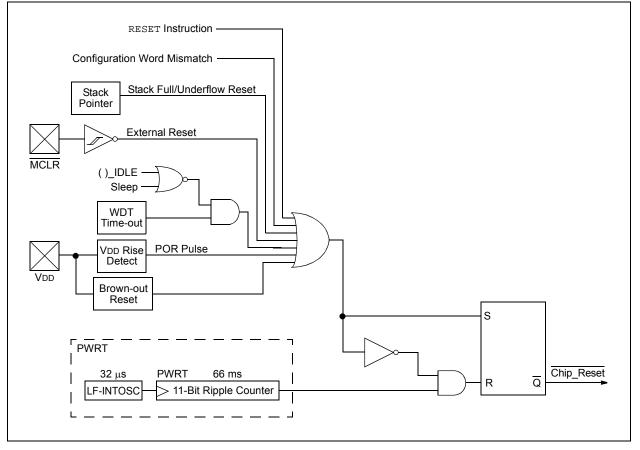

A simplified block diagram of the on-chip Reset circuit is shown in Figure 5-1.

## 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event.

The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.7** "**Reset State of Registers**".

The RCON register also has a control bit for setting interrupt priority (IPEN). Interrupt priority is discussed in **Section 11.0 "Interrupts"**.

## FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 5.7 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register ( $\overline{CM}$ ,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ ) are set or cleared differently in

different Reset situations, as indicated in Table 5-1. These bits are used in software to determine the nature of the Reset.

Table 5-2 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets, and WDT wake-ups.

## TABLE 5-1:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                                        | Program                |    |    | RCON | Register |     |     | STKPTR | Register |

|------------------------------------------------------------------|------------------------|----|----|------|----------|-----|-----|--------|----------|

| Condition                                                        | Counter <sup>(1)</sup> | CM | RI | то   | PD       | POR | BOR | STKFUL | STKUNF   |

| Power-on Reset                                                   | 0000h                  | 1  | 1  | 1    | 1        | 0   | 0   | 0      | 0        |

| RESET instruction                                                | 0000h                  | u  | 0  | u    | u        | u   | u   | u      | u        |

| Brown-out Reset                                                  | 0000h                  | 1  | 1  | 1    | 1        | u   | 0   | u      | u        |

| Configuration Mismatch Reset                                     | 0000h                  | 0  | u  | u    | u        | u   | u   | u      | u        |

| MCLR Reset during power-managed Run modes                        | 0000h                  | u  | u  | 1    | u        | u   | u   | u      | u        |

| MCLR Reset during power-<br>managed Idle modes and<br>Sleep mode | 0000h                  | u  | u  | 1    | 0        | u   | u   | u      | u        |

| MCLR Reset during full-power execution                           | 0000h                  | u  | u  | u    | u        | u   | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                                    | 0000h                  | u  | u  | u    | u        | u   | u   | 1      | u        |

| Stack Underflow Reset<br>(STVREN = 1)                            | 0000h                  | u  | u  | u    | u        | u   | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset, STVREN = 0)          | 0000h                  | u  | u  | u    | u        | u   | u   | u      | 1        |

| WDT time-out during full-power or power-managed Run modes        | 0000h                  | u  | u  | 0    | u        | u   | u   | u      | u        |

| WDT time-out during<br>power-managed Idle or Sleep<br>modes      | PC + 2                 | u  | u  | 0    | 0        | u   | u   | u      | u        |

| Interrupt exit from<br>power-managed modes                       | PC + 2                 | u  | u  | u    | 0        | u   | u   | u      | u        |

Legend: u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

### REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | EEPGD: Flash Program or Data EEPROM Memory Select bit                                              |

|-------|----------------------------------------------------------------------------------------------------|

|       | 1 = Access Flash program memory                                                                    |

|       | 0 = Access data EEPROM memory                                                                      |

| bit 6 | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                        |

|       | 1 = Access Configuration registers                                                                 |

|       | 0 = Access Flash program or data EEPROM memory                                                     |

| bit 5 | Unimplemented: Read as '0'                                                                         |

| bit 4 | FREE: Flash Row Erase Enable bit                                                                   |

|       | 1 = Erase the program memory row addressed by TBLPTR on the next WR command                        |

|       | (cleared by completion of erase operation)                                                         |

|       | 0 = Perform write-only                                                                             |

| bit 3 | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                     |

|       | 1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal |

|       | operation or an improper write attempt)                                                            |

|       | 0 = The write operation completed                                                                  |

| bit 2 | WREN: Flash Program/Data EEPROM Write Enable bit                                                   |

|       | 1 = Allows write cycles to Flash program/data EEPROM                                               |

|       | 0 = Inhibits write cycles to Flash program/data EEPROM                                             |

| bit 1 | WR: Write Control bit                                                                              |

|       | 1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle       |

|       | (The operation is self-timed and the bit is cleared by hardware once the write is complete.        |

|       | The WR bit can only be set (not cleared) in software.)                                             |

|       | 0 = Write cycle to the EEPROM is complete                                                          |

| bit 0 | RD: Read Control bit                                                                               |

|       | 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only |

|       | be set (not cleared) in software. The RD bit cannot be set when EEPGD = 1 or CFGS = 1.)            |

|       | 0 = Does not initiate an EEPROM read                                                               |

|       |                                                                                                    |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

| R/W-1         | R/W-1                          | R/W-1                             | R/W-1             | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|---------------|--------------------------------|-----------------------------------|-------------------|-------------------|-----------------|-----------------|-------|

| RBPU          | INTEDG0                        | INTEDG1                           | INTEDG2           | INTEDG3           | TMR0IP          | INT3IP          | RBIP  |

| bit 7         |                                |                                   |                   |                   |                 |                 | bit ( |

| Legend:       |                                |                                   |                   |                   |                 |                 |       |

| R = Readable  | e bit                          | W = Writable                      | bit               | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR                            | '1' = Bit is set                  |                   | '0' = Bit is clea | ared            | x = Bit is unkr | iown  |

| bit 7         | RBPU: PORT                     | B Pull-up Enat                    | ole bit           |                   |                 |                 |       |

|               |                                | B pull-ups are                    |                   |                   |                 |                 |       |

|               | 0 = PORTB p                    | oull-ups are ena                  | abled by individ  | dual TRIS regis   | ter values      |                 |       |

| bit 6         | INTEDG0: Ex                    | ternal Interrupt                  | 0 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 5         |                                | ternal Interrupt                  | 1 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge<br>on falling edge |                   |                   |                 |                 |       |

| bit 4         | •                              | ternal Interrupt                  | 2 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 3         | INTEDG3: Ex                    | ternal Interrupt                  | 3 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 2         |                                | R0 Overflow Int                   | errupt Priority   | bit               |                 |                 |       |

|               | 1 = High prio<br>0 = Low prior | •                                 |                   |                   |                 |                 |       |

| bit 1         | •                              | External Intern                   | int Priority bit  |                   |                 |                 |       |

|               | 1 = High prio                  |                                   | upt i nonty bit   |                   |                 |                 |       |

|               | 0 = Low prior                  | •                                 |                   |                   |                 |                 |       |

| bit 0         | RBIP: RB Por                   | rt Change Inter                   | rupt Priority bit | 1                 |                 |                 |       |

|               | 1 = High prio                  |                                   | 2                 |                   |                 |                 |       |

|               | 0 = Low prior                  | ity                               |                   |                   |                 |                 |       |

### REGISTER 11-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| Name    | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4   | Bit 3                 | Bit 2   | Bit 1  | Bit 0   |

|---------|------------------------|------------------------|------------------------|---------|-----------------------|---------|--------|---------|

| INTCON  | GIE/GIEH               | PEIE/GIEL              | TMR0IE                 | INT0IE  | RBIE                  | TMR0IF  | INT0IF | RBIF    |

| INTCON2 | RBPU                   | INTEDG0                | INTEDG1                | INTEDG2 | INTEDG3               | TMR0IP  | INT3IP | RBIP    |

| INTCON3 | INT2IP                 | INT1IP                 | INT3IE                 | INT2IE  | INT1IE                | INT3IF  | INT2IF | INT1IF  |

| PIR1    | PSPIP                  | ADIF                   | RC1IF                  | TX1IF   | SSP1IF                | TMR1GIF | TMR2IF | TMR1IF  |

| PIR2    | OSCFIF                 | —                      | SSP2IF                 | BCL2IF  | BCL1IF                | HLVDIF  | TMR3IF | TMR3GIF |

| PIR3    | TMR5GIF                | —                      | RC2IF                  | TX2IF   | CTMUIF                | CCP2IF  | CCP1IF | RTCCIF  |

| PIR4    | CCP10IF <sup>(1)</sup> | CCP9IF <sup>(1)</sup>  | CCP8IF                 | CCP7IF  | CCP6IF                | CCP5IF  | CCP4IF | CCP3IF  |

| PIR5    | TMR7GIF <sup>(1)</sup> | TMR12IF <sup>(1)</sup> | TMR10IF <sup>(1)</sup> | TMR8IF  | TMR7IF <sup>(1)</sup> | TMR6IF  | TMR5IF | TMR4IF  |

| PIR6    | —                      | —                      | _                      | EEIF    | —                     | CMP3IF  | CMP2IF | CMP1IF  |

| PIE1    | PSPIE                  | ADIE                   | RC1IE                  | TX1IE   | SSP1IE                | TMR1GIE | TMR2IE | TMR1IE  |

| PIE2    | OSCFIE                 | —                      | SSP2IE                 | BCL2IE  | BCL1IE                | HLVDIE  | TMR3IE | TMR3GIE |

| PIE3    | TMR5GIE                | —                      | RC2IE                  | TX2IE   | CTMUIE                | CCP2IE  | CCP1IE | RTCCIE  |

| PIE4    | CCP10IE <sup>(1)</sup> | CCP9IE <sup>(1)</sup>  | CCP8IE                 | CCP7IE  | CCP6IE                | CCP5IE  | CCP4IE | CCP3IE  |

| PIE5    | TMR7GIE <sup>(1)</sup> | TMR12IE <sup>(1)</sup> | TMR10IE <sup>(1)</sup> | TMR8IE  | TMR7IE <sup>(1)</sup> | TMR6IE  | TMR5IE | TMR4IE  |

| PIE6    | —                      | —                      | _                      | EEIE    | _                     | CMP3IE  | CMP2IE | CMP1IE  |

| IPR1    | PSPIP                  | ADIP                   | RC1IP                  | TX1IP   | SSP1IP                | TMR1GIP | TMR2IP | TMR1IP  |

| IPR2    | OSCFIP                 | —                      | SSP2IP                 | BCL2IP  | BCL1IP                | HLVDIP  | TMR3IP | TMR3GIP |

| IPR3    | TMR5GIP                | —                      | RC2IP                  | TX2IP   | CTMUIP                | CCP2IP  | CCP1IP | RTCCIP  |

| IPR4    | CCP10IP <sup>(1)</sup> | CCP9IP <sup>(1)</sup>  | CCP8IP                 | CCP7IP  | CCP6IP                | CCP5IP  | CCP4IP | CCP3IP  |

| IPR5    | TMR7GIP <sup>(1)</sup> | TMR12IP <sup>(1)</sup> | TMR10IP <sup>(1)</sup> | TMR8IP  | TMR7IP <sup>(1)</sup> | TMR6IP  | TMR5IP | TMR4IP  |

| IPR6    |                        |                        |                        | EEIP    |                       | CMP3IP  | CMP2IP | CMP1IP  |

| RCON    | IPEN                   | SBOREN                 | CM                     | RI      | TO                    | PD      | POR    | BOR     |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: Shaded cells are not used by the interrupts.

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

#### 12.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISD and LATD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by setting bit, RDPU (PADCFG1<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

On 80-pin devices, PORTD is multiplexed with the system bus as part of the external memory interface. The I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled, PORTD is the low-order byte of the multiplexed address/data bus (AD<7:0>). The TRISD bits are also overridden.

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. For additional information, see Section 12.11 "Parallel Slave Port".

The PORTD also has the I<sup>2</sup>C and SPI functionality on RD4, RD5 and RD6. The pins for SPI are also configurable for open-drain output. Open-drain configuration is selected by setting bit, SSP2OD (ODCON1<0>).

RD0 has a CTMU functionality. RD1 has the functionality for the Timer5 clock input and Timer7 external clock gate input.

| EXAMP | LE 12-4: | INITIALIZING PORTD      |

|-------|----------|-------------------------|

| CLRF  | PORTD    | ; Initialize PORTD by   |

|       |          | ; clearing output       |

|       |          | ; data latches          |

| CLRF  | LATD     | ; Alternate method      |

|       |          | ; to clear output       |

|       |          | ; data latches          |

| MOVLW | 0CFh     | ; Value used to         |

|       |          | ; initialize data       |

|       |          | ; direction             |

| MOVWF | TRISD    | ; Set RD<3:0> as inputs |

|       |          | ; RD<5:4> as outputs    |

|       |          | ; RD<7:6> as inputs     |

| Pin Name     | Function                             | TRIS<br>Setting      | I/O | l/O<br>Type | Description                       |

|--------------|--------------------------------------|----------------------|-----|-------------|-----------------------------------|

| RD0/PSP0/    | RD0                                  | 0                    | 0   | DIG         | LATD<0> data output.              |

| AD0/CTPLS    |                                      | 1                    | Ι   | ST          | PORTD<0> data input.              |

|              | PSP0 <sup>(1)</sup>                  | x                    | I/O | TTL         | Parallel Slave Port data.         |

|              | AD0 <sup>(2)</sup>                   | х                    | I/O | TTL         | External Memory Address/Data 0.   |

|              | CTPLS                                | х                    | 0   | DIG         | CTMU pulse generator output.      |

| RD1/PSP1/    | RD1                                  | 0                    | 0   | DIG         | LATD<1> data output.              |

| AD1/T5CKI/   | 1/T5CKI/ 1 I ST PORTD<1> data input. | PORTD<1> data input. |     |             |                                   |

| T7G          | PSP1 <sup>(1)</sup>                  | х                    | I/O | TTL         | Parallel Slave Port data.         |

|              | AD1 <sup>(2)</sup>                   | х                    | I/O | TTL         | External Memory Address/Data 1.   |

|              | T5CKI                                | х                    | Ι   | ST          | Timer5 clock input.               |

|              | T7G                                  | х                    | Ι   | ST          | Timer7 external clock gate input. |

| RD2/PSP2/AD2 | RD2                                  | 0                    | 0   | DIG         | LATD<2> data output.              |

|              |                                      | 1                    | Ι   | ST          | PORTD<2> data input.              |

|              | PSP2 <sup>(1)</sup>                  | х                    | I/O | TTL         | Parallel Slave Port data.         |

|              | AD2 <sup>(2)</sup>                   | x                    | I/O | TTL         | External Memory Address/Data 2.   |

### TABLE 12-7 PORTD FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,  $I^2C = I^2C^{\text{TM}}/\text{SMBus Buffer Input}$ , x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: The Parallel Slave Port (PSP) is available only in Microcontroller mode.

2: This feature is available only on PIC18F8XK22 devices.

## 13.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 13-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 13-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 13-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 13-1: TOCON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                   |                                         |                                |                    |  |  |  |  |  |  |

|------------|-------------------|-----------------------------------------|--------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | ble bit           | W = Writable bit                        | U = Unimplemented bit          | , read as '0'      |  |  |  |  |  |  |

| -n = Value | at POR            | '1' = Bit is set                        | '0' = Bit is cleared           | x = Bit is unknown |  |  |  |  |  |  |

|            |                   |                                         |                                |                    |  |  |  |  |  |  |

| bit 7      | TMR0ON            | : Timer0 On/Off Control bit             |                                |                    |  |  |  |  |  |  |

|            | 1 = Enabl         | es Timer0                               |                                |                    |  |  |  |  |  |  |

|            | 0 = Stops         | Timer0                                  |                                |                    |  |  |  |  |  |  |

| bit 6      | <b>T08BIT</b> : T | ïmer0 8-Bit/16-Bit Control b            | it                             |                    |  |  |  |  |  |  |

|            | 1 = Timer         | 0 is configured as an 8-bit ti          | mer/counter                    |                    |  |  |  |  |  |  |

|            | 0 = Timer         | 0 is configured as a 16-bit ti          | mer/counter                    |                    |  |  |  |  |  |  |

| bit 5      | TOCS: Tir         | ner0 Clock Source Select bi             | t                              |                    |  |  |  |  |  |  |

|            | 1 = Trans         | ition on TOCKI pin input edg            | le                             |                    |  |  |  |  |  |  |

|            | 0 = Intern        | al clock (Fosc/4)                       |                                |                    |  |  |  |  |  |  |

| bit 4      | T0SE: Tin         | ner0 Source Edge Select bit             | t                              |                    |  |  |  |  |  |  |

|            | 1 = Increr        | nent on high-to-low transitio           | n on T0CKI pin                 |                    |  |  |  |  |  |  |

|            | 0 = Increr        | ment on low-to-high transitio           | n on T0CKI pin                 |                    |  |  |  |  |  |  |

| bit 3      | PSA: Tim          | er0 Prescaler Assignment b              | it                             |                    |  |  |  |  |  |  |

|            | 1 = Timer         | 0 prescaler is not assigned;            | Timer0 clock input bypasses    | prescaler          |  |  |  |  |  |  |

|            | 0 = Timer         | 0 prescaler is assigned; Tim            | ner0 clock input comes from pr | escaler output     |  |  |  |  |  |  |

| bit 2-0    | T0PS<2:0          | T0PS<2:0>: Timer0 Prescaler Select bits |                                |                    |  |  |  |  |  |  |

|            | 111 <b>= 1</b> :2 | 56 Prescale value                       |                                |                    |  |  |  |  |  |  |

|            | 110 <b>= 1</b> :1 | 28 Prescale value                       |                                |                    |  |  |  |  |  |  |

|            | 101 <b>= 1</b> :6 | 4 Prescale value                        |                                |                    |  |  |  |  |  |  |

|            |                   | 2 Prescale value                        |                                |                    |  |  |  |  |  |  |

|            |                   | 6 Prescale value                        |                                |                    |  |  |  |  |  |  |

|            |                   | Prescale value                          |                                |                    |  |  |  |  |  |  |

|            | 001 = 1:4         | <ul> <li>Prescale value</li> </ul>      |                                |                    |  |  |  |  |  |  |

### 14.1 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), displayed in Register 14-2, is used to control the Timer1 gate.

## REGISTER 14-2: T1GCON: TIMER1 GATE CONTROL REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0             | R/W-0                               | R/W-0         | R/W-0                                | R-x            | R/W-0                     | R/W-0         |

|--------------|-------------------|-------------------------------------|---------------|--------------------------------------|----------------|---------------------------|---------------|

| TMR1GE       | T1GPOL            | T1GTM                               | T1GSPM        | T1GGO/T1DONE                         | T1GVAL         | T1GSS1                    | T1GSS0        |

| bit 7        |                   |                                     |               |                                      |                |                           | bit 0         |

|              |                   |                                     |               |                                      |                |                           |               |

| Legend:      |                   |                                     |               |                                      |                |                           |               |

| R = Readab   |                   | W = Writable                        |               | U = Unimplemented                    | d bit, read as |                           |               |

| -n = Value a | t POR             | '1' = Bit is set                    |               | '0' = Bit is cleared                 |                | x = Bit is unkr           | iown          |

| bit 7        | TMR1GE: Ti        | mer1 Gate Ena                       | able bit      |                                      |                |                           |               |

|              | If TMR1ON =       | <u>    0</u> :                      |               |                                      |                |                           |               |

|              | This bit is igr   | ored.                               |               |                                      |                |                           |               |

|              | If TMR10N =       |                                     |               |                                      |                |                           |               |

|              |                   | ounting is cont<br>ounts regardle   |               | Timer1 gate function gate function   |                |                           |               |

| bit 6        | T1GPOL: Tir       | ner1 Gate Pola                      | arity bit     | -                                    |                |                           |               |

|              |                   |                                     |               | ounts when gate is high              |                |                           |               |

|              | 0 = Timer1 g      | ate is active-lo                    | w (Timer1 co  | unts when gate is low                | v)             |                           |               |

| bit 5        | T1GTM: Tim        | er1 Gate Togg                       | e Mode bit    |                                      |                |                           |               |

|              |                   | Gate Toggle m                       |               |                                      |                |                           |               |

|              |                   | Jate Toggle me<br>flip-flop toggles |               | d and toggle flip-flop<br>ing edge.  | is cleared     |                           |               |

| bit 4        | -                 | mer1 Gate Sin                       | -             |                                      |                |                           |               |

|              | 1 = Timer1 G      | ate Single Pul                      | se mode is ei | nabled and is controll               | ling Timer1 ga | ate                       |               |

|              | 0 = Timer1 G      | ate Single Pul                      | se mode is di | sabled                               |                |                           |               |

| bit 3        | T1GGO/T1D         | ONE: Timer1 (                       | Gate Single P | ulse Acquisition State               | us bit         |                           |               |

|              |                   |                                     |               | is ready, waiting for a              |                |                           |               |

|              |                   |                                     |               | has completed or ha GSPM is cleared. | is not been st | arted                     |               |

| bit 2        |                   | ner1 Gate Cur                       |               | Gor Wild Cleared.                    |                |                           |               |

|              |                   |                                     |               | gate that could be p                 | provided to TI |                           | unaffected by |

|              |                   | Enable (TMR1                        |               | gate that could be p                 |                | vii ( 11 1. 1 1vii ( 1 L, | unanceted by  |

| bit 1-0      | T1GSS<1:0>        | : Timer1 Gate                       | Source Sele   | ct bits                              |                |                           |               |

|              | 11 <b>= Compa</b> | rator 2 output                      |               |                                      |                |                           |               |

|              |                   | rator 1 output                      |               |                                      |                |                           |               |

|              |                   | o match PR2 c                       | output        |                                      |                |                           |               |

|              | 00 = Timer1       | yate pill                           |               |                                      |                |                           |               |

| Note 1: P    | rogramming th     | e T1GCON pri                        | or to T1CON   | is recommended                       |                |                           |               |

**Note 1:** Programming the T1GCON prior to T1CON is recommended.

## 15.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- Eight-bit Timer and Period registers (TMR2 and PR2, respectively)

- Both registers are readable and writable

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

This module is controlled through the T2CON register (Register 15-1) that enables or disables the timer, and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 15-1.

## 15.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A four-bit counter/prescaler on the clock input gives the prescale options of direct input, divide-by-4 or divide-by-16. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>).

The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler. (See **Section 15.2 "Timer2 Interrupt**".)

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR)

TMR2 is not cleared when T2CON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 20-2, Register 19-2 and Register 19-3.

### REGISTER 15-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| bit 7<br>bit 6-3 | Unimplemented: Read as '0'<br>T2OUTPS<3:0>: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>• |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                  | •<br>1111 = 1:16 Postscale                                                                                                           |

| bit 2            | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                       |

| bit 1-0          | <b>T2CKPS&lt;1:0&gt;:</b> Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16    |

| Name                  | Bit 7                                                                                              | Bit 6                   | Bit 5                  | Bit 4     | Bit 3                 | Bit 2   | Bit 1    | Bit 0                  |

|-----------------------|----------------------------------------------------------------------------------------------------|-------------------------|------------------------|-----------|-----------------------|---------|----------|------------------------|

| INTCON                | GIE/GIEH                                                                                           | PEIE/GIEL               | TMR0IE                 | INT0IE    | RBIE                  | TMR0IF  | INT0IF   | RBIF                   |

| IPR5                  | TMR7GIP <sup>(1)</sup>                                                                             | TMR12IP <sup>(1)</sup>  | TMR10IP <sup>(1)</sup> | TMR8IP    | TMR7IP <sup>(1)</sup> | TMR6IP  | TMR5IP   | TMR4IP                 |

| PIR5                  | TMR7GIF <sup>(1)</sup>                                                                             | TMR12IF <sup>(1)</sup>  | TMR10IF <sup>(1)</sup> | TMR8IF    | TMR7IF <sup>(1)</sup> | TMR6IF  | TMR5IF   | TMR4IF                 |

| PIE5                  | TMR7GIE <sup>(1)</sup>                                                                             | TMR12IE <sup>(1)</sup>  | TMR10IE <sup>(1)</sup> | TMR8IE    | TMR7IE <sup>(1)</sup> | TMR6IE  | TMR5IE   | TMR4IE                 |

| TMR4                  | Timer4 Regis                                                                                       | ter                     |                        |           |                       |         |          |                        |

| T4CON                 | _                                                                                                  | T4OUTPS3                | T4OUTPS2               | T4OUTPS1  | T4OUTPS0              | TMR4ON  | T4CKPS1  | T4CKPS0                |

| PR4                   | Timer4 Period                                                                                      | d Register              |                        |           |                       |         |          |                        |

| TMR6                  | Timer6 Regis                                                                                       | ter                     |                        |           |                       |         |          |                        |

| T6CON                 | —                                                                                                  | T6OUTPS3                | T6OUTPS2               | T6OUTPS1  | T6OUTPS0              | TMR6ON  | T6CKPS1  | T6CKPS0                |

| PR6                   | Timer6 Period                                                                                      | d Register              |                        |           |                       |         |          |                        |

| TMR8                  | Timer8 Regis                                                                                       | ter                     |                        |           |                       |         |          |                        |

| T8CON                 | —                                                                                                  | T8OUTPS3                | T8OUTPS2               | T8OUTPS1  | T8OUTPS0              | TMR8ON  | T8CKPS1  | T8CKPS0                |

| PR8                   | Timer8 Period                                                                                      | d Register              |                        |           |                       |         |          |                        |

| TMR10 <sup>(1)</sup>  | Timer10 Regi                                                                                       | ster                    |                        |           |                       |         |          |                        |

| T10CON <sup>(1)</sup> | —                                                                                                  | T10OUTPS3               | T100UTPS2              | T10OUTPS1 | T10OUTPS0             | TMR10ON | T10CKPS1 | T10CKPS0               |

| PR10 <sup>(1)</sup>   | Timer10 Peric                                                                                      | od Register             |                        |           |                       |         |          |                        |

| TMR12 <sup>(1)</sup>  | Timer12 Regi                                                                                       | ster                    |                        |           |                       |         |          |                        |

| T12CON <sup>(1)</sup> | —                                                                                                  | T12OUTPS3               | T12OUTPS2              | T12OUTPS1 | T12OUTPS0             | TMR12ON | T12CKPS1 | T12CKPS0               |

| PR12 <sup>(1)</sup>   | Timer12 Perio                                                                                      | Timer12 Period Register |                        |           |                       |         |          |                        |

| PMD1                  | PSPMD                                                                                              | CTMUMD                  | RTCCMD                 | TMR4MD    | TMR3MD                | TMR2MD  | TMR1MD   | EMBMD                  |

| PMD2                  | TMR10MD <sup>(1)</sup>                                                                             |                         | TMR7MD <sup>(1)</sup>  | TMR6MD    | TMR5MD                | CMP3MD  | CMP2MD   | CMP2MD                 |

| PMD3                  | CCP10MD <sup>(1)</sup>                                                                             | CCP9MD <sup>(1)</sup>   | CCP8MD                 | CCP7MD    | CCP6MD                | CCP5MD  | CCP4MD   | TMR12MD <sup>(1)</sup> |

|                       | we we have a stand and any (o). Obside discussion and we add her the Times of (0)(40)(40) we added |                         |                        |           |                       |         |          |                        |

| TABLE 17-3: | REGISTERS ASSOCIATED WITH TIMER4/6/8/10/12 AS A TIMER/COUNTER |

|-------------|---------------------------------------------------------------|

|-------------|---------------------------------------------------------------|

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer4/6/8/10/12 module.

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

## 21.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

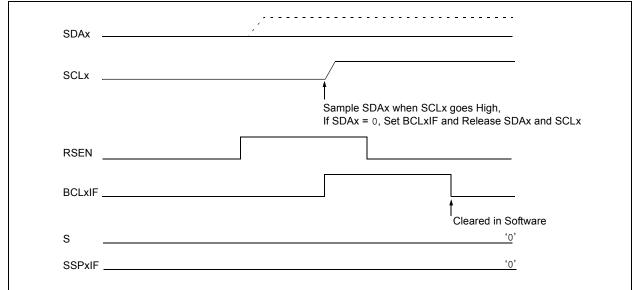

- a) A low level is sampled on SDAx when SCLx goes from a low level to a high level.

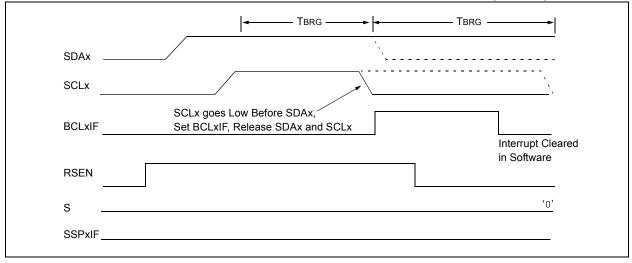

- SCLx goes low before SDAx is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDAx and the pin is allowed to float high, the BRG is loaded with SSPxADD<6:0> and counts down to 0. The SCLx pin is then deasserted and when sampled high, the SDAx pin is sampled.

If SDAx is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 21-31). If SDAx is sampled high, the BRG is reloaded and begins counting. If SDAx goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDAx at exactly the same time.

If SCLx goes from high-to-low before the BRG times out and SDAx has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 21-32).

If, at the end of the BRG time-out, both SCLx and SDAx are still high, the SDAx pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCLx pin, the SCLx pin is driven low and the Repeated Start condition is complete.

#### FIGURE 21-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 21-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

## 22.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 22-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN/J2602 bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRGx begins counting up, using the preselected clock source on the first rising edge of RXx. After eight bits on the RXx pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGHx:SPBRGx register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCONx<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 22-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. The BRG clock will be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG1 and SPBRGH1 as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGHx register. Refer to Table 22-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCxIF interrupt is set once the fifth rising edge on RXx is detected. The value in the RCREGx needs to be read to clear the RCxIF interrupt. The contents of RCREGx should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

- To maximize baud rate range, if that feature is used, it is recommended that the BRG16 bit (BAUDCONx<3>) be set.

## TABLE 22-4:BRG COUNTER<br/>CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |  |  |  |  |

|-------|------|-------------------|--|--|--|--|

| 0     | 0    | Fosc/512          |  |  |  |  |

| 0     | 1    | Fosc/128          |  |  |  |  |

| 1     | 0    | Fosc/128          |  |  |  |  |

| 1     | 1    | Fosc/32           |  |  |  |  |

### 22.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREGx cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

## REGISTER 23-6: ADRESH: A/D RESULT HIGH BYTE REGISTER, RIGHT JUSTIFIED (ADFM = 1)

| R/W-x | R/W-x | R/W-x | R/W-x | R/W-x   | R/W-x   | R/W-x  | R/W-x  |

|-------|-------|-------|-------|---------|---------|--------|--------|

| ADSGN | ADSGN | ADSGN | ADSGN | ADRES11 | ADRES10 | ADRES9 | ADRES8 |

| bit 7 |       |       |       |         |         |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | ADSGN: A/D Result Sign bit              |

|---------|-----------------------------------------|

|         | 1 = A/D result is negative              |

|         | 0 = A/D result is positive              |

| bit 3-0 | ADRESH<11:8>: A/D Result High Byte bits |

## REGISTER 23-7: ADRESL: A/D RESULT LOW BYTE REGISTER, RIGHT JUSTIFIED (ADFM = 1)

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 ADRES<7:0>: A/D Result Low Byte bits

### 28.2.1 CONTROL REGISTER

Register 28-16 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT Enable Configuration bit, but only if the Configuration bit has disabled the WDT.

#### REGISTER 28-16: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| R/W-0        | U-0              | R-x                                   | R/W-0                 | U-0              | R/W-0                | R/W-0            | R/W-0                 |

|--------------|------------------|---------------------------------------|-----------------------|------------------|----------------------|------------------|-----------------------|

| REGSLP       |                  | ULPLVL                                | SRETEN <sup>(2)</sup> | _                | ULPEN                | ULPSINK          | SWDTEN <sup>(1)</sup> |

| bit 7        |                  |                                       |                       |                  |                      |                  | bit (                 |

| Legend:      |                  |                                       |                       |                  |                      |                  |                       |

| R = Readab   | le bit           | W = Writable                          | bit                   | U = Unimple      | mented bit, rea      | d as '0'         |                       |

| -n = Value a | t POR            | '1' = Bit is se                       | t                     | ʻ0' = Bit is cl  | eared                | x = Bit is unk   | nown                  |

| bit 7        |                  | Regulator Voltag<br>tor goes into Lov | -                     |                  | s Sloop modo i       | anablad          |                       |

|              |                  | tor stays in norm                     |                       |                  |                      |                  |                       |

| bit 6        | Unimpleme        | ented: Read as                        | '0'                   |                  | -                    |                  |                       |

| bit 5        | ULPLVL: U        | Itra Low-Power                        | Wake-up Outp          | ut bit           |                      |                  |                       |

|              | Not valid ur     | less ULPEN = 1                        | L.                    |                  |                      |                  |                       |

|              |                  | e on RA0 pin > ~                      |                       |                  |                      |                  |                       |

|              | •                | e on RA0 pin < ~                      |                       | (2)              |                      |                  |                       |

| bit 4        |                  | Regulator Voltag                      | •                     |                  |                      |                  |                       |

|              |                  | EN (CONFIG1L<<br>n Sleep              | (0>) = 0 and the      | e regulator is e | enabled, the dev     | rice goes into U | ltra Low-Powe         |

|              |                  | gulator is on w                       | hen the device        | e's Sleep mo     | de is enabled        | and the Low-F    | ower mode is          |

|              |                  | led by REGSLP                         |                       |                  |                      |                  |                       |

| bit 3        | Unimpleme        | ented: Read as                        | ʻ0'                   |                  |                      |                  |                       |

| bit 2        | ULPEN: UI        | tra Low-Power V                       | Vake-up Modul         | e Enable bit     |                      |                  |                       |

|              |                  | ow-Power Wake<br>ow-Power Wake        |                       |                  | LVL bit indicate     | s the comparat   | or output             |

| bit 1        | ULPSINK:         | Ultra Low-Powe                        | r Wake-up Cur         | rent Sink Ena    | ble bit              |                  |                       |

|              | Not valid ur     | less ULPEN = 1                        | L.                    |                  |                      |                  |                       |

|              |                  | ow-Power Wake<br>ow-Power Wake        |                       |                  |                      |                  |                       |

| bit 0        | SWDTEN: S        | Software Contro                       | lled Watchdog         | Timer Enable     | e bit <sup>(1)</sup> |                  |                       |

|              |                  | og Timer is on                        |                       |                  |                      |                  |                       |

|              | 0 = Watchd       | og Timer is off                       |                       |                  |                      |                  |                       |

| Note 1. T    | his hit has no o | ffect if the Confi                    | guration bits. M      |                  | are enabled          |                  |                       |

**Note 1:** This bit has no effect if the Configuration bits, WDTEN<1:0>, are enabled.

**2:** This bit is available only when ENVREG = 1 and  $\overline{\text{RETEN}}$  = 0.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1   | Bit 0  |

|--------|--------|--------|--------|--------|-------|-------|---------|--------|

| RCON   | IPEN   | SBOREN | CM     | RI     | TO    | PD    | POR     | BOR    |

| WDTCON | REGSLP |        | ULPLVL | SRETEN |       | ULPEN | ULPSINK | SWDTEN |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

| RCA                                                                                                                                                                                                                                                                                                                                                              | LL             | Relative C                     | all           |      |                                                                      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------|---------------|------|----------------------------------------------------------------------|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                            | ax:            | RCALL n                        | RCALL n       |      |                                                                      |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                             | ands:          | -1024 ≤ n ≤                    | ≤ 1023        |      |                                                                      |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                             | ation:         | (PC) + 2 →<br>(PC) + 2 +       | ,             | ;    |                                                                      |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                            | s Affected:    | None                           |               |      |                                                                      |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                             | ding:          | 1101                           | 1nnn          | nnnn | nnnn                                                                 |  |  |  |

| Description: Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complemen<br>number '2n' to the PC. Since the PC'<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |                |                                |               |      | t, return<br>into the<br>plement<br>the PC will<br>e next<br>will be |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                             | ls:            | 1                              | 1             |      |                                                                      |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                            | es:            | 2                              |               |      |                                                                      |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                               | ycle Activity: |                                |               |      |                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                  | Q1             | Q2                             | Q3            | 5    | Q4                                                                   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                  | Decode         | Read literal<br>'n'<br>PUSH PC | Proce<br>Data |      | rite to PC                                                           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                  |                | to stack                       |               |      |                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                  | No             | No                             | No            |      | No                                                                   |  |  |  |

| RES   | ET             | Reset |                                                                      |      |    |         |  |

|-------|----------------|-------|----------------------------------------------------------------------|------|----|---------|--|

| Synta | ax:            | RESET |                                                                      |      |    |         |  |

| Oper  | ands:          | None  |                                                                      |      |    |         |  |

| Oper  | ation:         |       | Reset all registers and flags that are affected by a MCLR Reset.     |      |    |         |  |

| Statu | s Affected:    | All   | All                                                                  |      |    |         |  |

| Enco  | ding:          | 0000  | 0000                                                                 | 1111 |    | 1111    |  |

| Desc  | ription:       | -     | This instruction provides a way to execute a MCLR Reset in software. |      |    |         |  |

| Word  | ls:            | 1     |                                                                      |      |    |         |  |

| Cycle | es:            | 1     |                                                                      |      |    |         |  |

| QC    | ycle Activity: |       |                                                                      |      |    |         |  |

|       | Q1             | Q2    | Q3                                                                   | 8    |    | Q4      |  |

|       | Decode         | Start | No                                                                   |      |    | No      |  |

|       |                | reset | operat                                                               | ion  | ор | eration |  |

Example:

| • | Instri | iction |  |

|---|--------|--------|--|

| After Instruction |             |

|-------------------|-------------|

| Registers =       | Reset Value |

| Flags* =          | Reset Value |

RESET

Example: HERE RCALL Jump

operation

operation

operation

Before Instruction

operation

PC = Address (HERE) After Instruction PC = TOS = Address (Jump) Address (HERE + 2)

| SUBWFB                        | Subtrac                                                  | t W from f                                                                                                                                                                                                                                                                               | with Borr          | ow                    |  |  |  |

|-------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--|--|--|

| Syntax:                       | SUBWF                                                    | 3 f {,d {,a]                                                                                                                                                                                                                                                                             | -}                 |                       |  |  |  |

| Operands:                     | $0 \le f \le 25$                                         | 55                                                                                                                                                                                                                                                                                       |                    |                       |  |  |  |

|                               | d ∈ [0,1]<br>a ∈ [0,1]                                   |                                                                                                                                                                                                                                                                                          |                    |                       |  |  |  |

| Operation:                    |                                                          | $-(\overline{C}) \rightarrow de$                                                                                                                                                                                                                                                         | et                 |                       |  |  |  |

| Operation:                    |                                                          | . ,                                                                                                                                                                                                                                                                                      | รเ                 |                       |  |  |  |

| Status Affected:              | N, OV, C                                                 | 1                                                                                                                                                                                                                                                                                        |                    | 6666                  |  |  |  |

| Encoding:                     | 0101                                                     | Subtract W and the Carry flag (borrow)                                                                                                                                                                                                                                                   |                    |                       |  |  |  |

| Description:                  | from regi<br>method).<br>in W. If 'c                     | from register 'f' (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f'.                                                                                                                                  |                    |                       |  |  |  |

|                               | <b>lf 'a' is</b> '1                                      | If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.                                                                                                                                                                                       |                    |                       |  |  |  |