Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-VQFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k22-i-mr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode provides controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. To maintain software compatibility with future devices, it is recommended that SCS0 also be cleared, though its value is ignored. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC/MFIOSEL bit is set, the INTOSC output is enabled. The HFIOFS/MFIOFS bits become set, after the INTOSC output becomes stable, after an interval of TIOBST (Parameter 38, Table 31-13). (For information on the HFIOFS/MFIOFS bits, see Table 4-3.)

Clocks to the peripherals continue while the INTOSC source stabilizes. The HFIOFS/MFIOFS bits will remain set if the IRCF bits were previously at a non-zero value or if INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled, the HFIOFS/MFIOFS bits will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD (Parameter 38, Table 31-13) following the wake event, the CPU begins executing code clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what this mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals.

PIC18F87K22 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- Peripheral Enable bit, generically named XXXEN Located in the respective module's main control register

- Peripheral Module Disable (PMD) bit, generically named, XXXMD – Located in one of the PMDx Control registers (PMD0, PMD1, PMD2 or PMD3)

Disabling a module by clearing its XXXEN bit disables the module's functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as the second approach.

Most peripheral modules have an enable bit.

In contrast, setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral are also disabled, so writes to those registers have no effect and read values are invalid. Many peripheral modules have a corresponding PMD bit.

There are four PMD registers in the PIC18F87K22 family devices: PMD0, PMD1, PMD2 and PMD3. These registers have bits associated with each module for disabling or enabling a particular peripheral.

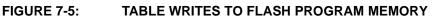

# 7.5 Writing to Flash Program Memory

The programming blocks are:

- PIC18FX5K22 and PIC18FX6K22 32 words or 64 bytes

- PIC18FX7K22 64 words or 128 bytes

Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. The number of holding registers used for programming by the table writes are:

- PIC18FX5K22 and PIC18FX6K22 64

- PIC18FX7K22 128

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 or 128 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write is terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets, and after write operations, is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 or 128 holding registers before executing a write operation.

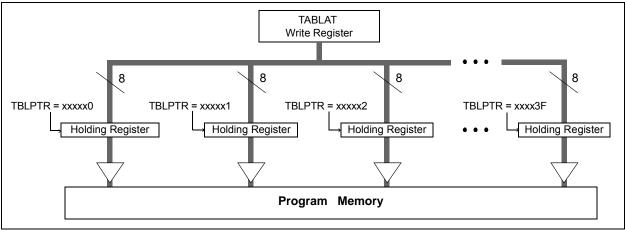

### 8.6.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F87K22 family devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

#### REGISTER 11-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1      | R/W-1                                                            | R/W-0                                                 | R/W-0                          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|------------|------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|--------|

| INT2IP     | INT1IP                                                           | INT3IE                                                | INT2IE                         | INT1IE           | INT3IF          | INT2IF          | INT1IF |

| bit 7      |                                                                  |                                                       |                                |                  |                 |                 | bit (  |

| Legend:    |                                                                  |                                                       |                                |                  |                 |                 |        |

| R = Reada  | able bit                                                         | W = Writable                                          | bit                            | U = Unimpler     | nented bit, rea | d as '0'        |        |

| -n = Value | at POR                                                           | '1' = Bit is set                                      |                                | '0' = Bit is cle |                 | x = Bit is unkr | nown   |

| bit 7      | 1 = High prio                                                    | ,                                                     | upt Priority bit               |                  |                 |                 |        |

| bit 6      | 0 = Low prior<br>INT1IP: INT1<br>1 = High prio<br>0 = Low prior  | External Interr                                       | upt Priority bit               |                  |                 |                 |        |

| bit 5      | INT3IE: INT3<br>1 = Enables 1                                    | External Interr<br>the INT3 exterr<br>the INT3 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 4      | 1 = Enables                                                      | External Interr<br>the INT2 exterr<br>the INT2 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 3      | 1 = Enables                                                      | External Interr<br>the INT1 exterr<br>the INT1 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 2      | 1 = The INT3                                                     | External Interr<br>external interr<br>external interr | upt occurred (                 | must be cleared  | d in software)  |                 |        |

| bit 1      | INT2IF: INT2<br>1 = The INT2                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

| bit 0      | INT1IF: INT1<br>1 = The INT1                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

|            | Interrupt flag bits<br>enable bit or the 0<br>are clear prior to | Global Interrupt                                      | Enable bit. Us                 | ser software sho | ould ensure the | appropriate int |        |

# REGISTER 11-11: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0         | U-0                                               | R/W-0                                                      | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|---------------|---------------------------------------------------|------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|---------|

| OSCFIE        | —                                                 | SSP2IE                                                     | BCL2IE          | BCL1IE            | HLVDIE           | TMR3IE          | TMR3GIE |

| bit 7         |                                                   |                                                            |                 |                   |                  |                 | bit 0   |

|               |                                                   |                                                            |                 |                   |                  |                 |         |

| Legend:       |                                                   |                                                            |                 |                   |                  |                 |         |

| R = Readable  | e bit                                             | W = Writable b                                             | bit             | U = Unimplem      | nented bit, read | d as '0'        |         |

| -n = Value at | POR                                               | '1' = Bit is set                                           |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 7         | <b>OSCFIE:</b> Osc<br>1 = Enabled<br>0 = Disabled | sillator Fail Inter                                        | rupt Enable bi  | t                 |                  |                 |         |

| bit 6         | Unimplemen                                        | ted: Read as 'o                                            | ,               |                   |                  |                 |         |

| bit 5         | SSP2IE: Mas                                       | ter Synchronou                                             | s Serial Port 2 | Interrupt Enab    | le bit           |                 |         |

|               |                                                   | the MSSP inter<br>the MSSP inter                           |                 |                   |                  |                 |         |

| bit 4         | 1 = Enables                                       | Collision Interru<br>the bus collision<br>the bus collisio | interrupt       |                   |                  |                 |         |

| bit 3         | BCL1IE: Bus<br>1 = Enabled<br>0 = Disabled        | Collision Interro                                          | upt Enable bit  |                   |                  |                 |         |

| bit 2         | HLVDIE: High<br>1 = Enabled<br>0 = Disabled       | n/Low-Voltage [                                            | etect Interrup  | t Enable bit      |                  |                 |         |

| bit 1         | TMR3IE: TM                                        | R3 Overflow Inte                                           | errupt Enable   | bit               |                  |                 |         |

|               | 1 = Enabled<br>0 = Disabled                       |                                                            |                 |                   |                  |                 |         |

| bit 0         | TMR3GIE: Tin<br>1 = Enabled<br>0 = Disabled       | mer3 Gate Inter                                            | rupt Enable b   | it                |                  |                 |         |

#### 20.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2/4/6/8 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HF-INTOSC and the postscaler may not be immediately stable.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCPx module without change.

### 20.4.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

### 20.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states. This forces the ECCP module to reset to a state compatible with previous, non-Enhanced CCP modules used on other PIC18 and PIC16 devices.

|                      |                        | 2314/0/0/10/1         | -      |        |        |        |        |        |

|----------------------|------------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| File Name            | Bit 7                  | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| INTCON               | GIE/GIEH               | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   |

| RCON                 | IPEN                   | SBOREN                | CM     | RI     | TO     | PD     | POR    | BOR    |

| PIR3                 | TMR5GIF                | —                     | RC2IF  | TX2IF  | CTMUIF | CCP2IF | CCP1IF | RTCCIF |

| PIR4                 | CCP10IF <sup>(1)</sup> | CCP9IF <sup>(1)</sup> | CCP8IF | CCP7IF | CCP6IF | CCP5IF | CCP4IF | CCP3IF |

| PIE3                 | TMR5GIE                | —                     | RC2IE  | TX2IE  | CTMUIE | CCP2IE | CCP1IE | RTCCIE |

| PIE4                 | CCP10IE <sup>(1)</sup> | CCP9IE <sup>(1)</sup> | CCP8IE | CCP7IE | CCP6IE | CCP5IE | CCP4IE | CCP3IE |

| IPR3                 | TMR5GIP                | —                     | RC2IP  | TX2IP  | CTMUIP | CCP2IP | CCP1IP | RTCCIP |

| IPR4                 | CCP10IP <sup>(1)</sup> | CCP9IP <sup>(1)</sup> | CCP8IP | CCP7IP | CCP6IP | CCP5IP | CCP4IP | CCP3IP |

| TRISB                | TRISB7                 | TRISB6                | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| TRISC                | TRISC7                 | TRISC6                | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| TRISE                | TRISE7                 | TRISE6                | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 |

| TRISH <sup>(2)</sup> | TRISH7                 | TRISH6                | TRISH5 | TRISH4 | TRISH3 | TRISH2 | TRISH1 | TRISH0 |

| TMR1H                | Timer1 Register        | High Byte             |        |        |        |        |        |        |

| TMR1L                | Timer1 Register        | Low Byte              |        |        |        |        |        |        |

| TMR2                 | Timer2 Register        |                       |        |        |        |        |        |        |

| TMR3H                | Timer3 Register        | High Byte             |        |        |        |        |        |        |

| TMR3L                | Timer3 Register        | Low Byte              |        |        |        |        |        |        |

| TMR4                 | Timer4 Register        |                       |        |        |        |        |        |        |

| TMR6                 | Timer6 Register        |                       |        |        |        |        |        |        |

| TMR8                 | Timer8 Register        |                       |        |        |        |        |        |        |

| TMR10 <sup>(1)</sup> | TMR10 Register         | r                     |        |        |        |        |        |        |

| TMR12 <sup>(1)</sup> | TMR10 Register         | r                     |        |        |        |        |        |        |

| PR2                  | Timer2 Period R        | Register              |        |        |        |        |        |        |

| PR4                  | Timer4 Period R        | Register              |        |        |        |        |        |        |

| PR6                  | Timer6 Period R        | Register              |        |        |        |        |        |        |

| PR8                  | Timer8 Period R        | Register              |        |        |        |        |        |        |

| PR10 <sup>(1)</sup>  | Timer10 Period         | Register              |        |        |        |        |        |        |

| PR12 <sup>(1)</sup>  | Timer12 Period         | Register              |        |        |        |        |        |        |

#### TABLE 20-4: REGISTERS ASSOCIATED WITH ECCP1/2/3 MODULE AND TIMER1/2/3/4/6/8/10/12

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18F65K22 and PIC18F85K22).

**2:** Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

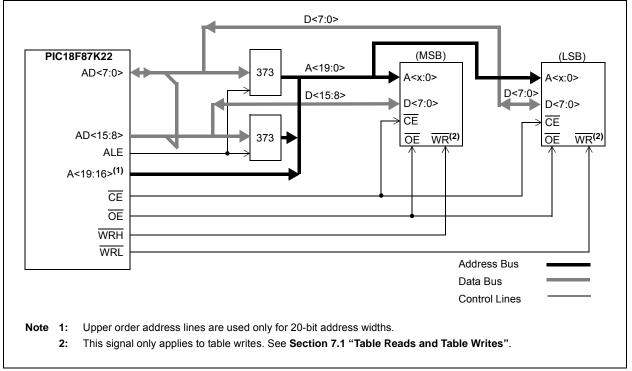

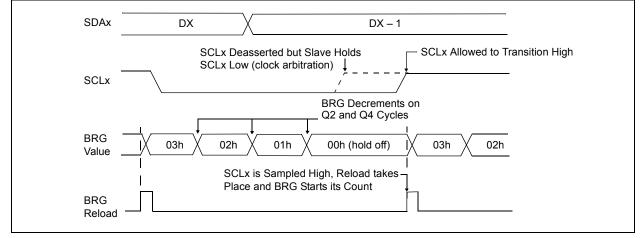

### 21.4.7.2 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the

SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 21-20).

### EXAMPLE 22-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC of 10 | 6 MH | z, desired baud rate of 9600, Asynchronous mode, and 8-bit BRG: |

|------------------------------|------|-----------------------------------------------------------------|

| Desired Baud Rate            | =    | Fosc/(64 ([SPBRGHx:SPBRGx] + 1))                                |

| Solving for SPBRGHx:         | SPB1 | RGx:                                                            |

| Х                            | =    | ((FOSC/Desired Baud Rate)/64) – 1                               |

|                              | =    | ((16000000/9600)/64) - 1                                        |

|                              | =    | [25.042] = 25                                                   |

| Calculated Baud Rate         | =    | 1600000/(64 (25 + 1))                                           |

|                              | =    | 9615                                                            |

| Error                        | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate    |

|                              | =    | (9615 - 9600)/9600 = 0.16%                                      |

|                              |      |                                                                 |

## TABLE 22-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name      | Bit 7       | Bit 6       | Bit 5         | Bit 4          | Bit 3   | Bit 2  | Bit 1  | Bit 0 |

|-----------|-------------|-------------|---------------|----------------|---------|--------|--------|-------|

| TXSTA1    | CSRC        | TX9         | TXEN          | SYNC           | SENDB   | BRGH   | TRMT   | TX9D  |

| RCSTA1    | SPEN        | RX9         | SREN          | CREN           | ADDEN   | FERR   | OERR   | RX9D  |

| BAUDCON1  | ABDOVF      | RCIDL       | RXDTP         | TXCKP          | BRG16   | _      | WUE    | ABDEN |

| SPBRGH1   | EUSART1 B   | aud Rate Ge | nerator Regis | ster High Byte | ;       |        |        |       |

| SPBRG1    | EUSART1 B   | aud Rate Ge | nerator Regis | ster           |         |        |        |       |

| TXSTA2    | CSRC        | TX9         | TXEN          | SYNC           | SENDB   | BRGH   | TRMT   | TX9D  |

| RCSTA2    | SPEN        | RX9         | SREN          | CREN           | ADDEN   | FERR   | OERR   | RX9D  |

| BAUDCON2  | ABDOVF      | RCIDL       | RXDTP         | TXCKP          | BRG16   |        | WUE    | ABDEN |

| SPBRGH2   | EUSART2 B   | aud Rate Ge | nerator Regis | ster High Byte | ;       |        |        |       |

| SPBRG2    | EUSART2 B   | aud Rate Ge | nerator Regis | ster           |         |        |        |       |

| PMD0      | CCP3MD      | CCP2MD      | CCP1MD        | UART2MD        | UART1MD | SSP2MD | SSP1MD | ADCMD |

| Lonondi – | unimplement |             |               |                |         | 2      |        |       |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 0, BRG            | <b>616 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | 0 MHz                       | Fosc                  | : = 10.000     | ) MHz                       | Fos                   | c = 8.000  | MHz                         |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     | _          |                             |                       | _          |                             |                       |                | _                           |                       | _          |                             |

| 1.2         | —                     | _          | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | —                     | _          | _                           |

| 115.2       | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | —                     | _          | _                           |

| TABI E 22-3 | BAUD RATES FOR ASYNCHRONOUS MODES |

|-------------|-----------------------------------|

| IADLL 22-J. |                                   |

|             |                       |            | S                           | YNC = 0, E            | BRGH = (   | , BRG16 =                   | 0                     |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                 | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2         | 1.202                 | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4         | 2.404                 | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | —                           |

| 9.6         | 8.929                 | -6.99      | 6                           | —                     | _          | _                           | _                     | _          | _                           |

| 19.2        | 20.833                | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6        | 62.500                | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2       | 62.500                | -45.75     | 0                           | _                     |            | _                           | _                     |            | —                           |

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | <b>i</b> = 1, BRG     | i <b>16 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | 0 MHz                       | Fosc                  | = 10.000        | ) MHz                       | Fos                   | c = 8.000  | MHz                         |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | —                     | _          | _                           | _                     | _          | _                           | _                     | _               | _                           | _                     | _          | _                           |

| 1.2          | —                     | —          | —                           | —                     | —          | —                           | —                     |                 | —                           | —                     | —          | —                           |

| 2.4          | —                     | _          | _                           | —                     | _          | _                           | 2.441                 | 1.73            | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16            | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73            | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36           | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51            | 4                           | —                     | _          | _                           |

|              |                       |            | S                           | YNC = 0, E            | BRGH = 1   | L, BRG16 =                  | 0                     |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Foso                  | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     |            | _                           |                       | _          | _                           | 0.300                 | -0.16      | 207                         |

| 1.2          | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4          | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6          | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |

| 19.2         | 19.231                | 0.16       | 12                          | _                     | _          | _                           | _                     | _          | _                           |

| 57.6         | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 125.000               | 8.51       | 1                           |                       | _          | —                           | _                     | _          | —                           |

$\ensuremath{\textcircled{}^{\circ}}$  2009-2011 Microchip Technology Inc.

#### 22.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# FIGURE 22-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

|    | bit 7            | ×:          | bit 6 | bit 5       | bit 4       | bit 3 | bit 2 | bit 1       | bit 0              |     | RC7/RX1/DT1 —<br>Pin         |

|----|------------------|-------------|-------|-------------|-------------|-------|-------|-------------|--------------------|-----|------------------------------|

|    | 1<br>1<br>1      | :           | Ŀ÷Ĺ   |             | ÷∟          |       |       |             |                    |     | RC6/TX1/CK1<br>1 (TXCKP = 0) |

|    |                  |             |       |             |             |       |       |             |                    |     | RC6/TX1/CK1<br>n (TXCKP = 1) |

|    | 1<br>1<br>1<br>1 | 1<br>1<br>1 |       |             | •<br>•<br>• |       |       |             | 1<br>1<br>1        |     | Write to<br>bit, SREN        |

|    | <u> </u>         |             |       |             |             |       |       | :           | i                  |     | SREN bit                     |

| '0 | i                |             |       |             |             |       |       |             |                    | · · | CREN bit                     |

|    | ÷                |             |       | 1<br>1<br>1 | 1<br>1<br>1 |       |       | 1<br>1<br>1 | י<br>י<br><u>י</u> |     | RC1IF bit<br>(Interrupt)——   |

| ╧  | i                | •           | 1     |             | <u> </u>    |       |       |             |                    | · · | Read<br>RCREG1 —             |

Note: Timing diagram demonstrates Sync Master mode with bit, SREN = 1, and bit, BRGH = 0. This example is equally applicable to EUSART2 (RG1/TX2/CK2/AN19/C3OUT and RG2/RX2/DT2/AN18/C3INA).

#### REGISTER 23-10: ANCON2: A/D PORT CONFIGURATION REGISTER 2

| R/W-1                  | R/W-1                  | R/W-1                  | R/W-1                  | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|------------------------|------------------------|------------------------|------------------------|---------|---------|---------|---------|

| ANSEL23 <sup>(1)</sup> | ANSEL22 <sup>(1)</sup> | ANSEL21 <sup>(1)</sup> | ANSEL20 <sup>(1)</sup> | ANSEL19 | ANSEL18 | ANSEL17 | ANSEL16 |

| bit 7                  |                        |                        |                        |         |         |         | bit 0   |

|                        |                        |                        |                        |         |         |         |         |

| Leaend:                |                        |                        |                        |         |         |         |         |

| Legenu.           |                  |                       |                                    |  |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |  |

#### bit 7-0 ANSEL<23:16>: Analog Port Configuration bits (AN23 through AN16)<sup>(1)</sup>

- 1 = Pin is configured as an analog channel; digital input is disabled and any inputs read as '0'

0 = Pin is configured as a digital port

- **Note 1:** AN15 through AN12 and AN23 through AN20 are implemented only on 80-pin devices. For 64-pin devices, the corresponding ANSELx bits are still implemented for these channels, but have no effect.

The analog reference voltage is software-selectable to either the device's positive and negative supply voltage (AVDD and AVSS) or the voltage level on the RA3/AN3/VREF+ and RA2/AN2/VREF- pins. VREF+ has two additional Internal Reference Voltage selections: 2.048V and 4.096V.

The A/D Converter can uniquely operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D Converter's internal RC oscillator.

The output of the Sample-and-Hold (S/H) is the input into the converter, which generates the result via successive approximation.

Each port pin associated with the A/D Converter can be configured as an analog input or a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0<1>) is cleared and the A/D Interrupt Flag bit, ADIF (PIR1<6>), is set.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted. The value in the ADRESH:ADRESL register pair is not modified for a Power-on Reset. These registers will contain unknown data after a Power-on Reset.

The block diagram of the A/D module is shown in Figure 23-4.

## 26.2 HLVD Setup

To set up the HLVD module:

- 1. Select the desired HLVD trip point by writing the value to the HLVDL<3:0> bits.

- 2. Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 3. Enable the HLVD module by setting the HLVDEN bit.

- 4. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- If interrupts are desired, enable the HLVD interrupt by setting the HLVDIE and GIE bits (PIE2<2> and INTCON<7>, respectively).

An interrupt will not be generated until the IRVST bit is set.

**Note:** Before changing any module settings (VDIRMAG, LVDL<3:0>), first disable the module (LVDEN = 0), make the changes and re-enable the module. This prevents the generation of false HLVD events.

# 26.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and consume static current. The total current consumption, when enabled, is specified in electrical specification Parameter D022B (Table 31-13).

Depending on the application, the HLVD module does not need to operate constantly. To reduce current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After such a check, the module could be disabled.

# 26.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification Parameter 37 (Section 31.0 "Electrical Characteristics"), may be used by other internal circuitry, such as the programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification Parameter 37 (Table 31-13).

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (see Figure 26-2 or Figure 26-3).

| R/W-0        | R/W-0                                                  | R/W-0                                                 | R/W-0       | R/W-0             | R/W-0           | DAM 0           | R/W-0 |  |  |  |  |  |

|--------------|--------------------------------------------------------|-------------------------------------------------------|-------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

|              |                                                        | _                                                     | 1           |                   | -               | R/W-0           | -     |  |  |  |  |  |

| ITRIM5       | ITRIM4                                                 | ITRIM3                                                | ITRIM2      | ITRIM1            | ITRIM0          | IRNG1           | IRNG0 |  |  |  |  |  |

| bit 7        |                                                        |                                                       |             |                   |                 |                 | bit 0 |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

| Legend:      |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

| R = Readal   | ble bit                                                | W = Writable                                          | bit         | U = Unimplen      | nented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a | at POR                                                 | '1' = Bit is set                                      |             | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

| bit 7-2      | ITRIM<5:0>:                                            | Current Source                                        | e Trim bits |                   |                 |                 |       |  |  |  |  |  |

|              | 011111 <b>= M</b> a                                    | 011111 = Maximum positive change from nominal current |             |                   |                 |                 |       |  |  |  |  |  |

|              | 011110                                                 |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 000001 = Minimum positive change from nominal current  |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 000000 = Nominal current output specified by IRNG<1:0> |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 111111 = Minimum negative change from nominal current  |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              |                                                        |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 100001 = Maximum negative change from nominal current  |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

| bit 1-0      |                                                        | IRNG<1:0>: Current Source Range Select bits           |             |                   |                 |                 |       |  |  |  |  |  |

|              | 11 = 100 x Ba                                          |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 10 = 10 x Bas                                          |                                                       |             |                   |                 |                 |       |  |  |  |  |  |

|              | 01 = Base Cl                                           | 01 = Base Current Level (0.55 μA nominal)             |             |                   |                 |                 |       |  |  |  |  |  |

#### REGISTER 27-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

00 = Current Source Disabled

### 28.2.1 CONTROL REGISTER

Register 28-16 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT Enable Configuration bit, but only if the Configuration bit has disabled the WDT.

#### REGISTER 28-16: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| R/W-0        | U-0                                                                                                                                                                    | R-x                                   | R/W-0                 | U-0              | R/W-0                | R/W-0            | R/W-0                 |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|------------------|----------------------|------------------|-----------------------|--|--|--|

| REGSLP       |                                                                                                                                                                        | ULPLVL                                | SRETEN <sup>(2)</sup> | _                | ULPEN                | ULPSINK          | SWDTEN <sup>(1)</sup> |  |  |  |

| bit 7        |                                                                                                                                                                        |                                       |                       |                  |                      |                  | bit (                 |  |  |  |

| Legend:      |                                                                                                                                                                        |                                       |                       |                  |                      |                  |                       |  |  |  |

| R = Readab   | le bit                                                                                                                                                                 | W = Writable                          | bit                   | U = Unimple      | mented bit, rea      | d as '0'         |                       |  |  |  |

| -n = Value a | t POR                                                                                                                                                                  | '1' = Bit is se                       | t                     | ʻ0' = Bit is cl  | eared                | x = Bit is unk   | nown                  |  |  |  |

| bit 7        |                                                                                                                                                                        | Regulator Voltag<br>tor goes into Lov | -                     |                  | s Sloop modo i       | anablad          |                       |  |  |  |

|              |                                                                                                                                                                        | tor stays in norm                     |                       |                  |                      |                  |                       |  |  |  |

| bit 6        | Unimpleme                                                                                                                                                              | ented: Read as                        | '0'                   |                  | -                    |                  |                       |  |  |  |

| bit 5        | ULPLVL: U                                                                                                                                                              | Itra Low-Power                        | Wake-up Outp          | ut bit           |                      |                  |                       |  |  |  |

|              | Not valid ur                                                                                                                                                           | less ULPEN = 1                        | L.                    |                  |                      |                  |                       |  |  |  |

|              |                                                                                                                                                                        | e on RA0 pin > ~                      |                       |                  |                      |                  |                       |  |  |  |

|              | •                                                                                                                                                                      | e on RA0 pin < ~                      |                       | (2)              |                      |                  |                       |  |  |  |

| bit 4        | <b>SRETEN:</b> Regulator Voltage Sleep Disable bit <sup>(2)</sup><br>1 = If RETEN (CONFIG1L<0>) = 0 and the regulator is enabled, the device goes into Ultra Low-Power |                                       |                       |                  |                      |                  |                       |  |  |  |

|              |                                                                                                                                                                        | EN (CONFIG1L<<br>n Sleep              | (0>) = 0 and the      | e regulator is e | enabled, the dev     | rice goes into U | ltra Low-Powe         |  |  |  |

|              |                                                                                                                                                                        | gulator is on w                       | hen the device        | e's Sleep mo     | de is enabled        | and the Low-F    | ower mode is          |  |  |  |

|              |                                                                                                                                                                        | led by REGSLP                         |                       |                  |                      |                  |                       |  |  |  |

| bit 3        | Unimpleme                                                                                                                                                              | ented: Read as                        | ʻ0'                   |                  |                      |                  |                       |  |  |  |

| bit 2        | ULPEN: UI                                                                                                                                                              | tra Low-Power V                       | Vake-up Modul         | e Enable bit     |                      |                  |                       |  |  |  |

|              |                                                                                                                                                                        | ow-Power Wake<br>ow-Power Wake        |                       |                  | LVL bit indicate     | s the comparat   | or output             |  |  |  |

| bit 1        | ULPSINK:                                                                                                                                                               | Ultra Low-Powe                        | r Wake-up Cur         | rent Sink Ena    | ble bit              |                  |                       |  |  |  |

|              | Not valid ur                                                                                                                                                           | less ULPEN = 1                        | L.                    |                  |                      |                  |                       |  |  |  |

|              |                                                                                                                                                                        | ow-Power Wake<br>ow-Power Wake        |                       |                  |                      |                  |                       |  |  |  |

| bit 0        | SWDTEN: S                                                                                                                                                              | Software Contro                       | lled Watchdog         | Timer Enable     | e bit <sup>(1)</sup> |                  |                       |  |  |  |

|              |                                                                                                                                                                        | og Timer is on                        |                       |                  |                      |                  |                       |  |  |  |

|              | 0 = Watchd                                                                                                                                                             | og Timer is off                       |                       |                  |                      |                  |                       |  |  |  |

| Note 1. T    | his hit has no o                                                                                                                                                       | ffect if the Confi                    | guration bits. M      |                  | are enabled          |                  |                       |  |  |  |

**Note 1:** This bit has no effect if the Configuration bits, WDTEN<1:0>, are enabled.

**2:** This bit is available only when ENVREG = 1 and  $\overline{\text{RETEN}}$  = 0.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1   | Bit 0  |

|--------|--------|--------|--------|--------|-------|-------|---------|--------|

| RCON   | IPEN   | SBOREN | CM     | RI     | TO    | PD    | POR     | BOR    |

| WDTCON | REGSLP |        | ULPLVL | SRETEN |       | ULPEN | ULPSINK | SWDTEN |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

| ADDWFC                                                                               | ADD W an                                                                                              | ADD W and Carry bit to f                                                                                                                                                |                                                                 |                                                |  |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|--|--|--|--|

| Syntax:                                                                              | ADDWFC                                                                                                | f {,d {,                                                                                                                                                                | a}}                                                             |                                                |  |  |  |  |

| Operands:                                                                            | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                   | d ∈ [0,1]                                                                                                                                                               |                                                                 |                                                |  |  |  |  |

| Operation:                                                                           | (W) + (f) +                                                                                           | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                      |                                                                 |                                                |  |  |  |  |

| Status Affected:                                                                     | N,OV, C, D                                                                                            | C, Z                                                                                                                                                                    |                                                                 |                                                |  |  |  |  |

| Encoding:                                                                            | 0010                                                                                                  | 00da                                                                                                                                                                    | ffff                                                            | ffff                                           |  |  |  |  |

| Description:                                                                         | location 'f'<br>placed in V                                                                           | Add W, the Carry flag and data memory<br>location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |                                                                 |                                                |  |  |  |  |

|                                                                                      | lf 'a' is '1', t                                                                                      | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.                                                                |                                                                 |                                                |  |  |  |  |

|                                                                                      | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 29<br>Bit-Oriente<br>Literal Off | led, this i<br>Literal O<br>never f ≤<br>0.2.3 "By<br>ed Instru                                                                                                         | nstruction<br>ffset Addr<br>95 (5Fh).<br>te-Orient<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |  |

| Words:                                                                               | 1                                                                                                     |                                                                                                                                                                         |                                                                 |                                                |  |  |  |  |

| Cycles:                                                                              | 1                                                                                                     |                                                                                                                                                                         |                                                                 |                                                |  |  |  |  |

| Q Cycle Activity:                                                                    |                                                                                                       |                                                                                                                                                                         |                                                                 |                                                |  |  |  |  |

| Q1                                                                                   | Q2                                                                                                    | Q3                                                                                                                                                                      |                                                                 | Q4                                             |  |  |  |  |

| Decode                                                                               | Read<br>register 'f'                                                                                  | Proce<br>Data                                                                                                                                                           |                                                                 | Vrite to<br>stination                          |  |  |  |  |

| Example:                                                                             | ADDWFC                                                                                                | REG,                                                                                                                                                                    | 0, 1                                                            |                                                |  |  |  |  |

| Before Instruc<br>Carry bit<br>REG<br>W<br>After Instructio<br>Carry bit<br>REG<br>W | = 1<br>= 02h<br>= 4Dh                                                                                 |                                                                                                                                                                         |                                                                 |                                                |  |  |  |  |

| ANDLW                 | AND Litera                  | AND Literal with W |     |          |      |  |  |  |

|-----------------------|-----------------------------|--------------------|-----|----------|------|--|--|--|

| Syntax:               | ANDLW                       | k                  |     |          |      |  |  |  |

| Operands:             | $0 \le k \le 255$           |                    |     |          |      |  |  |  |

| Operation:            | (W) .AND.                   | $k \rightarrow W$  |     |          |      |  |  |  |

| Status Affected:      | N, Z                        |                    |     |          |      |  |  |  |

| Encoding:             | 0000                        | 1011               | kkk | k        | kkkk |  |  |  |

| Description:          | The conten<br>8-bit literal |                    |     |          |      |  |  |  |

| Words:                | 1                           |                    |     |          |      |  |  |  |

| Cycles:               | 1                           |                    |     |          |      |  |  |  |

| Q Cycle Activity:     |                             |                    |     |          |      |  |  |  |

| Q1                    | Q2                          | Q3                 | 1   |          | Q4   |  |  |  |

| Decode                | Read literal<br>'k'         | Process<br>Data    |     | Write to |      |  |  |  |

| Example:              | ANDLW                       | 05Fh               |     |          |      |  |  |  |

| Before Instruc<br>W   | = A3h                       |                    |     |          |      |  |  |  |

| After Instructio<br>W | on<br>= 03h                 |                    |     |          |      |  |  |  |

| RRNCF                                                          | Rotate Right f (No Carry)                                                                                                                                                                                                                                                            |                                                                                                                                                                             |         |                                                 |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------|--|--|--|

| Syntax:                                                        | RRNCF                                                                                                                                                                                                                                                                                | RRNCF f {,d {,a}}                                                                                                                                                           |         |                                                 |  |  |  |

| Operands:                                                      | $0 \le f \le 253$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                  | 5                                                                                                                                                                           |         |                                                 |  |  |  |

| Operation:                                                     | $(f \le n >) \rightarrow$<br>$(f \le 0 >) \rightarrow$                                                                                                                                                                                                                               | dest <n 1<br="" –="">dest&lt;7&gt;</n>                                                                                                                                      | L>,     |                                                 |  |  |  |

| Status Affected:                                               | N, Z                                                                                                                                                                                                                                                                                 |                                                                                                                                                                             |         |                                                 |  |  |  |

| Encoding:                                                      | 0100                                                                                                                                                                                                                                                                                 | 00da                                                                                                                                                                        | fff     | f ffff                                          |  |  |  |

| Description:                                                   | one bit to<br>is placed                                                                                                                                                                                                                                                              | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. |         |                                                 |  |  |  |

|                                                                | selected,                                                                                                                                                                                                                                                                            | n the bank                                                                                                                                                                  | the BS  | nk will be<br>SR value. If 'a'<br>e selected as |  |  |  |