Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

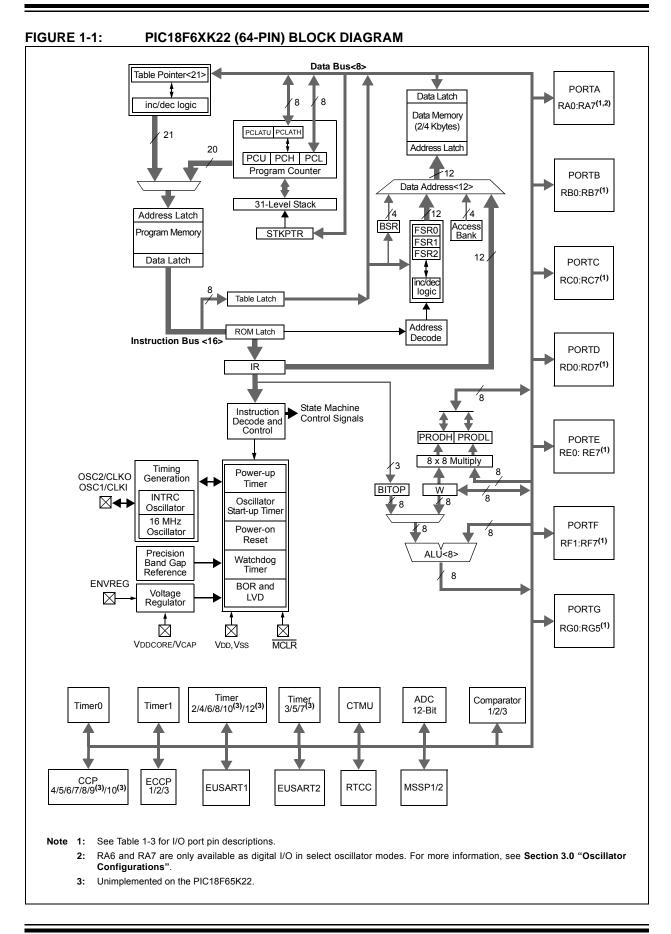

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k22-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nama                                                           | Pin Number | Pin                  | Buffer                       | Description                                                                                                                              |  |  |  |  |

|--------------------------------------------------------------------|------------|----------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                           | TQFP Type  |                      | Туре                         | Description                                                                                                                              |  |  |  |  |

|                                                                    |            |                      |                              | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |

| RC0/SOSCO/SCKLI<br>RC0<br>SOSCO<br>SCKLI                           | 36         | I/O<br>O<br>I        | ST<br>—<br>ST                | Digital I/O.<br>SOSC oscillator output.<br>Digital SOSC input.                                                                           |  |  |  |  |

| RC1/SOSCI/ECCP2/P2A<br>RC1<br>SOSCI<br>ECCP2 <sup>(1)</sup><br>P2A | 35         | I/O<br>I<br>I/O<br>O | ST<br>CMOS<br>ST<br>—        | Digital I/O.<br>SOSC oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>Enhanced PWM2 Output A.                       |  |  |  |  |

| RC2/ECCP1/P1A<br>RC2<br>ECCP1<br>P1A                               | 43         | I/O<br>I/O<br>O      | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced PWM1 Output A.                                                 |  |  |  |  |

| RC3/SCK1/SCL1<br>RC3<br>SCK1<br>SCL1                               | 44         | I/O<br>I/O<br>I/O    | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |  |  |  |  |

| RC4/SDI1/SDA1<br>RC4<br>SDI1<br>SDA1                               | 45         | I/O<br>I<br>I/O      | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |  |  |  |  |

| RC5/SDO1<br>RC5<br>SDO1                                            | 46         | I/O<br>O             | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                                                            |  |  |  |  |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                                   | 37         | I/O<br>O<br>I/O      | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX1/DT1).                                         |  |  |  |  |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                                   | 38         | I/O<br>I<br>I/O      | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX1/CK1).                                           |  |  |  |  |

| Legend: TTL = TTL com<br>ST = Schmitt 1                            |            | h CMC                | )S levels                    | CMOS = CMOS compatible input or output<br>Analog = Analog input                                                                          |  |  |  |  |

#### PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED) TABLE 1-4.

= Input = Power Ρ

L

$I^2C = I^2C^{TM}/SMBus$

= Output OD = Open-Drain (no P diode to VDD)

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

0

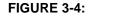

### 3.5 External Oscillator Modes

### 3.5.1 CRYSTAL OSCILLATOR/CERAMIC RESONATORS (HS MODES)

In HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-4 shows the pin connections.

The oscillator design requires the use of a crystal rated for parallel resonant operation.

**Note:** Use of a crystal rated for series resonant operation may give a frequency out of the crystal manufacturer's specifications.

## TABLE 3-2:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical | Capacitor | Values | Used: |  |

|---------|-----------|--------|-------|--|

|         |           |        |       |  |

| Mode | Freq.    | Freq. OSC1 |       |

|------|----------|------------|-------|

| HS   | 8.0 MHz  | 27 pF      | 27 pF |

|      | 16.0 MHz | 22 pF      | 22 pF |

Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator-specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC<sup>®</sup> Oscillator Design"

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following Table 3-3 for additional information.

## TABLE 3-3:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Typical Capa<br>Tes |       |

|----------|------------------|---------------------|-------|

|          | Fieq.            | C1                  | C2    |

| HS       | 4 MHz            | 27 pF               | 27 pF |

|          | 8 MHz            | 22 pF               | 22 pF |

|          | 20 MHz           | 15 pF               | 15 pF |

### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

Refer to the Microchip application notes cited in Table 3-2 for oscillator-specific information. Also see the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: Rs may be required to avoid overdriving crystals with a low drive level specification.

- 4: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

### CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

| Address | File Name              | Bit 7                   | Bit 6                                               | Bit 5               | Bit 4        | Bit 3            | Bit 2     | Bit 1     | Bit 0    | Value on<br>POR, BOR |  |

|---------|------------------------|-------------------------|-----------------------------------------------------|---------------------|--------------|------------------|-----------|-----------|----------|----------------------|--|

| F5Ch    | RTCVALL                | RTCC Value L            | RTCC Value Low Register Window Based on RTCPTR<1:0> |                     |              |                  |           |           |          |                      |  |

| F5Bh    | ALRMCFG                | ALRMEN                  | CHIME                                               | AMASK3              | AMASK2       | AMASK1           | AMASK0    | ALRMPTR1  | ALRMPTR0 | 0000 0000            |  |

| F5Ah    | ALRMRPT                | ARPT7                   | ARPT6                                               | ARPT5               | ARPT4        | ARPT3            | ARPT2     | ARPT1     | ARPT0    | 0000 0000            |  |

| F59h    | ALRMVALH               | Alarm Value H           | ligh Register V                                     | Vindow Based        | on APTR<1:0> |                  |           |           |          | xxxx xxxx            |  |

| F58h    | ALRMVALL               | Alarm Value L           | rm Value Low Register Window Based on APTR<1:0>     |                     |              |                  |           |           |          | XXXX XXXX            |  |

| F57h    | CTMUCONH               | CTMUEN                  | _                                                   | CTMUSIDL            | TGEN         | EDGEN            | EDGSEQEN  | IDISSEN   | CTTRIG   | 0-00 0000            |  |

| F56h    | CTMUCONL               | EDG2POL                 | EDG2SEL1                                            | EDG2SEL0            | EDG1POL      | EDG1SEL1         | EDG1SEL0  | EDG2STAT  | EDG1STAT | 0000 0000            |  |

| F55h    | CTMUICONH              | ITRIM5                  | ITRIM4                                              | ITRIM3              | ITRIM2       | ITRIM1           | ITRIM0    | IRNG1     | IRNG0    | 0000 0000            |  |

| F54h    | CM1CON                 | CON                     | COE                                                 | CPOL                | EVPOL1       | EVPOL0           | CREF      | CCH1      | CCH0     | 0001 1111            |  |

| F53h    | PADCFG1                | RDPU                    | REPU                                                | RJPU <sup>(2)</sup> | —            | —                | RTSECSEL1 | RTSECSEL0 | —        | 00000-               |  |

| F52h    | ECCP2AS                | ECCP2ASE                | ECCP2AS2                                            | ECCP2AS1            | ECCP2AS0     | PSS2AC1          | PSS2AC0   | PSS2BD1   | PSS2BD0  | 0000 0000            |  |

| F51h    | ECCP2DEL               | P2RSEN                  | P2DC6                                               | P2DC5               | P2DC4        | P2DC3            | P2DC2     | P2DC1     | P2DC0    | 0000 0000            |  |

| F50h    | CCPR2H                 | Capture/Com             | oare/PWM Reg                                        | gister 2 High B     | yte          |                  |           |           |          | XXXX XXXX            |  |

| F4Fh    | CCPR2L                 | Capture/Com             | oare/PWM Reg                                        | gister 2 Low By     | /te          |                  |           |           |          | XXXX XXXX            |  |

| F4Eh    | CCP2CON                | P2M1                    | P2M0                                                | DC2B1               | DC2B0        | CCP2M3           | CCP2M2    | CCP2M1    | CCP2M0   | 0000 0000            |  |

| F4Dh    | ECCP3AS                | ECCP3ASE                | ECCP3AS2                                            | ECCP3AS1            | ECCP3AS0     | PSS3AC1          | PSS3AC0   | PSS3BD1   | PSS3BD0  | 0000 0000            |  |

| F4Ch    | ECCP3DEL               | P3RSEN                  | P3DC6                                               | P3DC5               | P3DC4        | P3DC3            | P3DC2     | P3DC1     | P3DC0    | 0000 0000            |  |

| F4Bh    | CCPR3H                 | Capture/Com             | pare/PWM Reg                                        | gister 3 High B     | yte          |                  |           |           |          | xxxx xxxx            |  |

| F4Ah    | CCPR3L                 | Capture/Com             | pare/PWM Reg                                        | gister 3 Low By     | /te          |                  |           |           |          | xxxx xxxx            |  |

| F49h    | CCP3CON                | P3M1                    | P3M0                                                | DC3B1               | DC3B0        | CCP3M3           | CCP3M2    | CCP3M1    | CCP3M0   | 0000 0000            |  |

| F48h    | CCPR8H                 | Capture/Com             | pare/PWM Reg                                        | gister 8 High B     | vte          |                  |           |           | I        | xxxx xxxx            |  |

| F47h    | CCPR8L                 |                         | pare/PWM Reg                                        |                     |              |                  |           |           |          | xxxx xxxx            |  |

| F46h    | CCP8CON                |                         | _                                                   | DC8B1               | DC8B0        | CCP8M3           | CCP8M2    | CCP8M1    | CCP8M0   | 00 0000              |  |

| F45h    | CCPR9H <sup>(3)</sup>  | Capture/Com             | pare/PWM Reg                                        | gister 9 High B     | yte          |                  |           |           |          | xxxx xxxx            |  |

| F44h    | CCPR9L <sup>(3)</sup>  | Capture/Com             | pare/PWM Reg                                        | gister 9 Low By     | /te          |                  |           |           |          | xxxx xxxx            |  |

| F43h    | CCP9CON <sup>(3)</sup> |                         | _                                                   | DC9B1               | DC9B0        | CCP9M3           | CCP9M2    | CCP9M1    | CCP9M0   | 00 0000              |  |

| F42h    | CCPR10H(3)             | Capture/Com             | pare/PWM Reg                                        | gister 10 High I    | Byte         |                  |           |           |          | xxxx xxxx            |  |

| F41h    | CCPR10L(3)             | Capture/Com             | oare/PWM Reg                                        | gister 10 Low E     | Byte         |                  |           |           |          | xxxx xxxx            |  |

| F40h    | CCP10CON(3)            |                         | _                                                   | DC10B1              | DC10B0       | CCP10M3          | CCP10M2   | CCP10M1   | CCP10M0  | 00 0000              |  |

| F3Fh    | TMR7H <sup>(3)</sup>   | Timer7 Regist           | er High Byte                                        |                     | I            |                  |           |           | I        | xxxx xxxx            |  |

| F3Eh    | TMR7L <sup>(3)</sup>   | Timer7 Regist           |                                                     |                     |              |                  |           |           |          | 0000 0000            |  |

| F3Dh    | T7CON <sup>(3)</sup>   | TMR7CS1                 | TMR7CS0                                             | T7CKPS1             | T7CKPS0      | SOSCEN           | T7SYNC    | RD16      | TMR70N   | 0000 0000            |  |

| F3Ch    | T7GCON <sup>(3)</sup>  | TMR7GE                  | T7GPOL                                              | T7GTM               | T7GSPM       | T7GGO/<br>T7DONE | T7GVAL    | T7GSS1    | T7GSS0   | 0000 0x00            |  |

| F3Bh    | TMR6                   | Timer6 Regist           | er                                                  |                     |              |                  |           |           |          | 0000 0000            |  |

| F3Ah    | PR6                    | Timer6 Period           |                                                     |                     |              |                  |           |           |          | 1111 1111            |  |

| F39h    | T6CON                  | _                       | T6OUTPS3                                            | T6OUTPS2            | T6OUTPS1     | T6OUTPS0         | TMR6ON    | T6CKPS1   | T6CKPS0  | -000 0000            |  |

| F38h    | TMR8                   | Timer8 Register         |                                                     |                     |              |                  |           | 0000 0000 |          |                      |  |

| F37h    | PR8                    | Timer8 Period           |                                                     |                     |              |                  |           |           |          | 1111 1111            |  |

| F36h    | T8CON                  |                         | T8OUTPS3                                            | T8OUTPS2            | T8OUTPS1     | T8OUTPS0         | TMR8ON    | T8CKPS1   | T8CKPS0  | -000 0000            |  |

| F35h    | TMR10 <sup>(3)</sup>   |                         |                                                     |                     |              |                  |           | 0000 0000 |          |                      |  |

| F34h    | PR10 <sup>(3)</sup>    | Timer10 Period Register |                                                     |                     |              |                  |           | 1111 1111 |          |                      |  |

| F33h    | T10CON <sup>(3)</sup>  | _                       | 8                                                   | T10OUTPS2           | T10OUTPS1    | T10OUTPS0        | TMR100N   | T10CKPS1  | T10CKPS0 | -000 0000            |  |

| F32h    | TMR12 <sup>(3)</sup>   | TMR12 Regis             |                                                     |                     |              |                  |           |           |          | 0000 0000            |  |

| F31h    | PR12 <sup>(3)</sup>    | Timer12 Perio           |                                                     |                     |              |                  |           |           |          | 1111 1111            |  |

| F30h    | T12CON <sup>(3)</sup>  |                         | 2                                                   | T12OUTPS2           | T12OUTPS1    | T12OUTPS0        | TMR12ON   | T12CKPS1  | T12CKPS0 | -000 0000            |  |

| F2Fh    | CM2CON                 | CON                     | COE                                                 | CPOL                | EVPOL1       | EVPOL0           | CREF      | CCH1      | CCH0     | 0001 1111            |  |

| F2Eh    | CM3CON                 | CON                     | COE                                                 | CPOL                | EVPOL1       | EVPOL0           | CREF      | CCH1      | CCH0     | 0001 1111            |  |

| F2Dh    | CCPTMRS0               | C3TSEL1                 | C3TSEL0                                             | C2TSEL2             | C2TSEL1      | C2TSEL0          | C1TSEL2   | C1TSEL1   | C1TSEL0  | 0000 0000            |  |

#### TARI E 6-2. PIC18F87K22 FAMILY REGISTER FILE SUMMARY (CONTINUED)

This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented. Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'. Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22). Note 1:

2: 3:

### REGISTER 11-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1      | R/W-1                                                            | R/W-0                                                 | R/W-0                          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|------------|------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|--------|

| INT2IP     | INT1IP                                                           | INT3IE                                                | INT2IE                         | INT1IE           | INT3IF          | INT2IF          | INT1IF |

| bit 7      |                                                                  |                                                       |                                |                  |                 |                 | bit (  |

| Legend:    |                                                                  |                                                       |                                |                  |                 |                 |        |

| R = Reada  | able bit                                                         | W = Writable                                          | bit                            | U = Unimpler     | nented bit, rea | d as '0'        |        |

| -n = Value | at POR                                                           | '1' = Bit is set                                      |                                | '0' = Bit is cle |                 | x = Bit is unkr | nown   |

| bit 7      | 1 = High prio                                                    | ,                                                     | upt Priority bit               |                  |                 |                 |        |

| bit 6      | 0 = Low prior<br>INT1IP: INT1<br>1 = High prio<br>0 = Low prior  | External Interr                                       | upt Priority bit               |                  |                 |                 |        |

| bit 5      | INT3IE: INT3<br>1 = Enables 1                                    | External Interr<br>the INT3 exterr<br>the INT3 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 4      | 1 = Enables                                                      | External Interr<br>the INT2 exterr<br>the INT2 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 3      | 1 = Enables                                                      | External Interr<br>the INT1 exterr<br>the INT1 exter  | nal interrupt                  |                  |                 |                 |        |

| bit 2      | 1 = The INT3                                                     | External Interr<br>external interr<br>external interr | upt occurred (                 | must be cleared  | d in software)  |                 |        |

| bit 1      | INT2IF: INT2<br>1 = The INT2                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

| bit 0      | INT1IF: INT1<br>1 = The INT1                                     | External Interr                                       | upt Flag bit<br>upt occurred ( | must be cleared  | d in software)  |                 |        |

|            | Interrupt flag bits<br>enable bit or the 0<br>are clear prior to | Global Interrupt                                      | Enable bit. Us                 | ser software sho | ould ensure the | appropriate int |        |

## 12.2 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISA and LATA.

RA4/T0CKI is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

RA5 and RA<3:0> are multiplexed with analog inputs for the A/D Converter.

The operation of the analog inputs as A/D Converter inputs is selected by clearing or setting the ANSEL control bits in the ANCON1 register. The corresponding TRISA bits control the direction of these pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| Note: | RA5 and RA<3:0> are configured as             |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | analog inputs on any Reset and are rea        |  |  |  |  |  |

|       | as '0'. RA4 is configured as a digital input. |  |  |  |  |  |

OSC2/CLKO/RA6 and OSC1/CLKI/RA7 normally serve as the external circuit connections for the external (primary) oscillator circuit (HS Oscillator modes), or the external clock input and output (EC Oscillator modes). In these cases, RA6 and RA7 are not available as digital I/O and their corresponding TRIS and LAT bits are read as '0'. When the device is configured to use HF-INTOSC, MF-INTOSC or LF-INTOSC as the default oscillator mode, RA6 and RA7 are automatically configured as digital I/O; the oscillator and clock in/clock out functions are disabled.

RA5 has additional functionality for Timer1 and Timer3. It can be configured as the Timer1 clock input or the Timer3 external clock gate input.

| CLRF    | PORTA  | ; Initialize PORTA by              |

|---------|--------|------------------------------------|

|         |        | ; clearing output latches          |

| CLRF    | LATA   | ; Alternate method to              |

|         |        | ; clear output data latches        |

| BANKSEL | ANCON1 | ; Select bank with ANCON1 register |

| MOVLW   | 00h    | ; Configure A/D                    |

| MOVWF   | ANCON1 | ; for digital inputs               |

| BANKSEL | TRISA  | ; Select bank with TRISA register  |

| MOVLW   | OBFh   | ; Value used to initialize         |

|         |        | ; data direction                   |

| MOVWF   | TRISA  | ; Set RA<7, 5:0> as inputs,        |

|         |        | ; RA<6> as output                  |

|         |        |                                    |

### 12.9 PORTH, LATH and TRISH Registers

| Note: | PORTH is | available | only | on | the | 80-pin |

|-------|----------|-----------|------|----|-----|--------|

|       | devices. |           |      |    |     |        |

PORTH is an 8-bit wide, bidirectional I/O port. The corresponding Data Direction and Output Latch registers are TRISH and LATH.

All pins on PORTH are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

### EXAMPLE 12-8: INITIALIZING PORTH

| CLRF    | PORTH  | ; | Initialize PORTH by              |

|---------|--------|---|----------------------------------|

|         |        | ; | clearing output                  |

|         |        | ; | data latches                     |

| CLRF    | LATH   | ; | Alternate method                 |

|         |        | ; | to clear output                  |

|         |        | ; | data latches                     |

| BANKSEL | ANCON2 | ; | Select bank with ANCON2 register |

| MOVLW   | 0Fh    | ; | Configure PORTH as               |

| MOVWF   | ANCON2 | ; | digital I/O                      |

| MOVLW   | 0Fh    | ; | Configure PORTH as               |

| MOVWF   | ANCON1 | ; | digital I/O                      |

| BANKSEL | TRISH  | ; | Select bank with TRISH register  |

| MOVLW   | 0CFh   | ; | Value used to                    |

|         |        | ; | initialize data                  |

|         |        | ; | direction                        |

| MOVWF   | TRISH  | ; | Set RH3:RH0 as inputs            |

|         |        | ; | RH5:RH4 as outputs               |

|         |        | ; | RH7:RH6 as inputs                |

|         |        |   |                                  |

| Pin Name     | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                 |

|--------------|----------|-----------------|-----|-------------|---------------------------------------------------------------------------------------------|

| RH0/AN23/A16 | RH0      | 0               | 0   | DIG         | LATH<0> data output.                                                                        |

|              |          | 1               | Ι   | ST          | PORTH<0> data input.                                                                        |

|              | AN23     | 1               | Ι   | ANA         | A/D Input Channel 23.<br>Default input configuration on POR; does not affect digital input. |

|              | A16      | x               | 0   | DIG         | External memory interface, Address Line 16; takes priority over port data.                  |

| RH1/AN22/A17 | RH1      | 0               | 0   | DIG         | LATH<1> data output.                                                                        |

|              |          | 1               | Ι   | ST          | PORTH<1> data input.                                                                        |

|              | AN22     | 1               | Ι   | ANA         | A/D Input Channel 22.<br>Default input configuration on POR; does not affect digital input. |

|              | A17      | x               | 0   | DIG         | External memory interface, Address Line 17; takes priority over port data.                  |

| RH2/AN21/A18 | RH2      | 0               | 0   | DIG         | LATH<2> data output.                                                                        |

|              |          | 1               | I   | ST          | PORTH<2> data input.                                                                        |

|              | AN21     | 1               | Ι   | ANA         | A/D Input Channel 21.<br>Default input configuration on POR; does not affect digital input. |

|              | A18      | x               | 0   | DIG         | External memory interface, Address Line 18; takes priority over port data.                  |

| RH3/AN20/A19 | RH3      | 0               | 0   | DIG         | LATH<3> data output.                                                                        |

|              |          | 1               | I   | ST          | PORTH<3> data input.                                                                        |

|              | AN20     | 1               | Ι   | ANA         | A/D Input Channel 20.<br>Default input configuration on POR; does not affect digital input. |

|              | A19      | x               | 0   | DIG         | External memory interface, Address Line 19; takes priority over port data.                  |

### TABLE 12-15: PORTH FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

### 13.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 13-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 13-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 13-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 13-1: TOCON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                   |                                    |                                |                    |

|------------|-------------------|------------------------------------|--------------------------------|--------------------|

| R = Reada  | ble bit           | W = Writable bit                   | U = Unimplemented bit          | , read as '0'      |

| -n = Value | at POR            | '1' = Bit is set                   | '0' = Bit is cleared           | x = Bit is unknown |

|            |                   |                                    |                                |                    |

| bit 7      | TMR0ON            | : Timer0 On/Off Control bit        |                                |                    |

|            | 1 = Enabl         | es Timer0                          |                                |                    |

|            | 0 = Stops         | Timer0                             |                                |                    |

| bit 6      | <b>T08BIT</b> : T | ïmer0 8-Bit/16-Bit Control b       | it                             |                    |

|            | 1 = Timer         | 0 is configured as an 8-bit ti     | mer/counter                    |                    |

|            | 0 = Timer         | 0 is configured as a 16-bit ti     | mer/counter                    |                    |

| bit 5      | TOCS: Tir         | ner0 Clock Source Select bi        | t                              |                    |

|            | 1 = Trans         | ition on TOCKI pin input edg       | le                             |                    |

|            | 0 = Intern        | al clock (Fosc/4)                  |                                |                    |

| bit 4      | T0SE: Tin         | ner0 Source Edge Select bit        | t                              |                    |

|            | 1 = Increr        | nent on high-to-low transitio      | n on T0CKI pin                 |                    |

|            | 0 = Increr        | ment on low-to-high transitio      | n on T0CKI pin                 |                    |

| bit 3      | PSA: Tim          | er0 Prescaler Assignment b         | it                             |                    |

|            | 1 = Timer         | 0 prescaler is not assigned;       | Timer0 clock input bypasses    | prescaler          |

|            | 0 = Timer         | 0 prescaler is assigned; Tim       | ner0 clock input comes from pr | escaler output     |

| bit 2-0    | T0PS<2:0          | >: Timer0 Prescaler Select         | bits                           |                    |

|            | 111 <b>= 1</b> :2 | 56 Prescale value                  |                                |                    |

|            | 110 <b>= 1</b> :1 | 28 Prescale value                  |                                |                    |

|            | 101 <b>= 1</b> :6 | 4 Prescale value                   |                                |                    |

|            |                   | 2 Prescale value                   |                                |                    |

|            |                   | 6 Prescale value                   |                                |                    |

|            |                   | Prescale value                     |                                |                    |

|            | 001 = 1:4         | <ul> <li>Prescale value</li> </ul> |                                |                    |

### TABLE 14-5: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name    | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3            | Bit 2   | Bit 1  | Bit 0   |

|---------|-------------|----------------|---------|---------|------------------|---------|--------|---------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INT0IE  | RBIE             | TMR0IF  | INT0IF | RBIF    |

| PIR1    | PSPIF       | ADIF           | RC1IF   | TX1IF   | SSP1IF           | TMR1GIF | TMR2IF | TMR1IF  |

| PIE1    | PSPIE       | ADIE           | RC1IE   | TX1IE   | SSP1IE           | TMR1GIE | TMR2IE | TMR1IE  |

| IPR1    | PSPIP       | ADIP           | RC1IP   | TX1IP   | SSP1IP           | TMR1GIP | TMR2IP | TMR1IP  |

| TMR1L   | Timer1 Regi | ster Low Byte  | 9       |         |                  |         |        |         |

| TMR1H   | Timer1 Regi | ster High Byte | е       |         |                  |         |        |         |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1 | T1CKPS0 | SOSCEN           | T1SYNC  | RD16   | TMR10N  |

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM   | T1GSPM  | T1GGO/<br>T1DONE | T1GVAL  | T1GSS1 | T1GSS0  |

| OSCCON2 | _           | SOSCRUN        | _       | —       | SOSCGO           | _       | MFIOFS | MFIOSEL |

| PMD1    | PSPMD       | CTMUMD         | RTCCMD  | TMR4MD  | TMR3MD           | TMR2MD  | TMR1MD | EMBDM   |

Legend: Shaded cells are not used by the Timer1 module.

Note 1: Unimplemented on 32-Kbyte devices (PIC18FX5K22).

### 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex, asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

All members of the PIC18F87K22 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1) and PORTG (RG1/TX2/CK2/AN19/C3OUT and RG2/RX2/DT2/AN18/C3INA), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- Bit, SPEN (RCSTA1<7>), must be set (= 1)

- Bit, TRISC<7>, must be set (= 1)

- Bit, TRISC<6>, must be cleared (= 0) for Asynchronous and Synchronous Master modes

- Bit, TRISC<6>, must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- Bit, SPEN (RCSTA2<7>), must be set (= 1)

- Bit, TRISG<2>, must be set (= 1)

- Bit TRISG<1> must be cleared (= 0) for Asynchronous and Synchronous Master modes

- Bit, TRISC<6>, must be set (= 1) for Synchronous Slave mode

Note: The EUSART control will automatically reconfigure the pin from input to output as needed.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed on the following pages in Register 22-1, Register 22-2 and Register 22-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

| TADLE 22-0. | REGISTE     | K3 A3300       |             | пэтисп         |              |             |               |        |

|-------------|-------------|----------------|-------------|----------------|--------------|-------------|---------------|--------|

| Name        | Bit 7       | Bit 6          | Bit 5       | Bit 4          | Bit 3        | Bit 2       | Bit 1         | Bit 0  |

| INTCON      | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE         | RBIE         | TMR0IF      | INT0IF        | RBIF   |

| PIR1        | PSPIF       | ADIF           | RC1IF       | TX1IF          | SSP1IF       | TMR1GIF     | TMR2IF        | TMR1IF |

| PIE1        | PSPIE       | ADIE           | RC1IE       | TX1IE          | SSP1IE       | TMR1GIE     | TMR2IE        | TMR1IE |

| IPR1        | PSPIP       | ADIP           | RC1IP       | TX1IP          | SSP1IP       | TMR1GIP     | TMR2IP        | TMR1IP |

| PIR3        | TMR5GIF     | _              | RC2IF       | TX2IF          | CTMUIF       | CCP2IF      | CCP1IF        | RTCCIF |

| PIE3        | TMR5GIE     | _              | RC2IE       | TX2IE          | CTMUIE       | CCP2IE      | CCP1IE        | RTCCIE |

| IPR3        | TMR5GIP     | _              | RC2IP       | TX2IP          | CTMUIP       | CCP2IP      | CCP1IP        | RTCCIP |

| RCSTA1      | SPEN        | RX9            | SREN        | CREN           | ADDEN        | FERR        | OERR          | RX9D   |

| RCREG1      | EUSART1 R   | eceive Regist  | er          |                |              |             |               |        |

| TXSTA1      | CSRC        | TX9            | TXEN        | SYNC           | SENDB        | BRGH        | TRMT          | TX9D   |

| BAUDCON1    | ABDOVF      | RCIDL          | RXDTP       | TXCKP          | BRG16        |             | WUE           | ABDEN  |

| SPBRGH1     | EUSART1 Ba  | aud Rate Gen   | erator Regi | ster High Byt  | e            |             |               |        |

| SPBRG1      | EUSART1 B   | aud Rate Gen   | erator Regi | ster           |              |             |               |        |

| RCSTA2      | SPEN        | RX9            | SREN        | CREN           | ADDEN        | FERR        | OERR          | RX9D   |

| RCREG2      | EUSART2 R   | eceive Regist  | er          |                |              |             |               |        |

| TXSTA2      | CSRC        | TX9            | TXEN        | SYNC           | SENDB        | BRGH        | TRMT          | TX9D   |

| BAUDCON2    | ABDOVF      | RCIDL          | RXDTP       | TXCKP          | BRG16        |             | WUE           | ABDEN  |

| SPBRGH2     | EUSART2 Ba  | aud Rate Gen   | erator Regi | ster High Byt  | e            |             |               |        |

| SPBRG2      | EUSART2 Ba  | aud Rate Gen   | erator Regi | ster           |              |             |               |        |

| ODCON3      | U2OD        | U10D           |             |                |              |             |               | CTMUDS |

| PMD0        | CCP3MD      | CCP2MD         | CCP1MD      | UART2MD        | UART1MD      | SSP2MD      | SSP1MD        | ADCMD  |

| Legend: — = | unimplement | ed, read as '0 | '. Shaded c | ells are not u | sed for sync | hronous mas | ter reception |        |

#### **REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION** TABLE 22-8:

Legend: = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

### 23.8 Use of the Special Event Triggers

A/D conversion can be started by the Special Event Trigger of any of these modules:

- ECCP2 Requires CCP2M<3:0> bits (CCP2CON<3:0>) set at '1011'

- CTMU Requires the setting of the CTTRIG bit (CTMUCONH<0>)

- Timer1

- RTCC

To start an A/D conversion:

- The A/D module must be enabled (ADON = 1)

- The appropriate analog input channel is selected

- The minimum acquisition period is set one of these ways:

- Timing provided by the user

- Selection made of an appropriate TACQ time

With these conditions met, the trigger sets the GO/DONE bit and the A/D acquisition starts.

If the A/D module is not enabled (ADON = 0), the module ignores the Special Event Trigger.

Note: With an ECCP2 trigger, Timer1 or Timer 3 is cleared. The timers reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH:ADRESL to the desired location). If the A/D module is not enabled, the Special Event Trigger is ignored by the module, but the timer's counter resets.

### 23.9 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined, in part, by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON2 should be updated in accordance with the power-managed mode clock that will be used.

After the power-managed mode is entered (either of the power-managed Run modes), an A/D acquisition or conversion may be started. Once an acquisition or conversion is started, the device should continue to be clocked by the same power-managed mode clock source until the conversion has been completed. If desired, the device may be placed into the corresponding power-managed Idle mode during the conversion.

If the power-managed mode clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in Sleep mode requires that the A/D RC clock be selected. If bits, ACQT<2:0>, are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry into Sleep mode. The IDLEN and SCS<1:0> bits in the OSCCON register must have already been cleared prior to starting the conversion.

| R/W-0        | R/W-0                                                      | R/W-0            | R/W-0         | R/W-0             | R/W-0           | DAM 0           | R/W-0 |

|--------------|------------------------------------------------------------|------------------|---------------|-------------------|-----------------|-----------------|-------|

|              |                                                            | _                | 1             |                   | -               | R/W-0           | -     |

| ITRIM5       | ITRIM4                                                     | ITRIM3           | ITRIM2        | ITRIM1            | ITRIM0          | IRNG1           | IRNG0 |

| bit 7        |                                                            |                  |               |                   |                 |                 | bit 0 |

|              |                                                            |                  |               |                   |                 |                 |       |

| Legend:      |                                                            |                  |               |                   |                 |                 |       |

| R = Readal   | ble bit                                                    | W = Writable     | bit           | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR                                                     | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                                                            |                  |               |                   |                 |                 |       |

| bit 7-2      | ITRIM<5:0>:                                                | Current Source   | e Trim bits   |                   |                 |                 |       |

|              | 011111 <b>= M</b> a                                        | aximum positive  | e change from | nominal curren    | t               |                 |       |

|              | 011110                                                     |                  | C C           |                   |                 |                 |       |

|              | •                                                          |                  |               |                   |                 |                 |       |

|              | •                                                          |                  |               |                   |                 |                 |       |

|              | •<br>000001 = Minimum positive change from nominal current |                  |               |                   |                 |                 |       |

|              |                                                            |                  |               | d by IRNG<1:0>    |                 |                 |       |

|              |                                                            |                  |               | nominal curren    |                 |                 |       |

|              |                                                            | C C              | C             |                   |                 |                 |       |

|              |                                                            |                  |               |                   |                 |                 |       |

|              |                                                            |                  |               |                   |                 |                 |       |

|              | 100010                                                     |                  |               |                   | - 4             |                 |       |

|              |                                                            | •                | •             | n nominal currer  | าเ              |                 |       |

| bit 1-0      |                                                            | Current Source   | Range Select  | tbits             |                 |                 |       |

|              | 11 = 100 x Ba                                              |                  |               |                   |                 |                 |       |

|              | 10 = 10 x Bas                                              |                  |               |                   |                 |                 |       |

|              | 01 = Base Cl                                               | urrent Level (0. | oo μΑ nominal | )                 |                 |                 |       |

### REGISTER 27-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

00 = Current Source Disabled

## 27.8 Measuring Temperature with the CTMU Module

The CTMU, along with an internal diode, can be used to measure the temperature. The ADC can be connected to the internal diode and the CTMU module can source the current to the diode. The ADC reading will reflect the temperature. With the increase, the ADC readings will go low. This can be used for low-cost temperature measurement applications.

### EXAMPLE 27-5: ROUTINE FOR TEMPERATURE MEASUREMENT USING INTERNAL DIODE

| <pre>// Initialize CTMU CTMUICON = 0x03; CTMUCONHbits.CTMUEN = 1; CTMUCONLbits.EDG1STAT = 1;</pre> |                                                             |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| // Initialize ADC                                                                                  |                                                             |

| $ADCON0 = 0 \times E5;$                                                                            | // Enable ADC and connect to Internal diode                 |

| $ADCON1 = 0 \times 00;$                                                                            |                                                             |

| $ADCON2 = 0 \times BE;$                                                                            | // Right Justified                                          |

| ADCON0bits.GO = 1;                                                                                 | // Start conversion                                         |

| while(ADCON0bits.G0);                                                                              |                                                             |

| Temp = ADRES;                                                                                      | // Read ADC results (inversely proportional to temperature) |

|                                                                                                    |                                                             |

|                                                                                                    |                                                             |

Note: The temperature diode is not calibrated or standardized; the user must calibrate the diode to their application.

| CPFSGT                  | Compare f                    | with W, Skip                    | if f > W        | CPF         | SLT                  | Compare f                | with W, Skip                       | if f < W                           |

|-------------------------|------------------------------|---------------------------------|-----------------|-------------|----------------------|--------------------------|------------------------------------|------------------------------------|

| Syntax:                 | CPFSGT                       | f {,a}                          |                 | Synt        | ax:                  | CPFSLT                   | <sup>-</sup> {,a}                  |                                    |

| Operands:               | 0 ≤ f ≤ 255<br>a ∈ [0,1]     |                                 |                 | Oper        | ands:                | 0 ≤ f ≤ 255<br>a ∈ [0,1] |                                    |                                    |

| Operation:              | (f) - (W),                   |                                 |                 | Oner        | ation:               | (f) - (W),               |                                    |                                    |

|                         | skip if (f) ><br>(unsigned c | (W)<br>comparison)              |                 | oper        |                      | skip if (f) <            | (W)<br>comparison)                 |                                    |

| Status Affected:        | None                         |                                 |                 | Stati       | is Affected:         | None                     | empaneen)                          |                                    |

| Encoding:               | 0110                         | 010a ff:                        | ff ffff         |             |                      |                          | 000a ff:                           | ff ffff                            |

| Description:            |                              |                                 | f data memory   |             | oding:               | 0110                     |                                    |                                    |

|                         |                              | o the contents<br>an unsigned s |                 | Dest        | cription:            | location 'f' t           | o the contents of<br>an unsigned s | •                                  |

|                         |                              | -                               | eater than the  |             |                      |                          | nts of 'f' are le                  |                                    |

|                         |                              | WREG, then the s discarded and  |                 |             |                      |                          | W, then the fe                     |                                    |

|                         |                              | stead, making                   |                 |             |                      | executed in              | s discarded ar<br>stead, making    |                                    |

|                         | lf 'a' is 'o', t             | he Access Ba                    | nk is selected. |             |                      | two-cycle ir             | struction.                         |                                    |

|                         | GPR bank.                    |                                 | d to select the |             |                      |                          |                                    | nk is selected.<br>d to select the |

|                         |                              | nd the extend                   |                 | Word        | le.                  | 1                        |                                    |                                    |

|                         |                              | led, this instruc               | ction operates  | Cycle       |                      | 1(2)                     |                                    |                                    |

|                         | mode when                    | never f ≤ 95 (5                 | Fh). See        | Cyck        |                      | ( )                      | cles if skip an                    | d followed                         |

|                         |                              | .2.3 "Byte-Or<br>ed Instruction |                 |             |                      | by a                     | a 2-word instru                    | uction.                            |

|                         |                              | set Mode" for                   |                 | QC          | ycle Activity:       |                          |                                    |                                    |

| Words:                  | 1                            |                                 |                 |             | Q1                   | Q2                       | Q3                                 | Q4                                 |

| Cycles:                 | 1(2)                         |                                 |                 |             | Decode               | Read<br>register 'f'     | Process<br>Data                    | No<br>operation                    |

| -                       |                              | cycles if skip a                |                 | lf sk       | lip:                 | register i               | Dulu                               | operation                          |

|                         | by                           | a 2-word instr                  | uction.         |             | ,<br>Q1              | Q2                       | Q3                                 | Q4                                 |

| Q Cycle Activity:<br>Q1 | Q2                           | Q3                              | Q4              |             | No                   | No                       | No                                 | No                                 |

| Decode                  | Read                         | Process                         | No              |             | operation            | operation                | operation                          | operation                          |

|                         | register 'f'                 | Data                            | operation       | lf sk       | •                    | d by 2-word in           |                                    | <u>.</u>                           |

| If skip:                |                              |                                 |                 |             | Q1                   | Q2                       | Q3<br>No                           | Q4<br>No                           |

| Q1                      | Q2                           | Q3                              | Q4              |             | No<br>operation      | No<br>operation          | operation                          | operation                          |

| No<br>operation         | No<br>operation              | No<br>operation                 | No<br>operation |             | No                   | No                       | No                                 | No                                 |

| If skip and followe     |                              |                                 | opolation       |             | operation            | operation                | operation                          | operation                          |

| Q1                      | Q2                           | Q3                              | Q4              |             |                      |                          |                                    |                                    |

| No                      | No                           | No                              | No              | <u>Exar</u> | <u>nple:</u>         | HERE (                   | CPFSLT REG,                        | 1                                  |

| operation<br>No         | operation<br>No              | operation<br>No                 | operation<br>No |             |                      |                          | :                                  |                                    |

| operation               | operation                    | operation                       | operation       |             |                      |                          |                                    |                                    |

|                         |                              |                                 |                 |             | Before Instruc<br>PC |                          | dress (HERE                        | )                                  |

| Example:                | HERE                         | CPFSGT RE                       | IG, 0           |             | W                    | = ?                      |                                    | ,                                  |

|                         | NGREATER                     | :                               |                 |             | After Instruction    |                          |                                    |                                    |

| Poforo Instruc          | GREATER                      | :                               |                 |             | lf REG<br>PC         | < W;<br>= Ad             | dress (LESS                        | )                                  |

| Before Instruc<br>PC    |                              | dress (HERE                     | )               |             | If REG<br>PC         | ≥ W;                     |                                    |                                    |

| W                       | = ?                          |                                 |                 |             | ΓU                   | - Au                     | arcoo (NLES                        |                                    |

| After Instructio        |                              |                                 |                 |             |                      |                          |                                    |                                    |

| lf REG<br>PC            | > W;<br>= Ad                 | dress (GREA                     | TER)            |             |                      |                          |                                    |                                    |

| lf REG<br>PC            | ≤ W;                         |                                 |                 |             |                      |                          |                                    |                                    |

| FU                      | - Au                         | GIGGE (NGRE                     | гат цу /        |             |                      |                          |                                    |                                    |

### 29.2 Extended Instruction Set

In addition to the standard 75 instructions of the PIC18 instruction set, the PIC18F87K22 family of devices also provides an optional extension to the core CPU functionality. The added features include eight additional instructions that augment Indirect and Indexed Addressing operations and the implementation of Indexed Literal Offset Addressing for many of the standard PIC18 instructions.

The additional features of the extended instruction set are enabled by default on unprogrammed devices. Users must properly set or clear the XINST Configuration bit during programming to enable or disable these features.

The instructions in the extended set can all be classified as literal operations, which either manipulate the File Select Registers, or use them for Indexed Addressing. Two of the instructions, ADDFSR and SUBFSR, each have an additional special instantiation for using FSR2. These versions (ADDULNK and SUBULNK) allow for automatic return after execution.

The extended instructions are specifically implemented to optimize re-entrant program code (that is, code that is recursive or that uses a software stack) written in high-level languages, particularly C. Among other things, they allow users working in high-level languages to perform certain operations on data structures more efficiently. These include:

- Dynamic allocation and deallocation of software stack space when entering and leaving subroutines

- Function Pointer invocation

- Software Stack Pointer manipulation

- Manipulation of variables located in a software stack

A summary of the instructions in the extended instruction set is provided in Table 29-3. Detailed descriptions are provided in **Section 29.2.2 "Extended Instruction Set"**. The opcode field descriptions in Table 29-1 (page 432) apply to both the standard and extended PIC18 instruction sets.

Note: The instruction set extension and the Indexed Literal Offset Addressing mode were designed for optimizing applications written in C; the user may likely never use these instructions directly in assembler. The syntax for these commands is provided as a reference for users who may be reviewing code that has been generated by a compiler.

### 29.2.1 EXTENDED INSTRUCTION SYNTAX

Most of the extended instructions use indexed arguments, using one of the File Select Registers and some offset to specify a source or destination register. When an argument for an instruction serves as part of Indexed Addressing, it is enclosed in square brackets ("[]"). This is done to indicate that the argument is used as an index or offset. The MPASM<sup>™</sup> Assembler will flag an error if it determines that an index or offset value is not bracketed.

When the extended instruction set is enabled, brackets are also used to indicate index arguments in byte-oriented and bit-oriented instructions. This is in addition to other changes in their syntax. For more details, see Section 29.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands".

Note: In the past, square brackets have been used to denote optional arguments in the PIC18 and earlier instruction sets. In this text and going forward, optional arguments are denoted by braces ("{ }").

| Mnemo   | nic,                            | Description                              | Cycles | 16-E | Bit Instru | uction W | Vord | Status   |

|---------|---------------------------------|------------------------------------------|--------|------|------------|----------|------|----------|

| Operar  | nds                             | Description                              | Cycles | MSb  |            |          | LSb  | Affected |

| ADDFSR  | f, k                            | Add Literal to FSR                       | 1      | 1110 | 1000       | ffkk     | kkkk | None     |

| ADDULNK | k                               | Add Literal to FSR2 and Return           | 2      | 1110 | 1000       | 11kk     | kkkk | None     |

| CALLW   |                                 | Call Subroutine using WREG               | 2      | 0000 | 0000       | 0001     | 0100 | None     |

| MOVSF   | z <sub>s</sub> , f <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | 0zzz     | ZZZZ | None     |

|         |                                 | f <sub>d</sub> (destination) 2nd word    |        | 1111 | ffff       | ffff     | ffff |          |

| MOVSS   | z <sub>s</sub> , z <sub>d</sub> | Move z <sub>s</sub> (source) to 1st word | 2      | 1110 | 1011       | lzzz     | zzzz | None     |

|         |                                 | z <sub>d</sub> (destination) 2nd word    |        | 1111 | xxxx       | XZZZ     | ZZZZ |          |

| PUSHL   | k                               | Store Literal at FSR2,                   | 1      | 1110 | 1010       | kkkk     | kkkk | None     |

|         |                                 | Decrement FSR2                           |        |      |            |          |      |          |

| SUBFSR  | f, k                            | Subtract Literal from FSR                | 1      | 1110 | 1001       | ffkk     | kkkk | None     |

| SUBULNK | k                               | Subtract Literal from FSR2 and           | 2      | 1110 | 1001       | 11kk     | kkkk | None     |

|         |                                 | return                                   |        |      |            |          |      |          |

### TABLE 29-3: EXTENSIONS TO THE PIC18 INSTRUCTION SET

### 30.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 30.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 30.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 30.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

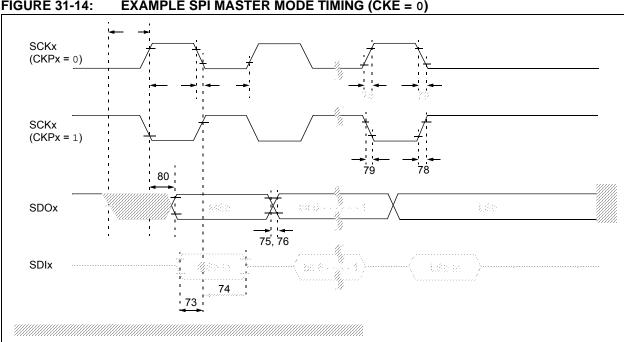

| TABLE 31-17: | EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0) |

|--------------|------------------------------------------------------|

|--------------|------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic                                            | Min          | Max | Units | Conditions |

|--------------|-----------------------|-----------------------------------------------------------|--------------|-----|-------|------------|

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                | 20           | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2 | 1.5 Tcy + 40 | —   | ns    |            |

| 74           | TscH2dlL,<br>TscL2dlL | Hold Time of SDIx Data Input to SCKx Edge                 | 40           | —   | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                                | —            | 25  | ns    |            |

| 76           | TDOF                  | SDOx Data Output Fall Time                                | —            | 25  | ns    |            |