Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k22t-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                 | Pin Number      | Pin Buffer           | Deceriation           |                                                                                                                             |

|------------------------------------------------------------------------------------------|-----------------|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                 | QFN/TQFP        | Туре                 | Туре                  | Description                                                                                                                 |

|                                                                                          |                 |                      |                       | PORTE is a bidirectional I/O port.                                                                                          |

| RE0/RD/P2D<br>RE0<br>RD<br>P2D                                                           | 2               | I/O<br> <br>0        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port read strobe.<br>EECP2 PWM Output D.                                                     |

| RE1/WR/P2C<br>RE1<br>WR<br>P2C                                                           | 1               | I/O<br>I<br>O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port write strobe.<br>ECCP2 PWM Output C.                                                    |

| RE2/ <u>CS</u> /P2B/CCP10<br>RE2<br>CS<br>P2B<br>CCP10 <sup>(3)</sup>                    | 64              | I/O<br> <br>0<br> /O | ST<br>TTL<br>—<br>S/T | Digital I/O.<br>Parallel Slave Port chip select.<br>ECCP2 PWM Output B.<br>Capture 10 input/Compare 10 output/PWM10 output. |

| RE3/P3C/CCP9/REFO<br>RE3<br>P3C<br>CCP9 <sup>(3,4)</sup><br>REFO                         | 63              | I/O<br>O<br>I/O<br>O | ST<br><br>S/T<br>     | Digital I/O.<br>ECCP3 PWM Output C.<br>Capture 9 input/Compare 9 output/PWM9 output.<br>Reference clock out.                |

| RE4/P3B/CCP8<br>RE4<br>P3B<br>CCP8 <sup>(4)</sup>                                        | 62              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP3 PWM Output B.<br>Capture 8 input/Compare 8 output/PWM8 output.                                        |

| RE5/P1C/CCP7<br>RE5<br>P1C<br>CCP7 <sup>(4)</sup>                                        | 61              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP1 PWM Output C.<br>Capture 7 input/Compare 7 output/PWM7 output.                                        |

| RE6/P1B/CCP6<br>RE6<br>P1B<br>CCP6 <sup>(4</sup>                                         | 60              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP1 PWM Output B.<br>Capture 6 input/Compare 6 output/PWM6 output.                                        |

| RE7/ECCP2/P2A<br>RE7<br>ECCP2 <sup>(2)</sup><br>P2A                                      | 59              | I/O<br>I/O<br>O      | ST<br>ST<br>—         | Digital I/O.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>ECCP2 PWM Output A.                                        |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input<br>P = Power<br>$I^2C = I^2C^{TM}/SI$ | Trigger input w | rith CN              | IOS levels            | CMOS= CMOS compatible input or outputAnalog= Analog inputO= OutputOD= Open-Drain (no P diode to VDD)                        |

#### TABLE 1-3: PIC18F6XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

**2:** Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

## **REGISTER 3-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 2 **HFIOFS:** INTOSC Frequency Stable bit

- 1 = HF-INTOSC oscillator frequency is stable

- 0 = HF-INTOSC oscillator frequency is not stable

- bit 1-0 SCS<1:0>: System Clock Select bits<sup>(4)</sup>

- 1x = Internal oscillator block (LF-INTOSC, MF-INTOSC or HF-INTOSC)

- 01 = SOSC oscillator

- 00 = Default primary oscillator (OSC1/OSC2 or HF-INTOSC with or without PLL; defined by the FOSC<3:0> Configuration bits, CONFIG1H<3:0>.)

- Note 1: The Reset state depends on the state of the IESO Configuration bit (CONFIG1H<7>).

- 2: Modifying these bits will cause an immediate clock frequency switch if the internal oscillator is providing the device clocks.

- 3: Source selected by the INTSRC bit (OSCTUNE<7>).

- 4: Modifying these bits will cause an immediate clock source switch.

- **5:** INTSRC = OSCTUNE<7> and MFIOSEL = OSCCON2<0>.

- 6: Lowest power option for an internal source.

### REGISTER 3-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-0     | U-0 | U-0 | R/W-0  | U-0 | R-x    | R/W-0   |

|-------|---------|-----|-----|--------|-----|--------|---------|

| —     | SOSCRUN | _   | —   | SOSCGO | —   | MFIOFS | MFIOSEL |

| bit 7 |         |     |     |        |     |        | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | SOSCRUN: SOSC Run Status bit                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = System clock comes from a secondary SOSC</li> <li>0 = System clock comes from an oscillator other than SOSC</li> </ul>                                                                                                                                                         |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                  |

| bit 3   | SOSCGO: Oscillator Start Control bit                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Oscillator is running, even if no other sources are requesting it</li> <li>0 = Oscillator is shut off if no other sources are requesting it (When the SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.)</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                  |

| bit 1   | MFIOFS: MF-INTOSC Frequency Stable bit                                                                                                                                                                                                                                                      |

|         | 1 = MF-INTOSC is stable<br>0 = MF-INTOSC is not stable                                                                                                                                                                                                                                      |

| bit 0   | MFIOSEL: MF-INTOSC Select bit                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = MF-INTOSC is used in place of HF-INTOSC frequencies of 500 kHz, 250 kHz and 31.25 kHz</li> <li>0 = MF-INTOSC is not used</li> </ul>                                                                                                                                            |

#### R/W-0 R/W-1 R/W-1 R/W-1 R-1 R-1 R/W-0 R/W-0 CM RI TO PD POR **IPEN** SBOREN BOR bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 IPEN: Interrupt Priority Enable bit 1 = Enable priority levels on interrupts 0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) bit 6 SBOREN: BOR Software Enable bit If BOREN<1:0> = 01: 1 = BOR is enabled 0 = BOR is disabled If BOREN<1:0> = 00. 10 or 11: Bit is disabled and read as '0'. CM: Configuration Mismatch Flag bit bit 5 1 = A Configuration Mismatch Reset has not occurred 0 = A Configuration Mismatch Reset has occurred (must be set in software after a Configuration Mismatch Reset occurs) bit 4 RI: RESET Instruction Flag bit 1 = The RESET instruction was not executed (set by firmware only) 0 = The RESET instruction was executed causing a device Reset (must be set in software after a Brown-out Reset occurs) bit 3 TO: Watchdog Time-out Flag bit 1 = Set by power-up, CLRWDT instruction or SLEEP instruction 0 = A WDT time-out occurred bit 2 PD: Power-Down Detection Flag bit 1 = Set by power-up or by the CLRWDT instruction 0 = Set by execution of the SLEEP instruction POR: Power-on Reset Status bit bit 1 1 = A Power-on Reset has not occurred (set by firmware only) 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) bit 0 BOR: Brown-out Reset Status bit 1 = A Brown-out Reset has not occurred (set by firmware only) 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

#### REGISTER 5-1: RCON: RESET CONTROL REGISTER

**Note 1:** It is recommended that the POR bit be set after a Power-on Reset has been detected, so that subsequent Power-on Resets may be detected.

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after a Power-on Reset).

| TABLE 5-2: |                            |                            |                                    | GISTERS (CONTINU<br>MCLR Resets,                               |                                 |  |

|------------|----------------------------|----------------------------|------------------------------------|----------------------------------------------------------------|---------------------------------|--|

| Register   | Applicable Devices         |                            | Power-on Reset,<br>Brown-out Reset | WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| ECCP1AS    | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| ECCP1DEL   | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CCPR1H     | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCPR1L     | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | uuuu uuuu                                                      | uuuu uuuu                       |  |

| CCP1CON    | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| PIR5       | PIC18F65K22                | PIC18F85K22                | 0 -000                             | 0 -000                                                         | u -uuu                          |  |

| PIR5       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| PIE5       | PIC18F65K22                | PIC18F85K22                | 0 0000                             | 0 0000                                                         | u uuuu <b>(1)</b>               |  |

| PIE5       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 000                           | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| IPR4       | PIC18F65K22                | PIC18F85K22                | 11 1111                            | 11 1111                                                        | uu uuuu                         |  |

| IPR4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 1111 1111                          | 1111 1111                                                      | uuuu uuuu                       |  |

| PIR4       | PIC18F65K22                | PIC18F85K22                | 00 0000                            | 00 0000                                                        | uu uuuu <b>(1)</b>              |  |

| PIR4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu <b>(1)</b>            |  |

| PIE4       | PIC18F65K22                | PIC18F85K22                | 00 0000                            | 00 0000                                                        | uu uuuu                         |  |

| PIE4       | PIC18F66K22<br>PIC18F67K22 | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CVRCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| CMSTAT     | PIC18F6XK22                | PIC18F8XK22                | xxx                                | xxx                                                            | uuu                             |  |

| TMR3H      | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx                          | սսսս սսսս                                                      | սսսս սսսս                       |  |

| TMR3L      | PIC18F6XK22                | PIC18F8XK22                | xxxx xxxx                          | սսսս սսսս                                                      | սսսս սսսս                       |  |

| T3CON      | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 00x0 0x00                                                      | սսսս սսսս                       |  |

| T3GCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00                          | 0000 0000                                                      | սսսս սսսս                       |  |

| SPBRG1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                       |  |

| RCREG1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                      | սսսս սսսս                       |  |

| TXREG1     | PIC18F6XK22                | PIC18F8XK22                | XXXX XXXX                          | xxxx xxxx                                                      | սսսս սսսս                       |  |

| TXSTA1     | PIC18F6XK22                | PIC18F8XK22                | 0000 0010                          | 0000 0010                                                      | սսսս սսսս                       |  |

| RCSTA1     | PIC18F6XK22                | PIC18F8XK22                | 0000 000x                          | 0000 000x                                                      | սսսս սսսս                       |  |

| T1GCON     | PIC18F6XK22                | PIC18F8XK22                | 0000 0x00                          | 00x0 0x00                                                      | uuuu -uuu                       |  |

| IPR6       | PIC18F6XK22                | PIC18F8XK22                | 1 -111                             | 1 -111                                                         | u -uuu                          |  |

| HLVDCON    | PIC18F6XK22                | PIC18F8XK22                | 0000 0101                          | 0000 0101                                                      | uuuu uuuu                       |  |

| PSPCON     | PIC18F6XK22                | PIC18F8XK22                | 0000                               | 0000                                                           | uuuu                            |  |

| PIR6       | PIC18F6XK22                | PIC18F8XK22                | 0 -000                             | 0 -000                                                         | u -uuu                          |  |

### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt, and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

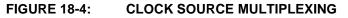

#### 18.2.2 CLOCK SOURCE

As previously mentioned, the RTCC module is intended to be clocked by an external Real-Time Clock (RTC) crystal, oscillating at 32.768 kHz, but an internal oscillator can be used. The RTCC clock selection is decided by the RTCOSC bit (CONFIG3L<0>).

Calibration of the crystal can be done through this module to yield an error of 3 seconds or less per month. (For further details, see **Section 18.2.9 "Calibration"**.)

#### 18.2.2.1 Real-Time Clock Enable

The RTCC module can be clocked by an external, 32.768 kHz crystal (SOSC oscillator) or the LF-INTOSC oscillator, which can be selected in CONFIG3L<0>.

If the external clock is used, the SOSC oscillator should be enabled. If LF-INTOSC is providing the clock, the INTOSC clock can be brought out to the RTCC pin by the RTSECSEL<1:0> bits (PADCFG<2:1>).

#### 18.2.3 DIGIT CARRY RULES

This section explains which timer values are affected when there is a rollover:

- Time of Day: From 23:59:59 to 00:00:00 with a carry to the Day field

- Month: From 12/31 to 01/01 with a carry to the Year field

- Day of Week: From 6 to 0 with no carry (see Table 18-1)

- Year Carry: From 99 to 00; this also surpasses the use of the RTCC

For the day-to-month rollover schedule, see Table 18-2.

Because the following values are in BCD format, the carry to the upper BCD digit occurs at the count of 10, not 16 (SECONDS, MINUTES, HOURS, WEEKDAY, DAYS and MONTHS).

#### TABLE 18-1: DAY OF WEEK SCHEDULE

| Day of Week |   |  |  |  |  |  |

|-------------|---|--|--|--|--|--|

| Sunday      | 0 |  |  |  |  |  |

| Monday      | 1 |  |  |  |  |  |

| Tuesday     | 2 |  |  |  |  |  |

| Wednesday   | 3 |  |  |  |  |  |

| Thursday    | 4 |  |  |  |  |  |

| Friday      | 5 |  |  |  |  |  |

| Saturday    | 6 |  |  |  |  |  |

## TABLE 18-2:DAY TO MONTH ROLLOVER<br/>SCHEDULE

| Maximum Day Field       |

|-------------------------|

| 31                      |

| 28 or 29 <sup>(1)</sup> |

| 31                      |

| 30                      |

| 31                      |

| 30                      |

| 31                      |

| 31                      |

| 30                      |

| 31                      |

| 30                      |

| 31                      |

|                         |

Note 1: See Section 18.2.4 "Leap Year".

### 20.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F87K22 family devices have three Enhanced Capture/Compare/PWM (ECCP) modules: ECCP1, ECCP2 and ECCP3. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upward compatible with CCP.

**Note:** Throughout this section, generic references are used for register and bit names that are the same, except for an 'x' variable that indicates the item's association with the ECCP1, ECCP2 or ECCP3 module. For example, the control register is named CCPxCON and refers to CCP1CON, CCP2CON and CCP3CON.

ECCP1, ECCP2 and ECCP3 are implemented as standard CCP modules with Enhanced PWM capabilities. These include:

- Provision for two or four output channels

- · Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- · Automatic shutdown and restart

The enhanced features are discussed in detail in Section 20.4 "PWM (Enhanced Mode)".

The ECCP1, ECCP2 and ECCP3 modules use the control registers: CCP1CON, CCP2CON and CCP3CON. The control registers, CCP4CON through CCP10CON, are for the modules, CCP4 through CCP10.

## REGISTER 20-5: PSTRxCON: PULSE STEERING CONTROL<sup>(1)</sup>

| bit 7 |       |     |         |       |       |       | bit 0 |

|-------|-------|-----|---------|-------|-------|-------|-------|

| CMPL1 | CMPL0 | —   | STRSYNC | STRD  | STRC  | STRB  | STRA  |

| R/W-0 | R/W-0 | U-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

| CMPL<1:0>: Complementary Mode Output Assignment Steering Sync bits                          |

|---------------------------------------------------------------------------------------------|

| 00 = See STR <d:a></d:a>                                                                    |

| 01 = PA and PB are selected as the complementary output pair                                |

| 10 = PA and PC are selected as the complementary output pair                                |

| 11 = PA and PD are selected as the complementary output pair                                |

| Unimplemented: Read as '0'                                                                  |

| STRSYNC: Steering Sync bit                                                                  |

| 1 = Output steering update occurs on the next PWM period                                    |

| 0 = Output steering update occurs at the beginning of the instruction cycle boundary        |

| STRD: Steering Enable bit D                                                                 |

| 1 = PxD pin has the PWM waveform with polarity control from CCPxM<1:0>                      |

| 0 = PxD pin is assigned to the port pin                                                     |

| STRC: Steering Enable bit C                                                                 |

| 1 = PxC pin has the PWM waveform with polarity control from CCPxM<1:0>                      |

| 0 = PxC pin is assigned to the port pin                                                     |

| STRB: Steering Enable bit B                                                                 |

| 1 = PxB pin has the PWM waveform with polarity control from CCPxM<1:0>                      |

| 0 = PxB pin is assigned to the port pin                                                     |

| STRA: Steering Enable bit A                                                                 |

| 1 = PxA pin has the PWM waveform with polarity control from CCPxM<1:0>                      |

| 0 = PxA pin is assigned to the port pin                                                     |

| The PWM Steering mode is available only when the CCPxCON register bits, CCPxM<3:2> = 11 and |

|                                                                                             |

PxM<1:0> = 00.

## REGISTER 21-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0      | R/W-0                                 | R/W-0                                 | R/W-0          | R/W-0                | R/W-0                                   | R/W-0                | R/W-0                |

|------------|---------------------------------------|---------------------------------------|----------------|----------------------|-----------------------------------------|----------------------|----------------------|

| WCOL       | SSPOV                                 | SSPEN <sup>(1)</sup>                  | CKP            | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>                    | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7      |                                       |                                       |                |                      |                                         |                      | bit (                |

| Legend:    |                                       |                                       |                |                      |                                         |                      |                      |

| R = Reada  | able bit                              | W = Writable b                        | it             | U = Unimple          | mented bit, rea                         | id as '0'            |                      |

| -n = Value |                                       | '1' = Bit is set                      | it.            | '0' = Bit is cl      |                                         | x = Bit is unk       | nown                 |

|            |                                       |                                       |                |                      | carca                                   |                      |                      |

| bit 7      | WCOL: Write                           | e Collision Detect                    | bit            |                      |                                         |                      |                      |

|            |                                       | ansmit mode:                          |                |                      | _                                       |                      |                      |

|            |                                       | to the SSPxBUF                        |                |                      |                                         | onditions were       | not valid for a      |

|            |                                       | sion to be started                    | d (must be cl  | eared in softwa      | are)                                    |                      |                      |

|            | 0 = No collis                         |                                       |                |                      |                                         |                      |                      |

|            | In Slave Trar                         | PxBUF register is                     | written while  | a it is still trans  | mitting the prev                        | vious word (mus      | st he cleared in     |

|            | software                              | -                                     | WHILE IT WHILE |                      |                                         |                      |                      |

|            | 0 = No collis                         | sion                                  |                |                      |                                         |                      |                      |

|            | <u>In Receive m</u><br>This is a "doi | node (Master or S                     | lave modes)    | <u>:</u>             |                                         |                      |                      |

| bit 6      |                                       | ceive Overflow Inc                    | dicator bit    |                      |                                         |                      |                      |

|            | In Receive m                          |                                       |                |                      |                                         |                      |                      |

|            |                                       | s received while th                   | ne SSPxBUF     | register is still    | holding the pre                         | vious byte (mu       | st be cleared i      |

|            | software                              | /                                     |                |                      |                                         |                      |                      |

|            | 0 = No over                           |                                       |                |                      |                                         |                      |                      |

|            | <u>In Transmit r</u><br>This is a "do | <u>node:</u><br>n't care" bit in Tra  | nsmit mode     |                      |                                         |                      |                      |

| bit 5      |                                       | ster Synchronous                      |                |                      |                                         |                      |                      |

|            |                                       | the serial port and                   |                |                      | SCLx pins as t                          | he serial port p     | ins                  |

|            |                                       | serial port and co                    |                |                      |                                         |                      |                      |

| bit 4      | CKP: SCKx                             | Release Control I                     | bit            |                      |                                         |                      |                      |

|            | In Slave mod                          | <u>le:</u>                            |                |                      |                                         |                      |                      |

|            | 1 = Releases                          |                                       |                |                      |                                         |                      |                      |

|            |                                       | ock low (clock stre                   | etch), used to | o ensure data s      | setup time                              |                      |                      |

|            | In Master mo<br>Unused in th          |                                       |                |                      |                                         |                      |                      |

| bit 3-0    | SSPM<3:0>                             | Master Synchro                        | nous Serial I  | Port Mode Sele       | ect bits <sup>(2)</sup>                 |                      |                      |

|            | 1111 = I <sup>2</sup> C S             | Slave mode: 10-b                      | it address wi  | th Start and St      | op bit interrupts                       | enabled              |                      |

|            | $1110 = I^2 C S$                      | Slave mode: 7-bit                     | address with   | n Start and Sto      | p bit interrupts                        |                      |                      |

|            |                                       | Firmware Controll                     |                |                      |                                         |                      |                      |

|            |                                       | I SSPMSK registe<br>Master mode: cloo |                |                      |                                         |                      |                      |

|            |                                       | Slave mode: 10-b                      |                |                      | • • • • • • • • • • • • • • • • • • • • |                      |                      |

|            |                                       | Slave mode: 7-bit                     |                |                      |                                         |                      |                      |

| Note 1:    | When enabled. t                       | he SDAx and SC                        | Lx pins must   | be confiaured        | as inputs.                              |                      |                      |

| 2:         |                                       | not specifically li                   | -              | -                    | -                                       | ited in SPI mod      | e only.              |

|            | When SSPM<3:                          | • •                                   |                |                      | •                                       |                      | •                    |

|            | SSPxMSK regist                        |                                       |                |                      |                                         | ,,                   |                      |

| 4:         | This mode is onl                      | y available when                      | 7-Bit Addres   | s Masking mo         | de is selected (                        | MSSPMSK Co           | nfiguration bit      |

|            | is '1').                              |                                       |                |                      |                                         |                      |                      |

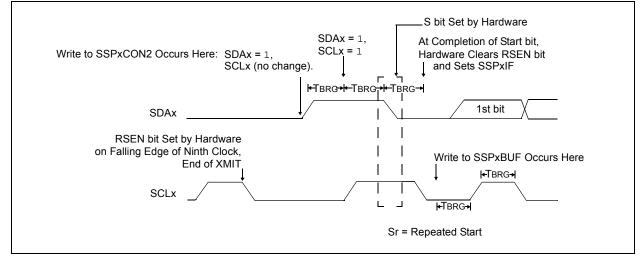

### 21.4.9 I<sup>2</sup>C<sup>™</sup> MASTER MODE REPEATED START CONDITION TIMING

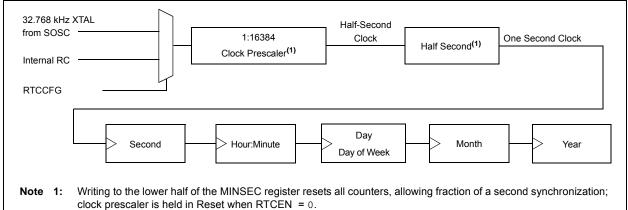

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, and if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 21.4.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 21-22: REPEATED START CONDITION WAVEFORM

### 24.6 Comparator Interrupts

The comparator interrupt flag is set whenever any of the following occurs:

- · Low-to-high transition of the comparator output

- High-to-low transition of the comparator output

- Any change in the comparator output

The comparator interrupt selection is done by the EVPOL<1:0> bits in the CMxCON register (CMxCON<4:3>).

In order to provide maximum flexibility, the output of the comparator may be inverted using the CPOL bit in the CMxCON register (CMxCON<5>). This is functionally identical to reversing the inverting and non-inverting inputs of the comparator for a particular mode.

An interrupt is generated on the low-to-high or high-tolow transition of the comparator output. This mode of interrupt generation is dependent on EVPOL<1:0> in the CMxCON register. When EVPOL<1:0> = 01 or 10, the interrupt is generated on a low-to-high or high-tolow transition of the comparator output. Once the interrupt is generated, it is required to clear the interrupt flag by software. When EVPOL<1:0> = 11, the comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMSTAT<7:5>, to determine the actual change that occurred.

The CMPxIF bits (PIR6<2:0>) are the Comparator Interrupt Flags. The CMPxIF bits must be reset by clearing them. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated. Table 24-2 shows the interrupt generation with respect to comparator input voltages and EVPOL bit settings.

Both the CMPxIE bits (PIE6<2:0>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMPxIF bits will still be set if an interrupt condition occurs.

A simplified diagram of the interrupt section is shown in Figure 24-3.

Note: The CMPxIF bits will not be set when EVPOL<1:0> = 00.

| CPOL | EVPOL<1:0> | Comparator<br>Input Change | CxOUT Transition | Interrupt<br>Generated |

|------|------------|----------------------------|------------------|------------------------|

|      | 0.0        | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 00         | VIN+ < VIN-                | High-to-Low      | No                     |

|      | 0.1        | VIN+ > VIN-                | Low-to-High      | Yes                    |

| 0    | 01         | VIN+ < VIN-                | High-to-Low      | No                     |

| 0    | 1.0        | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 10         | Vin+ < Vin-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ > VIN-                | Low-to-High      | Yes                    |

|      |            | VIN+ < VIN-                | High-to-Low      | Yes                    |

|      | 00         | VIN+ > VIN-                | High-to-Low      | No                     |

|      | 00         | Vin+ < Vin-                | Low-to-High      | No                     |

|      | 01         | VIN+ > VIN-                | High-to-Low      | No                     |

| 1    |            | Vin+ < Vin-                | Low-to-High      | Yes                    |

|      |            | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 10         | VIN+ < VIN-                | Low-to-High      | No                     |

|      | 11         | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ < VIN-                | Low-to-High      | Yes                    |

TABLE 24-2:

COMPARATOR INTERRUPT GENERATION

NOTES:

#### EXAMPLE 27-2: CURRENT CALIBRATION ROUTINE

```

#include "pl8cxxx.h"

#define COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

int main(void)

{

int i;

int j = 0; //index for loop

unsigned int Vread = 0;

double VTot = 0;

float Vavg=0, Vcal=0, CTMUISrc = 0; //float values stored for calcs

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

for(j=0;j<10;j++)</pre>

{

//drain charge on the circuit

CTMUCONHbits.IDISSEN = 1;

DELAY;

//wait 125us

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

//wait for 125us

DELAY;

//Stop charging circuit

CTMUCONLbits.EDG1STAT = 0;

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

```

| CPFSGT                  | Compare f                      | with W, Skip                    | if f > W                         | CPF         | SLT                  | Compare f                                  | with W, Skip                    | if f < W        |  |

|-------------------------|--------------------------------|---------------------------------|----------------------------------|-------------|----------------------|--------------------------------------------|---------------------------------|-----------------|--|

| Syntax:                 | CPFSGT                         | f {,a}                          |                                  | Synt        | ax:                  | CPFSLT                                     | {,a}                            |                 |  |

| Operands:               | 0 ≤ f ≤ 255<br>a ∈ [0,1]       |                                 |                                  | Oper        | rands:               | 0 ≤ f ≤ 255<br>a ∈ [0,1]                   |                                 |                 |  |

| Operation:              | (f) - (W),                     |                                 |                                  | Oper        | ration:              | (f) - (W),                                 |                                 |                 |  |

|                         | skip if (f) > (<br>(unsigned c | (W)<br>comparison)              |                                  | oper        |                      | skip if (f) < (W)<br>(unsigned comparison) |                                 |                 |  |

| Status Affected:        | None                           |                                 |                                  | Stati       | us Affected:         | None                                       | ienipalieeni)                   |                 |  |

| Encoding:               | 0110                           | 010a ff                         | ff ffff                          |             |                      |                                            | 000a ff:                        | ff ffff         |  |

| Description:            |                                |                                 | f data memory                    |             | oding:               | 0110                                       |                                 |                 |  |

|                         |                                | o the contents<br>an unsigned s |                                  | Desc        | cription:            | location 'f' t                             | o the contents of an unsigned s | •               |  |

|                         |                                | -                               | eater than the                   |             |                      |                                            | nts of 'f' are le               |                 |  |

|                         | instruction i                  | WREG, then a discarded a        | nd a NOP is                      |             |                      | contents of                                | W, then the fe                  | etched          |  |

|                         | executed in two-cycle in       | stead, making<br>struction.     | g this a                         |             |                      |                                            | stead, making                   |                 |  |

|                         |                                |                                 | nk is selected.                  |             |                      | -                                          |                                 | nk is selected. |  |

|                         | GPR bank.                      |                                 | d to select the                  |             |                      |                                            |                                 | d to select the |  |

|                         |                                | nd the extend                   | ed instruction<br>ction operates | Word        | ds:                  | 1                                          |                                 |                 |  |

|                         |                                | Literal Offset A                | •                                | Cycle       | es:                  | 1(2)                                       |                                 |                 |  |

|                         |                                | ever f ≤ 95 (5                  |                                  | ,           |                      | Note: 3 cy                                 | cles if skip an                 |                 |  |

|                         |                                | .2.3 "Byte-Or<br>d Instruction  |                                  |             |                      | by a                                       | a 2-word instru                 | iction.         |  |

|                         |                                | set Mode" for                   |                                  | QC          | ycle Activity:       |                                            |                                 |                 |  |

| Words:                  | 1                              |                                 |                                  |             | Q1                   | Q2                                         | Q3                              | Q4              |  |

| Cycles:                 | 1(2)                           |                                 |                                  |             | Decode               | Read<br>register 'f'                       | Process<br>Data                 | No<br>operation |  |

|                         |                                | ycles if skip a                 |                                  | lf sk       | kip:                 |                                            |                                 |                 |  |

|                         | by                             | a 2-word instr                  | uction.                          |             | Q1                   | Q2                                         | Q3                              | Q4              |  |

| Q Cycle Activity:<br>Q1 | Q2                             | Q3                              | Q4                               |             | No                   | No                                         | No                              | No              |  |

| Decode                  | Read                           | Process                         | No                               |             | operation            | operation                                  | operation                       | operation       |  |

|                         | register 'f'                   | Data                            | operation                        | lt sk       | •                    | d by 2-word in                             |                                 | 04              |  |

| If skip:                | 00                             | 00                              | 04                               |             | Q1<br>No             | Q2<br>No                                   | Q3<br>No                        | Q4<br>No        |  |

| Q1<br>No                | Q2<br>No                       | Q3<br>No                        | Q4<br>No                         |             | operation            | operation                                  | operation                       | operation       |  |

| operation               | operation                      | operation                       | operation                        |             | No                   | No                                         | No                              | No              |  |

| If skip and followe     |                                |                                 | <u> </u>                         |             | operation            | operation                                  | operation                       | operation       |  |

| Q1                      | Q2                             | Q3                              | Q4                               |             |                      |                                            |                                 |                 |  |

| No                      | No                             | No                              | No                               | <u>Exar</u> | <u>nple:</u>         |                                            | CPFSLT REG,                     | 1               |  |

| operation<br>No         | operation<br>No                | operation<br>No                 | operation<br>No                  |             |                      |                                            | :                               |                 |  |

| operation               | operation                      | operation                       | operation                        |             | Defene la star       |                                            | •                               |                 |  |

|                         |                                |                                 |                                  |             | Before Instruc<br>PC |                                            | dress (HERE                     | )               |  |

| Example:                | HERE                           | CPFSGT RE                       | EG, 0                            |             | W                    | = ?                                        |                                 | ,               |  |

|                         | NGREATER                       | :                               |                                  |             | After Instruction    |                                            |                                 |                 |  |

| Defere lastrus          | GREATER                        | :                               |                                  |             | lf REG<br>PC         | < W;<br>= Ad                               | dress (LESS                     | )               |  |

| Before Instruc<br>PC    |                                | dress (HERE                     | )                                |             | If REG               | ≥ W;                                       |                                 |                 |  |

| W                       | = ?                            |                                 | ,                                |             | PC                   | = A0                                       | dress (NLES                     | 5)              |  |

| After Instructio        |                                |                                 |                                  |             |                      |                                            |                                 |                 |  |

| lf REG<br>PC            | > W;<br>= Ad                   | dress (GREA                     | TER)                             |             |                      |                                            |                                 |                 |  |

| lf REG<br>PC            | ≤ W;                           |                                 |                                  |             |                      |                                            |                                 |                 |  |

| PC                      | - Ad                           | dress (NGRE                     | AILK /                           |             |                      |                                            |                                 |                 |  |

### 30.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 30.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 30.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 30.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 31.5 AC (Timing) Characteristics

#### 31.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                                |                            | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|--------------------------------------------|----------------------------|-----------|----------------------------------------|

| 2. TppS                                    |                            | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                                          |                            |           |                                        |

| F                                          | Frequency                  | Т         | Time                                   |

| Lowercase letters (pp) and their meanings: |                            |           |                                        |

| рр                                         |                            |           |                                        |

| сс                                         | CCP1                       | osc       | OSC1                                   |

| ck                                         | CLKO                       | rd        | RD                                     |

| cs                                         | CS                         | rw        | RD or WR                               |

| di                                         | SDI                        | sc        | SCK                                    |

| do                                         | SDO                        | SS        | SS                                     |

| dt                                         | Data in                    | tO        | TOCKI                                  |

| io                                         | I/O port                   | t1        | T1CKI                                  |

| mc                                         | MCLR                       | wr        | WR                                     |

| Uppercase l                                | etters and their meanings: |           |                                        |

| S                                          |                            |           |                                        |

| F                                          | Fall                       | Р         | Period                                 |

| н                                          | High                       | R         | Rise                                   |

| I                                          | Invalid (High-impedance)   | V         | Valid                                  |

| L                                          | Low                        | Z         | High-impedance                         |

| I <sup>2</sup> C only                      |                            |           |                                        |

| AA                                         | output access              | High      | High                                   |

| BUF                                        | Bus free                   | Low       | Low                                    |

| Tcc:st (I <sup>2</sup> C :                 | specifications only)       |           |                                        |

| CC                                         |                            |           |                                        |

| HD                                         | Hold                       | SU        | Setup                                  |

| ST                                         |                            |           |                                        |

| DAT                                        | DATA input hold            | STO       | Stop condition                         |

| STA                                        | Start condition            |           |                                        |

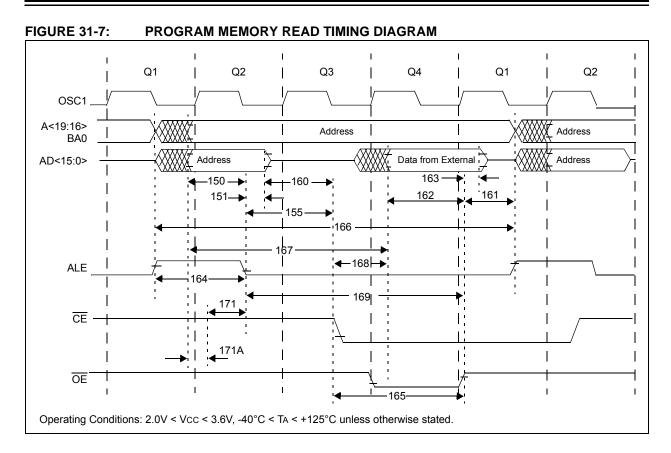

| Param.<br>No | Symbol   | Characteristics                                                           | Min            | Тур       | Мах            | Units |

|--------------|----------|---------------------------------------------------------------------------|----------------|-----------|----------------|-------|

| 150          | TadV2alL | Address Out Valid to ALE $\downarrow$ (address setup time)                | 0.25 TCY – 10  | _         | _              | ns    |

| 151          | TalL2adl | ALE $\downarrow$ to Address Out Invalid (address hold time)               | 5              | _         | —              | ns    |

| 155          | TalL2oeL | ALE $\downarrow$ to $\overline{OE} \downarrow$                            | 10             | 0.125 TCY | —              | ns    |

| 160          | TadZ2oeL | AD High-Z to $\overline{OE} \downarrow$ (bus release to $\overline{OE}$ ) | 0              |           | —              | ns    |

| 161          | ToeH2adD | OE ↑ to AD Driven                                                         | 0.125 Tcy – 5  |           | _              | ns    |

| 162          | TadV2oeH | LS Data Valid before $\overline{OE}$ $\uparrow$ (data setup time)         | 20             | _         | —              | ns    |

| 163          | ToeH2adl | OE ↑ to Data In Invalid (data hold time)                                  | 0              | _         | —              | ns    |

| 164          | TalH2alL | ALE Pulse Width                                                           | —              | 0.25 TCY  | —              | ns    |

| 165          | ToeL2oeH | OE Pulse Width                                                            | 0.5 Tcy – 5    | 0.5 TCY   | _              | ns    |

| 166          | TalH2alH | ALE $\uparrow$ to ALE $\uparrow$ (cycle time)                             | —              | Тсү       | —              | ns    |

| 167          | Tacc     | Address Valid to Data Valid                                               | 0.75 Tcy – 25  |           | —              | ns    |

| 168          | Тое      | $\overline{OE}\downarrow$ to Data Valid                                   |                |           | 0.5 TCY – 25   | ns    |

| 169          | TalL2oeH | ALE ↓ to OE ↑                                                             | 0.625 Tcy – 10 | _         | 0.625 Tcy + 10 | ns    |

| 171          | TalH2csL | Chip Enable Active to ALE $\downarrow$                                    | 0.25 Tcy – 20  | _         | —              | ns    |

| 171A         | TubL2oeH | AD Valid to Chip Enable Active                                            |                |           | 10             | ns    |

| TABLE 31-11: | <b>CLKO AND I/O TIMING REQUIREMENTS</b> |

|--------------|-----------------------------------------|

|              |                                         |

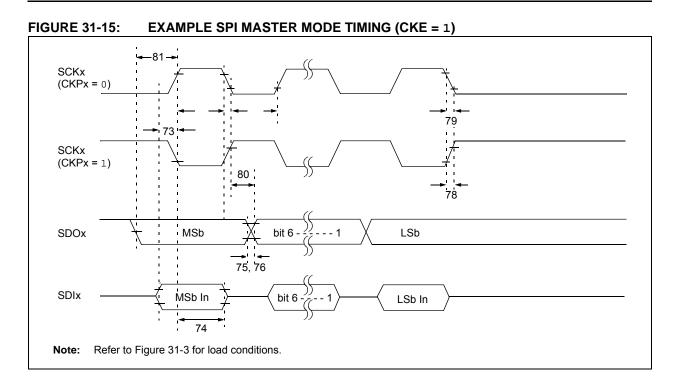

| Param.<br>No. | Symbol                | Characteristic                                            | Min          | Max | Units | Conditions |

|---------------|-----------------------|-----------------------------------------------------------|--------------|-----|-------|------------|

| 73            | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                | 20           | —   | ns    |            |

| 73A           | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2 | 1.5 Tcy + 40 | _   | ns    |            |

| 74            | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge                 | 40           | _   | ns    |            |

| 75            | TDOR                  | SDOx Data Output Rise Time                                | —            | 25  | ns    |            |

| 76            | TDOF                  | SDOx Data Output Fall Time                                | _            | 25  | ns    |            |

| 78            | TscR                  | SCKx Output Rise Time (Master mode)                       | _            | 25  | ns    |            |

| 79            | TscF                  | SCKx Output Fall Time (Master mode)                       | _            | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge                    | —            | 50  | ns    |            |

| 81            | TDOV2scH,<br>TDOV2scL | SDOx Data Output Setup to SCKx Edge                       | Тсү          | _   | ns    |            |

#### TABLE 31-18: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

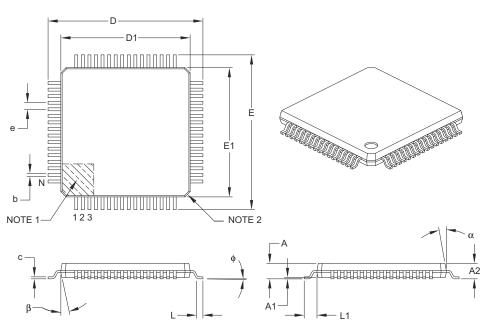

### 32.2 Package Details

The following sections give the technical details of the packages.

### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | MILLIMETERS | 6    |

|--------------------------|------------------|------|-------------|------|

| Dimens                   | Dimension Limits |      | NOM         | MAX  |

| Number of Leads          | Ν                |      | 64          |      |

| Lead Pitch               | е                |      | 0.50 BSC    |      |

| Overall Height           | А                | -    | -           | 1.20 |

| Molded Package Thickness | A2               | 0.95 | 1.00        | 1.05 |

| Standoff                 | A1               | 0.05 | -           | 0.15 |

| Foot Length              | L                | 0.45 | 0.60        | 0.75 |

| Footprint                | L1               |      | 1.00 REF    |      |

| Foot Angle               | ¢                | 0°   | 3.5°        | 7°   |

| Overall Width            | E                |      | 12.00 BSC   |      |

| Overall Length           | D                |      | 12.00 BSC   |      |

| Molded Package Width     | E1               |      | 10.00 BSC   |      |

| Molded Package Length    | D1               |      | 10.00 BSC   |      |

| Lead Thickness           | С                | 0.09 | -           | 0.20 |

| Lead Width               | b                | 0.17 | 0.22        | 0.27 |

| Mold Draft Angle Top     | α                | 11°  | 12°         | 13°  |

| Mold Draft Angle Bottom  | β                | 11°  | 12°         | 13°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

| RD1/PSP1/T5CKI/T7G 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD1/T5CKI/T7G/PSP1/AD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RD2/PSP219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |