Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 53                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67k22t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

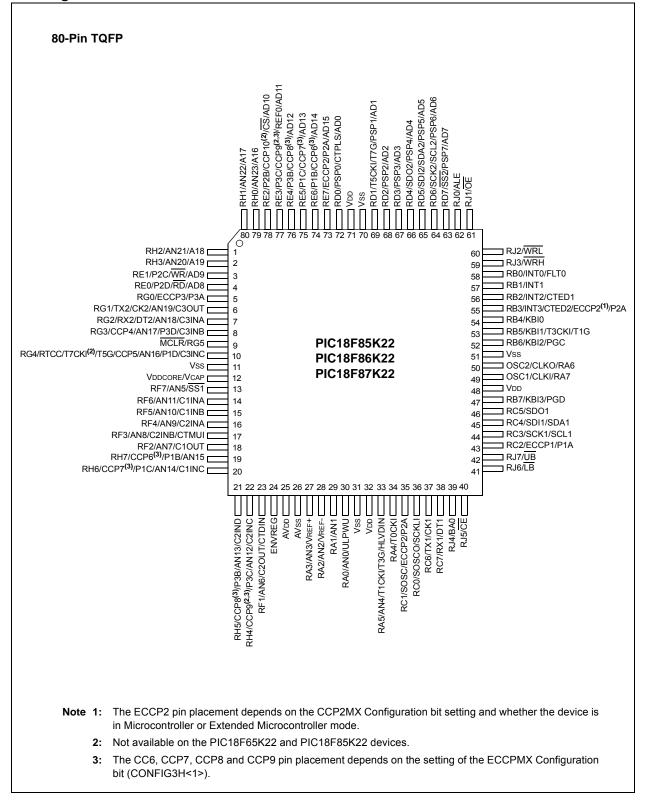

## Pin Diagrams – PIC18F8XK22

| R/W-0                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                     | R/W-0                    | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|-------------------|------------------|-----------------|-------|

| INTSRC                                                                                                                                                                                                                                                                | PLLEN                                                                                                                                                                                                     | TUN5                     | TUN4             | TUN3              | TUN2             | TUN1            | TUN0  |

| bit 7                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                           |                          |                  |                   |                  |                 | bit 0 |

| Legend:                                                                                                                                                                                                                                                               |                                                                                                                                                                                                           |                          |                  |                   |                  |                 |       |

| R = Readable                                                                                                                                                                                                                                                          | e bit                                                                                                                                                                                                     | W = Writable             | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at                                                                                                                                                                                                                                                         | POR                                                                                                                                                                                                       | '1' = Bit is set         |                  | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

| bit 7 <b>INTSRC:</b> Internal Oscillator Low-Frequency Source Select bit<br>1 = 31.25 kHz device clock derived from 16 MHz INTOSC source (divide-by-512 enabled, HF-INTC<br>21 bit is device clock derived from 16 MHz INTOSC source (divide-by-512 enabled, HF-INTC) |                                                                                                                                                                                                           |                          |                  |                   |                  |                 |       |

| bit 6                                                                                                                                                                                                                                                                 | <ul> <li>0 = 31 kHz device clock derived from INTRC 31 kHz oscillator (LF-INTOSC)</li> <li>PLLEN: Frequency Multiplier PLL Enable bit</li> <li>1 = PLL is enabled</li> <li>0 = PLL is disabled</li> </ul> |                          |                  |                   |                  |                 |       |

| bit 5-0                                                                                                                                                                                                                                                               | 011111 = Ma<br>0000001<br>000000 = Ce<br>111111                                                                                                                                                           | aximum frequer<br>•<br>• | ; fast RC oscill | Frequency Tunir   | -                | d frequency     |       |

#### REGISTER 3-3: OSCTUNE: OSCILLATOR TUNING REGISTER

Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (Parameter 39, Table 31-13).

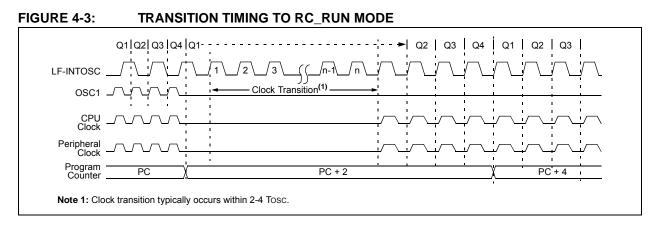

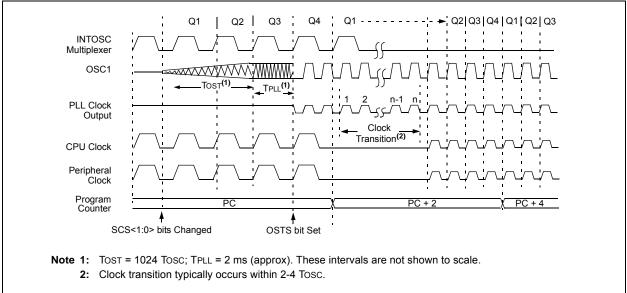

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the HFIOFS or MFIOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the HFIOFS or MFIOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The LF-INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

| R/W-0           | R/W-0                                                            | R/W-0                                                                                       | R/W-0           | R/W-0            | R/W-0             | R/W-0              | R/W-0   |  |  |

|-----------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|------------------|-------------------|--------------------|---------|--|--|

| CCP3MD          | CCP2MD                                                           | CCP1MD                                                                                      | UART2MD         | UART1MD          | SSP2MD            | SSP1MD             | ADCMD   |  |  |

| bit 7           |                                                                  |                                                                                             |                 |                  |                   |                    | bit 0   |  |  |

| r               |                                                                  |                                                                                             |                 |                  |                   |                    |         |  |  |

| Legend:         |                                                                  |                                                                                             |                 |                  |                   |                    |         |  |  |

| R = Readable    | bit                                                              | W = Writable                                                                                | bit             | U = Unimplen     | nented bit, read  | as '0'             |         |  |  |

| -n = Value at P | POR                                                              | '1' = Bit is set                                                                            |                 | '0' = Bit is cle | ared              | x = Bit is unkr    | Iown    |  |  |

| h:+ 7           |                                                                  |                                                                                             | hla/Diachla hi  |                  |                   |                    |         |  |  |

| bit 7           |                                                                  | /ID ECCP3 Ena                                                                               |                 |                  | CD2 disabling     | all of its alook a | 0.11000 |  |  |

|                 |                                                                  | lisabled for EC                                                                             |                 |                  | CP3, disabling a  | an of its clock s  | ources  |  |  |

| bit 6           | CCP2MD: PN                                                       | ID ECCP2 Ena                                                                                | able/Disable bi | it               |                   |                    |         |  |  |

|                 | 1 = PMD is e                                                     | PMD is enabled for ECCP2, disabling all of its clock sources                                |                 |                  |                   |                    |         |  |  |

|                 | 0 = PMD is d                                                     | lisabled for EC                                                                             | CP2             |                  |                   |                    |         |  |  |

| bit 5           | CCP1MD: PM                                                       | CP1MD: PMD ECCP1 Enable/Disable bit                                                         |                 |                  |                   |                    |         |  |  |

|                 | 1 = PMD is enabled for ECCP1, disabling all of its clock sources |                                                                                             |                 |                  |                   |                    |         |  |  |

|                 |                                                                  | lisabled for EC                                                                             | ••••            |                  |                   |                    |         |  |  |

| bit 4           | -                                                                | D: PMD UART2 Enable/Disable bit<br>is enabled for UART2, disabling all of its clock sources |                 |                  |                   |                    |         |  |  |

|                 |                                                                  | lisabled for UA                                                                             | •               |                  |                   |                    |         |  |  |

| bit 3           | UART1MD: F                                                       | MD UART1 E                                                                                  | nable/Disable   | bit              |                   |                    |         |  |  |

|                 | 1 = PMD is e                                                     | enabled for UAI                                                                             | RT1, disabling  | all of its clock | sources           |                    |         |  |  |

|                 | 0 = PMD is d                                                     | lisabled for UA                                                                             | RT1             |                  |                   |                    |         |  |  |

| bit 2           | SSP2MD: PM                                                       | 1D MSSP2 Ena                                                                                | able/Disable bi | t                |                   |                    |         |  |  |

|                 | 1 = PMD is enabled for MSSP2, disabling all of its clock sources |                                                                                             |                 |                  |                   |                    |         |  |  |

|                 |                                                                  | lisabled for MS                                                                             | •••             |                  |                   |                    |         |  |  |

| bit 1           |                                                                  | ID MSSP1 Ena                                                                                |                 |                  |                   |                    |         |  |  |

|                 |                                                                  | enabled for MS                                                                              | •               | all of its clock | sources           |                    |         |  |  |

| bit 0           | ADCMD: PMI                                                       | D Analog/Digita                                                                             | al Converter P  | MD Enable/Dis    | sable bit         |                    |         |  |  |

|                 |                                                                  | •••                                                                                         |                 |                  | abling all of its | clock sources      |         |  |  |

|                 | 0 = PMD is d                                                     | lisabled for the                                                                            | Analog/Digital  | l Converter      | -                 |                    |         |  |  |

|                 |                                                                  |                                                                                             |                 |                  |                   |                    |         |  |  |

### REGISTER 4-4: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

## 4.7 Ultra Low-Power Wake-up

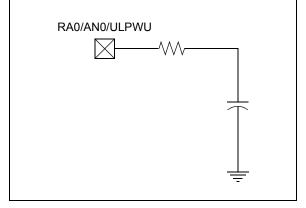

The Ultra Low-Power Wake-up (ULPWU) on pin, RA0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RA0 by configuring the RA0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RA0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the WDTCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RA0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RA0.

When the ULPWU module wakes the device from Sleep mode, the ULPLVL bit (WDTCON<5>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 4-1 for initializing the ULPWU module.

#### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

PORTAbits.RA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor

//on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power

//Wakeup module and allow

//capacitor discharge

WDTCONbits ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep

OSCCONbits.IDLEN = 0;

//Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RA0 and the external capacitor, provides overcurrent protection for the RA0/AN0/ ULPWU pin and enables software calibration of the time-out (see Figure 4-9).

#### FIGURE 4-9: ULTRA LOW-POWER WAKE-UP INITIALIZATION

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

Note: For more information, see AN879, "Using the Microchip Ultra Low-Power Wake-up Module" (DS00879).

## 5.7 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register ( $\overline{CM}$ ,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ ) are set or cleared differently in

different Reset situations, as indicated in Table 5-1. These bits are used in software to determine the nature of the Reset.

Table 5-2 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets, and WDT wake-ups.

## TABLE 5-1:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                                        | Program                | n RCON Register STKPTR Register |    |    |    |     |     |        | Register |

|------------------------------------------------------------------|------------------------|---------------------------------|----|----|----|-----|-----|--------|----------|

| Condition                                                        | Counter <sup>(1)</sup> | CM                              | RI | то | PD | POR | BOR | STKFUL | STKUNF   |

| Power-on Reset                                                   | 0000h                  | 1                               | 1  | 1  | 1  | 0   | 0   | 0      | 0        |

| RESET instruction                                                | 0000h                  | u                               | 0  | u  | u  | u   | u   | u      | u        |

| Brown-out Reset                                                  | 0000h                  | 1                               | 1  | 1  | 1  | u   | 0   | u      | u        |

| Configuration Mismatch Reset                                     | 0000h                  | 0                               | u  | u  | u  | u   | u   | u      | u        |

| MCLR Reset during power-managed Run modes                        | 0000h                  | u                               | u  | 1  | u  | u   | u   | u      | u        |

| MCLR Reset during power-<br>managed Idle modes and<br>Sleep mode | 0000h                  | u                               | u  | 1  | 0  | u   | u   | u      | u        |

| MCLR Reset during full-power execution                           | 0000h                  | u                               | u  | u  | u  | u   | u   | u      | u        |

| Stack Full Reset (STVREN = 1)                                    | 0000h                  | u                               | u  | u  | u  | u   | u   | 1      | u        |

| Stack Underflow Reset<br>(STVREN = 1)                            | 0000h                  | u                               | u  | u  | u  | u   | u   | u      | 1        |

| Stack Underflow Error (not an actual Reset, STVREN = 0)          | 0000h                  | u                               | u  | u  | u  | u   | u   | u      | 1        |

| WDT time-out during full-power or power-managed Run modes        | 0000h                  | u                               | u  | 0  | u  | u   | u   | u      | u        |

| WDT time-out during<br>power-managed Idle or Sleep<br>modes      | PC + 2                 | u                               | u  | 0  | 0  | u   | u   | u      | u        |

| Interrupt exit from power-managed modes                          | PC + 2                 | u                               | u  | u  | 0  | u   | u   | u      | u        |

Legend: u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

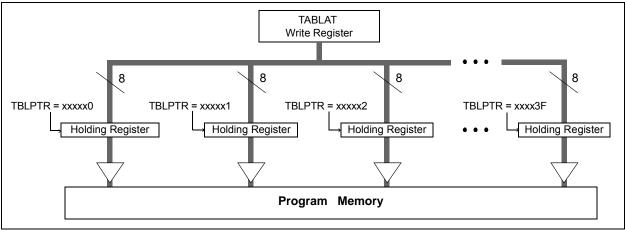

## 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an eight-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

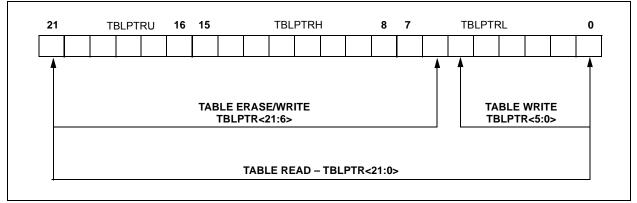

#### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways, based on the table operation. These operations are shown in Table 7-1 and only affect the low-order 21 bits.

## 7.2.4 TABLE POINTER BOUNDARIES

The TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into the TABLAT.

When a TBLWT is executed, the six LSbs of the Table Pointer register (TBLPTR<5:0>) determine which of the 64 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<21:6>) determine which program memory block of 64 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 7-3 describes the relevant boundaries of the TBLPTR based on Flash program memory operations.

| TABLE 7-1: | TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS |

|------------|------------------------------------------------------------|

|            |                                                            |

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

## 7.5 Writing to Flash Program Memory

The programming blocks are:

- PIC18FX5K22 and PIC18FX6K22 32 words or 64 bytes

- PIC18FX7K22 64 words or 128 bytes

Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. The number of holding registers used for programming by the table writes are:

- PIC18FX5K22 and PIC18FX6K22 64

- PIC18FX7K22 128

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 or 128 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write is terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

**Note:** The default value of the holding registers on device Resets, and after write operations, is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 or 128 holding registers before executing a write operation.

Example 10-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 10-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 10-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

#### EXAMPLE 10-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   |        |             | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | i                 |

|   |        | PRODL, RESO | ;                 |

| ; |        | · , ····    |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

|   |        |             |                   |

Example 10-4 shows the sequence to do a 16 x 16 signed multiply. Equation 10-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 10-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0= | ARG1H:ARG1L • ARG2H:ARG2L                                          |

|------------|--------------------------------------------------------------------|

| =          | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                           |

|            | $(ARG1H \bullet ARG2L \bullet 2^8) +$                              |

|            | $(ARG1L \bullet ARG2H \bullet 2^8) +$                              |

|            | $(ARG1L \bullet ARG2L) +$                                          |

|            | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$    |

|            | $(-1 \bullet ARG1H \le 7 \ge \bullet ARG2H: ARG2L \bullet 2^{16})$ |

|            |                                                                    |

#### EXAMPLE 10-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|    | MOVF    | ARG1L, W    |   |                  |

|----|---------|-------------|---|------------------|

|    | MULWF   | ARG2L       | ; | ARG1L * ARG2L -> |

|    |         |             |   | PRODH:PRODL      |

|    | MOVFF   | PRODH, RES1 | ; |                  |

|    | MOVFF   | PRODL, RESO |   |                  |

| ;  |         | - ,         |   |                  |

|    | MOVF    | ARG1H, W    |   |                  |

|    | MULWF   | ARG2H       | ; | ARG1H * ARG2H -> |

|    | ноциг   | AROZII      |   | PRODH:PRODL      |

|    | MOVFF   | PRODH, RES3 |   | TRODITIRODE      |

|    | MOVFF   |             |   |                  |

|    | MOVEL   | FRODE, RESZ | ' |                  |

| ;  | MOVE    |             |   |                  |

|    |         | ARG1L, W    |   |                  |

|    | MULWF   | ARG2H       |   | ARG1L * ARG2H -> |

|    |         |             |   | PRODH:PRODL      |

|    | MOVF    | PRODL, W    | ; |                  |

|    |         | RES1, F     |   | Add cross        |

|    | MOVF    |             | ; | products         |

|    | ADDWFC  | RES2, F     | ; |                  |

|    | CLRF    | WREG        | ; |                  |

|    | ADDWFC  | RES3, F     | ; |                  |

| ;  |         |             |   |                  |

|    | MOVF    | ARG1H, W    | ; |                  |

|    | MULWF   | ARG2L       | ; | ARG1H * ARG2L -> |

|    |         |             | ; | PRODH:PRODL      |

|    | MOVF    | PRODL, W    | ; |                  |

|    | ADDWF   | RES1, F     | ; | Add cross        |

|    | MOVF    | PRODH, W    | ; | products         |

|    | ADDWFC  | RES2, F     | ; | -                |

|    | CLRF    | WREG        | ; |                  |

|    | ADDWFC  | RES3, F     | ; |                  |

| ;  |         |             |   |                  |

|    | BTFSS   | ARG2H, 7    | ; | ARG2H:ARG2L neg? |

|    | BRA     | SIGN_ARG1   |   | no, check ARG1   |

|    | MOVF    | ARG1L, W    | ; | , 0110011 11101  |

|    | SUBWF   | RES2        | ; |                  |

|    | MOVF    | ARG1H, W    | ; |                  |

|    | SUBWFB  | RES3        |   | SIGN ARG1        |

|    | BTFSS   |             |   | ARG1H:ARG1L neg? |

|    |         |             |   |                  |

|    | BRA     | CONT_CODE   |   | no, done         |

|    | MOVF    | ARG2L, W    | ; |                  |

|    | SUBWF   | RES2        | ; |                  |

|    | MOVF    | ARG2H, W    | ; |                  |

|    | SUBWFB  | RES3        |   |                  |

| ;  |         |             |   |                  |

| CC | NT_CODE |             |   |                  |

|    | :       |             |   |                  |

|    |         |             |   |                  |

## 12.4 PORTC, TRISC and LATC Registers

PORTC is an eight-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISC and LATC. Only PORTC pins, RC2 through RC7, are digital only pins.

PORTC is multiplexed with ECCP, MSSP and EUSART peripheral functions (Table 12-5). The pins have Schmitt Trigger input buffers. The pins for ECCP, SPI and EUSART are also configurable for open-drain output whenever these functions are active. Open-drain configuration is selected by setting the SPIOD, CCPxOD and U1OD control bits in the registers, ODCON1 and ODCON3.

RC1 is normally configured as the default peripheral pin for the ECCP2 module. The assignment of ECCP2 is controlled by Configuration bit, CCP2MX (default state, CCP2MX = 1). When enabling peripheral functions, use care in defining TRIS bits for each PORTC pin. Some peripherals can override the TRIS bit to make a pin an output or input. Consult the corresponding peripheral section for the correct TRIS bit settings.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

| EXAMPLE 12-3: | INITIALIZING PORTC |

|---------------|--------------------|

|               |                    |

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATC  | ; Alternate method                         |

| CLRF  | LAIC  | , Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                    |

|       |       | ; RC<5:4> as outputs                       |

|       |       | ; RC<7:6> as inputs                        |

|       |       |                                            |

| Pin Name   | Function             | TRIS<br>Setting | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O<br>Type                                                    | Description                                                                                                                                     |  |  |  |  |

|------------|----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RC0/SOSCO/ | RC0                  | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | LATC<0> data output.                                                                                                                            |  |  |  |  |

| SCLKI/     |                      | 1               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST                                                             | PORTC<0> data input.                                                                                                                            |  |  |  |  |

|            | SOSCO                | 1               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST                                                             | SOSC oscillator output.                                                                                                                         |  |  |  |  |

|            | SCLKI                | 1               | I/O         Type         Description           O         DIG         LATC<0> data output.           I         ST         PORTC<0> data input.           I         ST         PORTC<0> data input.           I         ST         SOSC oscillator output.           I         ST         Digital clock input; enabled when SOSC oscillator is disabled.           O         DIG         LATC<1> data output.           I         ST         PORTC<1> data input.           I         ANA         SOSC oscillator input.           O         DIG         ECCP2 compare output and ECCP2 PWM output; takes priority over           I         ST         ECCP2 capture input.           O         DIG         ECCP2 capture input.           O         DIG         ECCP2 capture input.           O         DIG         ECCP2 capture of tri-state during Enhanced PWM shutdown ever priority over port data.           O         DIG         LATC<2> data output.           I         ST         PORTC<2> data input.           O         DIG         ECCP1 compare output and ECCP1 PWM output; takes priority over prid ata.           O | Digital clock input; enabled when SOSC oscillator is disabled. |                                                                                                                                                 |  |  |  |  |

| RC1/SOSCI/ | RC1                  | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | ST PORTC<1> data input.                                                                                                                         |  |  |  |  |

| ECCP2/P2A  |                      | 1               | IvoTypeDescription0ODIGLATC<0> data output.1ISTPORTC<0> data input.1ISTPORTC<0> data input.1ISTSOSC oscillator output.1ISTDigital clock input; enabled when SOSC oscillator is disabled.0ODIGLATC<1> data output.1ISTPORTC<1> data input.xIANASOSC oscillator input.0ODIGECCP2 compare output and ECCP2 PWM output; takes priorit1ISTECCP2 capture input.0ODIGECCP2 capture input.0ODIGECCP2 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdow<br>priority over port data.0ODIGLATC<2> data output.1ISTPORTC<2> data output.1ISTECCP1 compare output and ECCP1 PWM output; takes priority1ISTECCP1 capture input.0ODIGECCP1 capture input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |                                                                                                                                                 |  |  |  |  |

|            | SOSCI                | x               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ANA                                                            | SOSC oscillator input.                                                                                                                          |  |  |  |  |

|            | ECCP2 <sup>(1)</sup> | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | ECCP2 compare output and ECCP2 PWM output; takes priority over port data.                                                                       |  |  |  |  |

|            |                      | 1               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST                                                             | ECCP2 capture input.                                                                                                                            |  |  |  |  |

|            | 1ISTIP2A0ODIGI       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                | May be configured for tri-state during Enhanced PWM shutdown events; takes                                                                      |  |  |  |  |

| RC2/ECCP1/ | RC2                  | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | LATC<2> data output.                                                                                                                            |  |  |  |  |

| P1A        |                      | 1               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST                                                             | PORTC<2> data input.                                                                                                                            |  |  |  |  |

|            | ECCP1                | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | ECCP1 compare output and ECCP1 PWM output; takes priority over port data.                                                                       |  |  |  |  |

|            |                      | 1               | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ST                                                             | ECCP1 capture input.                                                                                                                            |  |  |  |  |

|            | P1A                  | 0               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DIG                                                            | ECCP1 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown events; takes<br>priority over port data. |  |  |  |  |

### TABLE 12-5: PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $I^2C = I^2C^{TM}$ /SMBus Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

## 16.3 Timer3/5/7 16-Bit Read/Write Mode

Timer3/5/7 can be configured for 16-bit reads and writes (see Figure 16.3). When the RD16 control bit (TxCON<1>) is set, the address for TMRxH is mapped to a buffer register for the high byte of Timer3/5/7. A read from TMRxL will load the contents of the high byte of Timer3/5/7 into the Timerx High Byte Buffer register. This provides users with the ability to accurately read all 16 bits of Timer3/5/7 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3/5/7 must also take place through the TMRxH Buffer register. The Timer3/5/7 high byte is updated with the contents of TMRxH when a write occurs to TMRxL. This allows users to write all 16 bits to both the high and low bytes of Timer3/5/7 at once.

The high byte of Timer3/5/7 is not directly readable or writable in this mode. All reads and writes must take place through the Timerx High Byte Buffer register.

Writes to TMRxH do not clear the Timer3/5/7 prescaler. The prescaler is only cleared on writes to TMRxL.

## 16.4 Using the SOSC Oscillator as the Timer3/5/7 Clock Source

The SOSC internal oscillator may be used as the clock source for Timer3/5/7. The SOSC oscillator is enabled by any peripheral that requests it. There are eight ways the SOSC can be enabled: if the SOSC is selected as the source by any of the odd timers, which is done by each respective SOSCEN bit (TxCON<3>), if the SOSC is selected as the RTCC source by the RTCOSC Configuration bit (CONFIG3L<1>), if the SOSC is selected as the CPU clock source by the SCS bits (OSCCON<1:0>) or if the SOSCGO bit is set (OSCCON2<3>). The SOSCGO bit is used to warm up the SOSC so that it is ready before any peripheral requests it. To use it as the Timer3/5/7 clock source, the TMRxCS bit must also be set. As previously noted, this also configures Timer3/5/7 to increment on every rising edge of the oscillator source.

The SOSC oscillator is described in **Section 14.5** "SOSC Oscillator".

## REGISTER 18-8: MONTH: MONTH VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |  |

|-------|-----|-----|---------|---------|---------|---------|---------|--|

| —     | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |  |

| bit 7 |     |     |         |         |         |         | bit 0   |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| Unimplemented: Read as '0'                                         |

|--------------------------------------------------------------------|

| MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit      |

| Contains a value of 0 or 1.                                        |

| MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits |

| Contains a value from 0 to 9.                                      |

|                                                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 18-9: DAY: DAY VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                       |

|---------|------------------------------------------------------------------|

| bit 5-4 | DAYTEN<1:0>: Binary Coded Decimal value of Day's Tens Digit bits |

|         | Contains a value from 0 to 3.                                    |

| bit 3-0 | DAYONE<3:0>: Binary Coded Decimal Value of Day's Ones Digit bits |

|         | Contains a value from 0 to 9.                                    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 18-10: WEEKDAY: WEEKDAY VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   |     |     | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                                                         |                      |                    |  |  |

|-------------------|---------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## **19.1 CCP Module Configuration**

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 19.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers, 1 through 8, which vary with the selected mode. Various timers are available to the CCP modules in Capture, Compare or PWM modes, as shown in Table 19-1.

#### TABLE 19-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource                    |

|----------|-----------------------------------|

| Capture  | Timeri Timeri Timeri 5 en Timeri  |

| Compare  | Timer1, Timer3, Timer 5 or Timer7 |

| PWM      | Timer2, Timer4, Timer 6 or Timer8 |

The assignment of a particular timer to a module is determined by the timer to CCP enable bits in the CCPTMRSx registers (see Register 19-2 and Register 19-3). All of the modules may be active at once and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time.

The CCPTMRS1 register selects the timers for CCP modules, 7, 6, 5 and 4, and the CCPTMRS2 register selects the timers for CCP modules, 10, 9 and 8. The possible configurations are shown in Table 19-2 and Table 19-3.

### TABLE 19-2: TIMER ASSIGNMENTS FOR CCP MODULES 4, 5, 6 AND 7

|                 | CCPTMRS1 Register           |             |         |                             |             |         |                             |             |                 |                             |      |

|-----------------|-----------------------------|-------------|---------|-----------------------------|-------------|---------|-----------------------------|-------------|-----------------|-----------------------------|------|

| CCP4 CCP5       |                             |             |         | CCP6                        |             |         |                             | CCP7        |                 |                             |      |

| C4TSEL<br><1:0> | Capture/<br>Compare<br>Mode | PWM<br>Mode | C5TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode | C6TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode | C7TSEL<br><1:0> | Capture/<br>Compare<br>Mode |      |

| 0 0             | TMR1                        | TMR2        | 0       | TMR1                        | TMR2        | 0       | TMR1                        | TMR2        | 0 0             | TMR1                        | TMR2 |

| 0 1             | TMR3                        | TMR4        | 1       | TMR5                        | TMR4        | 1       | TMR5                        | TMR2        | 0 1             | TMR5                        | TMR4 |

| 1 0             | TMR3                        | TMR6        |         |                             |             |         |                             |             | 1 0             | TMR5                        | TMR6 |

| 1 1             | 1 1 Reserved <sup>(1)</sup> |             |         |                             |             |         |                             | 1 1         | TMR5            | TMR8                        |      |

Note 1: Do not use the reserved bits.

### TABLE 19-3: TIMER ASSIGNMENTS FOR CCP MODULES 8, 9 AND 10

| CCPTMRS2 Register |                             |                   |                                |                             |                   |                     |                             |             |                      |                             |             |

|-------------------|-----------------------------|-------------------|--------------------------------|-----------------------------|-------------------|---------------------|-----------------------------|-------------|----------------------|-----------------------------|-------------|

| CCP8              |                             |                   | CCP8<br>Devices with 32 Kbytes |                             |                   | CCP9 <sup>(1)</sup> |                             |             | CCP10 <sup>(1)</sup> |                             |             |

| C8TSEL<br><1:0>   | Capture/<br>Compare<br>Mode | PWM<br>Mode       | C8TSEL<br><1:0>                | Capture/<br>Compare<br>Mode | PWM<br>Mode       | C9TSEL0             | Capture/<br>Compare<br>Mode | PWM<br>Mode | C10TSEL0             | Capture/<br>Compare<br>Mode | PWM<br>Mode |

| 0 0               | TMR1                        | TMR2              | 0 0                            | TMR1                        | TMR2              | 0                   | TMR1                        | TMR2        | 0                    | TMR1                        | TMR2        |

| 0 1               | TMR7                        | TMR4              | 0 1                            | TMR1                        | TMR4              | 1                   | TMR7                        | TMR4        | 1                    | TMR7                        | TMR2        |

| 1 0               | TMR7                        | TMR6              | 1 0                            | TMR1                        | TMR6              |                     |                             |             |                      |                             |             |

| 1 1               | Reserv                      | ed <sup>(2)</sup> | 1 1                            | Reserv                      | ed <sup>(2)</sup> |                     |                             |             |                      |                             |             |

**Note 1:** The module is not available for devices with 32 Kbytes of program memory (PIC18F65K22 and PIC18F85K22).

2: Do not use the reserved setting.

| Bit 0<br>CP0 |

|--------------|

| CP0          |

|              |

| —            |

| I WRT0       |

| —            |

| 1 EBTR0      |

| _            |

| יז<br>זי     |

TABLE 28-4: SUMMARY OF CODE PROTECTION REGISTERS

**Legend:** Shaded cells are unimplemented.

Note 1: This bit is available only on the PIC18F67K22 and PIC18F87K22 devices.

#### 28.6.1 PROGRAM MEMORY CODE PROTECTION

The program memory may be read to, or written from, any location using the table read and table write instructions. The Device ID may be read with table reads. The Configuration registers may be read and written with the table read and table write instructions.

In normal Execution mode, the CPx bits have no direct effect. CPx bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTx Configuration bit is '0'.

The EBTRx bits control table reads. For a block of user memory, with the EBTRx bit set to '0', a table read instruction that executes from within that block is allowed

to read. A table read instruction that executes from a location outside of that block is not allowed to read and will result in reading '0's. Figures 28-7 through 28-9 illustrate table write and table read protection.

Note: Code protection bits may only be written to a '0' from a '1' state. It is not possible to write a '1' to a bit in the '0' state. Code protection bits are only set to '1' by a full chip erase or block erase function. The full chip erase and block erase functions can only be initiated via ICSP or an external programmer. Refer to the device programming specification for more information.

#### **Register Values Program Memory Configuration Bit Settings** 000000h WRTB, EBTRB = 11 0007FFh 000800h TBLPTR = 0008FFh WRT0, EBTR0 = 01 PC = 003FFEh TBLWT\* 003FFFh 004000h WRT1, EBTR1 = 11 007FFFh 008000h PC = 00BFFEhTBLWT\* WRT2, EBTR2 = 11 00BFFFh 00C000h WRT3, EBTR3 = 11 00FFFFh Results: All table writes are disabled to Blockn whenever WRTx = 0.

### FIGURE 28-7: TABLE WRITE (WRTx) DISALLOWED