Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85k22-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.1.6 EASY MIGRATION

All devices share the same rich set of peripherals except that the devices with 32 Kbytes of program memory (PIC18F65K22 and PIC18F85K22) have two less CCPs and three less timers. This provides a smooth migration path within the device family as applications evolve and grow.

The consistent pinout scheme, used throughout the entire family, also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

All of the devices in the family share the same rich set of peripherals, except for those with 32 Kbytes of program memory (PIC18F65K22 and PIC18F85K22). Those devices have two less CCPs and three less timers.

The PIC18F87K22 family is also largely pin compatible with other PIC18 families, such as the PIC18F8720 and PIC18F8722 and the PIC18F85J11. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining a similar feature set.

### 1.2 Other Special Features

- Communications: The PIC18F87K22 family incorporates a range of serial communication peripherals, including two Enhanced USARTs (EUSART) that support LIN/J2602, and two Master SSP modules, capable of both SPI and I<sup>2</sup>C<sup>™</sup> (Master and Slave) modes of operation.

- CCP Modules: PIC18F87K22 family devices incorporate up to seven Capture/Compare/PWM (CCP) modules. Up to six different time bases can be used to perform several different operations at once.

- ECCP Modules: The PIC18F87K22 family has three Enhanced CCP (ECCP) modules to maximize flexibility in control applications:

- Up to eight different time bases for performing several different operations at once

- Up to four PWM outputs for each module, for a total of 12 PWMs

- Other beneficial features, such as polarity selection, programmable dead time, auto-shutdown and restart, and Half-Bridge and Full-Bridge Output modes

- 12-Bit A/D Converter: The PIC18F87K22 family has differential ADC. It incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and thus, reducing code overhead.

- Charge Time Measurement Unit (CTMU): The CTMU is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation.

- Together with other on-chip analog modules, the CTMU can precisely measure time, measure capacitance or relative changes in capacitance, or generate output pulses that are independent of the system clock.

- LP Watchdog Timer (WDT): This enhanced version incorporates a 22-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 31.0 "Electrical Characteristics" for time-out periods.

- Real-Time Clock and Calendar Module (RTCC): The RTCC module is intended for applications requiring that accurate time be maintained for extended periods of time with minimum to no intervention from the CPU.

- The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

= Open-Drain (no P diode to VDD)

#### TABLE 1-4: PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name              | Pin Number       | Pin   | Buffer                 | Description                                   |

|-----------------------|------------------|-------|------------------------|-----------------------------------------------|

|                       | TQFP             | Туре  | Surrey     Description |                                               |

| RH7/CCP6/P1B/AN15     | 19               |       |                        |                                               |

| RH7                   |                  | I/O   | ST                     | Digital I/O.                                  |

| CCP6 <sup>(5)</sup>   |                  | I/O   | ST                     | Capture 6 input/Compare 6 output/PWM6 output. |

| P1B                   |                  | 0     | —                      | ECCP1 PWM Output B.                           |

| AN15                  |                  | I.    | Analog                 | Analog Input 15.                              |

| Legend: TTL = TTL com | patible input    |       |                        | CMOS = CMOS compatible input or output        |

| ST = Schmitt T        | rigger input wit | h CMC | OS levels              | Analog = Analog input                         |

| I = Input             |                  |       |                        | O = Output                                    |

= Power Ρ

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

OD

| R/W-0           | R/W-0                                                            | R/W-0            | R/W-0           | R/W-0            | R/W-0             | R/W-0              | R/W-0   |

|-----------------|------------------------------------------------------------------|------------------|-----------------|------------------|-------------------|--------------------|---------|

| CCP3MD          | CCP2MD                                                           | CCP1MD           | UART2MD         | UART1MD          | SSP2MD            | SSP1MD             | ADCMD   |

| bit 7           |                                                                  |                  |                 |                  |                   |                    | bit 0   |

| r               |                                                                  |                  |                 |                  |                   |                    |         |

| Legend:         |                                                                  |                  |                 |                  |                   |                    |         |

| R = Readable    | bit                                                              | W = Writable     | bit             | U = Unimplen     | nented bit, read  | as '0'             |         |

| -n = Value at P | POR                                                              | '1' = Bit is set |                 | '0' = Bit is cle | ared              | x = Bit is unkr    | Iown    |

| h:+ 7           |                                                                  |                  | hla/Diachla hi  |                  |                   |                    |         |

| bit 7           |                                                                  | /ID ECCP3 Ena    |                 |                  | CD2 disabling     | all of its alook a | 0.11000 |

|                 |                                                                  | lisabled for EC  |                 |                  | CP3, disabling a  | an of its clock s  | ources  |

| bit 6           | CCP2MD: PN                                                       | ID ECCP2 Ena     | able/Disable bi | it               |                   |                    |         |

|                 | 1 = PMD is e                                                     | nabled for EC    | CP2, disabling  | all of its clock | sources           |                    |         |

|                 | 0 = PMD is d                                                     | lisabled for EC  | CP2             |                  |                   |                    |         |

| bit 5           | CCP1MD: PMD ECCP1 Enable/Disable bit                             |                  |                 |                  |                   |                    |         |

|                 | 1 = PMD is enabled for ECCP1, disabling all of its clock sources |                  |                 |                  |                   |                    |         |

|                 |                                                                  | lisabled for EC  | ••••            |                  |                   |                    |         |

| bit 4           | -                                                                | MD UART2 E       |                 |                  |                   |                    |         |

|                 |                                                                  | enabled for UAI  | •               | all of its clock | sources           |                    |         |

| bit 3           | UART1MD: F                                                       | MD UART1 E       | nable/Disable   | bit              |                   |                    |         |

|                 | 1 = PMD is e                                                     | enabled for UAI  | RT1, disabling  | all of its clock | sources           |                    |         |

|                 | 0 = PMD is d                                                     | lisabled for UA  | RT1             |                  |                   |                    |         |

| bit 2           | SSP2MD: PM                                                       | 1D MSSP2 Ena     | able/Disable bi | t                |                   |                    |         |

|                 | 1 = PMD is enabled for MSSP2, disabling all of its clock sources |                  |                 |                  |                   |                    |         |

|                 |                                                                  | lisabled for MS  | •••             |                  |                   |                    |         |

| bit 1           |                                                                  | ID MSSP1 Ena     |                 |                  |                   |                    |         |

|                 |                                                                  | enabled for MS   | •               | all of its clock | sources           |                    |         |

| bit 0           | ADCMD: PMI                                                       | D Analog/Digita  | al Converter P  | MD Enable/Dis    | sable bit         |                    |         |

|                 |                                                                  | •••              |                 |                  | abling all of its | clock sources      |         |

|                 | 0 = PMD is d                                                     | lisabled for the | Analog/Digital  | l Converter      | -                 |                    |         |

|                 |                                                                  |                  |                 |                  |                   |                    |         |

### REGISTER 4-4: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

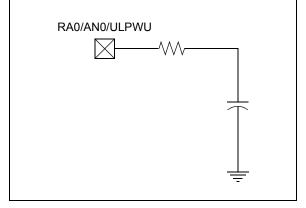

### 4.7 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on pin, RA0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RA0 by configuring the RA0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RA0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the WDTCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RA0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RA0.

When the ULPWU module wakes the device from Sleep mode, the ULPLVL bit (WDTCON<5>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 4-1 for initializing the ULPWU module.

### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

PORTAbits.RA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor

//on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power

//Wakeup module and allow

//capacitor discharge

WDTCONbits ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep

OSCCONDits.IDLEN = 0;

//Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RA0 and the external capacitor, provides overcurrent protection for the RA0/AN0/ ULPWU pin and enables software calibration of the time-out (see Figure 4-9).

### FIGURE 4-9: ULTRA LOW-POWER WAKE-UP INITIALIZATION

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

Note: For more information, see AN879, "Using the Microchip Ultra Low-Power Wake-up Module" (DS00879).

### 8.8 Operation in Power-Managed Modes

In alternate, power-managed Run modes, the external bus continues to operate normally. If a clock source with a lower speed is selected, bus operations will run at that speed. In these cases, excessive access times for the external memory may result if Wait states have been enabled and added to external memory operations. If operations in a lower power Run mode are anticipated, users should provide in their applications for adjusting memory access times at the lower clock speeds. In Sleep and Idle modes, the microcontroller core does not need to access data; bus operations are suspended. The state of the external bus is frozen, with the address/data pins, and most of the control pins, holding at the same state they were in when the mode was invoked. The only potential changes are to the  $\overline{CE}$ ,  $\overline{LB}$  and  $\overline{UB}$  pins, which are held at logic high.

| <b>TABLE 8-3</b> : | REGISTERS ASSOCIATED WITH THE EXTERNAL MEMORY BUS |

|--------------------|---------------------------------------------------|

|                    |                                                   |

| Name                  | Bit 7 | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0 |

|-----------------------|-------|--------|---------------------|--------|--------|-----------|-----------|-------|

| MEMCON <sup>(1)</sup> | EBDIS | _      | WAIT1               | WAIT0  |        | —         | WM1       | WM0   |

| PADCFG1               | RDPU  | REPU   | RJPU <sup>(1)</sup> | _      | —      | RTSECSEL1 | RTSECSEL0 |       |

| PMD1                  | PSPMD | CTMUMD | RTCCMD              | TMR4MD | TMR3MD | TMR2MD    | TMR1MD    | EMBMD |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during External Memory Bus access.

Note 1: Unimplemented in 64-pin devices (PIC18F6XK22), read as '0'.

#### EXAMPLE 9-1: DATA EEPROM READ

| MOVLW | DATA_EE_ADDRH | ;                                           |

|-------|---------------|---------------------------------------------|

| MOVWF | EEADRH        | ; Upper bits of Data Memory Address to read |

| MOVLW | DATA_EE_ADDR  | i                                           |

| MOVWF | EEADR         | ; Lower bits of Data Memory Address to read |

| BCF   | EECON1, EEPGD | ; Point to DATA memory                      |

| BCF   | EECON1, CFGS  | ; Access EEPROM                             |

| BSF   | EECON1, RD    | ; EEPROM Read                               |

| NOP   |               |                                             |

| MOVF  | EEDATA, W     | ; W = EEDATA                                |

#### EXAMPLE 9-2: DATA EEPROM WRITE

|          | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | DATA_EE_ADDRH<br>EEADRH<br>DATA_EE_ADDR<br>EEADR<br>DATA_EE_DATA<br>EEDATA | ;<br>; Upper bits of Data Memory Address to write<br>;<br>; Lower bits of Data Memory Address to write<br>;<br>; Data Memory Value to write |

|----------|----------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|          | BCF                                                | EECON1, EEPGD                                                              | ; Point to DATA memory                                                                                                                      |

|          | BCF                                                | EECON1, CFGS                                                               | ; Access EEPROM                                                                                                                             |

|          | BSF                                                | EECON1, WREN                                                               | ; Enable writes                                                                                                                             |

|          | BCF                                                | INTCON, GIE                                                                | ; Disable Interrupts                                                                                                                        |

|          | MOVLW                                              | 0x55                                                                       | ;                                                                                                                                           |

| Required | MOVWF                                              | EECON2                                                                     | ; Write 55h                                                                                                                                 |

| Sequence | MOVLW                                              | 0xAA                                                                       | i                                                                                                                                           |

|          | MOVWF                                              | EECON2                                                                     | ; Write OAAh                                                                                                                                |

|          | BSF                                                | EECON1, WR                                                                 | ; Set WR bit to begin write                                                                                                                 |

|          | BTFSC                                              | EECON1, WR                                                                 | ; Wait for write to complete GOTO \$-2                                                                                                      |

|          | BSF                                                | INTCON, GIE                                                                | ; Enable Interrupts                                                                                                                         |

|          |                                                    |                                                                            | · Harr godo ovogution                                                                                                                       |

|          | DOD                                                |                                                                            | ; User code execution                                                                                                                       |

|          | BCF                                                | EECON1, WREN                                                               | ; Disable writes on write complete (EEIF set)                                                                                               |

### 13.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-two increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (for example, CLRF TMR0, MOVWF TMR0, BSF TMR0) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

### 13.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 13.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| TABLE 13-1. REGISTERS ASSOCIATED WITH HIMLERD | TABLE 13-1: | REGISTERS ASSOCIATED WITH TIMER0 |

|-----------------------------------------------|-------------|----------------------------------|

|-----------------------------------------------|-------------|----------------------------------|

| Name   | Bit 7        | Bit 6                     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 |

|--------|--------------|---------------------------|--------|--------|-------|--------|--------|-------|

| TMR0L  | Timer0 Regis | ster Low Byte             |        |        |       |        |        |       |

| TMR0H  | Timer0 Regis | Timer0 Register High Byte |        |        |       |        |        |       |

| INTCON | GIE/GIEH     | PEIE/GIEL                 | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| TOCON  | TMR0ON       | T08BIT                    | TOCS   | T0SE   | PSA   | T0PS2  | T0PS1  | T0PS0 |

|        | · •          |                           |        |        |       | •      |        |       |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

| TABLE 16-5: REGISTERS ASSOCIATED WITH TIMER3/5/7 AS A TIMER/COUNTER |                                               |                        |                        |               |                       |        |        |         |

|---------------------------------------------------------------------|-----------------------------------------------|------------------------|------------------------|---------------|-----------------------|--------|--------|---------|

| Name                                                                | Bit 7                                         | Bit 6                  | Bit 5                  | Bit 4         | Bit 3                 | Bit 2  | Bit 1  | Bit 0   |

| INTCON                                                              | GIE/GIEH                                      | PEIE/GIEL              | TMR0IE                 | <b>INTOIE</b> | RBIE                  | TMR0IF | INT0IF | RBIF    |

| PIR5                                                                | TMR7GIF <sup>(1)</sup>                        | TMR12IF <sup>(1)</sup> | TMR10IF <sup>(1)</sup> | TMR8IF        | TMR7IF <sup>(1)</sup> | TMR6IF | TMR5IF | TMR4IF  |

| IPR5                                                                | TMR7GIP <sup>(1)</sup>                        | TMR12IP <sup>(1)</sup> | TMR10IP <sup>(1)</sup> | TMR8IP        | TMR7IP <sup>(1)</sup> | TMR6IP | TMR5IP | TMR4IP  |

| PIE5                                                                | TMR7GIE <sup>(1)</sup>                        | TMR12IE <sup>(1)</sup> | TMR10IE <sup>(1)</sup> | TMR8IE        | TMR7IE <sup>(1)</sup> | TMR6IE | TMR5IE | TMR4IE  |

| PIE3                                                                | TMR5GIE                                       | _                      | RC2IE                  | TX2IE         | CTMUIE                | CCP2IE | CCP1IE | RTCCIE  |

| IPR3                                                                | TMR5GIP                                       | _                      | RC2IP                  | TX2IP         | CTMUIP                | CCP2IP | CCP1IP | RTCCIP  |

| PIR3                                                                | TMR5GIF                                       | _                      | RC2IF                  | TX2IF         | CTMUIF                | CCP2IF | CCP1IF | RTCCIF  |

| PIE2                                                                | OSCFIE                                        | _                      | SSP2IE                 | BCL2IE        | BCL1IE                | HLVDIE | TMR3IE | TMR3GIE |

| PIR2                                                                | OSCFIF                                        | —                      | SSP2IF                 | BCL2IF        | BCL1IF                | HLVDIF | TMR3IF | TMR3GIF |

| IPR2                                                                | OSCFIP                                        | _                      | SSP2IP                 | BCL2IP        | BCL1IP                | HLVDIP | TMR3IP | TMR3GIP |

| TMR3H                                                               | Timer3 Register High Byte                     |                        |                        |               |                       |        |        |         |

| TMR3L                                                               | Timer3 Regist                                 | er Low Byte            |                        |               |                       |        |        |         |

| T3GCON                                                              | TMR3GE                                        | T3GPOL                 | T3GTM                  | T3GSPM        | T3GGO/<br>T3DONE      | T3GVAL | T3GSS1 | T3GSS0  |

| T3CON                                                               | TMR3CS1                                       | TMR3CS0                | T3CKPS1                | T3CKPS0       | SOSCEN                | T3SYNC | RD16   | TMR3ON  |

| TMR5H                                                               | Timer5 Regist                                 | er High Byte           |                        |               |                       |        |        |         |

| TMR5L                                                               | Timer5 Regist                                 | er Low Byte            |                        |               |                       |        |        |         |

| T5GCON                                                              | TMR5GE                                        | T5GPOL                 | T5GTM                  | T5GSPM        | T5GGO/<br>T5DONE      | T5GVAL | T5GSS1 | T5GSS0  |

| T5CON                                                               | TMR5CS1                                       | TMR5CS0                | T5CKPS1                | T5CKPS0       | SOSCEN                | T5SYNC | RD16   | TMR5ON  |

| TMR7H <sup>(1)</sup>                                                | /R7H <sup>(1)</sup> Timer7 Register High Byte |                        |                        |               |                       |        |        |         |

| TMR7L <sup>(1)</sup>                                                | Timer7 Regist                                 | er Low Byte            |                        |               |                       |        |        |         |

| T7GCON <sup>(1)</sup>                                               | TMR7GE                                        | T7GPOL                 | T7GTM                  | T7GSPM        | T7GGO/<br>T7DONE      | T7GVAL | T7GSS1 | T7GSS0  |

| T7CON <sup>(1)</sup>                                                | TMR7CS1                                       | TMR7CS0                | T7CKPS1                | T7CKPS0       | SOSCEN                | T7SYNC | RD16   | TMR7ON  |

| OSCCON2                                                             | —                                             | SOSCRUN                | —                      |               | SOSCGO                | —      | MFIOFS | MFIOSEL |

| PMD1                                                                | PSPMD                                         | CTMUMD                 | RTCCMD                 | TMR4MD        | TMR3MD                | TMR2MD | TMR1MD | EMBMD   |

| PMD2                                                                | TMR10MD <sup>(1)</sup>                        | TMR8MD                 | TMR7MD <sup>(1)</sup>  | TMR6MD        | TMR5MD                | CMP3MD | CMP2MD | CMP2MD  |

|                                                                     |                                               |                        |                        |               | •                     |        |        |         |

### TABLE 16-5: REGISTERS ASSOCIATED WITH TIMER3/5/7 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3/5/7 module.

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

# 17.0 TIMER4/6/8/10/12 MODULES

The Timer4/6/8/10/12 timer modules have the following features:

- Eight-bit Timer register (TMRx)

- Eight-bit Period register (PRx)

- Readable and writable (all registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match of PRx

Timer10 and Timer12 are unimplemented for devices with a program memory of 32 Kbytes (PIC18FX5K22).

| Note: | Throughout this section, generic references      |

|-------|--------------------------------------------------|

|       | are used for register and bit names that are the |

|       | same, except for an 'x' variable that indicates  |

|       | the item's association with the Timer4, Timer6,  |

|       | Timer8, Timer10 or Timer12 module. For           |

|       | example, the control register is named TxCON     |

|       | and refers to T4CON, T6CON, T8CON,               |

|       | T10CON and T12CON.                               |

The Timer4/6/8/10/12 modules have a control register, which is shown in Register 17-1. Timer4/6/8/10/12 can be shut off by clearing control bit, TMRxON (TxCON<2>), to minimize power consumption. The prescaler and post-scaler selection of Timer4/6/8/10/12 are also controlled by this register. Figure 17-1 is a simplified block diagram of the Timer4/6/8/10/12 modules.

# 17.1 Timer4/6/8/10/12 Operation

Timer4/6/8/10/12 can be used as the PWM time base for the PWM mode of the ECCP modules. The TMRx registers are readable and writable, and are cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, TxCKPS<1:0> (TxCON<1:0>). The match output of TMRx goes through a four-bit postscaler (that gives a 1:1 to 1:16 inclusive scaling) to generate a TMRx interrupt, latched in the flag bit, TMRxIF. Table 17-1 shows each module's flag bit.

| Timer<br>Module | Flag Bit<br>PIR5 <x></x> | Timer<br>Module | Flag Bit<br>PIR5 <x></x> |

|-----------------|--------------------------|-----------------|--------------------------|

| 4               | 0                        | 10              | 5                        |

| 6               | 2                        | 12              | 6                        |

| 8               | 4                        |                 |                          |

TABLE 17-1: TIMER4/6/8/10/12 FLAG BITS

The interrupt can be enabled or disabled by setting or clearing the Timerx Interrupt Enable bit (TMRxIE), shown in Table 17-2.

| TABLE 17-2: | TIMER4/6/8/10/12 INTERRUPT |

|-------------|----------------------------|

|             | ENABLE BITS                |

| Timer<br>Module | Flag Bit<br>PIE5 <x></x> | Timer<br>Module | Flag Bit<br>PIE5 <x></x> |

|-----------------|--------------------------|-----------------|--------------------------|

| 4               | 0                        | 10              | 5                        |

| 6               | 2                        | 12              | 6                        |

| 8               | 4                        |                 |                          |

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMRx register

- A write to the TxCON register

- <u>Any device Reset</u> Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR)

A TMRx is not cleared when a TxCON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 19-2, Register 19-3 and Register 20-2.

# FIGURE 18-6: TIMER PULSE GENERATION

| RTCEN bit        |  |

|------------------|--|

| ALRMEN bit       |  |

| RTCC Alarm Event |  |

| RTCC Pin         |  |

### 18.4 Sleep Mode

The timer and alarm continue to operate while in Sleep mode. The operation of the alarm is not affected by Sleep, as an alarm event can always wake up the CPU.

The Idle mode does not affect the operation of the timer or alarm.

### 18.5 Reset

### 18.5.1 DEVICE RESET

When a device Reset occurs, the ALRMRPT register is forced to its Reset state, causing the alarm to be disabled (if enabled prior to the Reset). If the RTCC was enabled, it will continue to operate when a basic device Reset occurs.

### 18.5.2 POWER-ON RESET (POR)

The RTCCFG and ALRMRPT registers are reset only on a POR. Once the device exits the POR state, the clock registers should be reloaded with the desired values.

The timer prescaler values can be reset only by writing to the SECONDS register. No device Reset can affect the prescalers.

### 22.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 22.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7     | Bit 6         | Bit 5        | Bit 4         | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|----------|-----------|---------------|--------------|---------------|---------|---------|--------|--------|

| INTCON   | GIE/GIEH  | PEIE/GIEL     | TMR0IE       | INT0IE        | RBIE    | TMR0IF  | INT0IF | RBIF   |

| PIR1     | PSPIF     | ADIF          | RC1IF        | TX1IF         | SSP1IF  | TMR1GIF | TMR2IF | TMR1IF |

| PIE1     | PSPIE     | ADIE          | RC1IE        | TX1IE         | SSP1IE  | TMR1GIE | TMR2IE | TMR1IE |

| IPR1     | PSPIP     | ADIP          | RC1IP        | TX1IP         | SSP1IP  | TMR1GIP | TMR2IP | TMR1IP |

| PIR3     | TMR5GIF   | —             | RC2IF        | TX2IF         | CTMUIF  | CCP2IF  | CCP1IF | RTCCIF |

| PIE3     | TMR5GIE   | —             | RC2IE        | TX2IE         | CTMUIE  | CCP2IE  | CCP1IE | RTCCIE |

| IPR3     | TMR5GIP   | —             | RC2IP        | TX2IP         | CTMUIP  | CCP2IP  | CCP1IP | RTCCIP |

| RCSTA1   | SPEN      | RX9           | SREN         | CREN          | ADDEN   | FERR    | OERR   | RX9D   |

| TXREG1   | EUSART1 T | ransmit Regis | ster         |               |         |         |        |        |

| TXSTA1   | CSRC      | TX9           | TXEN         | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |

| BAUDCON1 | ABDOVF    | RCIDL         | RXDTP        | TXCKP         | BRG16   | _       | WUE    | ABDEN  |

| SPBRGH1  | EUSART1 B | aud Rate Gei  | nerator Regi | ster High Byt | e       |         |        |        |

| SPBRG1   | EUSART1 B | aud Rate Ger  | nerator Regi | ster          |         |         |        |        |

| RCSTA2   | SPEN      | RX9           | SREN         | CREN          | ADDEN   | FERR    | OERR   | RX9D   |

| TXREG2   | EUSART2 T | ransmit Regis | ster         |               |         |         |        |        |

| TXSTA2   | CSRC      | TX9           | TXEN         | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |

| BAUDCON2 | ABDOVF    | RCIDL         | RXDTP        | TXCKP         | BRG16   | _       | WUE    | ABDEN  |

| SPBRGH2  | EUSART2 B | aud Rate Gei  | nerator Regi | ster High Byt | e       |         |        |        |

| SPBRG2   | EUSART2 B | aud Rate Ger  | nerator Regi | ster          |         |         |        |        |

| ODCON3   | U2OD      | U10D          | _            |               | —       |         | —      | CTMUDS |

| PMD0     | CCP3MD    | CCP2MD        | CCP1MD       | UART2MD       | UART1MD | SSP2MD  | SSP1MD | ADCMD  |

### TABLE 22-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

### 22.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of Sleep, or any Idle mode, and bit, SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREGx register. If the RCxIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RCxIE.

- 3. If 9-bit reception is desired, set bit, RX9.

- 4. To enable reception, set enable bit, CREN.

- 5. Flag bit, RCxIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREGx register.

- 8. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7     | Bit 6         | Bit 5        | Bit 4         | Bit 3   | Bit 2   | Bit 1         | Bit 0  |

|----------|-----------|---------------|--------------|---------------|---------|---------|---------------|--------|

| INTCON   | GIE/GIEH  | PEIE/GIEL     | TMR0IE       | INT0IE        | RBIE    | TMR0IF  | <b>INT0IF</b> | RBIF   |

| PIR1     | PSPIF     | ADIF          | RC1IF        | TX1IF         | SSP1IF  | TMR1GIF | TMR2IF        | TMR1IF |

| PIE1     | PSPIE     | ADIE          | RC1IE        | TX1IE         | SSP1IE  | TMR1GIE | TMR2IE        | TMR1IE |

| IPR1     | PSPIP     | ADIP          | RC1IP        | TX1IP         | SSP1IP  | TMR1GIP | TMR2IP        | TMR1IP |

| PIR3     | TMR5GIF   | _             | RC2IF        | TX2IF         | CTMUIF  | CCP2IF  | CCP1IF        | RTCCIF |

| PIE3     | TMR5GIE   | _             | RC2IE        | TX2IE         | CTMUIE  | CCP2IE  | CCP1IE        | RTCCIE |

| IPR3     | TMR5GIP   | _             | RC2IP        | TX2IP         | CTMUIP  | CCP2IP  | CCP1IP        | RTCCIP |

| RCSTA1   | SPEN      | RX9           | SREN         | CREN          | ADDEN   | FERR    | OERR          | RX9D   |

| RCREG1   | EUSART1 F | Receive Regis | ter          |               |         |         |               |        |

| TXSTA1   | CSRC      | TX9           | TXEN         | SYNC          | SENDB   | BRGH    | TRMT          | TX9D   |

| BAUDCON1 | ABDOVF    | RCIDL         | RXDTP        | TXCKP         | BRG16   | —       | WUE           | ABDEN  |

| SPBRGH1  | EUSART1 E | aud Rate Ge   | nerator Regi | ster High Byt | е       |         |               |        |

| SPBRG1   | EUSART1 E | Baud Rate Ge  | nerator Regi | ster          |         |         |               |        |

| RCSTA2   | SPEN      | RX9           | SREN         | CREN          | ADDEN   | FERR    | OERR          | RX9D   |

| RCREG2   | EUSART2 F | Receive Regis | ter          |               |         |         |               |        |

| TXSTA2   | CSRC      | TX9           | TXEN         | SYNC          | SENDB   | BRGH    | TRMT          | TX9D   |

| BAUDCON2 | ABDOVF    | RCIDL         | RXDTP        | TXCKP         | BRG16   | —       | WUE           | ABDEN  |

| SPBRGH2  | EUSART2 E | aud Rate Ge   | nerator Regi | ster High Byt | е       |         |               |        |

| SPBRG2   | EUSART2 E | Baud Rate Ge  | nerator Regi | ster          |         |         |               |        |

| ODCON3   | U2OD      | U10D          | _            | _             | —       | _       | —             | CTMUDS |

| PMD0     | CCP3MD    | CCP2MD        | CCP1MD       | UART2MD       | UART1MD | SSP2MD  | SSP1MD        | ADCMD  |

TABLE 22-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

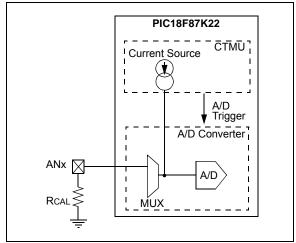

The CTMU current source may be trimmed with the trim bits in CTMUICON using an iterative process to get the exact current desired. Alternatively, the nominal value without adjustment may be used. That value may be stored by software for use in all subsequent capacitive or time measurements.

To calculate the value for  $\ensuremath{\mathrm{RCAL}}$  , the nominal current must be chosen. Then, the resistance can be calculated.

For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale (or 2.31V) as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as RCAL = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, RCAL would be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

### FIGURE 27-2: CTMU CURRENT SOURCE CALIBRATION CIRCUIT

A value of 70% of full-scale voltage is chosen to make sure that the A/D Converter was in a range that is well above the noise floor. If an exact current is chosen to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL may also be adjusted to allow for available resistor values. RCAL should be of the highest precision available, in light of the precision needed for the circuit that the CTMU will be measuring. A recommended minimum would be 0.1% tolerance.

The following examples show a typical method for performing a CTMU current calibration.

• Example 27-1 demonstrates how to initialize the A/D Converter and the CTMU.

This routine is typical for applications using both modules.

• Example 27-2 demonstrates one method for the actual calibration routine.

This method manually triggers the A/D Converter to demonstrate the entire step-wise process. It is also possible to automatically trigger the conversion by setting the CTMU's CTTRIG bit (CTMUCONH<0>).

| R/P-1         | U-0              | U-0                                                      | U-0          | R/P-1             | U-0          | R/P-1                          | R/P-1          |

|---------------|------------------|----------------------------------------------------------|--------------|-------------------|--------------|--------------------------------|----------------|

| MCLRE         |                  | _                                                        | —            | MSSPMSK           | —            | ECCPMX <sup>(1)</sup>          | CCP2MX         |

| bit 7         |                  |                                                          |              |                   |              |                                | bit (          |

| Legend:       |                  | P = Programm                                             | ahle hit     |                   |              |                                |                |

| R = Readabl   | le hit           | W = Writable b                                           |              | U = Unimplem      | ented hit re | ad as '0'                      |                |

| -n = Value at |                  | '1' = Bit is set                                         | nt -         | '0' = Bit is clea |              | x = Bit is unkn                | own            |

|               |                  |                                                          |              |                   | licu         |                                | OWIT           |

| bit 7         | MCLRE: MCI       | _R Pin Enable b                                          | it           |                   |              |                                |                |

|               |                  | n is enabled; RG<br>t pin is enabled;                    |              |                   |              |                                |                |

| bit 6-4       | Unimplemen       | ted: Read as '0                                          | 3            |                   |              |                                |                |

| bit 3         | MSSPMSK:         | MSSP V3 7-Bit /                                          | Address Ma   | sking Mode Enal   | ble bit      |                                |                |

|               |                  | ress Masking m<br>ress Masking m                         |              |                   |              |                                |                |

| bit 2         |                  | ted: Read as '0                                          |              |                   |              |                                |                |

| bit 1         | -                | CCP MUX bit <sup>(1)</sup>                               |              |                   |              |                                |                |

|               | 1 =              |                                                          |              |                   |              |                                |                |

|               |                  |                                                          |              |                   |              | RE6, and CCP7<br>RE4, and CCP9 |                |

|               | 0 =              |                                                          |              |                   |              | RH7, and CCP7                  |                |

|               |                  |                                                          |              |                   |              | RH5, and CCP9                  |                |

| bit 0         | CCP2MX: EC       | CP2 MUX bit                                              |              |                   |              |                                |                |

|               | 0 = ECCP2 i      | s multiplexed wi<br>s multiplexed w<br>licrocontroller m | ith RB3 in I | Extended Microc   | ontroller mo | de; ECCP2 is mu                | Iltiplexed wit |

| Note 1: U     | Inimplemented or | n 64-pin devices                                         | (PIC18F6X    | (K22), read as '0 | ,<br>-       |                                |                |

# REGISTER 28-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

2: Not implemented on 32K devices (PIC18F65K22 and PIC18F85K22).

| R/C-1              | R/C-1              | R/C-1                              | R/C-1                | R/C-1         | R/C-1           | R/C-1           | R/C-1 |

|--------------------|--------------------|------------------------------------|----------------------|---------------|-----------------|-----------------|-------|

| CP7 <sup>(1)</sup> | CP6 <sup>(1)</sup> | CP5 <sup>(1)</sup>                 | CP4 <sup>(1)</sup>   | CP3           | CP2             | CP1             | CP0   |

| bit 7              |                    |                                    |                      |               |                 |                 | bit 0 |

| Legend:            |                    | C = Clearable                      | hit                  |               |                 |                 |       |

| R = Readabl        | o hit              | W = Writable                       |                      | II – Unimploy | mented bit, rea | ad as '0'       |       |

| -n = Value at      |                    | '1' = Bit is set                   |                      | 0 = Onimpler  |                 | x = Bit is unkr |       |

|                    | IPOR               | I = DILIS SE                       | L                    |               | areu            | X = BILIS UNKI  | IOWII |

| bit 7              | CP7: Code F        | Protection bit <sup>(1)</sup>      |                      |               |                 |                 |       |

|                    | 1 = Block 7 i      | s not code-prot                    | ected <sup>(2)</sup> |               |                 |                 |       |

|                    |                    | s code-protecte                    | ed(2)                |               |                 |                 |       |

| bit 6              | CP6: Code F        | Protection bit <sup>(1)</sup>      |                      |               |                 |                 |       |

|                    |                    | s not code-prot                    |                      |               |                 |                 |       |

|                    |                    | s code-protecte                    | ed(2)                |               |                 |                 |       |

| bit 5              |                    | Protection bit <sup>(1)</sup>      | (2)                  |               |                 |                 |       |

|                    |                    | s not code-prot<br>s code-protecte |                      |               |                 |                 |       |

| <b>b</b> :t 4      |                    | Protection bit <sup>(1)</sup>      |                      |               |                 |                 |       |

| bit 4              |                    | s not code-prot                    | ootod(2)             |               |                 |                 |       |

|                    |                    | s code-protecte                    |                      |               |                 |                 |       |

| bit 3              | CP3: Code F        | Protection bit                     |                      |               |                 |                 |       |

|                    | 1 = Block 3 i      | s not code-prot                    | ected <sup>(2)</sup> |               |                 |                 |       |

|                    | 0 = Block 3 i      | s code-protecte                    | ed <sup>(2)</sup>    |               |                 |                 |       |

| bit 2              | CP2: Code F        |                                    |                      |               |                 |                 |       |

|                    |                    | s not code-prot                    |                      |               |                 |                 |       |

|                    |                    | s code-protecte                    | ed(2)                |               |                 |                 |       |

| bit 1              | CP1: Code F        |                                    | (2)                  |               |                 |                 |       |

|                    |                    | s not code-prot<br>s code-protecte |                      |               |                 |                 |       |

| bit 0              | CP0: Code F        | Protection bit                     |                      |               |                 |                 |       |

|                    |                    | s not code-prot                    |                      |               |                 |                 |       |

|                    | 0 = Block 0 i      | s code-protecte                    | ed <sup>(2)</sup>    |               |                 |                 |       |

| Note 1: T          | his bit is availab | le only on PIC1                    | 8F67K22 and          | I PIC18F87K22 | devices.        |                 |       |

# REGISTER 28-8: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

- This bit is available only on PIC18F67K22 and PIC18F87K22 devices. NOTE 1:

- 2: For the memory size of the blocks, see Figure 28-6.

| RRNCF                                                          | Rotate Ri                                                           | ight f (No                                                                    | Carry                                                      | )                                                 |  |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| Syntax:                                                        | RRNCF                                                               | f {,d {,a}}                                                                   |                                                            |                                                   |  |  |  |  |  |

| Operands:                                                      | $0 \le f \le 253$<br>$d \in [0,1]$<br>$a \in [0,1]$                 | 5                                                                             |                                                            |                                                   |  |  |  |  |  |

| Operation:                                                     |                                                                     | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$ |                                                            |                                                   |  |  |  |  |  |

| Status Affected:                                               | N, Z                                                                |                                                                               |                                                            |                                                   |  |  |  |  |  |

| Encoding:                                                      | 0100                                                                | 00da                                                                          | fff                                                        | f ffff                                            |  |  |  |  |  |

| Description:                                                   | one bit to<br>is placed                                             | the right.                                                                    | lf 'd' is<br>is '1',                                       | ' are rotated<br>'0', the result<br>the result is |  |  |  |  |  |

|                                                                | selected,                                                           | n the bank                                                                    | the BS                                                     | nk will be<br>SR value. If 'a'<br>e selected as   |  |  |  |  |  |

|                                                                | set is ena<br>in Indexed<br>mode whe<br>Section 2<br>Bit-Orien      | bled, this<br>d Literal O<br>enever $f \le$<br>29.2.3 "By                     | instruc<br>ffset A<br>95 (5F<br>r <b>te-Ori</b><br>ictions | ented and<br>s in Indexed                         |  |  |  |  |  |

|                                                                | Г                                                                   | ► re                                                                          | egister                                                    | f                                                 |  |  |  |  |  |

| Words:                                                         | 1                                                                   |                                                                               |                                                            |                                                   |  |  |  |  |  |

| Cycles:                                                        | 1                                                                   |                                                                               |                                                            |                                                   |  |  |  |  |  |

| Q Cycle Activity:                                              |                                                                     |                                                                               |                                                            |                                                   |  |  |  |  |  |

| Q1                                                             | Q2                                                                  | Q                                                                             | 3                                                          | Q4                                                |  |  |  |  |  |

| Decode                                                         | Read                                                                | Proce                                                                         | ess                                                        | Write to                                          |  |  |  |  |  |

|                                                                | register 'f'                                                        | Dat                                                                           | а                                                          | destination                                       |  |  |  |  |  |

|                                                                |                                                                     |                                                                               |                                                            | destination                                       |  |  |  |  |  |

| Example 1:                                                     | RRNCF                                                               | REG, 1                                                                        | , 0                                                        | destination                                       |  |  |  |  |  |

| Before Instruc<br>REG<br>After Instructi                       | ction<br>= 1101<br>ion                                              | 0111                                                                          | , 0                                                        |                                                   |  |  |  |  |  |

| Before Instruct<br>REG<br>After Instructi<br>REG               | ction<br>= 1101<br>ion<br>= 1110                                    | 0111<br>1011                                                                  |                                                            |                                                   |  |  |  |  |  |

| Before Instruct<br>REG<br>After Instructi<br>REG<br>Example 2: | ction<br>= 1101<br>ion<br>= 1110<br>RRNCF                           | 0111<br>1011                                                                  |                                                            |                                                   |  |  |  |  |  |

| Before Instruct<br>REG<br>After Instructi<br>REG               | ction<br>= 1101<br>ion<br>= 1110<br>RRNCF<br>ction<br>= ?<br>= 1101 | 0111<br>1011                                                                  |                                                            |                                                   |  |  |  |  |  |

| SETF                                                          | Set f                                                                                                     |                                                                    |                                                                   |                                                |  |  |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------|--|--|--|

| Syntax:                                                       | SETF f{,a                                                                                                 | a}                                                                 |                                                                   |                                                |  |  |  |

| Operands:                                                     | $0 \leq f \leq 255$                                                                                       |                                                                    |                                                                   |                                                |  |  |  |

|                                                               | a ∈ [0,1]                                                                                                 |                                                                    |                                                                   |                                                |  |  |  |

| Operation:                                                    | $FFh\tof$                                                                                                 |                                                                    |                                                                   |                                                |  |  |  |

| Status Affected:                                              | None                                                                                                      |                                                                    |                                                                   |                                                |  |  |  |

| Encoding:                                                     | 0110                                                                                                      | 100a                                                               | ffff                                                              | ffff                                           |  |  |  |

| Description:                                                  | The conten<br>are set to F                                                                                |                                                                    | specified r                                                       | register                                       |  |  |  |

|                                                               | lf 'a' is '0', ti<br>lf 'a' is '1', ti<br>GPR bank.                                                       |                                                                    |                                                                   |                                                |  |  |  |

|                                                               | If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>Section 29<br>Bit-Oriente<br>Literal Offs | ed, this ir<br>_iteral Off<br>ever f ≤ 9<br>.2.3 "Byt<br>d Instruc | nstruction<br>fset Addre<br>95 (5Fh). S<br>e-Oriente<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |

| Words:                                                        | 1                                                                                                         |                                                                    |                                                                   |                                                |  |  |  |

| Cycles:                                                       | 1                                                                                                         |                                                                    |                                                                   |                                                |  |  |  |

| Q Cycle Activity:                                             |                                                                                                           |                                                                    |                                                                   |                                                |  |  |  |

| Q1                                                            | Q2                                                                                                        | Q3                                                                 |                                                                   | Q4                                             |  |  |  |

| Decode                                                        | Read<br>register 'f'                                                                                      | Proces<br>Data                                                     |                                                                   | Write<br>gister 'f'                            |  |  |  |

| Example:<br>Before Instruct<br>REG<br>After Instructio<br>REG | = 5A                                                                                                      |                                                                    | 8,1                                                               |                                                |  |  |  |

### 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K22 Family (Industrial/Extended) (Continued)

|              | 7K22 Family<br>Istrial/Extended) | Standard (<br>Operating f | •    | •     | -40°C ≤ Ta ≤ | ns (unless otherwise stated)<br>$40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                      |  |

|--------------|----------------------------------|---------------------------|------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Param<br>No. | Device                           | Тур                       | Max  | Units |              | Conditions                                                                                                                                  |                                                      |  |

|              | Supply Current (IDD) Cont.       | (2,3)                     |      |       |              |                                                                                                                                             |                                                      |  |

|              | All devices                      | 2.1                       | 5.5  | μA    | -40°C        |                                                                                                                                             |                                                      |  |

|              |                                  | 2.1                       | 5.7  | μA    | +25°C        | VDD = 1.8V <sup>(4)</sup>                                                                                                                   |                                                      |  |

|              |                                  | 2.2                       | 6.0  | μA    | +85°C        | Regulator Disabled                                                                                                                          |                                                      |  |

|              |                                  | 10                        | 20   | μA    | +125°C       |                                                                                                                                             |                                                      |  |

|              | All devices                      | 3.7                       | 7.5  | μA    | -40°C        |                                                                                                                                             |                                                      |  |

|              |                                  | 3.9                       | 7.8  | μA    | +25°C        | VDD = 3.3V <sup>(4)</sup>                                                                                                                   | Fosc = 31 kHz                                        |  |

|              |                                  | 3.9                       | 8.5  | μA    | +85°C        | Regulator Disabled                                                                                                                          | ( <b>RC_IDLE</b> mode,<br>LF-INTOSC)                 |  |

|              |                                  | 12                        | 24   | μA    | +125°C       |                                                                                                                                             | L                                                    |  |

|              | All devices                      | 70                        | 180  | μA    | -40°C        |                                                                                                                                             |                                                      |  |