Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 69                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85k22t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 64/80-Pin, High-Performance, 1-Mbit Enhanced Flash MCUs with 12-Bit A/D and nanoWatt XLP Technology

#### Low-Power Features:

- Power-Managed modes:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- Two-Speed Oscillator Start-up

- Fail-Safe Clock Monitor

- Power-Saving Peripheral Module Disable (PMD)

- Ultra Low-Power Wake-up

- Fast Wake-up, 1 μs Typical

- Low-Power WDT, 300 nA Typical

- Ultra Low 50 nA Input Leakage

- Run mode Currents Down to 5.5 μA, Typical

- Idle mode Currents Down to 1.7 μA Typical

- Sleep mode Currents Down to Very Low 20 nA, Typical

- RTCC Current Downs to Very Low 700 nA, Typical

#### **Special Microcontroller Features:**

- Operating Voltage Range: 1.8V to 5.5V

- On-Chip 3.3V Regulator

- · Operating Speed up to 64 MHz

- Up to 128 Kbytes On-Chip Flash Program Memory

- Data EEPROM of 1,024 Bytes

- 4K x 8 General Purpose Registers (SRAM)

- 10,000 Erase/Write Cycle Flash Program Memory, Minimum

- 1,000,000 Erase/write Cycle Data EEPROM Memory, Typical

- · Flash Retention: 40 Years, Minimum

- Three Internal Oscillators: LF-INTRC (31 kHz), MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

- Self-Programmable under Software Control

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s (about 70 minutes)

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug via Two Pins

- Programmable:

- BOR

- LVD

|             | Prog             | ram Memory                    | Data Memory     |                   |     | 12-Bit  | CCP/     | MSSP |     | SP                          | Е     | tors        | t, e               | Bus      | _    |      |

|-------------|------------------|-------------------------------|-----------------|-------------------|-----|---------|----------|------|-----|-----------------------------|-------|-------------|--------------------|----------|------|------|

| Device      | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | I/O A/D | A/D ECCP |      | SPI | Master<br>I <sup>2</sup> C™ | EUSAR | Comparators | Timers<br>8/16-Bit | External | CTMU | RTCC |

| PIC18F65K22 | 32K              | 16,383                        | 2K              | 1K                | 53  | 16      | 5/3      | 2    | Y   | Y                           | 2     | 3           | 4/4                | Ν        | Y    | Y    |

| PIC18F66K22 | 64K              | 32,768                        | 4K              | 1K                | 53  | 16      | 7/3      | 2    | Y   | Y                           | 2     | 3           | 6/5                | Ν        | Y    | Y    |

| PIC18F67K22 | 128K             | 65,536                        | 4K              | 1K                | 53  | 16      | 7/3      | 2    | Y   | Y                           | 2     | 3           | 6/5                | Ν        | Y    | Y    |

| PIC18F85K22 | 32K              | 16,383                        | 2K              | 1K                | 69  | 24      | 5/3      | 2    | Y   | Y                           | 2     | 3           | 4/4                | Y        | Y    | Y    |

| PIC18F86K22 | 64K              | 32,768                        | 4K              | 1K                | 69  | 24      | 7/3      | 2    | Y   | Y                           | 2     | 3           | 6/5                | Y        | Y    | Y    |

| PIC18F87K22 | 128K             | 65,536                        | 4K              | 1K                | 69  | 24      | 7/3      | 2    | Y   | Y                           | 2     | 3           | 6/5                | Y        | Y    | Y    |

#### 4.0 POWER-MANAGED MODES

The PIC18F87K22 family of devices offers a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (such as battery-powered devices).

There are three categories of power-managed mode:

- Run modes

- Idle modes

- · Sleep mode

There is an Ultra Low-Power Wake-up (ULPWU) for waking from the Sleep mode.

These categories define which portions of the device are clocked, and sometimes, at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block). The Sleep mode does not use a clock source.

The ULPWU mode, on the RA0 pin, enables a slow falling voltage to generate a wake-up, even from Sleep, without excess current consumption. (See **Section 4.7 "Ultra Low-Power Wake-up"**.)

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices. This feature allows the controller to use the SOSC oscillator instead of the primary one. Another power-saving feature is Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions:

- · Will the CPU be clocked or not

- · What will be the clock source

The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

#### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits select one of three clock sources for power-managed modes. Those sources are:

- The primary clock as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the SOSC oscillator)

- The internal oscillator block (for LF-INTOSC modes)

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These considerations are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entering the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current and impending mode, a change to a power-managed mode does not always require setting all of the previously discussed bits. Many transitions can be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured as desired, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | oscco                   | ON Bits  | Module  | Clocking    | Available Clock and Oscillator Source                                                         |

|----------|-------------------------|----------|---------|-------------|-----------------------------------------------------------------------------------------------|

| Mode     | IDLEN<7> <sup>(1)</sup> | SCS<1:0> | CPU     | Peripherals | Available Clock and Oscillator Source                                                         |

| Sleep    | 0                       | N/A      | Off Off |             | None – All clocks are disabled                                                                |

| PRI_RUN  | N/A                     | 00       | Clocked | Clocked     | Primary – XT, LP, HS, EC, RC and PLL modes.<br>This is the normal, Full-Power Execution mode. |

| SEC_RUN  | N/A                     | 01       | Clocked | Clocked     | Secondary – SOSC Oscillator                                                                   |

| RC_RUN   | N/A                     | 1x       | Clocked | Clocked     | Internal oscillator block <sup>(2)</sup>                                                      |

| PRI_IDLE | 1                       | 00       | Off     | Clocked     | Primary – LP, XT, HS, RC, EC                                                                  |

| SEC_IDLE | 1                       | 01       | Off     | Clocked     | Secondary – SOSC oscillator                                                                   |

| RC_IDLE  | 1                       | lx       | Off     | Clocked     | Internal oscillator block <sup>(2)</sup>                                                      |

TABLE 4-1:POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

<sup>2:</sup> Includes INTOSC (HF-INTOSC and MG-INTOSC) and INTOSC postscaler, as well as the LF-INTOSC source.

### 4.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable. The HF-INTOSC and MF-INTOSC are termed as INTOSC in this chapter.

Three bits indicate the current clock source and its status, as shown in Table 4-2. The three bits are:

- OSTS (OSCCON<3>)

- HFIOFS (OSCCON<2>)

- SOSCRUN (OSCCON2<6>)

TABLE 4-2: SYSTEM CLOCK INDICATOR

| Main Clock Source                                    | OSTS | HFIOFSor<br>MFIOFS | SOSCRUN |

|------------------------------------------------------|------|--------------------|---------|

| Primary Oscillator                                   | 1    | 0                  | 0       |

| INTOSC (HF-INTOSC or<br>MF-INTOSC)                   | 0    | 1                  | 0       |

| Secondary Oscillator                                 | 0    | 0                  | 1       |

| MF-INTOSC or<br>HF-INTOSC as Primary<br>Clock Source | 1    | 1                  | 0       |

| LF-INTOSC is Running or INTOSC is Not Yet Stable     | 0    | 0                  | 0       |

When the OSTS bit is set, the primary clock is providing the device clock. When the HFIOFS or MFIOFS bit is set, the INTOSC output is providing a stable 16 MHz clock source to a divider that actually drives the device clock. When the SOSCRUN bit is set, the SOSC oscillator is providing the clock. If none of these bits are set, either the LF-INTOSC clock source is clocking the device or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC<3:0> Configuration bits (CONFIG1H<3:0>), then the OSTS and HFIOFS or MFIOFS bits can be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 16 MHz output. Entering another INTOSC power-managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. At a lower VDD, it is possible to select a higher clock speed than is supportable by that VDD. Improper device operation may result if the VDD/ Fosc specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode or one of the Idle modes, depending on the setting of the IDLEN bit.

#### 4.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting.

#### 4.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

#### 4.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, Full-Power Execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled. (For details, see **Section 28.4 "Two-Speed Start-up"**.) In this mode, the OSTS bit is set. The HFIOFS or MFIOFS bit may be set if the internal oscillator block is the primary clock source. (See **Section 3.2 "Control Registers"**.)

#### 4.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock-switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the SOSC oscillator. This enables lower power consumption while retaining a high-accuracy clock source.

SEC\_RUN mode is entered by setting the SCS<1:0> bits to '01'. The device clock source is switched to the SOSC oscillator (see Figure 4-1), the primary oscillator is shut down, the SOSCRUN bit (OSCCON2<6>) is set and the OSTS bit is cleared.

| Note: | The SOSC oscillator can be enabled by setting the SOSCGO bit (OSCCON2<3>). If this bit is set, the clock switch to the SEC_RUN mode can switch immediately |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | once SCS<1:0> are set to '01'.                                                                                                                             |

On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the SOSC oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the SOSCRUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up and the SOSC oscillator continues to run.

#### 6.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit (CONFIG4L<0>). When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.4 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR                               |

|-----------------|--------------------------------------------------|

| •               | ;SAVED IN FAST REGISTER                          |

| SUB1 •          | ;STACK                                           |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK |

#### 6.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the Program Counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value, 'nn', to the calling function.

The offset value (in WREG) specifies the number of bytes that the Program Counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

#### 6.1.5.2 Table Reads

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored, two bytes per program word, while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory, one byte at a time.

The table read operation is discussed further in **Section 7.1 "Table Reads and Table Writes**".

#### 8.1 External Memory Bus Control

The operation of the interface is controlled by the MEMCON register (Register 8-1). This register is available in all program memory operating modes except Microcontroller mode. In this mode, the register is disabled and cannot be written to.

The EBDIS bit (MEMCON<7>) controls the operation of the bus and related port functions. Clearing EBDIS enables the interface and disables the I/O functions of the ports, as well as any other functions multiplexed to those pins. Setting the bit enables the I/O ports and other functions, but allows the interface to override everything else on the pins when an external memory operation is required. By default, the external bus is always enabled and disables all other I/O. The operation of the EBDIS bit is also influenced by the program memory mode being used. This is discussed in more detail in Section 8.5 "Program Memory Modes and the External Memory Bus".

The WAIT bits allow for the addition of Wait states to external memory operations. The use of these bits is discussed in **Section 8.3 "Wait States**".

The WM bits select the particular operating mode used when the bus is operating in 16-Bit Data Width mode. These bits are discussed in more detail in **Section 8.6 "16-Bit Data Width Modes"**. These bits have no effect when an 8-Bit Data Width mode is selected.

#### REGISTER 8-1: MEMCON: EXTERNAL MEMORY BUS CONTROL REGISTER<sup>(1)</sup>

| R/W-0        | U-0                                                                            | R/W-0                                                                                              | R/W-0           | U-0               | U-0              | R/W-0           | R/W-0            |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|------------------|--|--|--|--|

| EBDIS        |                                                                                | WAIT1                                                                                              | WAIT0           | _                 | —                | WM1             | WM0              |  |  |  |  |

| bit 7        |                                                                                | ·                                                                                                  |                 |                   |                  | -               | bit 0            |  |  |  |  |

|              |                                                                                |                                                                                                    |                 |                   |                  |                 |                  |  |  |  |  |

| Legend:      |                                                                                |                                                                                                    |                 |                   |                  |                 |                  |  |  |  |  |

| R = Readal   | ble bit                                                                        | W = Writable                                                                                       | bit             | U = Unimplem      | nented bit, read | 1 as '0'        |                  |  |  |  |  |

| -n = Value a | at POR                                                                         | '1' = Bit is set                                                                                   |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown             |  |  |  |  |

|              |                                                                                |                                                                                                    |                 |                   |                  |                 |                  |  |  |  |  |

| bit 7        | EBDIS: Exter                                                                   | nal Bus Disabl                                                                                     | e bit           |                   |                  |                 |                  |  |  |  |  |

|              | 1 = External                                                                   | bus is enabled                                                                                     | when microco    | ontroller access  | es external me   | emory; otherwis | se, all external |  |  |  |  |

|              |                                                                                | rs are mapped                                                                                      |                 |                   |                  |                 |                  |  |  |  |  |

|              | 0 = External                                                                   | bus is always e                                                                                    | enabled, I/O po | orts are disabled | 1                |                 |                  |  |  |  |  |

| bit 6        | Unimplemen                                                                     | ted: Read as '                                                                                     | )'              |                   |                  |                 |                  |  |  |  |  |

| bit 5-4      | WAIT<1:0>:                                                                     | Table Reads ar                                                                                     | d Writes Bus    | Cycle Wait Cour   | nt bits          |                 |                  |  |  |  |  |

|              | 11 = Table rea                                                                 | ads and writes                                                                                     | will wait 0 TCY |                   |                  |                 |                  |  |  |  |  |

|              | 10 = Table rea                                                                 | ads and writes                                                                                     | will wait 1 TCY |                   |                  |                 |                  |  |  |  |  |

|              |                                                                                | ads and writes                                                                                     |                 |                   |                  |                 |                  |  |  |  |  |

|              | 00 = Table re                                                                  | ads and writes                                                                                     | will wait 3 TCY |                   |                  |                 |                  |  |  |  |  |

| bit 3-2      | Unimplemen                                                                     | ted: Read as '                                                                                     | )'              |                   |                  |                 |                  |  |  |  |  |

| bit 1-0      | WM<1:0>: TE                                                                    | WM<1:0>: TBLWT Operation with 16-Bit Data Bus Width Select bits                                    |                 |                   |                  |                 |                  |  |  |  |  |

|              | 1x = Word Write mode: TABLAT word output; WRH is active when TABLAT is written |                                                                                                    |                 |                   |                  |                 |                  |  |  |  |  |

|              |                                                                                | 01 = Byte Select mode: TABLAT data is copied on both MSB and LSB; WRH and (UB or LB) will activate |                 |                   |                  |                 |                  |  |  |  |  |

|              | 00 = Byte W                                                                    | rite mode: TAB                                                                                     | LAT data is co  | pied on both MS   | SB and LSB; V    | VRH or WRL wi   | ill activate     |  |  |  |  |

|              | l la incalana anta da                                                          | un C.4 min devile                                                                                  |                 |                   | 3                |                 |                  |  |  |  |  |

Note 1: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

#### REGISTER 11-21: IPR6: PERIPHERAL INTERRUPT PRIORITY REGISTER 6

| U-0               | U-0                                 | U-0                 | R/W-1      | U-0              | R/W-1            | R/W-1           | R/W-1  |

|-------------------|-------------------------------------|---------------------|------------|------------------|------------------|-----------------|--------|

| _                 | _                                   |                     | EEIP       |                  | CMP3IP           | CMP2IP          | CMP1IP |

| bit 7             |                                     |                     | •          | -                |                  |                 | bit 0  |

| Legend:           |                                     |                     |            |                  |                  |                 |        |

| R = Readab        | le bit                              | W = Writable        | bit        | U = Unimpler     | mented bit, read | 1 as '0'        |        |

| -n = Value a      | It POR                              | '1' = Bit is set    |            | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

|                   |                                     |                     |            |                  |                  |                 |        |

| bit 7-5           | Unimplem                            | ented: Read as '    | 0'         |                  |                  |                 |        |

| bit 4             | EEIP: EE li                         | nterrupt Priority b | it         |                  |                  |                 |        |

|                   | 1 = High p                          | riority             |            |                  |                  |                 |        |

|                   | 0 = Low pr                          | riority             |            |                  |                  |                 |        |

| bit 3             | Unimplem                            | ented: Read as '    | 0'         |                  |                  |                 |        |

| bit 2             | CMP3IP: C                           | MP3 Interrupt Pr    | iority bit |                  |                  |                 |        |

|                   | 1 = High p                          | riority             |            |                  |                  |                 |        |

|                   | 0 = Low priority                    |                     |            |                  |                  |                 |        |

| bit 1             | CMP2IP: CMP2 Interrupt Priority bit |                     |            |                  |                  |                 |        |

| 1 = High priority |                                     |                     |            |                  |                  |                 |        |

|                   | 0 = Low pr                          | riority             |            |                  |                  |                 |        |

| bit 0             |                                     | MP1 Interrupt Pr    | iority bit |                  |                  |                 |        |

|                   | 1 = High p                          |                     |            |                  |                  |                 |        |

|                   | 0 = Low pr                          | riority             |            |                  |                  |                 |        |

#### REGISTER 12-1: PADCFG1: PAD CONFIGURATION REGISTER

| R/W-0                                                                                        | R/W-0                                                                                                      | R/W-0                      | U-0                    | U-0             | R/W-0                    | R/W-0                    | U-0   |  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|-----------------|--------------------------|--------------------------|-------|--|--|

| RDPU                                                                                         | REPU                                                                                                       | RJPU <sup>(2)</sup>        | _                      | _               | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | _     |  |  |

| bit 7                                                                                        |                                                                                                            | •<br>•                     |                        |                 |                          |                          | bit 0 |  |  |

|                                                                                              |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

| Legend:                                                                                      |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                         |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

| -n = Value at                                                                                | POR                                                                                                        | '1' = Bit is set           | :                      | '0' = Bit is cl | eared                    | x = Bit is unknown       |       |  |  |

|                                                                                              |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

| bit 7                                                                                        | RDPU: POR                                                                                                  | RTD Pull-up Ena            | able bit               |                 |                          |                          |       |  |  |

|                                                                                              | 1 = PORTD pull-up resistors are enabled by individual port latch values                                    |                            |                        |                 |                          |                          |       |  |  |

|                                                                                              | 0 = All PORTD pull-up resistors are disabled                                                               |                            |                        |                 |                          |                          |       |  |  |

| bit 6                                                                                        | REPU: POR                                                                                                  | TE Pull-up Ena             | able bit               |                 |                          |                          |       |  |  |

|                                                                                              |                                                                                                            |                            |                        |                 | I port latch values      |                          |       |  |  |

|                                                                                              | 0 = All POR                                                                                                | TE pull-up resis           | stors are disa         | bled            |                          |                          |       |  |  |

| bit 5                                                                                        | RJPU: POR                                                                                                  | TJ Pull-up Ena             | ble bit <sup>(2)</sup> |                 |                          |                          |       |  |  |

|                                                                                              |                                                                                                            |                            |                        |                 | port latch values        |                          |       |  |  |

|                                                                                              | 0 = All POR                                                                                                | TJ pull-up resis           | tors are disa          | bled            |                          |                          |       |  |  |

| bit 4-3                                                                                      | Unimpleme                                                                                                  | nted: Read as              | '0'                    |                 |                          |                          |       |  |  |

| bit 2-1                                                                                      | RTSECSEL                                                                                                   | <1:0>: RTCC 8              | Seconds Cloo           | k Output Sele   | ect bits <sup>(1)</sup>  |                          |       |  |  |

|                                                                                              | 11 = Reserv                                                                                                | ed; do not use             |                        |                 |                          |                          |       |  |  |

| 10 = RTCC source clock is selected for the RTCC pin (the pin can be LF-INTOSC or SOSC, depen |                                                                                                            |                            |                        |                 |                          | depending                |       |  |  |

| on the RTCOSC (CONFIG3L<1>) bit setting)                                                     |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

|                                                                                              | 01 = RTCC seconds clock is selected for the RTCC pin<br>00 = RTCC alarm pulse is selected for the RTCC pin |                            |                        |                 |                          |                          |       |  |  |

| hit O                                                                                        |                                                                                                            | Unimplemented: Read as '0' |                        |                 |                          |                          |       |  |  |

| bit 0                                                                                        | Unimpleme                                                                                                  | nted: Read as              | U                      |                 |                          |                          |       |  |  |

|                                                                                              |                                                                                                            |                            |                        |                 |                          |                          |       |  |  |

- **Note 1:** To enable the actual RTCC output, the RTCOE (RTCCFG<2>) bit must be set.

- 2: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

| Pin Name       | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                              |  |  |

|----------------|----------|-----------------|-----|-------------|------------------------------------------------------------------------------------------|--|--|

| RA0/AN0/ULPWU  | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                       |  |  |

|                |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input is enabled.                              |  |  |

|                | AN0      | 1               | I   | ANA         | A/D Input Channel 0. Default input configuration on POR; does not affect digital output. |  |  |

|                | ULPWU    | 1               | I   | ANA         | Ultra Low-Power Wake-up input.                                                           |  |  |

| RA1/AN1        | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                       |  |  |

|                |          | 1               | I   | TTL         | PORTA<1> data input; disabled when analog input is enabled.                              |  |  |

|                | AN1      | 1               | I   | ANA         | A/D Input Channel 1. Default input configuration on POR; does not affect digital output. |  |  |

| RA2/AN2/VREF-  | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input.                                       |  |  |

|                |          | 1               | Ι   | TTL         | PORTA<2> data input; disabled when analog functions are enabled.                         |  |  |

|                | AN2      | 1               | Ι   | ANA         | A/D Input Channel 2. Default input configuration on POR.                                 |  |  |

|                | VREF-    | 1               | -   | ANA         | A/D and comparator low reference voltage input.                                          |  |  |

| RA3/AN3/VREF+  | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                       |  |  |

|                |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input is enabled.                              |  |  |

|                | AN3      | 1               | Ι   | ANA         | A/D Input Channel 3. Default input configuration on POR.                                 |  |  |

|                | VREF+    | 1               | -   | ANA         | A/D and comparator high reference voltage input.                                         |  |  |

| RA4/T0CKI      | RA4      | 0               | 0   | DIG         | LATA<4> data output.                                                                     |  |  |

|                |          | 1               | Ι   | ST          | PORTA<4> data input. Default configuration on POR.                                       |  |  |

|                | TOCKI    | x               | Ι   | ST          | Timer0 clock input.                                                                      |  |  |

| RA5/AN4/T1CKI/ | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                       |  |  |

| T3G/HLVDIN     |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input is enabled.                              |  |  |

|                | AN4      | 1               | Ι   | ANA         | A/D Input Channel 4. Default configuration on POR.                                       |  |  |

|                | T1CKI    | x               | Ι   | ST          | Timer1 clock input.                                                                      |  |  |

|                | T3G      | x               | I   | ST          | Timer3 external clock gate input.                                                        |  |  |

|                | HLVDIN   | 1               | Ι   | ANA         | High/Low-Voltage Detect (HLVD) external trip point input.                                |  |  |

| OSC2/CLKO/RA6  | OSC2     | x               | 0   | ANA         | Main oscillator feedback output connection (HS, XT and LP modes).                        |  |  |

|                | CLKO     | x               | 0   | DIG         | System cycle clock output (Fosc/4, EC and INTOSC modes).                                 |  |  |

|                | RA6      | 0               | 0   | DIG         | LATA<6> data output; disabled when FOSC2 Configuration bit is set.                       |  |  |

|                |          | 1               | I   | TTL         | PORTA<6> data input; disabled when FOSC2 Configuration bit is set.                       |  |  |

| OSC1/CLKI/RA7  | OSC1     | x               | Ι   | ANA         | Main oscillator input connection (HS, XT and LP modes).                                  |  |  |

|                | CLKI     | x               | Ι   | ANA         | Main external clock source input (EC modes).                                             |  |  |

|                | RA7      | 0               | 0   | DIG         | LATA<7> data output; disabled when FOSC2 Configuration bit is set.                       |  |  |

|                |          | 1               | Ι   | TTL         | PORTA<7> data input; disabled when FOSC2 Configuration bit is set.                       |  |  |

TABLE 12-1: PORTA FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| <b>TABLE 12-2:</b> | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|--------------------|--------------------------------------------|

|--------------------|--------------------------------------------|

| Name   | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| ANCON0 | ANSEL7                | ANSEL6                | ANSEL5 | ANSEL4 | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** These bits are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as 'x'.

### 12.4 PORTC, TRISC and LATC Registers

PORTC is an eight-bit wide, bidirectional port. The corresponding Data Direction and Output Latch registers are TRISC and LATC. Only PORTC pins, RC2 through RC7, are digital only pins.

PORTC is multiplexed with ECCP, MSSP and EUSART peripheral functions (Table 12-5). The pins have Schmitt Trigger input buffers. The pins for ECCP, SPI and EUSART are also configurable for open-drain output whenever these functions are active. Open-drain configuration is selected by setting the SPIOD, CCPxOD and U1OD control bits in the registers, ODCON1 and ODCON3.

RC1 is normally configured as the default peripheral pin for the ECCP2 module. The assignment of ECCP2 is controlled by Configuration bit, CCP2MX (default state, CCP2MX = 1). When enabling peripheral functions, use care in defining TRIS bits for each PORTC pin. Some peripherals can override the TRIS bit to make a pin an output or input. Consult the corresponding peripheral section for the correct TRIS bit settings.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

| EXAMPLE 12-3: | INITIALIZING PORTC |

|---------------|--------------------|

|               |                    |

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATC  | ; Alternate method                         |

| CLRF  | LAIC  | , Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                    |

|       |       | ; RC<5:4> as outputs                       |

|       |       | ; RC<7:6> as inputs                        |

|       |       |                                            |

| Pin Name   | Function             | TRIS<br>Setting              | I/O | I/O<br>Type          | Description                                                                                                                                     |  |  |

|------------|----------------------|------------------------------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RC0/SOSCO/ | RC0                  | 0                            | 0   | DIG                  | LATC<0> data output.                                                                                                                            |  |  |

| SCLKI/     |                      | 1                            | Ι   | ST                   | PORTC<0> data input.                                                                                                                            |  |  |

|            | SOSCO                | 1                            | Ι   | ST                   | SOSC oscillator output.                                                                                                                         |  |  |

|            | SCLKI                | 1                            | Ι   | ST                   | Digital clock input; enabled when SOSC oscillator is disabled.                                                                                  |  |  |

| RC1/SOSCI/ | RC1                  | 0 O DIG LATC<1> data output. |     |                      |                                                                                                                                                 |  |  |

| ECCP2/P2A  | 1                    | Ι                            | ST  | PORTC<1> data input. |                                                                                                                                                 |  |  |

|            | SOSCI                | x                            | Ι   | ANA                  | SOSC oscillator input.                                                                                                                          |  |  |

|            | ECCP2 <sup>(1)</sup> | 0                            | 0   | DIG                  | ECCP2 compare output and ECCP2 PWM output; takes priority over port dat                                                                         |  |  |

|            |                      | 1                            | Ι   | ST                   | ECCP2 capture input.                                                                                                                            |  |  |

|            | P2A                  | 0                            | 0   | DIG                  | ECCP2 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown events; takes<br>priority over port data. |  |  |

| RC2/ECCP1/ | RC2                  | 0                            | 0   | DIG                  | LATC<2> data output.                                                                                                                            |  |  |

| P1A        |                      | 1                            | Ι   | ST                   | PORTC<2> data input.                                                                                                                            |  |  |

|            | ECCP1                | 0                            | 0   | DIG                  | ECCP1 compare output and ECCP1 PWM output; takes priority over port data.                                                                       |  |  |

|            |                      | 1                            | Ι   | ST                   | ECCP1 capture input.                                                                                                                            |  |  |

|            | P1A                  | 0                            | 0   | DIG                  | ECCP1 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown events; takes<br>priority over port data. |  |  |

#### TABLE 12-5: PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $I^2C = I^2C^{TM}$ /SMBus Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

#### REGISTER 19-3: CCPTMRS2: CCP TIMER SELECT REGISTER 2

| U-0   | U-0 | U-0 | R/W-0                   | U-0 | R/W-0                  | R/W-0   | R/W-0   |

|-------|-----|-----|-------------------------|-----|------------------------|---------|---------|

| —     | —   | —   | C10TSEL0 <sup>(1)</sup> | —   | C9TSEL0 <sup>(1)</sup> | C8TSEL1 | C8TSEL0 |

| bit 7 |     |     |                         |     |                        |         | bit 0   |

| Legend:                            |                  |                                    |                    |  |  |  |  |

|------------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit                   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR                  | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

|                                    |                  |                                    |                    |  |  |  |  |

| bit 7-5 Unimplemented: Read as '0' |                  |                                    |                    |  |  |  |  |

| DIT 7-5 | Unimplemented: Read as 10                                 |

|---------|-----------------------------------------------------------|

| bit 4   | C10TSEL0: CCP10 Timer Selection bit <sup>(1)</sup>        |

|         | 0 = CCP10 is based off of TMR1/TMR2                       |

|         | 1 = CCP10 is based off of TMR7/TMR2                       |

| bit 3   | Unimplemented: Read as '0'                                |

| bit 2   | C9TSEL0: CCP9 Timer Selection bit <sup>(1)</sup>          |

|         | 0 = CCP9 is based off of TMR1/TMR2                        |

|         | 1 = CCP9 is based off of TMR7/TMR4                        |

| bit 1-0 | C8TSEL<1:0>: CCP8 Timer Selection bits                    |

|         | On Non 32-Byte Device Variants:                           |

|         | 00 = CCP8 is based off of TMR1/TMR2                       |

|         | 01 = CCP8 is based off of TMR7/TMR4                       |

|         | 10 = CCP8 is based off of TMR7/TMR6                       |

|         | 11 = Reserved; do not use                                 |

|         | On 32-Byte Device Variants (PIC18F65K22 and PIC18F85K22): |

|         | 00 = CCP8 is based off of TMR1/TMR2                       |

|         | 01 = CCP8 is based off of TMR1/TMR4                       |

|         | 10 = CCP8 is based off of TMR1/TMR6                       |

|         | 11 - Decembed de petuse                                   |

- 11 = Reserved; do not use

- Note 1: This bit is unimplemented and reads as '0' on devices with 32 Kbytes of program memory (PIC18FX5K22).

#### 19.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP4 pin produces up to a 10-bit resolution PWM output. Since the CCP4 pin is multiplexed with a PORTC or PORTE data latch, the appropriate TRIS bit must be cleared to make the CCP4 pin an output.

| Note: | Clearing the CCP4CON register will force<br>the RC1 or RE7 output latch (depending<br>on device configuration) to the default low<br>level. This is not the PORTC or PORTE |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | I/O data latch.                                                                                                                                                            |

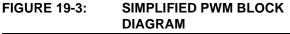

Figure 19-3 shows a simplified block diagram of the ECCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 19.4.3** "Setup for PWM Operation".

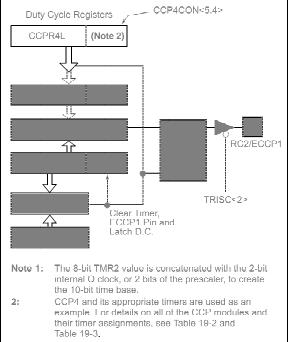

A PWM output (Figure 19-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 19-4: PWM OUTPUT

#### 19.4.1 PWM PERIOD

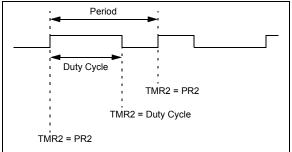

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 19-1:

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- · The CCP4 pin is set

(An exception: If PWM duty cycle = 0%, the CCP4 pin will not be set)

The PWM duty cycle is latched from CCPR4L into CCPR4H

| Note: | The     | Timer2       | postscalers        | (see     |

|-------|---------|--------------|--------------------|----------|

|       | Section | n 15.0 "Tin  | ner2 Module") a    | are not  |

|       | used ir | n the deter  | mination of the    | PWM      |

|       | frequen | cy. The po   | stscaler could be  | e used   |

|       | to have | a servo up   | odate rate at a di | ifferent |

|       | frequen | icy than the | PWM output.        |          |

#### REGISTER 21-4: SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0      | R/W-0                                                                                                                                                                     | R/W-0                                                                                                              | R/W-0        | R/W-0                     | R/W-0                         | R/W-0                | R/W-0                |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|-------------------------------|----------------------|----------------------|--|--|--|

| WCOL       | SSPOV                                                                                                                                                                     | SSPEN <sup>(1)</sup>                                                                                               | CKP          | SSPM3 <sup>(2)</sup>      | SSPM2 <sup>(2)</sup>          | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |  |

| bit 7      |                                                                                                                                                                           |                                                                                                                    |              |                           |                               |                      | bit (                |  |  |  |

| Legend:    |                                                                                                                                                                           |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

| R = Reada  | able bit                                                                                                                                                                  | W = Writable b                                                                                                     | it           | U = Unimple               | mented bit, rea               | d as '0'             |                      |  |  |  |

| -n = Value |                                                                                                                                                                           | '1' = Bit is set                                                                                                   |              | '0' = Bit is cle          |                               | x = Bit is unk       | nown                 |  |  |  |

|            |                                                                                                                                                                           | i Bitlo oot                                                                                                        |              |                           |                               |                      |                      |  |  |  |

| bit 7      | WCOL: Write                                                                                                                                                               | e Collision Detect                                                                                                 | bit          |                           |                               |                      |                      |  |  |  |

|            | In Master Tra                                                                                                                                                             |                                                                                                                    |              |                           | 2                             |                      |                      |  |  |  |

|            |                                                                                                                                                                           | to the SSPxBUF                                                                                                     |              |                           |                               | onditions were       | not valid for a      |  |  |  |

|            | transmis<br>0 = No collis                                                                                                                                                 | sion to be started                                                                                                 | d (must be c | leared in softwa          | are)                          |                      |                      |  |  |  |

|            | In Slave Trar                                                                                                                                                             |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            |                                                                                                                                                                           | PxBUF register is                                                                                                  | written whil | e it is still trans       | mitting the prev              | vious word (mus      | st be cleared i      |  |  |  |

|            | software                                                                                                                                                                  | -                                                                                                                  |              |                           | 5                             |                      |                      |  |  |  |

|            | 0 = No collis                                                                                                                                                             | sion                                                                                                               |              |                           |                               |                      |                      |  |  |  |

|            | <u>In Receive m</u><br>This is a "doi                                                                                                                                     | <u>node (Master or S</u><br>n't care" bit.                                                                         | lave modes   | <u>):</u>                 |                               |                      |                      |  |  |  |

| bit 6      | SSPOV: Receive Overflow Indicator bit                                                                                                                                     |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | In Receive mode:                                                                                                                                                          |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | -                                                                                                                                                                         | 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software) |              |                           |                               |                      |                      |  |  |  |

|            | software)<br>0 = No overflow                                                                                                                                              |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            |                                                                                                                                                                           |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | <u>In Transmit mode:</u><br>This is a "don't care" bit in Transmit mode.                                                                                                  |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

| bit 5      | SSPEN: Mas                                                                                                                                                                | ster Synchronous                                                                                                   | Serial Port  | Enable bit <sup>(1)</sup> |                               |                      |                      |  |  |  |

|            | 1 = Enables                                                                                                                                                               | the serial port an serial port and co                                                                              | d configures | the SDAx and              |                               | he serial port p     | ins                  |  |  |  |

| bit 4      |                                                                                                                                                                           | Release Control                                                                                                    | -            |                           |                               |                      |                      |  |  |  |

|            | In Slave mod                                                                                                                                                              |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | 1 = Releases clock                                                                                                                                                        |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | 0 = Holds clock low (clock stretch), used to ensure data setup time                                                                                                       |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            | In Master mo<br>Unused in th                                                                                                                                              |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

| bit 3-0    |                                                                                                                                                                           | : Master Synchro                                                                                                   | nous Serial  | Port Mode Sele            | ct bits <sup>(2)</sup>        |                      |                      |  |  |  |

|            | 1111 <b>= I<sup>2</sup>C S</b>                                                                                                                                            | Slave mode: 10-b                                                                                                   | it address w | ith Start and Sto         | op bit interrupts             | enabled              |                      |  |  |  |

|            | 1111 = $I^2C$ Slave mode: 10-bit address with Start and Stop bit interrupts enabled<br>1110 = $I^2C$ Slave mode: 7-bit address with Start and Stop bit interrupts enabled |                                                                                                                    |              |                           |                               |                      |                      |  |  |  |

|            |                                                                                                                                                                           | irmware Controll                                                                                                   |              |                           |                               |                      |                      |  |  |  |