Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 64MHz                                                                          |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 32KB (16K x 16)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 24x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f85k22t-i-ptrsl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Peripheral Highlights:**

- Up to Ten CCP/ECCP modules:

- Up to seven Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules

- Up to Eleven 8/16-Bit Timer/Counter modules:

- Timer0 8/16-bit timer/counter with 8-bit programmable prescaler

- Timer1,3 16-bit timer/counter

- Timer2,4,6,8 8-bit timer/counter

- Timer5,7 16-bit timer/counter for 64k and 128k parts

- Timer10,12 8-bit timer/counter for 64k and 128k parts

- Three Analog Comparators

- Configurable Reference Clock Output

- Hardware Real-Time Clock and Calendar (RTCC) module with Clock, Calendar and Alarm Functions

- Charge Time Measurement Unit (CTMU):

- Capacitance measurement for mTouch™ sensing solution

- Time measurement with 1 ns typical resolution

- Integrated temperature sensor

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

- Up to Four External Interrupts

- Two Master Synchronous Serial Port (MSSP) modules:

- 3/4-wire SPI (supports all four SPI modes)

- I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Two Enhanced Addressable USART modules:

- LIN/J2602 support

- Auto-Baud Detect (ABD)

- 12-Bit A/D Converter with up to 24 Channels:

- Auto-acquisition and Sleep operationDifferential input mode of operation

- Integrated Voltage Reference

| Pin Name                                                                                 | Pin Number      | Pin                  | Buffer                | Deceriation                                                                                                                 |  |  |  |  |

|------------------------------------------------------------------------------------------|-----------------|----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                                 | QFN/TQFP        | Туре                 | Туре                  | Description                                                                                                                 |  |  |  |  |

|                                                                                          |                 |                      |                       | PORTE is a bidirectional I/O port.                                                                                          |  |  |  |  |

| RE0/RD/P2D<br>RE0<br>RD<br>P2D                                                           | 2               | I/O<br> <br>0        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port read strobe.<br>EECP2 PWM Output D.                                                     |  |  |  |  |

| RE1/WR/P2C<br>RE1<br>WR<br>P2C                                                           | 1               | I/O<br>I<br>O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port write strobe.<br>ECCP2 PWM Output C.                                                    |  |  |  |  |

| RE2/ <u>CS</u> /P2B/CCP10<br>RE2<br>CS<br>P2B<br>CCP10 <sup>(3)</sup>                    | 64              | I/O<br> <br>0<br> /O | ST<br>TTL<br>—<br>S/T | Digital I/O.<br>Parallel Slave Port chip select.<br>ECCP2 PWM Output B.<br>Capture 10 input/Compare 10 output/PWM10 output. |  |  |  |  |

| RE3/P3C/CCP9/REFO<br>RE3<br>P3C<br>CCP9 <sup>(3,4)</sup><br>REFO                         | 63              | I/O<br>O<br>I/O<br>O | ST<br><br>S/T<br>     | Digital I/O.<br>ECCP3 PWM Output C.<br>Capture 9 input/Compare 9 output/PWM9 output.<br>Reference clock out.                |  |  |  |  |

| RE4/P3B/CCP8<br>RE4<br>P3B<br>CCP8 <sup>(4)</sup>                                        | 62              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP3 PWM Output B.<br>Capture 8 input/Compare 8 output/PWM8 output.                                        |  |  |  |  |

| RE5/P1C/CCP7<br>RE5<br>P1C<br>CCP7 <sup>(4)</sup>                                        | 61              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP1 PWM Output C.<br>Capture 7 input/Compare 7 output/PWM7 output.                                        |  |  |  |  |

| RE6/P1B/CCP6<br>RE6<br>P1B<br>CCP6 <sup>(4</sup>                                         | 60              | I/O<br>O<br>I/O      | ST<br>—<br>S/T        | Digital I/O.<br>ECCP1 PWM Output B.<br>Capture 6 input/Compare 6 output/PWM6 output.                                        |  |  |  |  |

| RE7/ECCP2/P2A<br>RE7<br>ECCP2 <sup>(2)</sup><br>P2A                                      | 59              | I/O<br>I/O<br>O      | ST<br>ST<br>—         | Digital I/O.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>ECCP2 PWM Output A.                                        |  |  |  |  |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input<br>P = Power<br>$I^2C = I^2C^{TM}/SI$ | Trigger input w | rith CN              | IOS levels            | CMOS= CMOS compatible input or outputAnalog= Analog inputO= OutputOD= Open-Drain (no P diode to VDD)                        |  |  |  |  |

#### TABLE 1-3: PIC18F6XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

**2:** Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

= Open-Drain (no P diode to VDD)

#### TABLE 1-4: PIC18F8XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                           | Pin Number Pin Br |           |           | Description                                   |  |  |  |  |

|------------------------------------|-------------------|-----------|-----------|-----------------------------------------------|--|--|--|--|

|                                    | TQFP              | Туре Туре |           | Description                                   |  |  |  |  |

| RH7/CCP6/P1B/AN15                  | 19                |           |           |                                               |  |  |  |  |

| RH7                                |                   | I/O       | ST        | Digital I/O.                                  |  |  |  |  |

| CCP6 <sup>(5)</sup>                |                   | I/O       | ST        | Capture 6 input/Compare 6 output/PWM6 output. |  |  |  |  |

| P1B                                |                   | 0         | —         | ECCP1 PWM Output B.                           |  |  |  |  |

| AN15                               |                   | I.        | Analog    | Analog Input 15.                              |  |  |  |  |

| Legend: TTL = TTL compatible input |                   |           |           | CMOS = CMOS compatible input or output        |  |  |  |  |

| ST = Schmitt T                     | rigger input wit  | h CMC     | OS levels | Analog = Analog input                         |  |  |  |  |

| I = Input                          |                   |           |           | O = Output                                    |  |  |  |  |

= Power Ρ

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

4: PSP is available only in Microcontroller mode.

5: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

OD

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                            |                                    |                                                                                |                                 |  |  |  |  |  |

|------------|---------------------------------------------------------|----------------------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register   | Applicabl                                               | e Devices                  | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| ODCON2     | PIC18F66K22<br>PIC18F67K22                              | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |

| ODCON2     | PIC18F65K22                                             | PIC18F85K22                | 00 0000                            | uu uuuu                                                                        | uu uuuu                         |  |  |  |  |  |

| ODCON3     | PIC18F6XK22                                             | PIC18F8XK22                | 000                                | uuu                                                                            | uuu                             |  |  |  |  |  |

| MEMCON     | PIC18F6XK22                                             | PIC18F8XK22                | 0-0000                             | 0-0000                                                                         | u-uuuu                          |  |  |  |  |  |

| ANCON0     | PIC18F6XK22                                             | PIC18F8XK22                | 1111 1111                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |

| ANCON1     | PIC18F6XK22                                             | PIC18F8XK22                | 1111 1111                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |

| ANCON2     | PIC18F6XK22                                             | PIC18F8XK22                | 1111 1111                          | սսսս սսսս                                                                      | սսսս սսսս                       |  |  |  |  |  |

| RCSTA2     | PIC18F6XK22                                             | PIC18F8XK22                | 0000 000x                          | 0000 000x                                                                      | սսսս սսսս                       |  |  |  |  |  |

| TXSTA2     | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0010                          | 0000 0010                                                                      | սսսս սսսս                       |  |  |  |  |  |

| BAUDCON2   | PIC18F6XK22                                             | PIC18F8XK22                | 0100 0-00                          | 0100 0-00                                                                      | uuuu u-uu                       |  |  |  |  |  |

| SPBRGH2    | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| SPBRG2     | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| RCREG2     | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| TXREG2     | PIC18F6XK22                                             | PIC18F8XK22                | xxxx xxxx                          | xxxx xxxx                                                                      | uuuu uuuu                       |  |  |  |  |  |

| PSTR2CON   | PIC18F6XK22                                             | PIC18F8XK22                | 00-0 0001                          | 00-0 0001                                                                      | uu-u uuuu                       |  |  |  |  |  |

| PSTR3CON   | PIC18F6XK22                                             | PIC18F8XK22                | 00-0 0001                          | 00-0 0001                                                                      | uu-u uuuu                       |  |  |  |  |  |

| PMD0       | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |  |  |

| PMD1       | PIC18F6XK22                                             | PIC18F8XK22                | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| PMD2       | PIC18F66K22<br>PIC18F67K22                              | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| PMD2       | PIC18F65K22                                             | PIC18F85K22                | -0-0 0000                          | -0-0 0000                                                                      | -u-u uuuu                       |  |  |  |  |  |

| PMD3       | PIC18F66K22<br>PIC18F67K22                              | PIC18F86K22<br>PIC18F87K22 | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |  |  |  |  |  |

| PMD3       | PIC18F65K22                                             | PIC18F85K22                | 00 000-                            | 00 000-                                                                        | uu uuu-                         |  |  |  |  |  |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt, and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

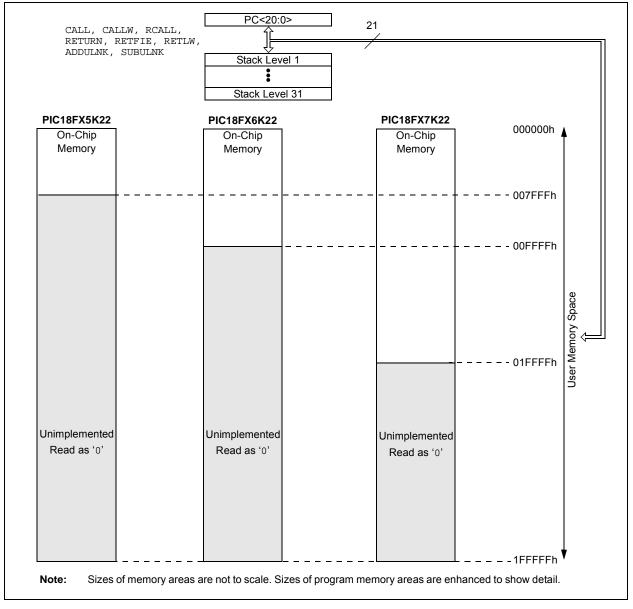

#### 6.0 MEMORY ORGANIZATION

PIC18F87K22 family devices have these types of memory:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses. This enables concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device because it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**. The data EEPROM is discussed separately in **Section 9.0 "Data EEPROM Memory"**.

#### FIGURE 6-1: MEMORY MAPS FOR PIC18F87K22 FAMILY DEVICES

#### 8.8 Operation in Power-Managed Modes

In alternate, power-managed Run modes, the external bus continues to operate normally. If a clock source with a lower speed is selected, bus operations will run at that speed. In these cases, excessive access times for the external memory may result if Wait states have been enabled and added to external memory operations. If operations in a lower power Run mode are anticipated, users should provide in their applications for adjusting memory access times at the lower clock speeds. In Sleep and Idle modes, the microcontroller core does not need to access data; bus operations are suspended. The state of the external bus is frozen, with the address/data pins, and most of the control pins, holding at the same state they were in when the mode was invoked. The only potential changes are to the  $\overline{CE}$ ,  $\overline{LB}$  and  $\overline{UB}$  pins, which are held at logic high.

| <b>TABLE 8-3</b> : | REGISTERS ASSOCIATED WITH THE EXTERNAL MEMORY BUS |

|--------------------|---------------------------------------------------|

|                    |                                                   |

| Name                  | Bit 7 | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0 |

|-----------------------|-------|--------|---------------------|--------|--------|-----------|-----------|-------|

| MEMCON <sup>(1)</sup> | EBDIS | _      | WAIT1               | WAIT0  |        | —         | WM1       | WM0   |

| PADCFG1               | RDPU  | REPU   | RJPU <sup>(1)</sup> | _      | —      | RTSECSEL1 | RTSECSEL0 |       |

| PMD1                  | PSPMD | CTMUMD | RTCCMD              | TMR4MD | TMR3MD | TMR2MD    | TMR1MD    | EMBMD |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during External Memory Bus access.

Note 1: Unimplemented in 64-pin devices (PIC18F6XK22), read as '0'.

NOTES:

| R/W-0         | U-0                         | R-0              | R-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|---------------|-----------------------------|------------------|-----------------|-------------------|-----------------|-----------------|--------|

| TMR5GIE       | —                           | RC2IE            | TX2IE           | CTMUIE            | CCP2IE          | CCP1IE          | RTCCIE |

| bit 7         |                             |                  |                 |                   |                 |                 | bit 0  |

|               |                             |                  |                 |                   |                 |                 |        |

| Legend:       |                             |                  |                 |                   |                 |                 |        |

| R = Readable  | e bit                       | W = Writable     | bit             | U = Unimplem      | nented bit, rea | d as '0'        |        |

| -n = Value at | POR                         | '1' = Bit is set |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |

| bit 7         | TMR5GIF: Tir                | ner5 Gate Inter  | rupt Enable bit | ·                 |                 |                 |        |

|               | 1 = Enabled                 |                  |                 |                   |                 |                 |        |

|               | 0 = Disabled                |                  |                 |                   |                 |                 |        |

| bit 6         | Unimplement                 | ted: Read as '   | כי              |                   |                 |                 |        |

| bit 5         | RC2IE: EUSA                 | RT Receive In    | terrupt Enable  | bit               |                 |                 |        |

|               | 1 = Enabled                 |                  |                 |                   |                 |                 |        |

|               | 0 = Disabled                |                  |                 |                   |                 |                 |        |

| bit 4         |                             | RT Transmit Ir   | iterrupt Enable | e bit             |                 |                 |        |

|               | 1 = Enabled<br>0 = Disabled |                  |                 |                   |                 |                 |        |

| bit 3         |                             | MU Interrupt Er  | nable bit       |                   |                 |                 |        |

|               | 1 = Enabled                 |                  |                 |                   |                 |                 |        |

|               | 0 = Disabled                |                  |                 |                   |                 |                 |        |

| bit 2         | CCP2IE: ECC                 | P2 Interrupt E   | nable bit       |                   |                 |                 |        |

|               | 1 = Enabled                 |                  |                 |                   |                 |                 |        |

|               | 0 = Disabled                |                  |                 |                   |                 |                 |        |

| bit 1         |                             | CP1 Interrupt E  | nable bit       |                   |                 |                 |        |

|               | 1 = Enabled<br>0 = Disabled |                  |                 |                   |                 |                 |        |

| bit 0         | RTCCIE: RTC                 | C Interrupt En   | able bit        |                   |                 |                 |        |

|               | 1 = Enabled                 | 1                |                 |                   |                 |                 |        |

|               | 0 = Disabled                |                  |                 |                   |                 |                 |        |

|               |                             |                  |                 |                   |                 |                 |        |

#### REGISTER 11-12: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

#### REGISTER 11-13: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| R/W-0                              | R/W-0                 | R/W-0  | R/W-0                                   | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

|------------------------------------|-----------------------|--------|-----------------------------------------|------------------------------------|--------|--------|--------|--|

| CCP10IE <sup>(1)</sup>             | CCP9IE <sup>(1)</sup> | CCP8IE | CCP7IE                                  | CCP6IE                             | CCP5IE | CCP4IE | CCP3IE |  |

| bit 7                              | •                     | •      |                                         | •                                  |        | •      | bit 0  |  |

|                                    |                       |        |                                         |                                    |        |        |        |  |

| Legend:                            |                       |        |                                         |                                    |        |        |        |  |

| R = Readable bit W = Writable bit  |                       |        | bit                                     | U = Unimplemented bit, read as '0' |        |        |        |  |

| -n = Value at POR '1' = Bit is set |                       |        | '0' = Bit is cleared x = Bit is unknown |                                    |        |        |        |  |

bit 7-0 CCP<10:3>IE: CCP<10:3> Interrupt Enable bits<sup>(1)</sup>

- 1 = Enabled

- 0 = Disabled

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

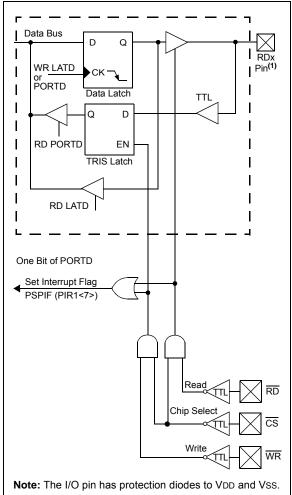

#### 12.11 Parallel Slave Port

PORTD can function as an 8-bit-wide Parallel Slave Port (PSP), or microprocessor port, when control bit, PSPMODE (PSPCON<4>), is set. The port is asynchronously readable and writable by the external world through the RD control input pin (RE0/P2D/RD/AD8) and WR control input pin (RE1/P2C/WR/AD9).

| Note: | The Parallel Slave Port is available only in |

|-------|----------------------------------------------|

|       | Microcontroller mode.                        |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an eight-bit latch.

Setting bit, PSPMODE, enables port pin, RE0/P2D/RD/AD8, to be the RD input, RE1/P2C/WR/AD9 to be the WR input and RE2/P2B/CCP10/CS/AD10 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (= 111).

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits (PIR1<7> and PSPCON<7>, respectively) are set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit (PSPCON<6>) is set. If the user writes new data to PORTD to set OBF, the data is immediately read out, but the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  line is detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 12-4 and Figure 12-5, respectively.

### FIGURE 12-3: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

#### REGISTER 20-2: CCPTMRS0: CCP TIMER SELECT 0 REGISTER

| R/W-0           | R/W-0                                                | R/W-0                                                                                                                                       | R/W-0                                                    | R/W-0            | R/W-0            | R/W-0            | R/W-0           |

|-----------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------------------|------------------|-----------------|

| C3TSEL1         | C3TSEL0                                              | C2TSEL2                                                                                                                                     | C2TSEL1                                                  | C2TSEL0          | C1TSEL2          | C1TSEL1          | C1TSEL0         |

| bit 7           |                                                      |                                                                                                                                             |                                                          |                  |                  |                  | bit (           |

| Legend:         |                                                      |                                                                                                                                             |                                                          |                  |                  |                  |                 |

| R = Readable    | bit                                                  | W = Writable                                                                                                                                | bit                                                      | U = Unimpler     | nented bit, read | as '0'           |                 |

| -n = Value at F | POR                                                  | '1' = Bit is set                                                                                                                            |                                                          | '0' = Bit is cle | ared             | x = Bit is unkr  | nown            |

|                 | 01 = ECCP3<br>10 = ECCP3                             | is based off of<br>is based off of<br>is based off of<br>is based off of                                                                    | TMR3/TMR4<br>TMR3/TMR6                                   |                  |                  |                  |                 |

| bit 5-3         | 000 = ECCP<br>001 = ECCP<br>010 = ECCP<br>011 = ECCP | >: ECCP2 Time<br>2 is based off of<br>2 is based off of | of TMR1/TMR<br>of TMR3/TMR<br>of TMR3/TMR<br>of TMR3/TMR | 2<br>4<br>6<br>8 | ed on the 32-Kb  | yte device varia | ant; do not use |

- 101 = Reserved; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

- bit 2-0 C1TSEL<2:0>: ECCP1 Timer Selection bits

- 000 = ECCP1 is based off of TMR1/TMR2

- 001 = ECCP1 is based off of TMR3/TMR4

- 010 = ECCP1 is based off of TMR3/TMR6

- 011 = ECCP1 is based off of TMR3/TMR8

- 100 = ECCP1 is based off of TMR3/TMR10: option reserved on the 32-Kbyte device variant; do not use

- 101 = ECCP1 is based off of TMR3/TMR12: option reserved on the 32-Kbyte device variant; do not use

- 110 = Reserved; do not use

- 111 = Reserved; do not use

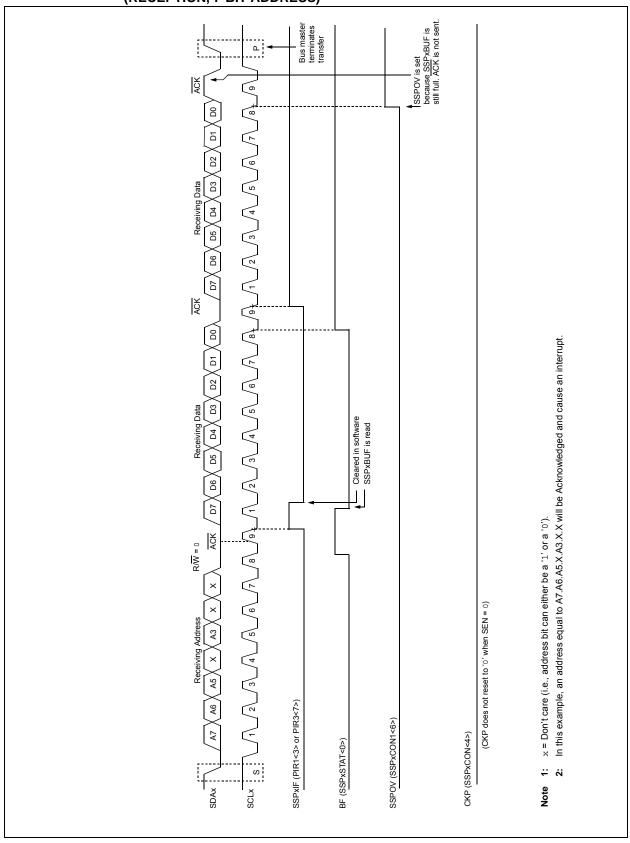

### **PIC18F87K22 FAMILY** I<sup>2</sup>C<sup>TM</sup> SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01011 (RECEPTION, 7-BIT ADDRESS)

FIGURE 21-9:

#### REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

| R-x                                                    | R-x                                          | R-x              | U-0 | U-0                                | U-0  | U-0             | U-0   |  |  |

|--------------------------------------------------------|----------------------------------------------|------------------|-----|------------------------------------|------|-----------------|-------|--|--|

| CMP3OUT                                                | CMP2OUT                                      | CMP1OUT          | —   | —                                  | —    | —               | —     |  |  |

| bit 7                                                  | •                                            |                  |     |                                    |      | •               | bit 0 |  |  |

|                                                        |                                              |                  |     |                                    |      |                 |       |  |  |

| Legend:                                                |                                              |                  |     |                                    |      |                 |       |  |  |

| R = Readable                                           | bit                                          | W = Writable I   | oit | U = Unimplemented bit, read as '0' |      |                 |       |  |  |

| -n = Value at I                                        | POR                                          | '1' = Bit is set |     | '0' = Bit is clea                  | ared | x = Bit is unkr | nown  |  |  |

|                                                        |                                              |                  |     |                                    |      |                 |       |  |  |

| bit 7-5                                                | it 7-5 CMP<3:1>OUT: Comparator x Status bits |                  |     |                                    |      |                 |       |  |  |

| If CPOL (CMxCON<5>)= <u>0</u> (non-inverted polarity): |                                              |                  |     |                                    |      |                 |       |  |  |

| 1 = Comparator x's VIN+ > VIN-                         |                                              |                  |     |                                    |      |                 |       |  |  |

0 = Comparator x's Vin+ < Vin-

If CPOL = 1 (inverted polarity):

1 = Comparator x's Vin+ < Vin-

0 = Comparator x's ViN+ > ViN-

bit 4-0 Unimplemented: Read as '0'

### 25.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 32-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 25-1. The resistor ladder is segmented to provide a range of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides a range of output voltage with 32 levels.

The CVR<4:0> selection bits (CVRCON<4:0>) offer a range of output voltages. Equation 25-1 shows the how the comparator voltage reference is computed.

#### EQUATION 25-1:

If CVRSS = 1:

$CVREF = (VREF-) + (CVR < 4:0 > /32) \cdot (VREF+ - VREF-)$

<u>If CVRSS = 0:</u>

$CVREF = (AVSS) + (CVR < 4:0 > /32) \cdot (AVDD - AVSS)$

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA3 and RA2. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0** "**Electrical Characteristics**").

#### REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0R/W-0R/W-0R/W-0R/W-0R/W-0CVRENCVROECVRSSCVR4CVR3CVR2CVR1bit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7CVREN: Comparator Voltage Reference Enable bit<br>1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered on<br>0 = CVREF circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>1 = CVREF comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>0 = COmparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVRCVRES = 1:<br>CVRES = 1:<br>CVRES = 0:When CVRSS = 1:<br>CVRES = 0:<br>When CVRSS = 0:                                                                                                              |           |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------|------------------|---------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       CVREN: Comparator Voltage Reference Enable bit       1 = CVREF circuit is powered on       0 = CVREF circuit is powered down         bit 6       CVROE: Comparator VREF Output Enable bit       1 = CVREF voltage level is output on CVREF pin       0 = CVREF voltage level is disconnected from CVREF pin         bit 5       CVRSS: Comparator VREF Source Selection bit       1 = Comparator reference source, CVRSRC = VREF + - VREF-       0 = Comparator reference source, CVRSRC = AVDD - AVSS         bit 4-0       CVR<4:0>: Comparator VREF Value Selection 0 ≤ CVR<4:0> ≤ 31 bits       When CVRSS = 1:       CVREF = (VREF-) + (CVR<4:0>/32) • (VREF + - VREF-)         When CVRSS = 0:       0:       0:       0:       0:            | /-0       | R/W-0                                                                               | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       CVREN: Comparator Voltage Reference Enable bit       1 = CVREF circuit is powered on       0 = CVREF circuit is powered down         bit 6       CVROE: Comparator VREF Output Enable bit       1 = CVREF voltage level is output on CVREF pin         0 = CVREF voltage level is disconnected from CVREF pin       0 = CVREF voltage level is disconnected from CVREF pin         bit 5       CVRSS: Comparator VREF Source Selection bit       1 = Comparator reference source, CVRSRC = VREF+ – VREF-         0 = Comparator reference source, CVRSRC = AVDD – AVSS       bit 4-0       CVR<4:0>: Comparator VREF Value Selection 0 ≤ CVR<4:0> ≤ 31 bits         When CVRSS = 1:       CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ – VREF-)       When CVRSS = 0: | EN        | CVROE                                                                               | CVRSS            | CVR4          | CVR3              | CVR2            | CVR1            | CVR0  |  |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7CVREN: Comparator Voltage Reference Enable bit1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>bit 5bit 5CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 ≤ CVR<4:0> ≤ 31 bits<br>When CVRSS = 1:<br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br>When CVRSS = 0:                                                                                                                                                          |           |                                                                                     |                  |               |                   |                 |                 | bit   |  |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7CVREN: Comparator Voltage Reference Enable bit1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>bit 5bit 5CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 ≤ CVR<4:0> ≤ 31 bits<br>When CVRSS = 1:<br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br>When CVRSS = 0:                                                                                                                                                          |           |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

| -n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7CVREN: Comparator Voltage Reference Enable bit<br>$1 = CVREF$ circuit is powered on<br>$0 = CVREF$ circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>$1 = CVREF$ voltage level is output on CVREF pin<br>$0 = CVREF$ voltage level is disconnected from CVREF pin<br>$0 = CVREF$ voltage level is disconnected from CVREF pin<br>$0 = CVREF$ voltage level is disconnected from CVREF pinbit 5CVRSS: Comparator VREF Source Selection bit<br>$1 = Comparator reference source, CVRSRC = VREF+ - VREF-0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 \le CVR<4:0> \le 31 bits\frac{When CVRSS = 1:}{CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)}\frac{When CVRSS = 0:}{When CVRSS = 0:}$                                                                                                                                    | 1:        |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

| bit 7 <b>CVREN:</b> Comparator Voltage Reference Enable bit<br>$1 = CV_{REF}$ circuit is powered on<br>$0 = CV_{REF}$ circuit is powered down<br>bit 6 <b>CVROE:</b> Comparator VREF Output Enable bit<br>$1 = CV_{REF}$ voltage level is output on CVREF pin<br>$0 = CV_{REF}$ voltage level is disconnected from CVREF pin<br>bit 5 <b>CVRSS:</b> Comparator VREF Source Selection bit<br>$1 = Comparator$ reference source, $CV_{RSRC} = V_{REF+} - V_{REF-}$<br>$0 = Comparator$ reference source, $CV_{RSRC} = AV_{DD} - AV_{SS}$<br>bit 4-0 <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le CVR<4:0> \le 31$ bits<br><u>When CVRSS = 1:</u><br>$CV_{REF} = (V_{REF-}) + (CVR<4:0>/32) \bullet (V_{REF+} - V_{REF-})$<br><u>When CVRSS = 0:</u>                                                                                                                                                                                                                          | adable bi | oit                                                                                 | W = Writable b   | pit           | U = Unimplem      | nented bit, rea | d as '0'        |       |  |  |  |  |  |

| 1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pinbit 5CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 $\leq$ CVR<4:0> $\leq$ 31 bits<br>When CVRSS = 1:<br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br>When CVRSS = 0:                                                                                                                                                                                                                                                                                                                                                                                                               | lue at PO | OR                                                                                  | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| 1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered downbit 6CVROE: Comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pinbit 5CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 $\leq$ CVR<4:0> $\leq$ 31 bits<br>When CVRSS = 1:<br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br>When CVRSS = 0:                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

| $0 = CVREF circuit is powered down$ bit 6 $CVROE: Comparator VREF Output Enable bit$ $1 = CVREF voltage level is output on CVREF pin$ $0 = CVREF voltage level is disconnected from CVREF pin$ bit 5 $CVRSS: Comparator VREF Source Selection bit$ $1 = Comparator reference source, CVRSRC = VREF+ - VREF-$ $0 = Comparator reference source, CVRSRC = AVDD - AVSS$ bit 4-0 $CVR<4:0>: Comparator VREF Value Selection 0 \le CVR<4:0> \le 31 \text{ bits}$ $\frac{When CVRSS = 1:}{CVREF = (VREF-) + (CVR<4:0>/32) \cdot (VREF+ - VREF-)}{When CVRSS = 0:}$                                                                                                                                                                                                                                                                                                                                                                                                                                | C         | CVREN: Comparator Voltage Reference Enable bit                                      |                  |               |                   |                 |                 |       |  |  |  |  |  |

| bit 6 <b>CVROE</b> : Comparator VREF Output Enable bit<br>1 = CVREF voltage level is output on CVREF pin<br>0 = CVREF voltage level is disconnected from CVREF pin<br>bit 5 <b>CVRSS</b> : Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ - VREF-<br>0 = Comparator reference source, CVRSRC = AVDD - AVSS<br>bit 4-0 <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le CVR<4:0> \le 31$ bits<br><u>When CVRSS = 1:</u><br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br><u>When CVRSS = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

| $1 = CVREF \text{ voltage level is output on CVREF pin}$ $1 = CVREF \text{ voltage level is disconnected from CVREF pin}$ $0 = CVRSS: \text{ Comparator VREF Source Selection bit}$ $1 = \text{ Comparator reference source, CVRSRC = VREF+ - VREF-}$ $0 = \text{ Comparator reference source, CVRSRC = AVDD - AVSS}$ bit 4-0 $CVR<4:0>: \text{ Comparator VREF Value Selection } 0 \le CVR<4:0> \le 31 \text{ bits}$ $\frac{When CVRSS = 1:}{CVREF = (VREF-) + (CVR<4:0>/32) \bullet (VREF+ - VREF-)}$ $\frac{When CVRSS = 0:}{When CVRSS = 0:}$                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0         | 0 = CVREF circuit is powered down                                                   |                  |               |                   |                 |                 |       |  |  |  |  |  |

| 0 = CVREF  voltage level is disconnected from CVREF pin<br>bit 5<br>CVRSS: Comparator VREF Source Selection bit $1 = Comparator reference source, CVRSRC = VREF+ - VREF-$ $0 = Comparator reference source, CVRSRC = AVDD - AVSSbit 4-0CVR<4:0>: Comparator VREF Value Selection 0 \le CVR<4:0> \le 31 \text{ bits}\frac{When CVRSS = 1:}{CVREF = (VREF-) + (CVR<4:0>/32) \cdot (VREF+ - VREF-)}\frac{When CVRSS = 0:}{VREF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C         | CVROE: Comparator VREF Output Enable bit                                            |                  |               |                   |                 |                 |       |  |  |  |  |  |

| bit 5 <b>CVRSS:</b> Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF - VREF - O = Comparator reference source, CVRSRC = AVDD - AVSS<br>bit 4-0 <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le \text{CVR}<4:0> \le 31$ bits<br><u>When CVRSS = 1:</u><br>CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ - VREF-)<br><u>When CVRSS = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | •                                                                                   |                  |               |                   |                 |                 |       |  |  |  |  |  |

| $1 = \text{Comparator reference source, CVRSRC} = \text{VREF+} - \text{VREF-} \\ 0 = \text{Comparator reference source, CVRSRC} = \text{AVDD} - \text{AVSS} \\ \text{bit 4-0} \qquad \text{CVR<4:0>: Comparator VREF Value Selection } 0 \le \text{CVR<4:0>} \le 31 \text{ bits} \\ \frac{\text{When CVRSS} = 1:}{\text{CVREF}} \\ \text{CVREF} = (\text{VREF-}) + (\text{CVR<4:0>}/32) \bullet (\text{VREF+} - \text{VREF-}) \\ \frac{\text{When CVRSS} = 0:}{\text{When CVRSS} = 0:} \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0         | 0 = CVREF voltage level is disconnected from CVREF pin                              |                  |               |                   |                 |                 |       |  |  |  |  |  |

| bit 4-0 $CVR<4:0>: Comparator VREF Value Selection 0 \leq CVR<4:0> \leq 31 bitsWhen CVRSS = 1:CVR=F (VREF-) + (CVR<4:0>/32) \bullet (VREF+ - VREF-)When CVRSS = 0:$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C         | CVRSS: Comparator VREF Source Selection bit                                         |                  |               |                   |                 |                 |       |  |  |  |  |  |

| bit 4-0 $CVR<4:0>: Comparator VREF Value Selection 0 \le CVR<4:0> \le 31 bits\frac{When CVRSS = 1:}{CVREF = (VREF-) + (CVR<4:0>/32) \bullet (VREF+ - VREF-)}{When CVRSS = 0:}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

| When $CVRSS = 1$ :<br>$CVREF = (VREF-) + (CVR<4:0>/32) \bullet (VREF+ - VREF-)$<br>When $CVRSS = 0$ :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0         | 0 = Comparator reference source, CVRSRC = AVDD – AVSS                               |                  |               |                   |                 |                 |       |  |  |  |  |  |

| CVREF = (VREF-) + (CVR<4:0>/32) • (VREF+ – VREF-)<br><u>When CVRSS = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C         | <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le CVR<4:0> \le 31$ bits |                  |               |                   |                 |                 |       |  |  |  |  |  |

| When CVRSS = 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | When CVRSS = 1:                                                                     |                  |               |                   |                 |                 |       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                                                                     | , (              | >/32) • (VREF | + – VREF-)        |                 |                 |       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                                                                     |                  | (00) (1) /    | () (22)           |                 |                 |       |  |  |  |  |  |

| $CVREF = (AVSS) + (CVR < 4:0 > /32) \bullet (AVDD - AVSS)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C         | OVREF = (AV                                                                         | SS) + (CVR<4:0   | >/32) • (AVDD | – AVSS)           |                 |                 |       |  |  |  |  |  |

#### 26.2 HLVD Setup

To set up the HLVD module:

- 1. Select the desired HLVD trip point by writing the value to the HLVDL<3:0> bits.

- 2. Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- 3. Enable the HLVD module by setting the HLVDEN bit.

- 4. Clear the HLVD interrupt flag (PIR2<2>), which may have been set from a previous interrupt.

- If interrupts are desired, enable the HLVD interrupt by setting the HLVDIE and GIE bits (PIE2<2> and INTCON<7>, respectively).

An interrupt will not be generated until the IRVST bit is set.

**Note:** Before changing any module settings (VDIRMAG, LVDL<3:0>), first disable the module (LVDEN = 0), make the changes and re-enable the module. This prevents the generation of false HLVD events.

#### 26.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and consume static current. The total current consumption, when enabled, is specified in electrical specification Parameter D022B (Table 31-13).

Depending on the application, the HLVD module does not need to operate constantly. To reduce current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After such a check, the module could be disabled.

#### 26.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification Parameter 37 (Section 31.0 "Electrical Characteristics"), may be used by other internal circuitry, such as the programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification Parameter 37 (Table 31-13).

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval (see Figure 26-2 or Figure 26-3).

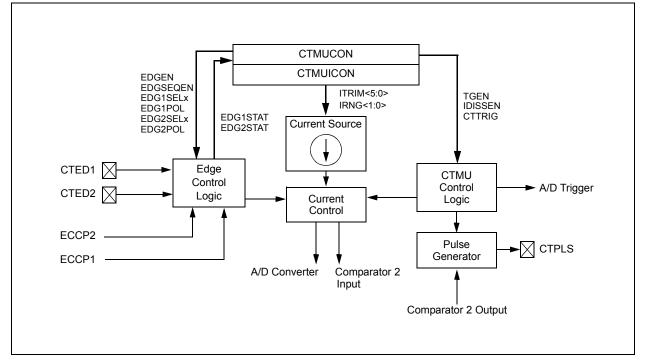

### 27.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can precisely measure time, capacitance and relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes these key features:

- Up to 24 channels available for capacitive or time measurement input

- · On-chip precision current source

- Four-edge input trigger sources

- Polarity control for each edge source

- Control of edge sequence

#### FIGURE 27-1: CTMU BLOCK DIAGRAM

- Control of response to edges

- · Time measurement resolution of 1 nanosecond

- · High-precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 24 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs or the ECCP1/ECCP2 Special Event Triggers.

The CTMU special event can trigger the Analog-to-Digital Converter module.

Figure 27-1 provides a block diagram of the CTMU.

| U-0               | R/P-1                                                                                         | R/P-1                      | R/P-1     | R/P-1                              | R/P-1  | R/P-1              | R/P-1  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------|----------------------------|-----------|------------------------------------|--------|--------------------|--------|--|--|--|--|

| _                 | WDTPS4                                                                                        | WDTPS3                     | WDTPS2    | WDTPS1                             | WDTPS0 | WDTEN1             | WDTEN0 |  |  |  |  |

| bit 7             |                                                                                               |                            |           |                                    |        |                    | bit    |  |  |  |  |

| Legend:           |                                                                                               | P = Programr               | nable bit |                                    |        |                    |        |  |  |  |  |

| R = Readab        | ole bit                                                                                       | W = Writable bit           |           | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |  |

| -n = Value at POR |                                                                                               | '1' = Bit is set           |           | '0' = Bit is cle                   | ared   | x = Bit is unknown |        |  |  |  |  |

| bit 7             | Unimplemen                                                                                    | Jnimplemented: Read as '0' |           |                                    |        |                    |        |  |  |  |  |

| bit 6-2           | WDTPS<4:0>: Watchdog Timer Postscale Select bits                                              |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10101-11111 = Reserved                                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10100 = 1:1,048,576 (4,194.304s)                                                              |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10011 = 1:524,288 (2,097.152s)                                                                |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10010 = 1:262,144 (1,048.576s)                                                                |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10001 = 1:131,072 (524.288s)                                                                  |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10000 = 1:65,536 (262.144s)                                                                   |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01111 = 1:32,768 (131.072s)                                                                   |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01110 = 1:16,384 (65.536s)<br>01101 = 1:8,192 (32.768s)                                       |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01101 = 1.8, 192 (32.7688)<br>01100 = 1:4,096 (16.384s)                                       |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01011 = 1:2,048 (8.192s)                                                                      |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01011 = 1.2,040 (0.1323)<br>01010 = 1:1,024 (4.096s)                                          |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01001 = 1:512 (2.048s)                                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01000 = 1:256 (1.024s)                                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 00111 = 1:128 (512 ms)                                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 00110 = 1:64 (256 ms)                                                                         |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 00101 = 1:32 (128  ms)                                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 00100 = 1:16 (64 ms)<br>00011 = 1:8 (32 ms)                                                   |                            |           |                                    |        |                    |        |  |  |  |  |

|                   |                                                                                               | • •                        |           |                                    |        |                    |        |  |  |  |  |

|                   | 00010 = 1:4 (16 ms)<br>00001 = 1:2 (8 ms)                                                     |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 000001 = 1.2<br>000000 = 1.1                                                                  |                            |           |                                    |        |                    |        |  |  |  |  |

| bit 1-0           | WDTEN<1:0>: Watchdog Timer Enable bits                                                        |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 11 = WDT is enabled in hardware; SWDTEN bit is disabled                                       |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 10 = WDT is controlled by the SWDTEN bit setting                                              |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | 01 = WDT is enabled only while the device is active and disabled in Sleep mode; SWDTEN bit is |                            |           |                                    |        |                    |        |  |  |  |  |

|                   | disable                                                                                       | -1                         |           |                                    |        |                    |        |  |  |  |  |

|                   |                                                                                               |                            |           | TEN bit is disa                    |        |                    |        |  |  |  |  |

### REGISTER 28-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

NOTES:

#### 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K22 Family (Industrial/Extended) (Continued)