Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

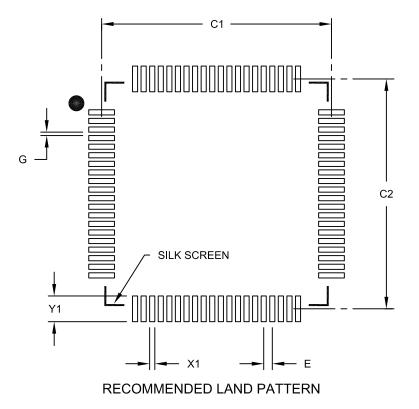

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86k22-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name              | Pin Number      | Pin                                       | in Buffer  | Description                                          |  |  |  |

|-----------------------|-----------------|-------------------------------------------|------------|------------------------------------------------------|--|--|--|

| Pin Name              | QFN/TQFP        | Туре Туре                                 |            | Description                                          |  |  |  |

|                       | 7               |                                           |            | Master Clear (input) or programming voltage (input). |  |  |  |

| MCLR/RG5              |                 |                                           |            |                                                      |  |  |  |

| MCLR                  |                 | 1                                         | ST         | This pin is an active-low Reset to the device.       |  |  |  |

| RG5                   |                 | 1                                         | ST         | General purpose, input only pin.                     |  |  |  |

| OSC1/CLKI/RA7         | 39              |                                           |            | Oscillator crystal or external clock input.          |  |  |  |

| OSC1                  |                 | 1                                         | CMOS       | Oscillator crystal input.                            |  |  |  |

| CLKI                  |                 | 1                                         | CMOS       | External clock source input. Always associated       |  |  |  |

|                       |                 |                                           |            | with pin function, OSC1. (See related OSC1/CLKI,     |  |  |  |

|                       |                 |                                           |            | OSC2/CLKO pins.)                                     |  |  |  |

| RA7                   |                 | I/O                                       | TTL        | General purpose I/O pin.                             |  |  |  |

| OSC2/CLKO/RA6         | 40              |                                           |            | Oscillator crystal or clock output.                  |  |  |  |

| OSC2                  |                 | 0                                         | —          | Oscillator crystal output. Connects to crystal or    |  |  |  |

|                       |                 |                                           |            | resonator in Crystal Oscillator mode.                |  |  |  |

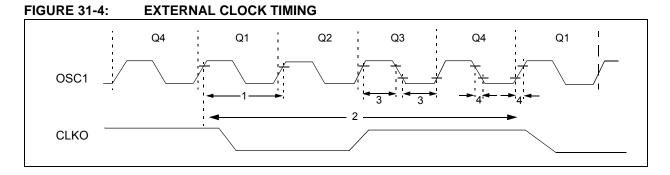

| CLKO                  |                 | 0                                         | _          | In certain oscillator modes, OSC2 pin outputs CLKO,  |  |  |  |

|                       |                 | which has 1/4 the frequency of OSC1 and d |            | which has 1/4 the frequency of OSC1 and denotes the  |  |  |  |

|                       |                 |                                           |            | instruction cycle rate.                              |  |  |  |

| RA6                   |                 | I/O                                       | TTL        | General purpose I/O pin.                             |  |  |  |

| Legend: TTL = TTL con | npatible input  |                                           |            | CMOS = CMOS compatible input or output               |  |  |  |

| ST = Schmitt          | Trigger input w | ith CN                                    | 10S levels | Analog = Analog input                                |  |  |  |

|                       |                 |                                           |            |                                                      |  |  |  |

#### **TABLE 1-3**: PIC18F6XK22 PINOUT I/O DESCRIPTIONS

1 = Input

Ρ = Power

$I^2C = I^2C^{TM}/SMBus$

= Output = Open-Drain (no P diode to VDD)

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

- 2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

- 3: Not available on PIC18F65K22 and PIC18F85K22 devices.

- 4: The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

0

OD

| Din Nama                                                           | Pin Number                        | Pin                  | Buffer                       | Description                                                                                                                              |

|--------------------------------------------------------------------|-----------------------------------|----------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                           | QFN/TQFP                          | Туре                 | Туре                         | Description                                                                                                                              |

|                                                                    |                                   |                      |                              | PORTC is a bidirectional I/O port.                                                                                                       |

| RC0/SOSCO/SCLKI<br>RC0<br>SOSCO<br>SCLKI                           | 30                                | I/O<br>O<br>I        | ST<br>—<br>ST                | Digital I/O.<br>SOSC oscillator output.<br>Digital SOSC input.                                                                           |

| RC1/SOSCI/ECCP2/P2A<br>RC1<br>SOSCI<br>ECCP2 <sup>(1)</sup><br>P2A | 29                                | I/O<br>I<br>I/O<br>O | ST<br>CMOS<br>ST             | Digital I/O.<br>SOSC oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>Enhanced PWM2 Output A.                       |

| RC2/ECCP1/P1A<br>RC2<br>ECCP1<br>P1A                               | 33                                | I/O<br>I/O<br>O      | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced PWM1 Output A.                                                 |

| RC3/SCK1/SCL1<br>RC3<br>SCK1<br>SCL1 <sup>(4)</sup>                | 34                                | I/O<br>I/O<br>I/O    | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI1/SDA1<br>RC4<br>SDI1<br>SDA1 <sup>(4)</sup>                | 35                                | I/O<br>I<br>I/O      | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |

| RC5/SDO1<br>RC5<br>SDO1                                            | 36                                | I/O<br>O             | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                                                            |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                                   | 31                                | I/O<br>O<br>I/O      | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX1/DT1).                                         |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                                   | 32                                | I/O<br>I<br>I/O      | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX1/CK1).                                           |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input                 | npatible input<br>Trigger input w | ∕ith C№              | 10S levels                   | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output                                                            |

### TABLE 1-3: PIC18F6XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

OD

= Open-Drain (no P diode to VDD)

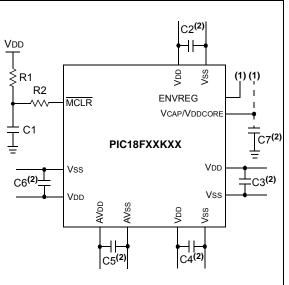

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FXXKXX MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F87K22 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG (if implemented) and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic R1: 10 k $\Omega$

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)" for explanation of ENVREG pin connections.

- 2: The example shown is for a PIC18F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

| R/W-0                  | R/W-0                                                                                                                                     | R/W-0                              | R/W-0                  | R/W-0             | R/W-0            | R/W-0           | R/W-0    |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------|-------------------|------------------|-----------------|----------|

| TMR10MD <sup>(1)</sup> | TMR8MD                                                                                                                                    | TMR7MD <sup>(1)</sup>              | TMR6MD                 | TMR5MD            | CMP3MD           | CMP2MD          | CMP1MD   |

| bit 7                  |                                                                                                                                           |                                    |                        |                   |                  |                 | bit (    |

| Lovende                |                                                                                                                                           |                                    |                        |                   |                  |                 |          |

| Legend:                | L : 4                                                                                                                                     |                                    |                        |                   |                  |                 |          |

| R = Readable           |                                                                                                                                           | W = Writable k                     | DIT                    |                   | nented bit, read |                 |          |

| -n = Value at P        | OR                                                                                                                                        | '1' = Bit is set                   |                        | '0' = Bit is cle  | ared             | x = Bit is unkr | nown     |

| bit 7                  | TMR10MD: T                                                                                                                                | MR10MD Disat                       | ole bit <sup>(1)</sup> |                   |                  |                 |          |

|                        |                                                                                                                                           | al Module Disab<br>disabled and TM |                        |                   | TMR10MD clo      | ck sources are  | disabled |

| bit 6                  | TMR8MD: TN                                                                                                                                | AR8MD Disable                      | bit                    |                   |                  |                 |          |

|                        |                                                                                                                                           | enabled and all                    |                        |                   | disabled         |                 |          |

| ait E                  | <ul> <li>PMD is disabled and TMR8MD is enabled</li> <li>TMR7MD: TMR7MD Disable bit<sup>(1)</sup></li> </ul>                               |                                    |                        |                   |                  |                 |          |

| bit 5                  |                                                                                                                                           | enabled and all                    |                        | ak aguraga ara    | disabled         |                 |          |

|                        |                                                                                                                                           | lisabled and TM                    |                        |                   | uisabieu         |                 |          |

| bit 4                  | TMR6MD: TN                                                                                                                                | AR6MD Disable                      | bit                    |                   |                  |                 |          |

|                        |                                                                                                                                           | enabled and all                    |                        |                   | disabled         |                 |          |

| bit 3                  | <ul> <li>PMD is disabled and TMR6MD is enabled</li> <li>TMR5MD Disable bit</li> </ul>                                                     |                                    |                        |                   |                  |                 |          |

| bit o                  | 1 = PMD is enabled and all TMR5MD clock sources are disabled                                                                              |                                    |                        |                   |                  |                 |          |

|                        | 0 = PMD is disabled and TMR5MD clock sources are disabled                                                                                 |                                    |                        |                   |                  |                 |          |

| bit 2                  | CMP3MD: PI                                                                                                                                | MD Comparator                      | 3 Enable/Dis           | able bit          |                  |                 |          |

|                        | <ul> <li>1 = PMD is enabled for Comparator 3, disabling all of its clock sources</li> <li>0 = PMD is disabled for Comparator 3</li> </ul> |                                    |                        |                   |                  |                 |          |

| bit 1                  | CMP2MD: PI                                                                                                                                | MD Comparator                      | 3 Enable/Dis           | able bit          |                  |                 |          |

|                        | <ul> <li>1 = PMD is enabled for Comparator 2, disabling all of its clock sources</li> <li>0 = PMD is disabled for Comparator 2</li> </ul> |                                    |                        |                   |                  |                 |          |

| bit 0                  | CMP1MD: PI                                                                                                                                | MD Comparator                      | 3 Enable/Dis           | able bit          |                  |                 |          |

|                        |                                                                                                                                           | enabled for Com                    |                        | abling all of its | clock sources    |                 |          |

|                        | 0 = PMD is c                                                                                                                              | lisabled for Com                   | parator 1              |                   |                  |                 |          |

#### REGISTER 4-2: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

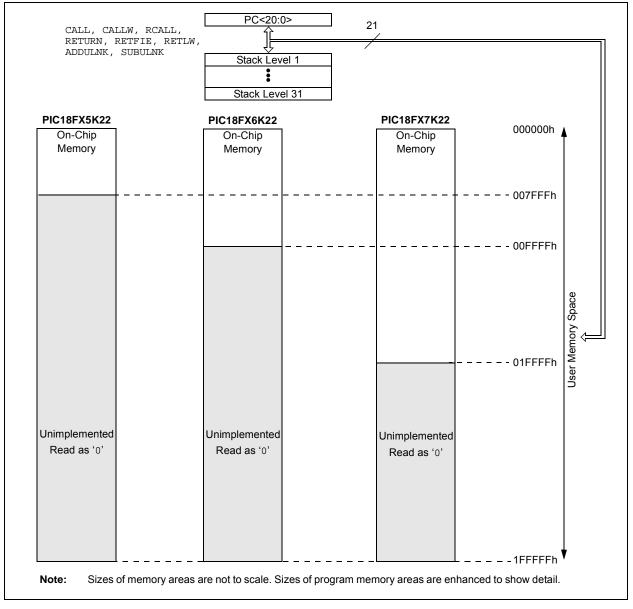

# 6.0 MEMORY ORGANIZATION

PIC18F87K22 family devices have these types of memory:

- Program Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate busses. This enables concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device because it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**. The data EEPROM is discussed separately in **Section 9.0 "Data EEPROM Memory"**.

#### FIGURE 6-1: MEMORY MAPS FOR PIC18F87K22 FAMILY DEVICES

# 11.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are six Peripheral Interrupt Priority registers (IPR1 through IPR6). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit (RCON<7>) be set.

#### REGISTER 11-16: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1    | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1   | R/W-1  | R/W-1  |

|----------|-------|-------|-------|--------|---------|--------|--------|

| PSPIP    | ADIP  | RC1IP | TX1IP | SSP1IP | TMR1GIP | TMR2IP | TMR1IP |

| bit 7    |       |       |       |        |         |        | bit 0  |

|          |       |       |       |        |         |        |        |

| l egend. |       |       |       |        |         |        |        |

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>PSPIP:</b> Parallel Slave Port Read/Write Interrupt Priority bit<br>1 = High priority |

|-------|------------------------------------------------------------------------------------------|

|       | 0 = Low priority                                                                         |

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                                               |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 5 | RC1IP: EUSART Receive Interrupt Priority bit                                             |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 4 | TX1IP: EUSART Transmit Interrupt Priority bit                                            |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 3 | SSP1IP: Master Synchronous Serial Port Interrupt Priority bit                            |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 2 | TMR1GIP: Timer1 Gate Interrupt Priority bit                                              |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 1 | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit                                         |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| bit 0 | TMR1IP: TMR1 Overflow Interrupt Priority bit                                             |

|       | 1 = High priority                                                                        |

|       | 0 = Low priority                                                                         |

| TABLE 12-9: | Function     TRIS     I/O     I/O     Description |         |     |                                                                                    |                                                                                            |  |  |  |  |

|-------------|---------------------------------------------------|---------|-----|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name    | Function                                          | Setting | 1/0 | Туре                                                                               | Description                                                                                |  |  |  |  |

| RE2/CS/P2B/ | RE2                                               | 0       | 0   | DIG                                                                                | LATE<2> data output.                                                                       |  |  |  |  |

| CCP10/AD10  |                                                   | 1       | Ι   | ST                                                                                 | PORTE<2> data input.                                                                       |  |  |  |  |

|             | CS                                                | x       | Ι   | TTL                                                                                | Parallel Slave Port chip select.                                                           |  |  |  |  |

|             | P2B                                               | 0       | 0   | —                                                                                  | ECCP2 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown events |  |  |  |  |

|             | CCP10                                             | 1       | I/O | ST                                                                                 | Capture 10 input/Compare 10 output/PWM10 output.                                           |  |  |  |  |

|             | AD10 <sup>(2)</sup>                               | x       | 0   | DIG                                                                                | External memory interface, Address/Data Bit 10 output.                                     |  |  |  |  |

|             |                                                   | x       | -   | TTL                                                                                | External memory interface, Data Bit 10 input.                                              |  |  |  |  |

| RE3/P3C/    | RE3                                               | 0       | 0   | DIG                                                                                | LATE<3> data output.                                                                       |  |  |  |  |

| CCP9/REFO/  |                                                   | 1       | Ι   | ST                                                                                 | PORTE<3> data input.                                                                       |  |  |  |  |

| AD11        | P3C                                               | 0       | 0   | ECCP3 PWM Output C.     May be configured for tri-state during Enhanced PWM shutdo |                                                                                            |  |  |  |  |

|             | CCP9 0 O                                          |         | DIG | CCP9 Compare/PWM output; takes priority over port data.                            |                                                                                            |  |  |  |  |

|             |                                                   | 1       | Ι   | ST                                                                                 | CCP9 capture input.                                                                        |  |  |  |  |

|             | REFO                                              | x       | 0   | DIG                                                                                | Reference output clock.                                                                    |  |  |  |  |

|             | AD11 <sup>(2)</sup>                               | x       | 0   | DIG                                                                                | External memory interface, Address/Data Bit 11 output.                                     |  |  |  |  |

|             |                                                   | x       | Ι   | TTL                                                                                | External memory interface, Data Bit 11 input.                                              |  |  |  |  |

| RE4/P3B/    | RE4                                               | 0       | 0   | DIG                                                                                | LATE<4> data output.                                                                       |  |  |  |  |

| CCP8/AD12   |                                                   | 1       | Ι   | ST                                                                                 | PORTE<4> data input.                                                                       |  |  |  |  |

| -           | P3B                                               | 0       | 0   | —                                                                                  | ECCP3 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown events |  |  |  |  |

|             | CCP8                                              | 0       | 0   | DIG                                                                                | CCP8 compare/PWM output; takes priority over port data.                                    |  |  |  |  |

|             |                                                   | 1       | I   | ST                                                                                 | CCP8 capture input.                                                                        |  |  |  |  |

|             | AD12 <sup>(2)</sup>                               | x       | 0   | DIG                                                                                | External memory interface, Address/Data Bit 12 output.                                     |  |  |  |  |

|             |                                                   | x       | I   | TTL                                                                                | External memory interface, Data Bit 12 input.                                              |  |  |  |  |

| RE5/P1C/    | RE5                                               | 0       | 0   | DIG                                                                                | LATE<5> data output.                                                                       |  |  |  |  |

| CCP7/AD13   |                                                   | 1       | Ι   | ST                                                                                 | PORTE<5> data input.                                                                       |  |  |  |  |

|             | P1C                                               | 0       | 0   | —                                                                                  | ECCP1 PWM Output C.<br>May be configured for tri-state during Enhanced PWM shutdown events |  |  |  |  |

|             | CCP7                                              | 0       | 0   | DIG                                                                                | CCP7 compare/PWM output; takes priority over port data.                                    |  |  |  |  |

|             |                                                   | 1       | I   | ST                                                                                 | CCP7 capture input.                                                                        |  |  |  |  |

|             | AD13 <sup>(2)</sup>                               | x       | 0   | DIG                                                                                | External memory interface, Address/Data Bit 13 output.                                     |  |  |  |  |

|             |                                                   | x       | 1   | TTL                                                                                | External memory interface, Data Bit 13 input.                                              |  |  |  |  |

| RE6/P1B/    | RE6                                               | 0       | 0   | DIG                                                                                | LATE<6> data output.                                                                       |  |  |  |  |

| CCP6/AD14   |                                                   | 1       | Ι   | ST                                                                                 | PORTE<6> data input.                                                                       |  |  |  |  |

|             | P1B                                               | 0       | 0   | —                                                                                  | ECCP1 PWM Output B.<br>May be configured for tri-state during Enhanced PWM shutdown event  |  |  |  |  |

|             | CCP6                                              | 0       | 0   | DIG                                                                                | CCP6 compare/PWM output; takes priority over port data.                                    |  |  |  |  |

|             |                                                   | 1       | I   | ST                                                                                 | CCP9 capture input.                                                                        |  |  |  |  |

|             | AD14 <sup>(2)</sup>                               | x       | 0   | DIG                                                                                | External memory interface, Address/Data Bit 14 output.                                     |  |  |  |  |

|             |                                                   | x       |     | TTL                                                                                | External memory interface, Data Bit 14 input.                                              |  |  |  |  |

#### TABLE 12-9: PORTE FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared and in Microcontroller mode.

2: This feature is only available on PIC18F8XKXX devices.

### 14.1 Timer1 Gate Control Register

The Timer1 Gate Control register (T1GCON), displayed in Register 14-2, is used to control the Timer1 gate.

# REGISTER 14-2: T1GCON: TIMER1 GATE CONTROL REGISTER<sup>(1)</sup>

| R/W-0        | R/W-0                                                                                                                                                             | R/W-0                                      | R/W-0         | R/W-0                               | R-x            | R/W-0           | R/W-0         |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------|-------------------------------------|----------------|-----------------|---------------|--|--|

| TMR1GE       | T1GPOL                                                                                                                                                            | T1GTM                                      | T1GSPM        | T1GGO/T1DONE                        | T1GVAL         | T1GSS1          | T1GSS0        |  |  |

| bit 7        |                                                                                                                                                                   |                                            |               |                                     |                |                 | bit 0         |  |  |

|              |                                                                                                                                                                   |                                            |               |                                     |                |                 |               |  |  |

| Legend:      |                                                                                                                                                                   |                                            |               |                                     |                |                 |               |  |  |

| R = Readab   |                                                                                                                                                                   | W = Writable                               |               | U = Unimplemented                   | d bit, read as |                 |               |  |  |

| -n = Value a | t POR                                                                                                                                                             | '1' = Bit is set                           |               | '0' = Bit is cleared                |                | x = Bit is unkr | iown          |  |  |

| bit 7        | TMR1GE: Ti                                                                                                                                                        | mer1 Gate Ena                              | able bit      |                                     |                |                 |               |  |  |

|              | If TMR1ON =                                                                                                                                                       | <u>    0</u> :                             |               |                                     |                |                 |               |  |  |

|              | This bit is igr                                                                                                                                                   | ored.                                      |               |                                     |                |                 |               |  |  |

|              | If TMR1ON =                                                                                                                                                       |                                            |               |                                     |                |                 |               |  |  |

|              | <ol> <li>1 = Timer1 counting is controlled by the Timer1 gate function</li> <li>0 = Timer1 counts regardless of Timer1 gate function</li> </ol>                   |                                            |               |                                     |                |                 |               |  |  |

| bit 6        | <b>T1GPOL:</b> Timer1 Gate Polarity bit                                                                                                                           |                                            |               |                                     |                |                 |               |  |  |

|              | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                                                  |                                            |               |                                     |                |                 |               |  |  |

|              | 0 = Timer1 g                                                                                                                                                      | ate is active-lo                           | w (Timer1 co  | unts when gate is low               | v)             |                 |               |  |  |

| bit 5        | T1GTM: Tim                                                                                                                                                        | er1 Gate Togg                              | e Mode bit    |                                     |                |                 |               |  |  |

|              |                                                                                                                                                                   | Gate Toggle m                              |               |                                     |                |                 |               |  |  |

|              |                                                                                                                                                                   | Jate Toggle me<br>flip-flop toggles        |               | d and toggle flip-flop<br>ing edge. | is cleared     |                 |               |  |  |

| bit 4        | -                                                                                                                                                                 | mer1 Gate Sin                              | -             |                                     |                |                 |               |  |  |

|              | 1 = Timer1 G                                                                                                                                                      | ate Single Pul                             | se mode is ei | nabled and is controll              | ling Timer1 ga | ate             |               |  |  |

|              | 0 = Timer1 G                                                                                                                                                      | ate Single Pul                             | se mode is di | sabled                              |                |                 |               |  |  |

| bit 3        | T1GGO/T1D                                                                                                                                                         | ONE: Timer1 (                              | Gate Single P | ulse Acquisition State              | us bit         |                 |               |  |  |

|              |                                                                                                                                                                   |                                            |               | is ready, waiting for a             |                |                 |               |  |  |

|              | <ul> <li>Timer1 gate single pulse acquisition has completed or has not been started</li> <li>This bit is automatically cleared when T1GSPM is cleared.</li> </ul> |                                            |               |                                     |                |                 |               |  |  |

| bit 2        |                                                                                                                                                                   | ner1 Gate Cur                              |               | Gor Wild Cleared.                   |                |                 |               |  |  |

|              |                                                                                                                                                                   |                                            |               | gate that could be r                | provided to TI |                 | unaffected by |  |  |

|              | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L; unaffected by Timer1 Gate Enable (TMR1GE) bit.                              |                                            |               |                                     |                |                 |               |  |  |

| bit 1-0      | T1GSS<1:0>                                                                                                                                                        | T1GSS<1:0>: Timer1 Gate Source Select bits |               |                                     |                |                 |               |  |  |

|              | 11 <b>= Compa</b>                                                                                                                                                 | rator 2 output                             |               |                                     |                |                 |               |  |  |

|              |                                                                                                                                                                   | rator 1 output                             |               |                                     |                |                 |               |  |  |

|              |                                                                                                                                                                   | o match PR2 c                              | output        |                                     |                |                 |               |  |  |

|              | 00 = Timer1                                                                                                                                                       | yate pill                                  |               |                                     |                |                 |               |  |  |

| Note 1: P    | Programming the T1GCON prior to T1CON is recommended.                                                                                                             |                                            |               |                                     |                |                 |               |  |  |

**Note 1:** Programming the T1GCON prior to T1CON is recommended.

## REGISTER 16-3: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0                                                                  | R-0                                                                                                                                                                                                              | U-0                                  | U-0            | R/W-0                                                                                                                  | U-0           | R-x             | R/W-0     |  |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|-----------|--|--|--|--|

| _                                                                    | SOSCRUN                                                                                                                                                                                                          |                                      |                | SOSCGO                                                                                                                 | _             | MFIOFS          | MFIOSEL   |  |  |  |  |

| bit 7                                                                |                                                                                                                                                                                                                  |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

| Legend:                                                              |                                                                                                                                                                                                                  |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                                                                                                                                  |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

| -n = Value a                                                         | at POR                                                                                                                                                                                                           | '1' = Bit is set                     |                | '0' = Bit is clea                                                                                                      | ared          | x = Bit is unkr | nown      |  |  |  |  |

|                                                                      |                                                                                                                                                                                                                  |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 7                                                                | Unimplemen                                                                                                                                                                                                       | ted: Read as 'd                      | )'             |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 6                                                                | SOSCRUN: S                                                                                                                                                                                                       | SOSC Run Stat                        | us bit         |                                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      |                                                                                                                                                                                                                  | lock comes fro                       |                |                                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      | 0 = System c                                                                                                                                                                                                     | lock comes fro                       | m an oscillato | r other than SO                                                                                                        | SC            |                 |           |  |  |  |  |

| bit 5-4                                                              | Unimplemen                                                                                                                                                                                                       | ted: Read as 'd                      | )'             |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 3                                                                | SOSCGO: Os                                                                                                                                                                                                       | SOSCGO: Oscillator Start Control bit |                |                                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      |                                                                                                                                                                                                                  |                                      |                | ources are requ                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      | <ul> <li>0 = Oscillator is shut off if no other sources are requesting it (When the SOSC is selected to run from<br/>a digital clock input, rather than an external crystal, this bit has no effect.)</li> </ul> |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 2                                                                | Unimplemen                                                                                                                                                                                                       | ted: Read as 'd                      | )'             |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 1                                                                | MFIOFS: MF-                                                                                                                                                                                                      | -INTOSC Frequ                        | ency Stable b  | it                                                                                                                     |               |                 |           |  |  |  |  |

|                                                                      | 1 = MF-INTOSC is stable                                                                                                                                                                                          |                                      |                |                                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      | 0 = MF-INTO                                                                                                                                                                                                      | 0 = MF-INTOSC is not stable          |                |                                                                                                                        |               |                 |           |  |  |  |  |

| bit 0                                                                | MFIOSEL: M                                                                                                                                                                                                       | F-INTOSC Sele                        | ect bit        |                                                                                                                        |               |                 |           |  |  |  |  |

|                                                                      | 1 = MF-INTO                                                                                                                                                                                                      | SC is used in p                      | lace of HF-IN  | TOSC frequence                                                                                                         | ies of 500 kH | z, 250 kHz and  | 31.25 kHz |  |  |  |  |

|                                                                      | 0 = MF-INTO                                                                                                                                                                                                      | SC is not used                       |                | 1 = MF-INTOSC is used in place of HF-INTOSC frequencies of 500 kHz, 250 kHz and 31.25 kHz<br>0 = MF-INTOSC is not used |               |                 |           |  |  |  |  |

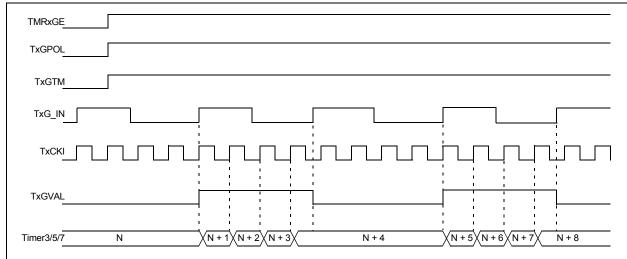

#### 16.5.2 TIMER3/5/7 GATE SOURCE SELECTION

The Timer3/5/7 gate source can be selected from one of four different sources. Source selection is controlled by the TxGSS<1:0> bits (TxGCON<1:0>). The polarity for each available source is also selectable and is controlled by the TxGPOL bit (TxGCON <6>).

| TABLE 16-2: | <b>TIMER3/5/7 GATE SOURCES</b> |

|-------------|--------------------------------|

|             |                                |

| TxGSS<1:0> | Timerx Gate Source                                                     |

|------------|------------------------------------------------------------------------|

| 00         | Timerx Gate Pin                                                        |

| 01         | TMR(x+1) to Match PR(x+1)<br>(TMR(x+1) increments to match<br>PR(x+1)) |

| 10         | Comparator 1 Output<br>(comparator logic high output)                  |

| 11         | Comparator 2 Output<br>(comparator logic high output)                  |

16.5.2.1 TxG Pin Gate Operation

The TxG pin is one source for Timer3/5/7 gate control. It can be used to supply an external source to the Timerx gate circuitry.

#### 16.5.2.2 Timer4/6/8 Match Gate Operation

The TMR(x+1) register will increment until it matches the value in the PR(x+1) register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timerx gate circuitry. The pulse will remain high for one instruction cycle and will return back to a low state until the next match.

Depending on TxGPOL, Timerx increments differently when TMR(x+1) matches PR(x+1). When TxGPOL = 1, Timerx increments for a single instruction

cycle following a TMR(x+1) match with PR(x+1). When TxGPOL = 0, Timerx increments continuously, except for the cycle following the match, when the gate signal goes from low-to-high.

#### 16.5.2.3 Comparator 1 Output Gate Operation

The output of Comparator 1 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 1 with the CM1CON register, Timerx will increment depending on the transitions of the CMP1OUT (CMSTAT<5>) bit.

#### 16.5.2.4 Comparator 2 Output Gate Operation

The output of Comparator 2 can be internally supplied to the Timerx gate circuitry. After setting up Comparator 2 with the CM2CON register, Timerx will increment depending on the transitions of the CMP2OUT (CMSTAT<6>) bit.

#### 16.5.3 TIMER3/5/7 GATE TOGGLE MODE

When Timer3/5/7 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3/5/7 gate signal, as opposed to the duration of a single level pulse.

The Timerx gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 16-3.)

The TxGVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3/5/7 Gate Toggle mode is enabled by setting the TxGTM bit (TxGCON<5>). When the TxGTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 16-3: TIMER3/5/7 GATE TOGGLE MODE

# 24.0 COMPARATOR MODULE

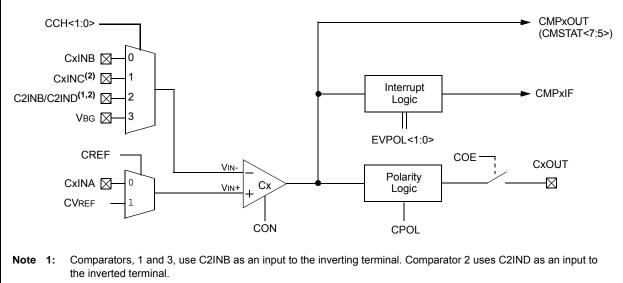

The analog comparator module contains three comparators that can be independently configured in a variety of ways. The inputs can be selected from the analog inputs and two Internal Reference Voltages. The digital outputs are available at the pin level and can also be read through the control register. Multiple output and interrupt event generation are also available. A generic single comparator from the module is shown in Figure 24-1.

Key features of the module includes:

- · Independent comparator control

- · Programmable input configuration

- · Output to both pin and register levels

- · Programmable output polarity

- Independent interrupt generation for each comparator with configurable interrupt-on-change

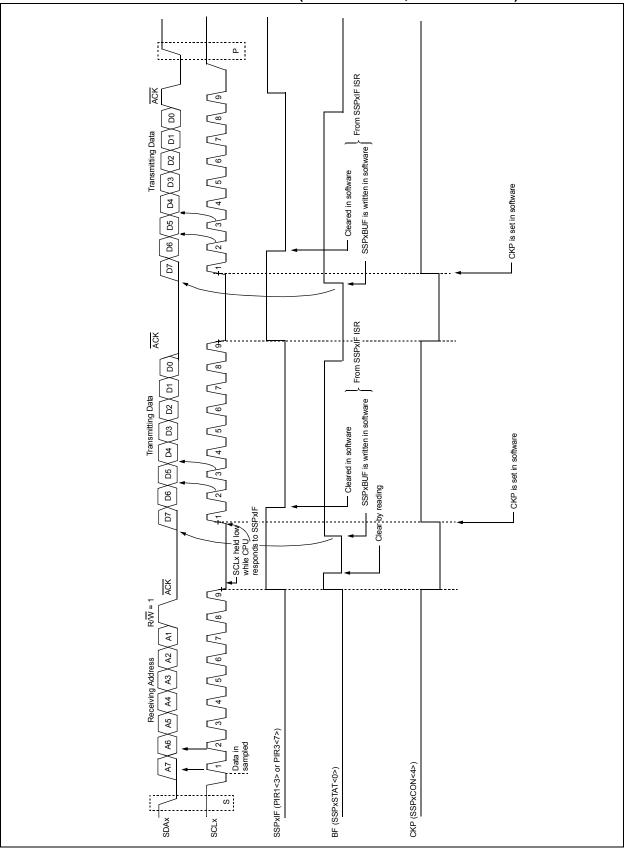

## 24.1 Registers

The CMxCON registers (CM1CON, CM2CON and CM3CON) select the input and output configuration for each comparator, as well as the settings for interrupt generation (see Register 24-1).

The CMSTAT register (Register 24-2) provides the output results of the comparators. The bits in this register are read-only.

2: C1INC, C2INC and C2IND are all unavailable for 64-pin devices (PIC18F6XK22).

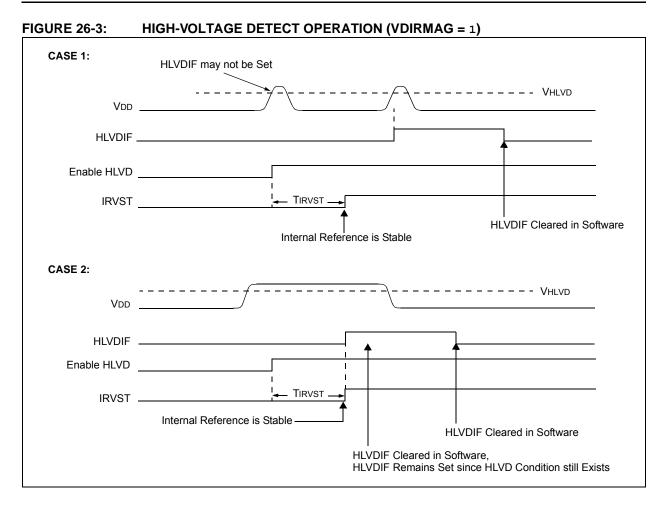

### 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

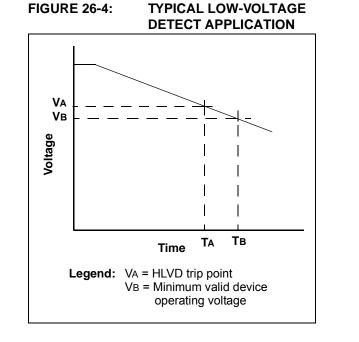

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an Interrupt Service Routine (ISR), which would allow the application to perform "housekeeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

## 26.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 26.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   |

|---------|-----------------------|-----------------------|--------|--------|--------|--------|--------|---------|

| HLVDCON | VDIRMAG               | BGVST                 | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0  |

| INTCON  | GIE/GIEH              | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF    |

| PIR2    | OSCFIF                | —                     | SSP2IF | BLC2IF | BCL1IF | HLVDIF | TMR3IF | TMR3GIF |

| PIE2    | OSCFIE                | _                     | SSP2IE | BLC2IE | BCL1IE | HLVDIE | TMR3IE | TMR3GIE |

| IPR2    | OSCFIP                | _                     | SSP2IP | BLC2IP | BCL1IP | HLVDIP | TMR3IP | TMR3GIP |

| TRISA   | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0  |

| ANCON0  | ANSEL7                | ANSEL6                | ANSEL5 | ANSEL4 | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0  |

#### TABLE 26-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

**Note 1:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

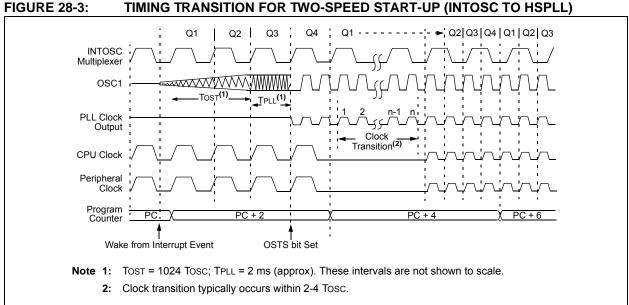

#### 28.4 **Two-Speed Start-up**

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTOSC (LF-INTOSC, MF-INTOSC, HF-INTOSC) oscillator as a clock source until the primary clock source is available; it is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT or HS (Crystal-Based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 28.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to Section 4.1.4 "Multiple Sleep Commands"). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

# 31.2 DC Characteristics: Power-Down and Supply Current PIC18F87K22 Family (Industrial/Extended) (Continued)

| PIC18F87K22 Family<br>(Industrial/Extended) |                           | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array} $ |      |       |                              |                                                             |                                                           |  |  |

|---------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Param<br>No.                                | Device                    | Тур                                                                                                                                                                                                                                                              | Max  | Units |                              | Conditions                                                  |                                                           |  |  |

|                                             | Supply Current (IDD) Cont | (2,3)                                                                                                                                                                                                                                                            |      |       |                              |                                                             |                                                           |  |  |

|                                             | All devices               | 42                                                                                                                                                                                                                                                               | 73   | μA    | -40°C                        |                                                             |                                                           |  |  |

|                                             |                           | 42                                                                                                                                                                                                                                                               | 73   | μA    | +25°C                        | VDD = 1.8V <sup>(4)</sup>                                   | Fosc = 1 MHz<br>( <b>PRI_IDLE</b> mode,<br>EC oscillator) |  |  |

|                                             |                           | 43                                                                                                                                                                                                                                                               | 74   | μA    | +85°C                        | Regulator Disabled                                          |                                                           |  |  |

|                                             |                           | 53                                                                                                                                                                                                                                                               | 100  | μA    | +125°C                       |                                                             |                                                           |  |  |

|                                             | All devices               | 110                                                                                                                                                                                                                                                              | 190  | μA    | -40°C                        |                                                             |                                                           |  |  |

|                                             |                           | 110                                                                                                                                                                                                                                                              | 195  | μA    | +25°C                        | VDD = 3.3V <sup>(4)</sup>                                   |                                                           |  |  |

|                                             |                           | 110                                                                                                                                                                                                                                                              | 195  | μA    | +85°C                        | Regulator Disabled                                          |                                                           |  |  |

|                                             |                           | 130                                                                                                                                                                                                                                                              | 250  | μA    | +125°C                       |                                                             |                                                           |  |  |

|                                             | All devices               | 280                                                                                                                                                                                                                                                              | 450  | μA    | -40°C                        |                                                             |                                                           |  |  |

|                                             |                           | 290                                                                                                                                                                                                                                                              | 440  | μA    | +25°C                        | VDD = 5√ <sup>(5)</sup>                                     |                                                           |  |  |