Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 64MHz                                                                         |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 69                                                                            |

| Program Memory Size        | 64KB (32K x 16)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                   |

| Data Converters            | A/D 24x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

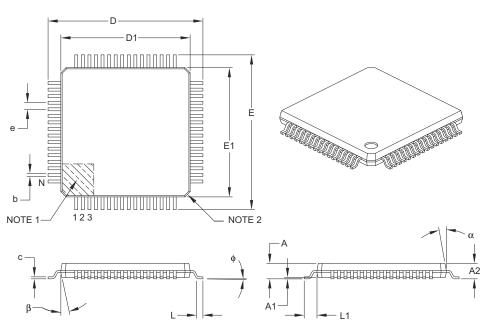

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86k22-i-ptrsl |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Highlights:**

- Up to Ten CCP/ECCP modules:

- Up to seven Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules

- Up to Eleven 8/16-Bit Timer/Counter modules:

- Timer0 8/16-bit timer/counter with 8-bit programmable prescaler

- Timer1,3 16-bit timer/counter

- Timer2,4,6,8 8-bit timer/counter

- Timer5,7 16-bit timer/counter for 64k and 128k parts

- Timer10,12 8-bit timer/counter for 64k and 128k parts

- Three Analog Comparators

- Configurable Reference Clock Output

- Hardware Real-Time Clock and Calendar (RTCC) module with Clock, Calendar and Alarm Functions

- Charge Time Measurement Unit (CTMU):

- Capacitance measurement for mTouch™ sensing solution

- Time measurement with 1 ns typical resolution

- Integrated temperature sensor

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

- Up to Four External Interrupts

- Two Master Synchronous Serial Port (MSSP) modules:

- 3/4-wire SPI (supports all four SPI modes)

- I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Two Enhanced Addressable USART modules:

- LIN/J2602 support

- Auto-Baud Detect (ABD)

- 12-Bit A/D Converter with up to 24 Channels:

- Auto-acquisition and Sleep operationDifferential input mode of operation

- Integrated Voltage Reference

#### 6.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit (CONFIG4L<0>). When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.4 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR                               |

|-----------------|--------------------------------------------------|

| •               | ;SAVED IN FAST REGISTER                          |

| SUB1 •          | ;STACK                                           |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK |

## 6.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

## 6.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the Program Counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value, 'nn', to the calling function.

The offset value (in WREG) specifies the number of bytes that the Program Counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

## 6.1.5.2 Table Reads

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored, two bytes per program word, while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory, one byte at a time.

The table read operation is discussed further in **Section 7.1 "Table Reads and Table Writes**".

## TABLE 6-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F87K22 FAMILY (CONTINUED)

| Addr. | Name                  | Addr. | Name                  | Addr. | Name     | Addr. | Name |

|-------|-----------------------|-------|-----------------------|-------|----------|-------|------|

| F3Fh  | TMR7H <sup>(3)</sup>  | F32h  | TMR12 <sup>(3)</sup>  | F25h  | ANCON0   | F18h  | PMD1 |

| F3Eh  | TMR7L <sup>(3)</sup>  | F31h  | PR12 <sup>(3)</sup>   | F24h  | ANCON1   | F17h  | PMD2 |

| F3Dh  | T7CON <sup>(3)</sup>  | F30h  | T12CON <sup>(3)</sup> | F23h  | ANCON2   | F16h  | PMD3 |

| F3Ch  | T7GCON <sup>(3)</sup> | F2Fh  | CM2CON                | F22h  | RCSTA2   | _     |      |

| F3Bh  | TMR6                  | F2Eh  | CM3CON                | F21h  | TXSTA2   |       |      |

| F3Ah  | PR6                   | F2Dh  | CCPTMRS0              | F20h  | BAUDCON2 |       |      |

| F39H  | T6CON                 | F2Ch  | CCPTMRS1              | F1Fh  | SPBRGH2  |       |      |

| F38h  | TMR8                  | F2Bh  | CCPTMRS2              | F1Eh  | SPBRG2   |       |      |

| F37h  | PR8                   | F2Ah  | REFOCON               | F1Dh  | RCREG2   |       |      |

| F36h  | T8CON                 | F29H  | ODCON1                | F1Ch  | TXREG2   |       |      |

| F35h  | TMR10 <sup>(3)</sup>  | F28h  | ODCON2                | F1Bh  | PSTR2CON |       |      |

| F34h  | PR10 <sup>(3)</sup>   | F27h  | ODCON3                | F1Ah  | PSTR3CON |       |      |

| F33h  | T10CON <sup>(3)</sup> | F26h  | MEMCON <sup>(3)</sup> | F19h  | PMD0     |       |      |

**Note 1:** This is not a physical register.

2: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

- 3: This register is not available on devices with a program memory of 32 Kbytes (PIC18FX5K22).

- 4: Addresses, F16h through F5Fh, are also used by SFRs, but are not part of the Access RAM. To access these registers, users must always load the proper BSR value.

| Address | File Name | Bit 7                                                                                                                              | Bit 6                                               | Bit 5           | Bit 4                                | Bit 3           | Bit 2           | Bit 1            | Bit 0   | Value on<br>POR, BOR |  |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|--------------------------------------|-----------------|-----------------|------------------|---------|----------------------|--|

| FFFh    | TOSU      | —                                                                                                                                  | _                                                   | _               | Top-of-Stack Upper Byte (TOS<20:16>) |                 |                 |                  |         |                      |  |

| FFEh    | TOSH      | Top-of-Stack H                                                                                                                     | ligh Byte (TOS                                      | S<15:8>)        |                                      |                 |                 |                  |         | 0000 0000            |  |

| FFDh    | TOSL      | Top-of-Stack L                                                                                                                     | ow Byte (TOS                                        | <7:0>)          |                                      |                 |                 |                  |         | 0000 0000            |  |

| FFCh    | STKPTR    | STKFUL                                                                                                                             | STKUNF                                              | _               | Return Stack F                       | Pointer         |                 |                  |         | uu-0 0000            |  |

| FFBh    | PCLATU    | —                                                                                                                                  | _                                                   | —               | Holding Regist                       | er for PC<20:1  | 6>              |                  |         | 0 0000               |  |

| FFAh    | PCLATH    | Holding Regis                                                                                                                      | ter for PC<15:                                      | 8>              |                                      |                 |                 |                  |         | 0000 0000            |  |

| FF9h    | PCL       | PC Low Byte                                                                                                                        | (PC<7:0>)                                           |                 |                                      |                 |                 |                  |         | 0000 0000            |  |

| FF8h    | TBLPTRU   | _                                                                                                                                  | _                                                   | bit 21          | Program Mem                          | ory Table Point | ter Upper Byte  | (TBLPTR<20:      | 16>)    | 00 0000              |  |

| FF7h    | TBLPTRH   | Program Mem                                                                                                                        | ory Table Poin                                      | ter High Byte   | (TBLPTR<15:8                         | >)              |                 |                  |         | 0000 0000            |  |

| FF6h    | TBLPTRL   | Program Mem                                                                                                                        | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |                 |                                      |                 |                 |                  |         |                      |  |

| FF5h    | TABLAT    | Program Memory Table Latch                                                                                                         |                                                     |                 |                                      |                 |                 |                  |         | 0000 0000            |  |

| FF4h    | PRODH     | Product Register High Byte                                                                                                         |                                                     |                 |                                      |                 |                 |                  |         | XXXX XXXX            |  |

| FF3h    | PRODL     | Product Regis                                                                                                                      | ter Low Byte                                        |                 |                                      |                 |                 |                  |         | XXXX XXXX            |  |

| FF2h    | INTCON    | GIE/GIEH                                                                                                                           | PEIE/GIEL                                           | TMR0IE          | <b>INTOIE</b>                        | RBIE            | TMR0IF          | INTOIF           | RBIF    | 0000 000x            |  |

| FF1h    | INTCON2   | RBPU                                                                                                                               | INTEDG0                                             | INTEDG1         | INTEDG2                              | INTEDG3         | TMR0IP          | INT3IP           | RBIP    | 1111 1111            |  |

| FF0h    | INTCON3   | INT2IP                                                                                                                             | INT1IP                                              | INT3IE          | INT2IE                               | INT1IE          | INT3IF          | INT2IF           | INT1IF  | 1100 0000            |  |

| FEFh    | INDF0     | Uses contents                                                                                                                      | of FSR0 to ac                                       | dress data me   | emory – value o                      | f FSR0 not cha  | anged (not a pł | nysical register | )       |                      |  |

| FEEh    | POSTINC0  | Uses contents                                                                                                                      | of FSR0 to ac                                       | ldress data me  | emory – value o                      | f FSR0 post-in  | cremented (no   | t a physical reg | gister) |                      |  |

| FEDh    | POSTDEC0  | Uses contents                                                                                                                      | of FSR0 to ac                                       | dress data me   | emory – value o                      | f FSR0 post-de  | ecremented (no  | ot a physical re | gister) |                      |  |

| FECh    | PREINC0   | Uses contents                                                                                                                      | of FSR0 to ac                                       | ldress data me  | emory – value o                      | f FSR0 pre-inc  | remented (not   | a physical regi  | ster)   |                      |  |

| FEBh    | PLUSW0    | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W |                                                     |                 |                                      |                 |                 |                  |         |                      |  |

| FEAh    | FSR0H     | _                                                                                                                                  | _                                                   | _               | _                                    | Indirect Data   | Memory Addre    | ess Pointer 0 H  | igh     | 0000                 |  |

| FE9h    | FSR0L     | Indirect Data N                                                                                                                    | lemory Addre                                        | ss Pointer 0 Lo | ow Byte                              |                 |                 |                  |         | XXXX XXXX            |  |

| FE8h    | WREG      | Working Regis                                                                                                                      | ster                                                |                 |                                      |                 |                 |                  |         | XXXX XXXX            |  |

| FE7h    | INDF1     | Uses contents                                                                                                                      | of FSR1 to ac                                       | dress data me   | emory – value o                      | f FSR1 not cha  | anged (not a pl | nysical register | )       |                      |  |

#### TABLE 6-2: PIC18F87K22 FAMILY REGISTER FILE SUMMARY

Note 1: This bit is available when Master Clear is disabled (MCLRE = 0). When MCLRE is set, the bit is unimplemented.

2: Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

3: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

## 8.0 EXTERNAL MEMORY BUS

| Note:                          | The | External | Memory | Bus | is | not |  |  |

|--------------------------------|-----|----------|--------|-----|----|-----|--|--|

| implemented on 64-pin devices. |     |          |        |     |    |     |  |  |

The External Memory Bus (EMB) allows the device to access external memory devices (such as Flash, EPROM or SRAM) as program or data memory. It supports both 8 and 16-Bit Data Width modes and three address widths of up to 20 bits.

The bus is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals.

A list of the pins and their functions is provided in Table 8-1.

| TABLE 8-1: | PIC18F87K22 FAMILY EXTERNAL BUS – I/O PORT FUNCTIONS |

|------------|------------------------------------------------------|

| Name     | Port  | Bit | External Memory Bus Function           |

|----------|-------|-----|----------------------------------------|

| RD0/AD0  | PORTD | 0   | Address Bit 0 or Data Bit 0            |

| RD1/AD1  | PORTD | 1   | Address Bit 1 or Data Bit 1            |

| RD2/AD2  | PORTD | 2   | Address Bit 2 or Data Bit 2            |

| RD3/AD3  | PORTD | 3   | Address Bit 3 or Data Bit 3            |

| RD4/AD4  | PORTD | 4   | Address Bit 4 or Data Bit 4            |

| RD5/AD5  | PORTD | 5   | Address Bit 5 or Data Bit 5            |

| RD6/AD6  | PORTD | 6   | Address Bit 6 or Data Bit 6            |

| RD7/AD7  | PORTD | 7   | Address Bit 7 or Data Bit 7            |

| RE0/AD8  | PORTE | 0   | Address Bit 8 or Data Bit 8            |

| RE1/AD9  | PORTE | 1   | Address Bit 9 or Data Bit 9            |

| RE2/AD10 | PORTE | 2   | Address Bit 10 or Data Bit 10          |

| RE3/AD11 | PORTE | 3   | Address Bit 11 or Data Bit 11          |

| RE4/AD12 | PORTE | 4   | Address Bit 12 or Data Bit 12          |

| RE5/AD13 | PORTE | 5   | Address Bit 13 or Data Bit 13          |

| RE6/AD14 | PORTE | 6   | Address Bit 14 or Data Bit 14          |

| RE7/AD15 | PORTE | 7   | Address Bit 15 or Data Bit 15          |

| RH0/A16  | PORTH | 0   | Address Bit 16                         |

| RH1/A17  | PORTH | 1   | Address Bit 17                         |

| RH2/A18  | PORTH | 2   | Address Bit 18                         |

| RH3/A19  | PORTH | 3   | Address Bit 19                         |

| RJ0/ALE  | PORTJ | 0   | Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | 1   | Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | 2   | Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | 3   | Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | 4   | Byte Address Bit 0 (BA0)               |

| RJ5/CE   | PORTJ | 5   | Chip Enable (CE) Control pin           |

| RJ6/LB   | PORTJ | 6   | Lower Byte Enable (IB) Control pin     |

| RJ7/UB   | PORTJ | 7   | Upper Byte Enable (UB) Control pin     |

**Note:** For the sake of clarity, only I/O port and external bus assignments are shown here. One or more additional multiplexed features may be available on some pins.

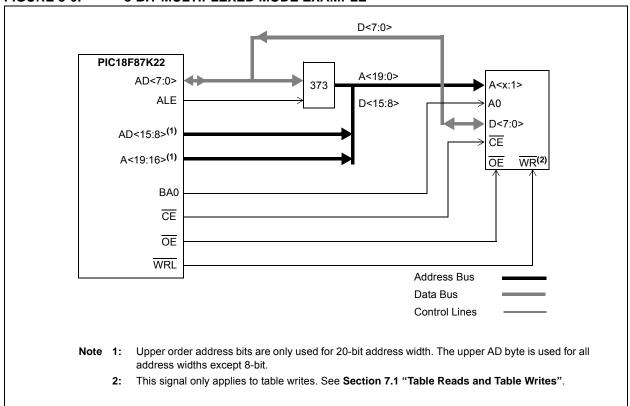

## 8.7 8-Bit Data Width Mode

In 8-Bit Data Width mode, the External Memory Bus operates only in Multiplexed mode; that is, data shares the 8 Least Significant bits of the address bus.

Figure 8-6 shows an example of 8-Bit Multiplexed mode for PIC18F8XK22 devices. This mode is used for a single, 8-bit memory connected for 16-bit operation. The instructions will be fetched as two 8-bit bytes on a shared data/address bus. The two bytes are sequentially fetched within one instruction cycle (TcY). Therefore, the designer must choose external memory devices according to timing calculations based on 1/2 TcY (2 times the instruction rate). For proper memory speed selection, glue logic propagation delay times must be considered, along with setup and hold times.

The Address Latch Enable (ALE) pin indicates that the Address bits, AD<15:0>, are available on the External Memory Bus interface. The Output Enable (OE) signal

will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The Least Significant bit of the address, BA0, must be connected to the memory devices in this mode. The Chip Enable (CE) signal is active at any time that the microcontroller accesses external memory, whether reading or writing. It is inactive (asserted high) whenever the device is in Sleep mode.

This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate level of the BA0 control line is strobed on the LSb of the TBLPTR.

FIGURE 8-6: 8-BIT MULTIPLEXED MODE EXAMPLE

| R/W-1         | R/W-1                          | R/W-1                             | R/W-1             | R/W-1             | R/W-1           | R/W-1           | R/W-1 |

|---------------|--------------------------------|-----------------------------------|-------------------|-------------------|-----------------|-----------------|-------|

| RBPU          | INTEDG0                        | INTEDG1                           | INTEDG2           | INTEDG3           | TMR0IP          | INT3IP          | RBIP  |

| bit 7         |                                |                                   |                   |                   |                 |                 | bit ( |

| Legend:       |                                |                                   |                   |                   |                 |                 |       |

| R = Readable  | e bit                          | W = Writable                      | bit               | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR                            | '1' = Bit is set                  |                   | '0' = Bit is clea | ared            | x = Bit is unkr | iown  |

| bit 7         | RBPU: PORT                     | B Pull-up Enat                    | ole bit           |                   |                 |                 |       |

|               |                                | B pull-ups are                    |                   |                   |                 |                 |       |

|               | 0 = PORTB p                    | oull-ups are ena                  | abled by individ  | dual TRIS regis   | ter values      |                 |       |

| bit 6         | INTEDG0: Ex                    | ternal Interrupt                  | 0 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 5         |                                | ternal Interrupt                  | 1 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge<br>on falling edge |                   |                   |                 |                 |       |

| bit 4         | •                              | ternal Interrupt                  | 2 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 3         | INTEDG3: Ex                    | ternal Interrupt                  | 3 Edge Select     | t bit             |                 |                 |       |

|               |                                | on rising edge                    |                   |                   |                 |                 |       |

|               |                                | on falling edge                   |                   |                   |                 |                 |       |

| bit 2         |                                | R0 Overflow Int                   | errupt Priority   | bit               |                 |                 |       |

|               | 1 = High prio<br>0 = Low prior | •                                 |                   |                   |                 |                 |       |

| bit 1         | •                              | External Intern                   | int Priority bit  |                   |                 |                 |       |

|               | 1 = High prio                  |                                   | upt i nonty bit   |                   |                 |                 |       |

|               | 0 = Low prior                  | •                                 |                   |                   |                 |                 |       |

| bit 0         | RBIP: RB Por                   | rt Change Inter                   | rupt Priority bit | 1                 |                 |                 |       |

|               | 1 = High prio                  |                                   | 2                 |                   |                 |                 |       |

|               | 0 = Low prior                  | ity                               |                   |                   |                 |                 |       |

### REGISTER 11-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| Pin Name        | Function             | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                                                     |

|-----------------|----------------------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RB3/INT3/CTED2/ | RB3                  | 0               | 0   | DIG         | LATB<3> data output.                                                                                                                            |

| ECCP2/P2A       |                      | 1               | I   | TTL         | PORTB<3> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                 | INT3                 | 1               | I   | ST          | External Interrupt 3 input.                                                                                                                     |

|                 | CTED2                | x               | I   | ST          | CTMU Edge 2 input.                                                                                                                              |

|                 | ECCP2 <sup>(1)</sup> | 0               | 0   | DIG         | ECCP2 compare output and ECCP2 PWM output.<br>Takes priority over port data.                                                                    |

|                 |                      | 1               | Ι   | ST          | ECCP2 capture input.                                                                                                                            |

|                 | P2A                  | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, Channel A.<br>May be configured for tri-state during Enhanced PWM shutdown<br>events. Takes priority over port data. |

| RB4/KBI0        | RB4                  | 0               | 0   | DIG         | LATB<4> data output.                                                                                                                            |

|                 |                      | 1               | Ι   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                 | KBI0                 | 1               | Ι   | TTL         | Interrupt-on-pin change.                                                                                                                        |

| RB5/KBI1/T3CKI/ | RB5                  | 0               | 0   | DIG         | LATB<5> data output.                                                                                                                            |

| T1G             |                      | 1               | I   | TTL         | PORTB<5> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared.                                                                 |

|                 | KBI1                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|                 | T3CKI                | x               | I   | ST          | Timer3 clock input.                                                                                                                             |

|                 | T1G                  | x               | I   | ST          | Timer1 external clock gate input.                                                                                                               |

| RB6/KBI2/PGC    | RB6                  | 0               | 0   | DIG         | LATB<6> data output.                                                                                                                            |

|                 |                      | 1               | I   | TTL         | PORTB<6> data input; weak pull-up when $\overline{\text{RBPU}}$ bit is cleared.                                                                 |

|                 | KBI2                 | 1               | I   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|                 | PGC                  | x               | Ι   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operations.                                                                               |

| RB7/KBI3/PGD    | RB7                  | 0               | 0   | DIG         | LATB<7> data output.                                                                                                                            |

|                 |                      | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                 | KBI3                 | 1               | Ι   | TTL         | Interrupt-on-pin change.                                                                                                                        |

|                 | PGD                  | х               | 0   | DIG         | Serial execution data output for ICSP and ICD operations.                                                                                       |

|                 |                      | х               | Ι   | ST          | Serial execution data input for ICSP and ICD operations.                                                                                        |

TABLE 12-3: PORTB FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared and in Extended Microcontroller mode.

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|-----------|---------|---------|---------|--------|--------|--------|

| PORTB   | RB7      | RB6       | RB5     | RB4     | RB3     | RB2    | RB1    | RB0    |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4   | LATB3   | LATB2  | LATB1  | LATB0  |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1 | TRISB0 |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP   |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF | INT2IF | INT1IF |

| ODCON1  | SSP10D   | CCP2OD    | CCP10D  |         | _       | _      |        | SSP2OD |

Legend: Shaded cells are not used by PORTB.

NOTES:

When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 20.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC) and (PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:2> and <1:0>, respectively).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

## REGISTER 20-3: ECCPxAS: ECCPx AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |       |                  |                                    |                    |  |

|-------------------|-------|------------------|------------------------------------|--------------------|--|

| R = Readable      | e bit | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR |       | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

0 = ECCP outputs are operating

## bit 6-4 ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits

- 000 = Auto-shutdown is disabled

- 001 = Comparator C1OUT output is high

- 010 = Comparator C2OUT output is high

- 011 = Either Comparator C1OUT or C2OUT is high

- 100 = VIL on FLTO pin

- 101 = VIL on FLT0 pin or Comparator C1OUT output is high

- 110 = VIL on FLT0 pin or Comparator C2OUT output is high

- 111 = VIL on FLT0 pin or Comparator C1OUT or Comparator C2OUT is high

#### bit 3-2 PSSxAC<1:0>: PxA and PxC Pins Shutdown State Control bits

- 00 = Drive pins, PxA and PxC, to '0'

- 01 = Drive pins, PxA and PxC, to '1'

- 1x = PxA and PxC pins tri-state

#### bit 1-0 **PSSxBD<1:0>:** Pins PxB and PxD Shutdown State Control bits

- 00 = Drive pins, PxB and PxD, to '0'

- 01 = Drive pins, PxB and PxD, to '1'

- 1x = PxB and PxD pins tri-state

## **Note 1:** The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

- 2: Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

#### 20.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2/4/6/8 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HF-INTOSC and the postscaler may not be immediately stable.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCPx module without change.

## 20.4.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

## 20.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states. This forces the ECCP module to reset to a state compatible with previous, non-Enhanced CCP modules used on other PIC18 and PIC16 devices.

|                      |                        | 2314/0/0/10/1         | -      |        |        |        |        |        |

|----------------------|------------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| File Name            | Bit 7                  | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| INTCON               | GIE/GIEH               | PEIE/GIEL             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   |

| RCON                 | IPEN                   | SBOREN                | CM     | RI     | TO     | PD     | POR    | BOR    |

| PIR3                 | TMR5GIF                | —                     | RC2IF  | TX2IF  | CTMUIF | CCP2IF | CCP1IF | RTCCIF |

| PIR4                 | CCP10IF <sup>(1)</sup> | CCP9IF <sup>(1)</sup> | CCP8IF | CCP7IF | CCP6IF | CCP5IF | CCP4IF | CCP3IF |

| PIE3                 | TMR5GIE                | —                     | RC2IE  | TX2IE  | CTMUIE | CCP2IE | CCP1IE | RTCCIE |

| PIE4                 | CCP10IE <sup>(1)</sup> | CCP9IE <sup>(1)</sup> | CCP8IE | CCP7IE | CCP6IE | CCP5IE | CCP4IE | CCP3IE |

| IPR3                 | TMR5GIP                | —                     | RC2IP  | TX2IP  | CTMUIP | CCP2IP | CCP1IP | RTCCIP |

| IPR4                 | CCP10IP <sup>(1)</sup> | CCP9IP <sup>(1)</sup> | CCP8IP | CCP7IP | CCP6IP | CCP5IP | CCP4IP | CCP3IP |

| TRISB                | TRISB7                 | TRISB6                | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| TRISC                | TRISC7                 | TRISC6                | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| TRISE                | TRISE7                 | TRISE6                | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 |

| TRISH <sup>(2)</sup> | TRISH7                 | TRISH6                | TRISH5 | TRISH4 | TRISH3 | TRISH2 | TRISH1 | TRISH0 |

| TMR1H                | Timer1 Register        | High Byte             |        |        |        |        |        |        |

| TMR1L                | Timer1 Register        | Low Byte              |        |        |        |        |        |        |

| TMR2                 | Timer2 Register        |                       |        |        |        |        |        |        |

| TMR3H                | Timer3 Register        | High Byte             |        |        |        |        |        |        |

| TMR3L                | Timer3 Register        | Low Byte              |        |        |        |        |        |        |

| TMR4                 | Timer4 Register        |                       |        |        |        |        |        |        |

| TMR6                 | Timer6 Register        |                       |        |        |        |        |        |        |

| TMR8                 | Timer8 Register        |                       |        |        |        |        |        |        |

| TMR10 <sup>(1)</sup> | TMR10 Register         | r                     |        |        |        |        |        |        |

| TMR12 <sup>(1)</sup> | TMR10 Register         | r                     |        |        |        |        |        |        |

| PR2                  | Timer2 Period R        | Register              |        |        |        |        |        |        |

| PR4                  | Timer4 Period R        | Register              |        |        |        |        |        |        |

| PR6                  | Timer6 Period R        | Register              |        |        |        |        |        |        |

| PR8                  | Timer8 Period R        | Register              |        |        |        |        |        |        |

| PR10 <sup>(1)</sup>  | Timer10 Period         | Register              |        |        |        |        |        |        |

| PR12 <sup>(1)</sup>  | Timer12 Period         | Register              |        |        |        |        |        |        |

#### TABLE 20-4: REGISTERS ASSOCIATED WITH ECCP1/2/3 MODULE AND TIMER1/2/3/4/6/8/10/12

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18F65K22 and PIC18F85K22).

**2:** Unimplemented on 64-pin devices (PIC18F6XK22), read as '0'.

## 23.3 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the Charge Holding (CHOLD) capacitor must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 23-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD).

The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected or changed, the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 23-1 can be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 23-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| • CHOLD =                 | 25 pF                              |

|---------------------------|------------------------------------|

| • Rs =                    | 2.5 kΩ                             |

| • Conversion Error $\leq$ | 1/2 LSb                            |

| • Vdd =                   | $3V \rightarrow Rss = 2 \ k\Omega$ |

| Temperature =             | 85°C                               |

#### EQUATION 23-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

|      |   |                                                                                     |

#### EQUATION 23-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{TC/CHOLD}(\text{RIC} + \text{RSS} + \text{RS}))})$ |

|-------|---|----------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                                |

| TC    | = | -(CHOLD)(RIC + RSS + RS) ln(1/2048)                                                                            |

## EQUATION 23-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =      | TAMP + TC + TCOFF                                                                                                                                |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =      | 0.2 μs                                                                                                                                           |

| TCOFF   | =      | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                 |

| Tempera | ture c | oefficient is only required for temperatures $> 25^{\circ}$ C. Below 25°C, TCOFF = 0 ms.                                                         |

| Тс      | =      | -(Chold)(Ric + Rss + Rs) $\ln(1/2048) \ \mu s$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu s$<br>1.05 $\mu s$ |

| TACQ    | =      | 0.2 μs + 1.05 μs + 1.2 μs<br>2.45 μs                                                                                                             |

## 26.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18F87K22 family of devices has a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt. The High/Low-Voltage Detect Control register (Register 26-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 26-1.

## REGISTER 26-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0                                                                | R-0                 | R-0              | R/W-0            | R/W-0                 | R/W-1                                | R/W-0                 | R/W-0                 |

|----------------------------------------------------------------------|---------------------|------------------|------------------|-----------------------|--------------------------------------|-----------------------|-----------------------|

| VDIRMAG                                                              | BGVST               | IRVST            | HLVDEN           | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup>                | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7                                                                |                     |                  |                  |                       |                                      | •                     | bit 0                 |

|                                                                      |                     |                  |                  |                       |                                      |                       |                       |

| Legend:                                                              |                     |                  |                  |                       |                                      |                       |                       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                     |                  |                  |                       |                                      |                       |                       |

| -n = Value at F                                                      | POR                 | '1' = Bit is set |                  | '0' = Bit is cle      | ared                                 | x = Bit is unkr       | nown                  |

|                                                                      |                     |                  |                  |                       |                                      |                       |                       |

| bit 7                                                                | VDIRMAG: V          | oltage Direction | n Magnitude S    | Select bit            |                                      |                       |                       |

|                                                                      |                     |                  |                  |                       | oint (HLVDL<3:0                      |                       |                       |

|                                                                      | 0 = Event occ       | curs when volta  | ge equals or     | falls below trip      | point (HLVDL<                        | 3:0>)                 |                       |

| bit 6                                                                |                     | d Gap Referend   | •                |                       | ag bit                               |                       |                       |

|                                                                      |                     | and gap voltag   |                  |                       |                                      |                       |                       |

|                                                                      |                     | and gap voltag   |                  |                       |                                      |                       |                       |

| bit 5                                                                |                     | al Reference V   | •                | •                     |                                      |                       |                       |

|                                                                      |                     |                  |                  |                       | e interrupt flag<br>ate the interrup |                       |                       |

|                                                                      |                     | d the HLVD int   |                  |                       |                                      | t hay at the spe      | ecilieu voltage       |

| bit 4                                                                | •                   | gh/Low-Voltage   |                  |                       |                                      |                       |                       |

|                                                                      | 1 = HLVD is         |                  |                  |                       |                                      |                       |                       |

|                                                                      | 0 = HLVD is         | disabled         |                  |                       |                                      |                       |                       |

| bit 3-0                                                              | HLVDL<3:0>          | : Voltage Deteo  | ction Limit bits | (1)                   |                                      |                       |                       |

|                                                                      |                     | • •              | it is used (inp  | ut comes from         | the HLVDIN pin                       | ı)                    |                       |

|                                                                      | 1110 <b>= Maxir</b> | num setting      |                  |                       |                                      |                       |                       |

|                                                                      |                     |                  |                  |                       |                                      |                       |                       |

|                                                                      |                     |                  |                  |                       |                                      |                       |                       |

|                                                                      | 0000 = Minim        | num setting      |                  |                       |                                      |                       |                       |

|                                                                      | the electrical a    |                  |                  | D 400                 |                                      |                       |                       |

## REGISTER 28-9: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1                     | R/C-1       | U-0              | U-0                                     | U-0                                | U-0 | U-0  | U-0   |

|---------------------------|-------------|------------------|-----------------------------------------|------------------------------------|-----|------|-------|

| CPD                       | CPB         | —                | _                                       | —                                  | _   | _    | —     |

| bit 7                     | ·           |                  |                                         |                                    | •   | ·    | bit 0 |

|                           |             |                  |                                         |                                    |     |      |       |

| Legend: C = Clearable bit |             | bit              |                                         |                                    |     |      |       |

| R = Readable              | bit         | W = Writable     | bit                                     | U = Unimplemented bit, read as '0' |     |      |       |

| -n = Value at I           | POR         | '1' = Bit is set | et '0' = Bit is cleared x = Bit is unkn |                                    |     | nown |       |

|                           |             |                  |                                         |                                    |     |      |       |

| bit 7                     | CPD: Data E | EPROM Code I     | Protection bit                          |                                    |     |      |       |

|                           | 1 = Data EE | PROM is not co   | de-protected                            |                                    |     |      |       |

- 0 = Data EEPROM is code-protected

- bit 6 **CPB:** Boot Block Code Protection bit 1 = Boot block is not code-protected<sup>(1)</sup> 0 = Boot block is code-protected<sup>(1)</sup>

- bit 5-0 Unimplemented: Read as '0'

Note 1: For the memory size of the blocks, see Figure 28-6. The boot block size changes with BBSIZO.

## 29.0 INSTRUCTION SET SUMMARY

The PIC18F87K22 family of devices incorporates the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 29.1 Standard Instruction Set

The standard PIC18 MCU instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 29-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 29-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction. The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator, 'b', selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the Program Counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 29-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 29-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 29.1.1 "Standard Instruction Set" provides a description of each instruction.

| IORLW               | Inclusive (         | Inclusive OR Literal with W                                                           |      |               |  |  |  |

|---------------------|---------------------|---------------------------------------------------------------------------------------|------|---------------|--|--|--|

| Syntax:             | IORLW k             | IORLW k                                                                               |      |               |  |  |  |

| Operands:           | $0 \le k \le 255$   | i                                                                                     |      |               |  |  |  |

| Operation:          | (W) .OR. k          | $\rightarrow$ W                                                                       |      |               |  |  |  |

| Status Affected:    | N, Z                | N, Z                                                                                  |      |               |  |  |  |

| Encoding:           | 0000                | 1001                                                                                  | kkkk | kkkk          |  |  |  |

| Description:        |                     | The contents of W are ORed with the eight-bit literal 'k'. The result is placed in W. |      |               |  |  |  |

| Words:              | 1                   | 1                                                                                     |      |               |  |  |  |

| Cycles:             | 1                   |                                                                                       |      |               |  |  |  |

| Q Cycle Activity:   |                     |                                                                                       |      |               |  |  |  |

| Q1                  | Q2                  | Q3                                                                                    |      | Q4            |  |  |  |

| Decode              | Read<br>literal 'k' | Proce<br>Data                                                                         |      | Vrite to<br>W |  |  |  |

| Example:            | IORLW               | 35h                                                                                   |      |               |  |  |  |

| Before Instruc<br>W | tion<br>= 9Ah       |                                                                                       |      |               |  |  |  |

| IORWF             | Inclusive C                                                                                                 | Inclusive OR W with f                                                                                                                 |                                                                 |                                                |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|--|--|--|

| Syntax:           | IORWF f                                                                                                     | {,d {,a}}                                                                                                                             |                                                                 |                                                |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                          |                                                                                                                                       |                                                                 |                                                |  |  |  |

| Operation:        | (W) .OR. (f)                                                                                                | $\rightarrow$ dest                                                                                                                    |                                                                 |                                                |  |  |  |

| Status Affected:  | N, Z                                                                                                        |                                                                                                                                       |                                                                 |                                                |  |  |  |

| Encoding:         | 0001                                                                                                        | 00da                                                                                                                                  | ffff                                                            | ffff                                           |  |  |  |

| Description:      | '0', the resu                                                                                               | Inclusive OR W with register 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f'. |                                                                 |                                                |  |  |  |

|                   | , -                                                                                                         | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.                              |                                                                 |                                                |  |  |  |

|                   | If 'a' is '0' ar<br>set is enabl<br>in Indexed I<br>mode when<br>Section 29.<br>Bit-Oriente<br>Literal Offs | ed, this i<br>₋iteral O<br>ever f ≤<br>.2.3 "By<br>d Instru                                                                           | nstruction<br>ffset Addr<br>95 (5Fh).<br>te-Orient<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |

| Words:            | 1                                                                                                           |                                                                                                                                       |                                                                 |                                                |  |  |  |

| Cycles:           | 1                                                                                                           |                                                                                                                                       |                                                                 |                                                |  |  |  |

| Q Cycle Activity: |                                                                                                             |                                                                                                                                       |                                                                 |                                                |  |  |  |

| Q1                | Q2                                                                                                          | Q3                                                                                                                                    | 3                                                               | Q4                                             |  |  |  |

| Decode            | Read<br>register 'f'                                                                                        | Proce<br>Data                                                                                                                         |                                                                 | Vrite to<br>stination                          |  |  |  |

| Example:          | IORWF RE                                                                                                    | ESULT,                                                                                                                                | 0, 1                                                            |                                                |  |  |  |

| W             | =   | 9Ah |  |  |  |

|---------------|-----|-----|--|--|--|

| After Instruc |     |     |  |  |  |

| W             | BFh |     |  |  |  |

|               |     |     |  |  |  |

| imple:            | IOF | SME, |

|-------------------|-----|------|

| Before Instructi  | on  |      |

| RESULT            | =   | 13h  |

| W                 | =   | 91h  |

| After Instruction | ۱   |      |

| RESULT            | =   | 13h  |

| W                 | =   | 93h  |

|                   |     |      |

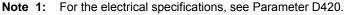

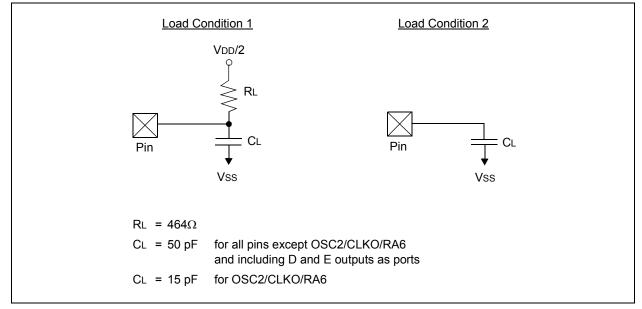

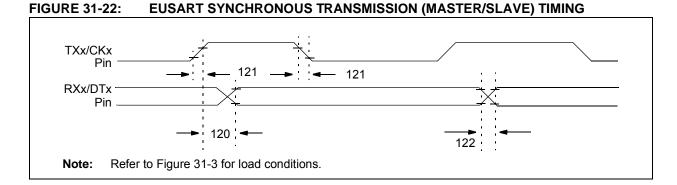

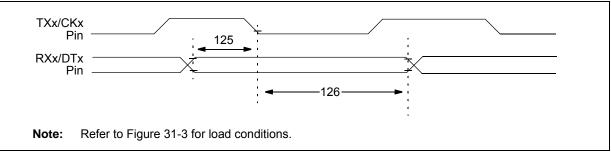

## 31.5.2 TIMING CONDITIONS

The temperature and voltages specified in Table 31-5 apply to all timing specifications unless otherwise noted. Figure 31-3 specifies the load conditions for the timing specifications.

#### TABLE 31-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions (unless otherwise stated)                                   |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial               |  |  |  |

| AC CHARACTERISTICS | $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                                      |  |  |  |

|                    | Operating voltage VDD range as described in <b>Section 31.1</b> and <b>Section 31.3</b> . |  |  |  |

#### FIGURE 31-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

| Param.<br>No. | Symbol  | Characteris                | tic          | Min         | Max  | Units | Conditions                              |  |

|---------------|---------|----------------------------|--------------|-------------|------|-------|-----------------------------------------|--|

| 100           | Тнідн   | Clock High Time            | 100 kHz mode | 4.0         |      | μS    |                                         |  |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    |                                         |  |

|               |         |                            | MSSP module  | 1.5 TCY     | —    |       |                                         |  |

| 101           | TLOW    | Clock Low Time             | 100 kHz mode | 4.7         | —    | μS    |                                         |  |

|               |         |                            | 400 kHz mode | 1.3         | —    | μS    |                                         |  |

|               |         |                            | MSSP module  | 1.5 TCY     | —    |       |                                         |  |

| 102           | TR      | SDAx and SCLx Rise Time    | 100 kHz mode | —           | 1000 | ns    |                                         |  |

|               |         |                            | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | CB is specified to be from 10 to 400 pF |  |

| 103           | TF      | SDAx and SCLx Fall Time    | 100 kHz mode | —           | 300  | ns    |                                         |  |

|               |         |                            | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | CB is specified to be from 10 to 400 pF |  |

| 90            | TSU:STA | Start Condition Setup Time | 100 kHz mode | 4.7         | —    | μS    | Only relevant for Repeated              |  |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    | Start condition                         |  |

| 91            | THD:STA | Start Condition Hold Time  | 100 kHz mode | 4.0         | —    | μS    | After this period, the first clock      |  |

|               |         |                            | 400 kHz mode | 0.6         | —    | μS    | pulse is generated                      |  |