Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 69                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87k22t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

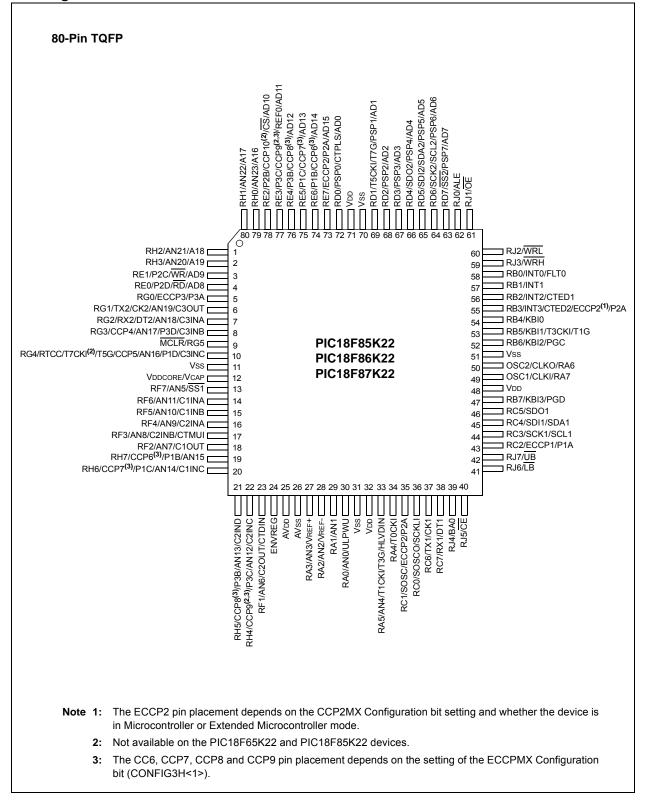

### Pin Diagrams – PIC18F8XK22

### 1.3 Details on Individual Family Members

Devices in the PIC18F87K22 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in these ways:

- Flash Program Memory:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – 32 Kbytes

- PIC18FX6K22 (PIC18F66K22 and PIC18F86K22) 64 Kbytes

- PIC18FX7K22 (PIC18F67K22 and PIC18F87K22) 128 Kbytes

- Data RAM:

- All devices except PIC18FX5K22 4 Kbytes

- PIC18FX5K22 2 Kbytes

- I/O Ports:

- PIC18F6XK22 (64-pin devices) 7 bidirectional ports

- PIC18F8XK22 (80-pin devices) 9 bidirectional ports

- CCP modules:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – 5 CCP modules

- PIC18FX6K22 and PIC18FX7K22 (PIC18F66K22, PIC18F86K22, PIC18F67K22, and PIC18F87K22) – 7 CCP modules

- · Timer modules:

- PIC18FX5K22 (PIC18F65K22 and PIC18F85K22) – Four 8-bit timer/counters and four 16-bit timer/counters

- PIC18FX6K22 and PIC18FX7K22 (PIC18F66K22, PIC18F86K22, PIC18F67K22, and PIC18F87K22) – Six 8-bit timer/counters and five 16-bit timer/counters

- A/D Channels:

- PIC18F6XK22 (64-pin devices) 24 channels

- PIC18F8XK22 (80-pin devices) 16 channels

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

| Din Nama                                                           | Pin Number                        | Pin                  | Buffer                       | Description                                                                                                                              |

|--------------------------------------------------------------------|-----------------------------------|----------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                           | QFN/TQFP                          | Туре                 | Туре                         | Description                                                                                                                              |

|                                                                    |                                   |                      |                              | PORTC is a bidirectional I/O port.                                                                                                       |

| RC0/SOSCO/SCLKI<br>RC0<br>SOSCO<br>SCLKI                           | 30                                | I/O<br>O<br>I        | ST<br>—<br>ST                | Digital I/O.<br>SOSC oscillator output.<br>Digital SOSC input.                                                                           |

| RC1/SOSCI/ECCP2/P2A<br>RC1<br>SOSCI<br>ECCP2 <sup>(1)</sup><br>P2A | 29                                | I/O<br>I<br>I/O<br>O | ST<br>CMOS<br>ST             | Digital I/O.<br>SOSC oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>Enhanced PWM2 Output A.                       |

| RC2/ECCP1/P1A<br>RC2<br>ECCP1<br>P1A                               | 33                                | I/O<br>I/O<br>O      | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>Enhanced PWM1 Output A.                                                 |

| RC3/SCK1/SCL1<br>RC3<br>SCK1<br>SCL1 <sup>(4)</sup>                | 34                                | I/O<br>I/O<br>I/O    | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI1/SDA1<br>RC4<br>SDI1<br>SDA1 <sup>(4)</sup>                | 35                                | I/O<br>I<br>I/O      | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |

| RC5/SDO1<br>RC5<br>SDO1                                            | 36                                | I/O<br>O             | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                                                            |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                                   | 31                                | I/O<br>O<br>I/O      | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX1/DT1).                                         |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                                   | 32                                | I/O<br>I<br>I/O      | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX1/CK1).                                           |

| Legend: TTL = TTL con<br>ST = Schmitt<br>I = Input                 | npatible input<br>Trigger input w | ∕ith C№              | 10S levels                   | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output                                                            |

### TABLE 1-3: PIC18F6XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power

$I^2C = I^2C^{TM}/SMBus$

Note 1: Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2 when the CCP2MX Configuration bit is cleared.

3: Not available on PIC18F65K22 and PIC18F85K22 devices.

**4:** The CC6, CCP7, CCP8 and CCP9 pin placement depends on the setting of the ECCPMX Configuration bit (CONFIG3H<1>).

OD

= Open-Drain (no P diode to VDD)

## 3.0 OSCILLATOR CONFIGURATIONS

### 3.1 Oscillator Types

The PIC18F87K22 family of devices can be operated in the following oscillator modes:

- EC External clock, RA6 available

- ECIO External clock, clock out RA6 (Fosc/4 on RA6)

- HS High-Speed Crystal/Resonator

- XT Crystal/Resonator

- LP Low-Power Crystal

- RC External Resistor/Capacitor, RA6 available

- RCIO External Resistor/Capacitor, clock out RA6 (Fosc/4 on RA6)

- INTIO2 Internal Oscillator with I/O on RA6 and RA7

- INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

There is also an option for running the 4xPLL on any of the clock sources in the input frequency range of 4 to 16 MHz.

The PLL is enabled by setting the PLLCFG bit (CONFIG1H<4>) or the PLLEN bit (OSCTUNE<6>).

For the EC and HS mode, the PLLEN (software) or PLLCFG (CONFIG) bit can be used to enable the PLL.

For the INTIOx modes (HF-INTOSC):

- Only the PLLEN can enable the PLL (PLLCFG is ignored).

- When the oscillator is configured for the internal oscillator (FOSC<3:0> = 100x), the PLL can be enabled only when the HF-INTOSC frequency is 8 or 16 MHz.

When the RA6 and RA7 pins are not used for an oscillator function or CLKOUT function, they are available as general purpose I/Os. To optimize power consumption when using EC/HS/ XT/LP/RC as the primary oscillator, the frequency input range can be configured to yield an optimized power bias:

- Low-Power Bias External frequency less than 160 kHz

- Medium Power Bias External frequency between 160 kHz and 16 MHz

- High-Power Bias External frequency greater than 16 MHz

All of these modes are selected by the user by programming the FOSC<3:0> Configuration bits (CONFIG1H<3:0>). In addition, PIC18F87K22 family devices can switch between different clock sources, either under software control or, under certain conditions, automatically. This allows for additional power savings by managing device clock speed in real time without resetting the application. The clock sources for the PIC18F87K22 family of devices are shown in Figure 3-1.

For the HS and EC mode, there are additional power modes of operation – depending on the frequency of operation.

HS1 is the Medium Power mode with a frequency range of 4 MHz to 16 MHz. HS2 is the High-Power mode, where the oscillator frequency can go from 16 MHz to 25 MHz. HS1 and HS2 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 406.)

EC mode has these modes of operation:

- EC1 For low power with a frequency range up to 160 kHz

- EC2 Medium power with a frequency range of 160 kHz to 16 MHz

- EC3 High power with a frequency range of 16 MHz to 64 MHz

EC1, EC2 and EC3 are achieved by setting the CONFIG1H<3:0> correctly. (For details, see Register 28-2 on page 406.)

Table 3-1 shows the HS and EC modes' frequency range and FOSC<3:0> settings.

## 4.0 POWER-MANAGED MODES

The PIC18F87K22 family of devices offers a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (such as battery-powered devices).

There are three categories of power-managed mode:

- Run modes

- Idle modes

- · Sleep mode

There is an Ultra Low-Power Wake-up (ULPWU) for waking from the Sleep mode.

These categories define which portions of the device are clocked, and sometimes, at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block). The Sleep mode does not use a clock source.

The ULPWU mode, on the RA0 pin, enables a slow falling voltage to generate a wake-up, even from Sleep, without excess current consumption. (See **Section 4.7 "Ultra Low-Power Wake-up"**.)

The power-managed modes include several powersaving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices. This feature allows the controller to use the SOSC oscillator instead of the primary one. Another power-saving feature is Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions:

- · Will the CPU be clocked or not

- · What will be the clock source

The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits select one of three clock sources for power-managed modes. Those sources are:

- The primary clock as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the SOSC oscillator)

- The internal oscillator block (for LF-INTOSC modes)

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These considerations are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entering the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current and impending mode, a change to a power-managed mode does not always require setting all of the previously discussed bits. Many transitions can be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured as desired, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | oscco                   | ON Bits  | Module  | Clocking    | Available Clock and Oscillator Source                                                         |

|----------|-------------------------|----------|---------|-------------|-----------------------------------------------------------------------------------------------|

| Mode     | IDLEN<7> <sup>(1)</sup> | SCS<1:0> | CPU     | Peripherals | Available Clock and Oscillator Source                                                         |

| Sleep    | 0                       | N/A      | Off     | Off         | None – All clocks are disabled                                                                |

| PRI_RUN  | N/A                     | 00       | Clocked | Clocked     | Primary – XT, LP, HS, EC, RC and PLL modes.<br>This is the normal, Full-Power Execution mode. |

| SEC_RUN  | N/A                     | 01       | Clocked | Clocked     | Secondary – SOSC Oscillator                                                                   |

| RC_RUN   | N/A                     | 1x       | Clocked | Clocked     | Internal oscillator block <sup>(2)</sup>                                                      |

| PRI_IDLE | 1                       | 00       | Off     | Clocked     | Primary – LP, XT, HS, RC, EC                                                                  |

| SEC_IDLE | 1                       | 01       | Off     | Clocked     | Secondary – SOSC oscillator                                                                   |

| RC_IDLE  | 1                       | lx       | Off     | Clocked     | Internal oscillator block <sup>(2)</sup>                                                      |

TABLE 4-1:POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

<sup>2:</sup> Includes INTOSC (HF-INTOSC and MG-INTOSC) and INTOSC postscaler, as well as the LF-INTOSC source.

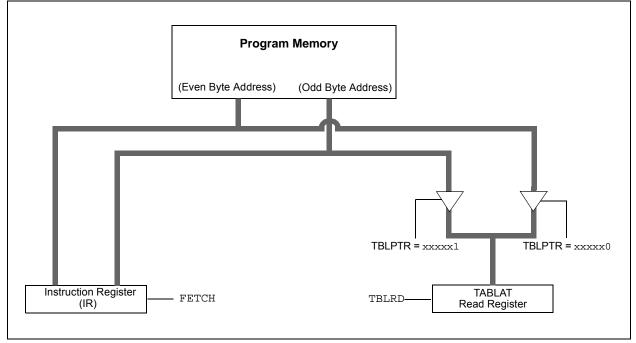

### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed, one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, the TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | BCF     | EECON1, CFGS    | ; point to Flash program memory  |

|-----------|---------|-----------------|----------------------------------|

|           | BSF     | EECON1, EEPGD   | ; access Flash program memory    |

|           | MOVLW   | CODE_ADDR_UPPER | ; Load TBLPTR with the base      |

|           | MOVWF   | TBLPTRU         | ; address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |                                  |

|           | MOVWF   | TBLPTRH         |                                  |

|           | MOVLW   | CODE_ADDR_LOW   |                                  |

|           | MOVWF   | TBLPTRL         |                                  |

| READ_WORD |         |                 |                                  |

|           | TBLRD*- | ÷               | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVWF   | WORD_EVEN       |                                  |

|           | TBLRD*- | ÷               | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; get data                       |

|           | MOVF    | WORD_ODD        |                                  |

|           |         |                 |                                  |

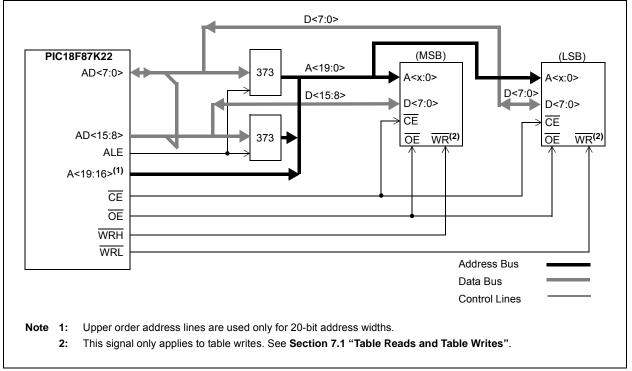

### 8.6.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F87K22 family devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

| Pin Name    | Function | TRIS<br>Setting | I/O | l/O<br>Type      | Description                                                                       |

|-------------|----------|-----------------|-----|------------------|-----------------------------------------------------------------------------------|

| RC3/SCK1/   | RC3      | 0               | 0   | DIG              | LATC<3> data output.                                                              |

| SCL1        |          | 1               | Ι   | ST               | PORTC<3> data input.                                                              |

|             | SCK1     | 0               | 0   | DIG              | SPI clock output (MSSP module); takes priority over port data.                    |

|             |          | 1               | Ι   | ST               | SPI clock input (MSSP module).                                                    |

|             | SCL1     | 0               | 0   | DIG              | I <sup>2</sup> C clock output (MSSP module); takes priority over port data.       |

|             |          | 1               | Ι   | l <sup>2</sup> C | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting. |

| RC4/SDI1/   | RC4      | 0               | 0   | DIG              | LATC<4> data output.                                                              |

| SDA1        |          | 1               | Ι   | ST               | PORTC<4> data input.                                                              |

|             | SDI1     |                 | Ι   | ST               | SPI data input (MSSP module).                                                     |

|             | SDA1     | 1               | 0   | DIG              | I <sup>2</sup> C data output (MSSP module); takes priority over port data.        |

|             |          | 1               | Ι   | l <sup>2</sup> C | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.  |

| RC5/SDO1    | RC5      | 0               | 0   | DIG              | LATC<5> data output.                                                              |

|             |          | 1               | Ι   | ST               | PORTC<5> data input.                                                              |

|             | SDO1     | 0               | 0   | DIG              | SPI data output (MSSP module).                                                    |

| RC6/TX1/CK1 | RC6      | 0               | 0   | DIG              | LATC<6> data output.                                                              |

|             |          | 1               | -   | ST               | PORTC<6> data input.                                                              |

|             | TX1      | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data.    |

|             | CK1      | 1               | 0   | DIG              | Synchronous serial data input (EUSART module); user must configure as an input.   |

|             |          | 1               | Ι   | ST               | Synchronous serial clock input (EUSART module).                                   |

| RC7/RX1/DT1 | RC7      | 0               | 0   | DIG              | LATC<7> data output.                                                              |

|             |          | 1               | Ι   | ST               | PORTC<7> data input.                                                              |

|             | RX1      | 1               | Ι   | ST               | Asynchronous serial receive data input (EUSART module).                           |

|             | DT1      | 1               | 0   | DIG              | Synchronous serial data output (EUSART module); takes priority over port data.    |

|             |          | 1               | Ι   | ST               | Synchronous serial data input (EUSART module); user must configure as an input.   |

TABLE 12-5: PORTC FUNCTIONS (CONTINUED)

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $I^2C = I^2C^{TM}$ /SMBus Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for ECCP2 when the CCP2MX Configuration bit is set.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| PORTC  | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    |

| LATC   | LATC7  | LATBC6 | LATC5  | LATCB4 | LATC3  | LATC2  | LATC1  | LATC0  |

| TRISC  | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| ODCON1 | SSP10D | CCP2OD | CCP10D | _      | _      |        | _      | SSP2OD |

| ODCON3 | U2OD   | U10D   | _      | _      | _      | _      | _      | CTMUDS |

Legend: Shaded cells are not used by PORTC.

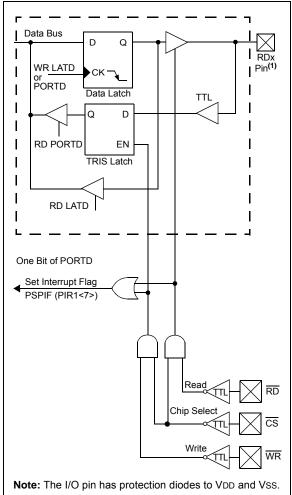

## 12.11 Parallel Slave Port

PORTD can function as an 8-bit-wide Parallel Slave Port (PSP), or microprocessor port, when control bit, PSPMODE (PSPCON<4>), is set. The port is asynchronously readable and writable by the external world through the RD control input pin (RE0/P2D/RD/AD8) and WR control input pin (RE1/P2C/WR/AD9).

| Note: | The Parallel Slave Port is available only in |

|-------|----------------------------------------------|

|       | Microcontroller mode.                        |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an eight-bit latch.

Setting bit, PSPMODE, enables port pin, RE0/P2D/RD/AD8, to be the RD input, RE1/P2C/WR/AD9 to be the WR input and RE2/P2B/CCP10/CS/AD10 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (= 111).

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits (PIR1<7> and PSPCON<7>, respectively) are set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit (PSPCON<6>) is set. If the user writes new data to PORTD to set OBF, the data is immediately read out, but the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  line is detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP. When this happens, the IBF and OBF bits can be polled and the appropriate action taken.

The timing for the control signals in Write and Read modes is shown in Figure 12-4 and Figure 12-5, respectively.

## FIGURE 12-3: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

NOTES:

|    |                                                                 |                                                                                                              | -              | ł                        | - Period             |                    |

|----|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|--------------------------|----------------------|--------------------|

| 00 | (Single Output)                                                 | PxA Modulated                                                                                                |                |                          |                      |                    |

|    |                                                                 | PxA Modulated                                                                                                |                | ►<br>elay <sup>(1)</sup> | Delay <sup>(1)</sup> |                    |

| 10 | (Half-Bridge)                                                   | PxB Modulated                                                                                                | ;<br>;         | siay"                    |                      |                    |

|    |                                                                 | PxA Active                                                                                                   |                |                          |                      |                    |

| 01 | (Full-Bridge,<br>Forward)                                       | PxB Inactive                                                                                                 |                |                          | <u> </u>             | <i>i</i><br>I<br>I |

| 01 | Forward)                                                        | PxC Inactive                                                                                                 | _ :            |                          |                      | I<br>              |

|    |                                                                 | PxD Modulated                                                                                                | = —Ĺ           |                          |                      |                    |

|    |                                                                 | PxA Inactive                                                                                                 |                |                          | 1                    | 1<br>1<br>1        |

| 11 | (Full-Bridge,                                                   | PxB Modulated                                                                                                | = – <u> </u> _ |                          |                      | 1                  |

|    | Reverse)                                                        | PxC Active                                                                                                   |                |                          | 1<br>                |                    |

|    |                                                                 | PxD Inactive                                                                                                 | '              |                          |                      | i<br>i<br>i        |

|    | <ul> <li>Pulse Width = Tos</li> <li>Delay = 4 * Tosc</li> </ul> | * (PR2 + 1) * (TMR2 Pre<br>sc * (CCPRxL<7:0>:CCP<br>* (ECCPxDEL<6:0>)<br>  delay is programmed usir<br>log") | xCON<5:4>)     | ·                        | ,                    | ammable Dead-Banc  |

### FIGURE 20-5: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

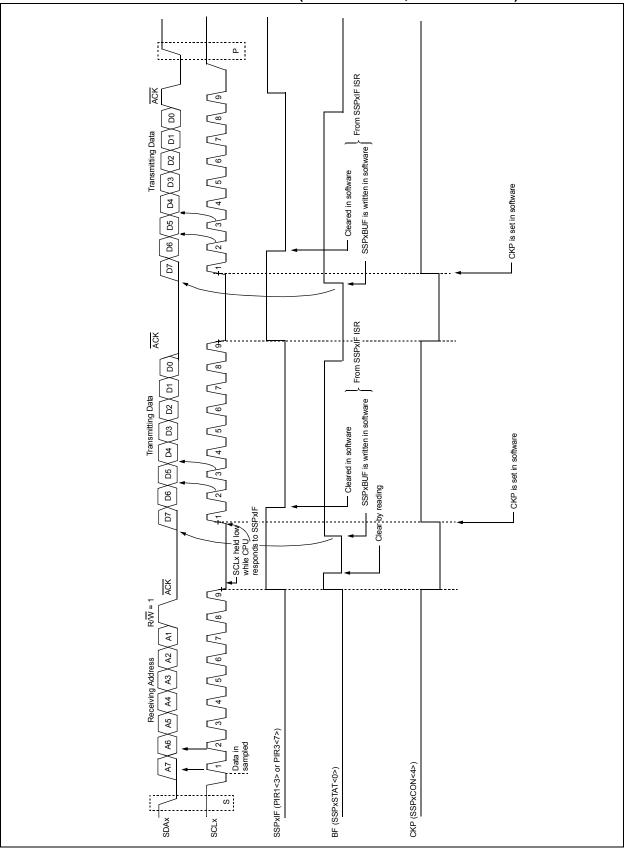

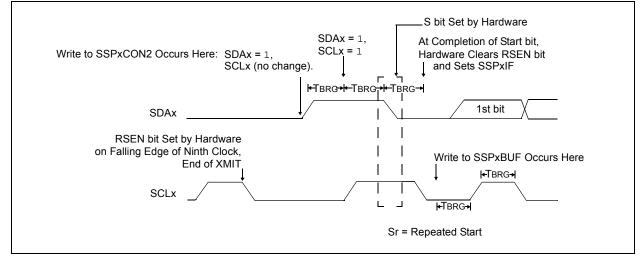

### 21.4.9 I<sup>2</sup>C<sup>™</sup> MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, and if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 21.4.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 21-22: REPEATED START CONDITION WAVEFORM

| R/W-0         | R-1                                        | R/W-0                                                  | R/W-0            | R/W-0                             | U-0             | R/W-0           | R/W-0           |

|---------------|--------------------------------------------|--------------------------------------------------------|------------------|-----------------------------------|-----------------|-----------------|-----------------|

| ABDOVF        | RCIDL                                      | RXDTP                                                  | TXCKP            | BRG16                             | _               | WUE             | ABDEN           |

| bit 7         |                                            |                                                        |                  |                                   |                 |                 | bit             |

| Legend:       |                                            |                                                        |                  |                                   |                 |                 |                 |

| R = Readabl   | e bit                                      | W = Writable                                           | bit              | U = Unimplem                      | ented bit, read | d as '0'        |                 |

| -n = Value at | POR                                        | '1' = Bit is set                                       |                  | ʻ0' = Bit is clea                 | red             | x = Bit is unki | nown            |

| bit 7         |                                            | to-Baud Acquis                                         |                  | Status bit<br>uto-Baud Rate I     | Detect mode (I  | must be cleare  | d in software)  |

|               | 0 = No BRG                                 | rollover has oc                                        | curred           |                                   |                 |                 |                 |

| bit 6         |                                            | ive Operation I                                        |                  |                                   |                 |                 |                 |

|               |                                            | peration is Idle                                       |                  |                                   |                 |                 |                 |

| bit 5         | RXDTP: Data                                | /Receive Polar                                         | ity Select bit   |                                   |                 |                 |                 |

|               |                                            | <u>s mode:</u><br>lata (RXx) is in<br>lata (RXx) is no |                  |                                   |                 |                 |                 |

|               |                                            | mode:<br><) is inverted (a<br><) is not inverte        |                  |                                   |                 |                 |                 |

| bit 4         | TXCKP: Sync                                | hronous Clock                                          | Polarity Selec   | t bit                             |                 |                 |                 |

|               | Asynchronous<br>1 = Idle state             |                                                        | (x) is a low lev | el                                |                 |                 |                 |

|               |                                            | <u>mode:</u><br>for clock (CKx)<br>for clock (CKx)     |                  |                                   |                 |                 |                 |

| bit 3         | <b>BRG16:</b> 16-B                         | it Baud Rate R                                         | egister Enable   | bit                               |                 |                 |                 |

|               |                                            |                                                        |                  | Hx and SPBRGA                     |                 | RGHx value ig   | nored           |

| bit 2         | Unimplemen                                 | ted: Read as '                                         | )'               |                                   |                 |                 |                 |

| bit 1         | WUE: Wake-u                                | up Enable bit                                          |                  |                                   |                 |                 |                 |

|               | hardware                                   |                                                        | sing edge        | RXx pin – interru<br>letected     | ipt generated   | on falling edge | ; bit cleared i |

|               | Synchronous<br>Unused in this              |                                                        |                  |                                   |                 |                 |                 |

| bit 0         |                                            | -Baud Detect I                                         | -<br>nable bit   |                                   |                 |                 |                 |

|               | Asynchronous<br>1 = Enable b<br>cleared ir | <u>s mode:</u><br>aud rate meas<br>ı hardware upo      | urement on the   | e next character<br>has completed | r. Requires re  | ception of a Sy | ync field (55h  |

|               | Synchronous<br>Unused in this              |                                                        |                  |                                   |                 |                 |                 |

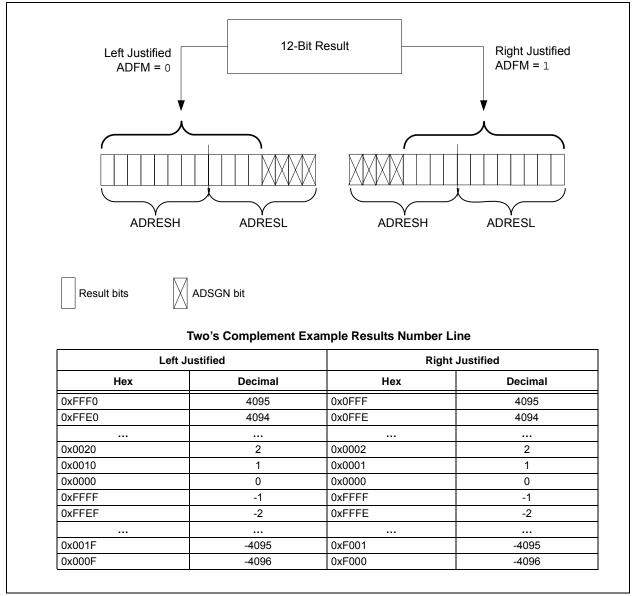

### 23.2.2 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is where the 12-bit A/D result and extended sign bits (ADSGN) are loaded at the completion of a conversion. This register pair is 16 bits wide. The A/D module gives the flexibility of left or right justifying the 12-bit result in the 16-Bit Result register. The A/D Format Select bit (ADFM) controls this justification. Figure 23-3 shows the operation of the A/D result justification and location of the extended sign bits (ADSGN). The extended sign bits allow for easier 16-bit math to be performed on the result. The results are represented as a two's compliment binary value. This means that when sign bits and magnitude bits are considered together in right justification, the ADRESH and ADRESL registers can be read as a single signed integer value.

When the A/D Converter is disabled, these 8-bit registers can be used as two general purpose registers.

FIGURE 23-3: A/D RESULT JUSTIFICATION

| BRA   |                                                                 | Unconditio                                                                             | onal Brai                                         | nch                                      |                  |

|-------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------|------------------|

| Synta | ax:                                                             | BRA n                                                                                  |                                                   |                                          |                  |

| Oper  | ands:                                                           | -1024 ≤ n ≤                                                                            | ≤ 1023                                            |                                          |                  |

| Oper  | ation:                                                          | (PC) + 2 +                                                                             | $2n \rightarrow PC$                               | ;                                        |                  |

| Statu | s Affected:                                                     | None                                                                                   |                                                   |                                          |                  |

| Enco  | ding:                                                           | 1101                                                                                   | 0nnn                                              | nnnr                                     | n nnnn           |

| Desc  | ription:                                                        | Add the 2's<br>the PC. Sir<br>incremente<br>instruction,<br>PC + 2 + 2<br>two-cycle in | nce the P<br>ed to fetch<br>the new<br>n. This in | C will h<br>the ne<br>addres<br>structio | ext<br>s will be |

| Word  | ls:                                                             | 1                                                                                      |                                                   |                                          |                  |

| Cycle | es:                                                             | 2                                                                                      |                                                   |                                          |                  |

| QC    | ycle Activity:                                                  |                                                                                        |                                                   |                                          |                  |

|       | Q1                                                              | Q2                                                                                     | Q3                                                |                                          | Q4               |

|       | Decode                                                          | Read literal<br>'n'                                                                    | Proce<br>Data                                     |                                          | Write to<br>PC   |

|       | No<br>operation                                                 | No<br>operation                                                                        | No<br>operat                                      | ion                                      | No<br>operation  |

|       | n <u>ple:</u><br>Before Instruc<br>PC<br>After Instructio<br>PC | = ac                                                                                   | Idress (1                                         | Jump<br>HERE)<br>Jump)                   |                  |

| BSF                                | Bit Set f                                                                                      |                                                                      |                                                     |                                                  |

|------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|

| Syntax:                            | BSF f, b {                                                                                     | [,a}                                                                 |                                                     |                                                  |

| Operands:                          | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$             |                                                                      |                                                     |                                                  |

| Operation:                         | $1 \rightarrow \text{f}$                                                                       |                                                                      |                                                     |                                                  |

| Status Affected:                   | None                                                                                           |                                                                      |                                                     |                                                  |

| Encoding:                          | 1000                                                                                           | bbba                                                                 | ffff                                                | ffff                                             |

| Description:                       | Bit 'b' in reg                                                                                 | gister 'f' i                                                         | s set.                                              | •                                                |

|                                    | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.                                              |                                                                      |                                                     |                                                  |

|                                    | If 'a' is '0' a<br>set is enabl<br>in Indexed                                                  | ed, this i                                                           | nstruction                                          | operates                                         |

|                                    | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs                                         | neverf≤<br>.2.3 "By<br>ed Instru                                     | 95 (5Fh).<br>te-Oriente<br>ctions in                | See<br>ed and<br>Indexed                         |

| Words:                             | mode wher<br>Section 29<br>Bit-Oriente                                                         | neverf≤<br>.2.3 "By<br>ed Instru                                     | 95 (5Fh).<br>te-Oriente<br>ctions in                | See<br>ed and<br>Indexed                         |

|                                    | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offe                                         | neverf≤<br>.2.3 "By<br>ed Instru                                     | 95 (5Fh).<br>te-Oriente<br>ctions in                | See<br>ed and<br>Indexed                         |

| Cycles:                            | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs<br>1                                    | neverf≤<br>.2.3 "By<br>ed Instru                                     | 95 (5Fh).<br>te-Oriente<br>ctions in                | See<br>ed and<br>Indexed                         |

|                                    | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs<br>1                                    | neverf≤<br>.2.3 "By<br>ed Instru                                     | 95 (5Fh).<br>te-Oriente<br>ctions in<br>e" for deta | See<br>ed and<br>Indexed                         |

| Cycles:<br>Q Cycle Activity:       | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offe<br>1                                    | never f ≤<br>.2.3 "By<br>ed Instru<br>set Mode                       | 95 (5Fh).<br>te-Orient<br>ctions in<br>or deta      | See<br>ed and<br>Indexed<br>ails.                |

| Cycles:<br>Q Cycle Activity:<br>Q1 | mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f' | ever f ≤<br>.2.3 "By<br>ed Instru<br>set Mode<br>Q3<br>Proce<br>Data | 95 (5Fh).<br>te-Orient<br>ctions in<br>or deta      | See<br>ed and<br>Indexed<br>ails.<br>Q4<br>Write |

| SUBLW                 | Subtract W from Literal |                         |    |                         |        |    |               |  |

|-----------------------|-------------------------|-------------------------|----|-------------------------|--------|----|---------------|--|

| Syntax:               | S                       | SUBLW k                 |    |                         |        |    |               |  |

| Operands:             | 0                       | $0 \leq k \leq 255$     |    |                         |        |    |               |  |

| Operation:            | k                       | $k - (W) \rightarrow W$ |    |                         |        |    |               |  |

| Status Affected:      | Ν                       | I, OV, (                | С, | DC, Z                   |        |    |               |  |

| Encoding:             | Γ                       | 0000                    |    | 1000                    | kkł    | ck | kkkk          |  |

| Description:          |                         |                         |    | acted from              |        |    |               |  |

| Words:                | 1                       |                         |    |                         |        |    |               |  |

| Cycles:               | 1                       |                         |    |                         |        |    |               |  |

| Q Cycle Activity:     |                         |                         |    |                         |        |    |               |  |

| Q1                    |                         | Q2                      |    | Q3                      |        |    | Q4            |  |

| Decode                | -                       | Read<br>eral 'k'        |    | Proce:<br>Data          |        | V  | Vrite to<br>W |  |

| Example 1:            | S                       | UBLW                    | (  | )2h                     |        |    |               |  |

| Before Instruc        | tion                    |                         |    |                         |        |    |               |  |

| W<br>C                | =                       | 01h<br>?                |    |                         |        |    |               |  |

| After Instruction     | n                       |                         |    |                         |        |    |               |  |

| W<br>C                | =                       | UIII                    |    |                         |        |    |               |  |

| Ž                     | =                       | 0                       | ,  | result is p             | 505111 |    |               |  |

| N<br>Furmula O        | =                       | 0                       |    |                         |        |    |               |  |

| Example 2:            |                         | UBLW                    | (  | )2h                     |        |    |               |  |

| Before Instruc<br>W   | tion<br>=               | 02h                     |    |                         |        |    |               |  |

| Ċ                     | =                       | ?                       |    |                         |        |    |               |  |

| After Instructio<br>W | on<br>_                 | 00h                     |    |                         |        |    |               |  |

| C                     | =                       | 1                       | ;  | result is z             | zero   |    |               |  |

| Z<br>N                | =                       | 1<br>0                  |    |                         |        |    |               |  |

| Example 3:            | S                       | UBLW                    | (  | )2h                     |        |    |               |  |

| Before Instruc        | tion                    |                         |    |                         |        |    |               |  |

| W<br>C                | =                       | 03h<br>?                |    |                         |        |    |               |  |

| After Instruction     | n                       | •                       |    |                         |        |    |               |  |

| W<br>C                | =                       | FFh<br>0                |    | (2's com<br>result is r |        |    |               |  |

| Z                     | =                       | 0                       | ,  | result is I             | icyal  | ve |               |  |

| Ν                     | N = 1                   |                         |    |                         |        |    |               |  |

|                       |                         |                         |    |                         |        |    |               |  |

| SUBWF                   | Sub                                                                                                    | otract W                                                                                                                                                  | from f                                                                                                                               |                                                              |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Syntax:                 | SUBWF f {,d {,a}}                                                                                      |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| Operands:               | $0 \le f \le 255$                                                                                      |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

|                         | d ∈ [0,1]                                                                                              |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

|                         |                                                                                                        | a ∈ [0,1]                                                                                                                                                 |                                                                                                                                      |                                                              |  |  |  |

| Operation:              | (f) –                                                                                                  | $-$ (W) $\rightarrow$                                                                                                                                     | dest                                                                                                                                 |                                                              |  |  |  |

| Status Affected:        | Ν, Ο                                                                                                   | DV, C, D                                                                                                                                                  | C, Z                                                                                                                                 |                                                              |  |  |  |

| Encoding:               | 0                                                                                                      | 101                                                                                                                                                       | 11da fff                                                                                                                             | f ffff                                                       |  |  |  |

| Description:            | com<br>resu                                                                                            | Subtract W from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |                                                                                                                                      |                                                              |  |  |  |

|                         | If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select th<br>GPR bank. |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

|                         | set<br>in Ir<br>moo<br>Sec<br>Bit-                                                                     | is enable<br>ndexed L<br>de when<br>ation 29.<br>Oriente                                                                                                  | nd the extended<br>ed, this instructi<br>Literal Offset Ad<br>ever f ≤ 95 (5Fh<br>2.3 "Byte-Orie<br>d Instructions<br>et Mode" for d | on operates<br>dressing<br>n). See<br>nted and<br>in Indexed |  |  |  |

| Words:                  | 1                                                                                                      |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| Cycles:                 | 1                                                                                                      |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| Q Cycle Activity:       |                                                                                                        |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| Q1                      |                                                                                                        | Q2                                                                                                                                                        | Q3                                                                                                                                   | Q4                                                           |  |  |  |

| Decode                  | F                                                                                                      | Read                                                                                                                                                      | Process                                                                                                                              | Write to                                                     |  |  |  |

|                         | reg                                                                                                    | ister 'f'                                                                                                                                                 | Data                                                                                                                                 | destination                                                  |  |  |  |

| Example 1:              | S                                                                                                      | UBWF                                                                                                                                                      | REG, 1, 0                                                                                                                            |                                                              |  |  |  |

| Before Instruc          | tion                                                                                                   |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| REG<br>W                | =                                                                                                      | 3<br>2<br>?                                                                                                                                               |                                                                                                                                      |                                                              |  |  |  |

| C                       | =                                                                                                      | ?                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| After Instruction       | on                                                                                                     |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| REG<br>W                | =                                                                                                      | 1<br>2                                                                                                                                                    |                                                                                                                                      |                                                              |  |  |  |

| C                       | =                                                                                                      |                                                                                                                                                           | result is positiv                                                                                                                    | е                                                            |  |  |  |

| ZN                      | =                                                                                                      | 0<br>0                                                                                                                                                    |                                                                                                                                      |                                                              |  |  |  |

| Example 2:              | _                                                                                                      | UBWF                                                                                                                                                      | REG, 0, 0                                                                                                                            |                                                              |  |  |  |

| Before Instruc          |                                                                                                        | ODWI                                                                                                                                                      | REG, 0, 0                                                                                                                            |                                                              |  |  |  |

| REG                     | =                                                                                                      | 2                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| W<br>C                  | =                                                                                                      | 2<br>2<br>?                                                                                                                                               |                                                                                                                                      |                                                              |  |  |  |

| After Instructio        | -<br>on                                                                                                | :                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| REG                     | =                                                                                                      | 2                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| W                       | =                                                                                                      | 0                                                                                                                                                         | rogult in Table                                                                                                                      |                                                              |  |  |  |

| C<br>Z                  | =                                                                                                      | 1 ;<br>1                                                                                                                                                  | result is zero                                                                                                                       |                                                              |  |  |  |

| N                       | =                                                                                                      | 0                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| Example 3:              | S                                                                                                      | UBWF                                                                                                                                                      | REG, 1, 0                                                                                                                            |                                                              |  |  |  |

| Before Instruc          |                                                                                                        |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| REG<br>W                | =                                                                                                      | 1<br>2                                                                                                                                                    |                                                                                                                                      |                                                              |  |  |  |

| v v                     | =                                                                                                      | ?                                                                                                                                                         |                                                                                                                                      |                                                              |  |  |  |

| С                       |                                                                                                        |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| After Instruction       | on                                                                                                     |                                                                                                                                                           |                                                                                                                                      |                                                              |  |  |  |

| After Instructio<br>REG | =                                                                                                      |                                                                                                                                                           | (2's complemer                                                                                                                       | nt)                                                          |  |  |  |

| After Instruction       |                                                                                                        | 2                                                                                                                                                         | (2's complemer result is negative                                                                                                    | ,                                                            |  |  |  |

### 30.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 30.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 30.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 30.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction