Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 64MHz                                                                          |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 69                                                                             |

| Program Memory Size        | 128KB (64K x 16)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 24x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87k22t-i-ptrsl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSB will always read '0' (see **Section 6.1.2 "Program Counter"**).

Figure 6-5 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1> which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 shows how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. For more details on the instruction set, see **Section 29.0 "Instruction Set Summary"**.

| 100KL 0-J. | INGT           | KUCHUR     |                    |      |                |         |                           |

|------------|----------------|------------|--------------------|------|----------------|---------|---------------------------|

|            |                |            |                    |      | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|            |                | Program N  | lemory             |      |                |         | 000000h                   |

|            |                | Byte Locat | ions $\rightarrow$ |      |                |         | 000002h                   |

|            |                |            |                    |      |                |         | 000004h                   |

|            |                |            |                    |      |                |         | 000006h                   |

|            | Instruction 1: | MOVLW      | 055h               |      | 0Fh            | 55h     | 000008h                   |

|            | Instruction 2: | GOTO       | 0006h              |      | EFh            | 03h     | 00000Ah                   |

|            |                |            |                    |      | F0h            | 00h     | 00000Ch                   |

|            | Instruction 3: | MOVFF      | 123h,              | 456h | C1h            | 23h     | 00000Eh                   |

|            |                |            |                    |      | F4h            | 56h     | 000010h                   |

|            |                |            |                    |      |                |         | 000012h                   |

|            |                |            |                    |      |                |         | 000014h                   |

### FIGURE 6-5: INSTRUCTIONS IN PROGRAM MEMORY

### 6.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four, two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits. The other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence, immediately after the first word, the data in the second word is accessed and

used by the instruction sequence. If the first word is skipped, for some reason, and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 shows how this works.

Note: For information on two-word instructions in the extended instruction set, see Section 6.5 "Program Memory and the Extended Instruction Set".

| EXAMPLE 6-4: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

|              |                       |

| CASE 1:             |                    |                            |  |  |  |  |  |  |  |

|---------------------|--------------------|----------------------------|--|--|--|--|--|--|--|

| Object Code         | Source Code        |                            |  |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1 ;      | is RAM location 0?         |  |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 ; | No, skip this word         |  |  |  |  |  |  |  |

| 1111 0100 0101 0110 | ;                  | Execute this word as a NOP |  |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3 ;       | continue code              |  |  |  |  |  |  |  |

| CASE 2:             |                    |                            |  |  |  |  |  |  |  |

| Object Code         | Source Code        |                            |  |  |  |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1 ;      | is RAM location 0?         |  |  |  |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 ; | Yes, execute this word     |  |  |  |  |  |  |  |

| 1111 0100 0101 0110 | ;                  | 2nd word of instruction    |  |  |  |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3 ;       | continue code              |  |  |  |  |  |  |  |

© 2009-2011 Microchip Technology Inc.

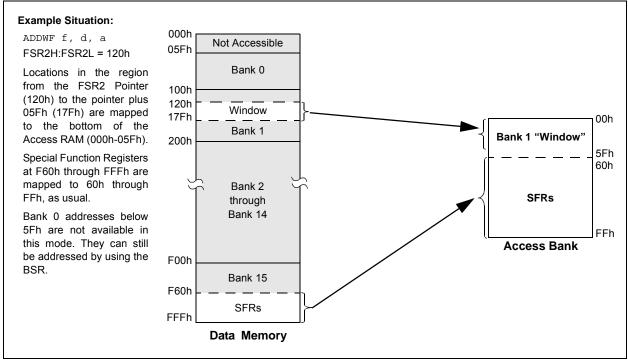

## 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space.

The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described. (See **Section 6.3.2 "Access Bank"**.) An example of Access Bank remapping in this addressing mode is shown in Figure 6-10. Remapping the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit = 1) will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

## 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

## FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

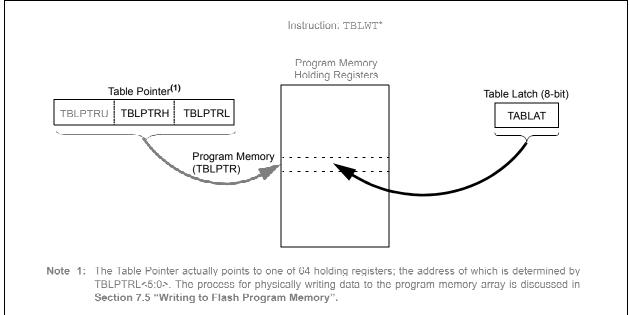

### FIGURE 7-2: TABLE WRITE OPERATION

## 7.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register, not a physical register, is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The EEPGD control bit determines if the access is a program or data EEPROM memory access. When clear, any subsequent operations operate on the data EEPROM memory. When set, any subsequent operations operate on the program memory.

The CFGS control bit determines if the access is to the Configuration/Calibration registers or to program memory/data EEPROM memory. When set, subsequent operations operate on Configuration registers regardless of EEPGD (see **Section 28.0 "Special Features of the CPU"**). When clear, memory selection access is determined by EEPGD. The FREE bit, when set, allows a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, allows a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |  |  |  |

|       | a Reset or a write operation was            |  |  |  |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

Note: The EEIF interrupt flag bit (PIR6<4>) is set when the write is complete. It must be cleared in software.

| Name    | Bit 7                  | Bit 6                  | Bit 5                  | Bit 4   | Bit 3                 | Bit 2   | Bit 1  | Bit 0   |

|---------|------------------------|------------------------|------------------------|---------|-----------------------|---------|--------|---------|

| INTCON  | GIE/GIEH               | PEIE/GIEL              | TMR0IE                 | INT0IE  | RBIE                  | TMR0IF  | INT0IF | RBIF    |

| INTCON2 | RBPU                   | INTEDG0                | INTEDG1                | INTEDG2 | INTEDG3               | TMR0IP  | INT3IP | RBIP    |

| INTCON3 | INT2IP                 | INT1IP                 | INT3IE                 | INT2IE  | INT1IE                | INT3IF  | INT2IF | INT1IF  |

| PIR1    | PSPIP                  | ADIF                   | RC1IF                  | TX1IF   | SSP1IF                | TMR1GIF | TMR2IF | TMR1IF  |

| PIR2    | OSCFIF                 | —                      | SSP2IF                 | BCL2IF  | BCL1IF                | HLVDIF  | TMR3IF | TMR3GIF |

| PIR3    | TMR5GIF                | —                      | RC2IF                  | TX2IF   | CTMUIF                | CCP2IF  | CCP1IF | RTCCIF  |

| PIR4    | CCP10IF <sup>(1)</sup> | CCP9IF <sup>(1)</sup>  | CCP8IF                 | CCP7IF  | CCP6IF                | CCP5IF  | CCP4IF | CCP3IF  |

| PIR5    | TMR7GIF <sup>(1)</sup> | TMR12IF <sup>(1)</sup> | TMR10IF <sup>(1)</sup> | TMR8IF  | TMR7IF <sup>(1)</sup> | TMR6IF  | TMR5IF | TMR4IF  |

| PIR6    | —                      | —                      | _                      | EEIF    | —                     | CMP3IF  | CMP2IF | CMP1IF  |

| PIE1    | PSPIE                  | ADIE                   | RC1IE                  | TX1IE   | SSP1IE                | TMR1GIE | TMR2IE | TMR1IE  |

| PIE2    | OSCFIE                 | —                      | SSP2IE                 | BCL2IE  | BCL1IE                | HLVDIE  | TMR3IE | TMR3GIE |

| PIE3    | TMR5GIE                | —                      | RC2IE                  | TX2IE   | CTMUIE                | CCP2IE  | CCP1IE | RTCCIE  |

| PIE4    | CCP10IE <sup>(1)</sup> | CCP9IE <sup>(1)</sup>  | CCP8IE                 | CCP7IE  | CCP6IE                | CCP5IE  | CCP4IE | CCP3IE  |

| PIE5    | TMR7GIE <sup>(1)</sup> | TMR12IE <sup>(1)</sup> | TMR10IE <sup>(1)</sup> | TMR8IE  | TMR7IE <sup>(1)</sup> | TMR6IE  | TMR5IE | TMR4IE  |

| PIE6    | —                      | —                      | _                      | EEIE    | _                     | CMP3IE  | CMP2IE | CMP1IE  |

| IPR1    | PSPIP                  | ADIP                   | RC1IP                  | TX1IP   | SSP1IP                | TMR1GIP | TMR2IP | TMR1IP  |

| IPR2    | OSCFIP                 | —                      | SSP2IP                 | BCL2IP  | BCL1IP                | HLVDIP  | TMR3IP | TMR3GIP |

| IPR3    | TMR5GIP                | —                      | RC2IP                  | TX2IP   | CTMUIP                | CCP2IP  | CCP1IP | RTCCIP  |

| IPR4    | CCP10IP <sup>(1)</sup> | CCP9IP <sup>(1)</sup>  | CCP8IP                 | CCP7IP  | CCP6IP                | CCP5IP  | CCP4IP | CCP3IP  |

| IPR5    | TMR7GIP <sup>(1)</sup> | TMR12IP <sup>(1)</sup> | TMR10IP <sup>(1)</sup> | TMR8IP  | TMR7IP <sup>(1)</sup> | TMR6IP  | TMR5IP | TMR4IP  |

| IPR6    |                        |                        |                        | EEIP    |                       | CMP3IP  | CMP2IP | CMP1IP  |

| RCON    | IPEN                   | SBOREN                 | CM                     | RI      | TO                    | PD      | POR    | BOR     |

### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: Shaded cells are not used by the interrupts.

Note 1: Unimplemented on devices with a program memory of 32 Kbytes (PIC18FX5K22).

| R/W-0                  | R/W-0                                                                                                   | R/W-0            | R/W-0         | R/W-0                  | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------|------------------|---------------|------------------------|-----------------|-----------------|--------|--|--|--|--|

| CCP100D <sup>(1)</sup> | CCP9OD <sup>(1)</sup>                                                                                   | CCP8OD           | CCP7OD        | CCP6OD                 | CCP5OD          | CCP4OD          | CCP3OD |  |  |  |  |

| bit 7                  |                                                                                                         |                  |               |                        |                 |                 | bit    |  |  |  |  |

|                        |                                                                                                         |                  |               |                        |                 |                 |        |  |  |  |  |

| Legend:                |                                                                                                         |                  |               |                        |                 |                 |        |  |  |  |  |

| R = Readable           | bit                                                                                                     | W = Writable     | bit           | •                      | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value at P        | OR                                                                                                      | '1' = Bit is set |               | '0' = Bit is cle       | ared            | x = Bit is unkr | nown   |  |  |  |  |

| L:1 7                  | 0004000-00                                                                                              |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 7                  | <b>CCP100D:</b> CC                                                                                      | •                | •             | able bit."             |                 |                 |        |  |  |  |  |

|                        | 1 = Open-drai<br>0 = Open-drai                                                                          |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 6                  | CCP9OD: CC                                                                                              | 1 5              |               | ble bit <sup>(1)</sup> |                 |                 |        |  |  |  |  |

|                        | 1 = Open-drain capability is enabled                                                                    |                  |               |                        |                 |                 |        |  |  |  |  |

|                        | 0 = Open-drai                                                                                           | in capability is | disabled      |                        |                 |                 |        |  |  |  |  |

| bit 5                  | CCP8OD: CCP8 Open-Drain Output Enable bit                                                               |                  |               |                        |                 |                 |        |  |  |  |  |

|                        | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 4                  | •                                                                                                       |                  |               | a bit                  |                 |                 |        |  |  |  |  |

| DIL 4                  | <b>CCP70D:</b> CCP7 Open-Drain Output Enable bit                                                        |                  |               |                        |                 |                 |        |  |  |  |  |

|                        | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 3                  | CCP6OD: CC                                                                                              | P6 Open-Drai     | n Output Enat | ole bit                |                 |                 |        |  |  |  |  |

|                        | 1 = Open-drai                                                                                           | n capability is  | enabled       |                        |                 |                 |        |  |  |  |  |

|                        | 0 = Open-drai                                                                                           | in capability is | disabled      |                        |                 |                 |        |  |  |  |  |

| bit 2                  | CCP5OD: CC                                                                                              | •                | •             | ole bit                |                 |                 |        |  |  |  |  |

|                        | 1 = Open-drain capability is enabled                                                                    |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 1                  | 0 = Open-drain capability is disabled                                                                   |                  |               |                        |                 |                 |        |  |  |  |  |

| DILI                   | <b>CCP4OD:</b> CCP4 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled                |                  |               |                        |                 |                 |        |  |  |  |  |

|                        | 0 = Open-drai                                                                                           |                  |               |                        |                 |                 |        |  |  |  |  |

| bit 0                  | CCP3OD: ECO                                                                                             |                  |               | able bit               |                 |                 |        |  |  |  |  |

| ·                      | 1 = Open-drai                                                                                           | •                |               |                        |                 |                 |        |  |  |  |  |

|                        | 0 = Open-drai                                                                                           |                  |               |                        |                 |                 |        |  |  |  |  |

### REGISTER 12-3: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2

Note 1: Not implemented on devices with 32-byte program memory (PIC18FX5K22).

### 16.6 Timer3/5/7 Interrupt

The TMRx register pair (TMRxH:TMRxL) increments from 0000h to FFFFh and overflows to 0000h. The Timerx interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMRxIF. Table 16-3 gives each module's flag bit.

#### TABLE 16-3: TIMER3/5/7 INTERRUPT FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIR2<1>  |

| 5            | PIR5<1>  |

| 7            | PIR5<3>  |

This interrupt can be enabled or disabled by setting or clearing the TMRxIE bit, respectively. Table 16-4 gives each module's enable bit.

## TABLE 16-4:TIMER3/5/7 INTERRUPTENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIE2<1>  |

| 5            | PIE5<1>  |

| 7            | PIE5<3>  |

### 16.7 Resetting Timer3/5/7 Using the ECCP Special Event Trigger

If the ECCP modules are configured to use Timerx and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timerx. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled. (For more information, see **Section 20.3.4 "Special Event Trigger"**.)

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timerx.

If Timerx is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timerx coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

| Note: | The Special Event Triggers from the        |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | ECCPx module will only clear the TMR3      |  |  |  |  |  |  |  |  |  |

|       | register's content, but not set the TMR3IF |  |  |  |  |  |  |  |  |  |

|       | interrupt flag bit (PIR1<0>).              |  |  |  |  |  |  |  |  |  |

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 19-2, Register 19-3 and Register 20-2

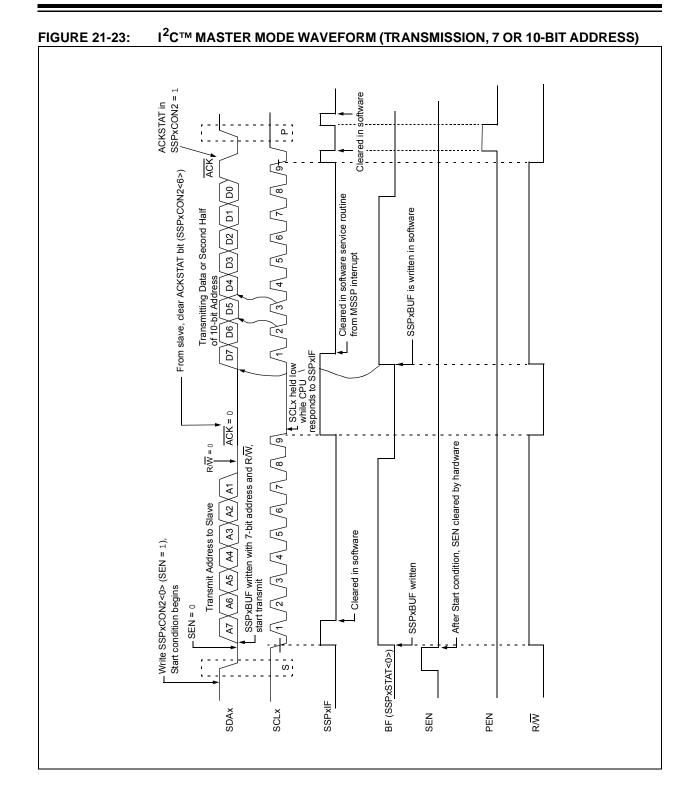

### 21.4.10 I<sup>2</sup>C<sup>™</sup> MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted (see data hold time specification Parameter 106). SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high (see data setup time specification Parameter 107). When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 21-23).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPxCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPxIF flag is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

### 21.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPxSTAT<0>) is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

### 21.4.10.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TCY after the SSPxBUF write. If SSPxBUF is rewritten within 2 TCY, the WCOL bit is set and SSPxBUF is updated. This may result in a corrupted transfer.

The user should verify that the WCOL bit is clear after each write to SSPxBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

### 21.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPxCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

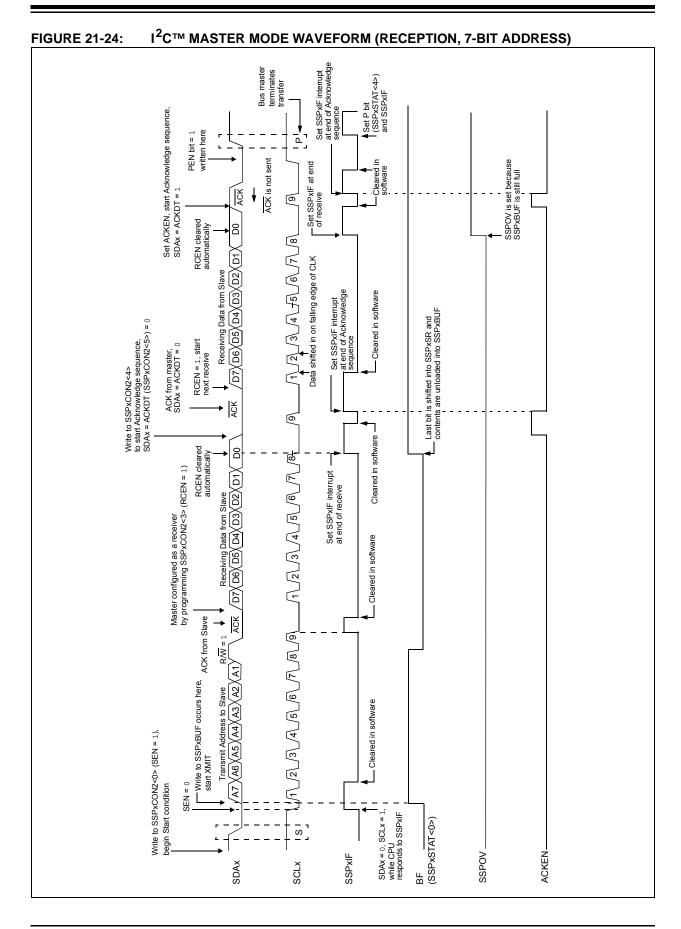

### 21.4.11 I<sup>2</sup>C<sup>™</sup> MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPxCON2<3>).

Note: The MSSP module must be in an inactive state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting, and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPxCON2<4>).

### 21.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 21.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 21.4.11.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

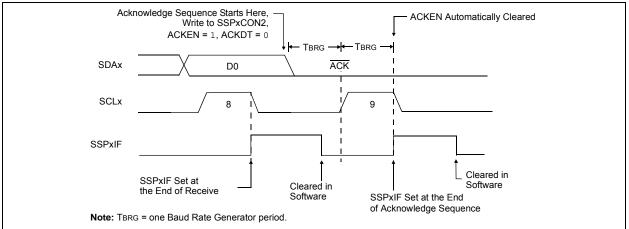

#### 21.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Seauence Enable bit. ACKEN (SSPxCON2<4>). When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG; the SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into an inactive state (Figure 21-25).

#### 21.4.12.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

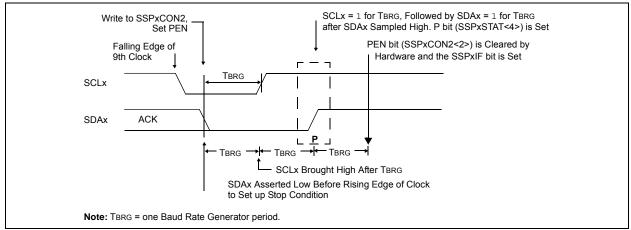

### 21.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPxCON2<2>). At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit (SSPxSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (see Figure 21-26).

### 21.4.13.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### FIGURE 21-25: ACKNOWLEDGE SEQUENCE WAVEFORM

### FIGURE 21-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

### 22.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 22-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RXx signal, the RXx signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN/J2602 bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRGx begins counting up, using the preselected clock source on the first rising edge of RXx. After eight bits on the RXx pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGHx:SPBRGx register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCONx<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 22-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. The BRG clock will be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG1 and SPBRGH1 as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGHx register. Refer to Table 22-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCxIF interrupt is set once the fifth rising edge on RXx is detected. The value in the RCREGx needs to be read to clear the RCxIF interrupt. The contents of RCREGx should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

- To maximize baud rate range, if that feature is used, it is recommended that the BRG16 bit (BAUDCONx<3>) be set.

## TABLE 22-4:BRG COUNTER<br/>CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

### 22.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREGx cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

| TADLE 22-J. |                                                                                             |              |              |               |         |         |        |        |  |

|-------------|---------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------|---------|--------|--------|--|

| Name        | Bit 7                                                                                       | Bit 6        | Bit 5        | Bit 4         | Bit 3   | Bit 2   | Bit 1  | Bit 0  |  |

| INTCON      | GIE/GIEH                                                                                    | PEIE/GIEL    | TMR0IE       | INT0IE        | RBIE    | TMR0IF  | INT0IF | RBIF   |  |

| PIR1        | PSPIF                                                                                       | ADIF         | RC1IF        | TX1IF         | SSP1IF  | TMR1GIF | TMR2IF | TMR1IF |  |

| PIE1        | PSPIE                                                                                       | ADIE         | RC1IE        | TX1IE         | SSP1IE  | TMR1GIE | TMR2IE | TMR1IE |  |

| IPR1        | PSPIP                                                                                       | ADIP         | RC1IP        | TX1IP         | SSP1IP  | TMR1GIP | TMR2IP | TMR1IP |  |

| PIR3        | TMR5GIF                                                                                     | —            | RC2IF        | TX2IF         | CTMUIF  | CCP2IF  | CCP1IF | RTCCIF |  |

| PIE3        | TMR5GIE                                                                                     | _            | RC2IE        | TX2IE         | CTMUIE  | CCP2IE  | CCP1IE | RTCCIE |  |

| IPR3        | TMR5GIP                                                                                     | _            | RC2IP        | TX2IP         | CTMUIP  | CCP2IP  | CCP1IP | RTCCIP |  |

| RCSTA1      | SPEN                                                                                        | RX9          | SREN         | CREN          | ADDEN   | FERR    | OERR   | RX9D   |  |

| TXREG1      | EUSART1 T                                                                                   | ransmit Regi | ster         |               |         |         |        |        |  |

| TXSTA1      | CSRC                                                                                        | TX9          | TXEN         | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |  |

| BAUDCON1    | ABDOVF                                                                                      | RCIDL        | RXDTP        | TXCKP         | BRG16   |         | WUE    | ABDEN  |  |

| SPBRGH1     | EUSART1 E                                                                                   | aud Rate Ge  | enerator Reg | ister High By | te      |         |        |        |  |

| SPBRG1      | EUSART1 E                                                                                   | Baud Rate Ge | enerator Reg | ister         |         |         |        |        |  |

| RCSTA2      | SPEN                                                                                        | RX9          | SREN         | CREN          | ADDEN   | FERR    | OERR   | RX9D   |  |

| TXREG2      | EUSART2 T                                                                                   | ransmit Regi | ster         |               |         |         |        |        |  |

| TXSTA2      | CSRC                                                                                        | TX9          | TXEN         | SYNC          | SENDB   | BRGH    | TRMT   | TX9D   |  |

| BAUDCON2    | ABDOVF                                                                                      | RCIDL        | RXDTP        | TXCKP         | BRG16   | _       | WUE    | ABDEN  |  |

| SPBRGH2     | EUSART2 E                                                                                   | Baud Rate Ge | enerator Reg | ister High By | te      |         |        |        |  |

| SPBRG2      | EUSART2 E                                                                                   | Baud Rate Ge | enerator Reg | ister         |         |         |        |        |  |

| ODCON3      | U2OD                                                                                        | U10D         |              |               |         |         |        | CTMUDS |  |

| PMD0        | CCP3MD                                                                                      | CCP2MD       | CCP1MD       | UART2MD       | UART1MD | SSP2MD  | SSP1MD | ADCMD  |  |

| legend: _ = | equiplemented locations read as '0' Shaded cells are not used for asynchronous transmission |              |              |               |         |         |        |        |  |

## TABLE 22-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

### 27.1 CTMU Registers

The control registers for the CTMU are:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 27-1 and Register 27-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 27-3) has bits for selecting the current source range and current source trim.

#### REGISTER 27-1: CTMUCONH: CTMU CONTROL HIGH REGISTER

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0  |

|--------|-----|----------|-------|-------|----------|---------|--------|

| CTMUEN | —   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | CTTRIG |

| bit 7  |     |          |       |       |          |         | bit 0  |

|        |     |          |       |       |          |         |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Module is enabled</li><li>0 = Module is disabled</li></ul>                                                             |

| bit 6 | Unimplemented: Read as '0'                                                                                                         |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                    |

|       | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                   |

|       | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                     |

| bit 3 | EDGEN: Edge Enable bit                                                                                                             |

|       | <ul><li>1 = Edges are not blocked</li><li>0 = Edges are blocked</li></ul>                                                          |

| bit 2 | EDGSEQEN: Edge Sequence Enable bit                                                                                                 |

|       | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>              |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                         |

|       | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>         |

| bit 0 | <b>CTTRIG:</b> Trigger Control bit<br>1 = Trigger output is enabled<br>0 = Trigger output is disabled                              |

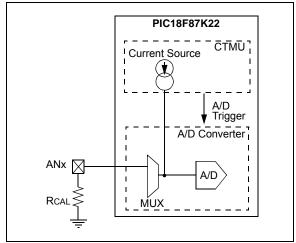

The CTMU current source may be trimmed with the trim bits in CTMUICON using an iterative process to get the exact current desired. Alternatively, the nominal value without adjustment may be used. That value may be stored by software for use in all subsequent capacitive or time measurements.

To calculate the value for  $\ensuremath{\mathrm{RCAL}}$  , the nominal current must be chosen. Then, the resistance can be calculated.

For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale (or 2.31V) as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as RCAL = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, RCAL would be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

#### FIGURE 27-2: CTMU CURRENT SOURCE CALIBRATION CIRCUIT

A value of 70% of full-scale voltage is chosen to make sure that the A/D Converter was in a range that is well above the noise floor. If an exact current is chosen to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL may also be adjusted to allow for available resistor values. RCAL should be of the highest precision available, in light of the precision needed for the circuit that the CTMU will be measuring. A recommended minimum would be 0.1% tolerance.

The following examples show a typical method for performing a CTMU current calibration.

• Example 27-1 demonstrates how to initialize the A/D Converter and the CTMU.

This routine is typical for applications using both modules.

• Example 27-2 demonstrates one method for the actual calibration routine.

This method manually triggers the A/D Converter to demonstrate the entire step-wise process. It is also possible to automatically trigger the conversion by setting the CTMU's CTTRIG bit (CTMUCONH<0>).

## 27.7 Creating a Delay with the CTMU Module

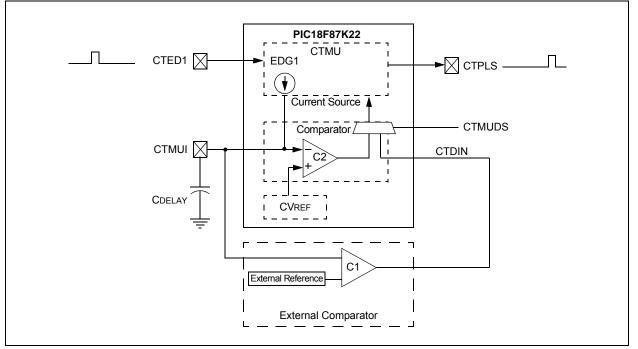

A unique feature on board the CTMU module is its ability to generate system clock independent output pulses, based on either an external voltage or an external capacitor value. When using an external voltage, this is accomplished using the CTDIN input pin as a trigger for the pulse delay. When using an external capacitor value, this is accomplished using the internal comparator voltage reference module and Comparator 2 input pin.The pulse is output onto the CTPLS pin. To enable this mode, set the TGEN bit.

See Figure 27-4 for an example circuit. When CTMUDS (ODCON3<0>) is cleared, the pulse delay is determined by the output of Comparator 2, and when it is set, the pulse delay is determined by the input of CTDIN. CDELAY is chosen by the user to determine the output pulse width on CTPLS. The pulse width is calculated by T = (CDELAY/I) \* V, where I is known from the current source measurement step (Section 27.4.1 "Current Source Calibration") and V is the Internal Reference Voltage (CVREF).

An example use of the external capacitor feature is interfacing with variable capacitive-based sensors, such as a humidity sensor. As the humidity varies, the pulse-width output on CTPLS will vary. An example use of the CTDIN feature is interfacing with a digital sensor. The CTPLS output pin can be connected to an input capture pin and the varying pulse width measured to determine the sensor's output in the application.

To use this feature:

- 1. If CTMUDS is cleared, initialize Comparator 2.

- 2. If CTMUDS is cleared, initialize the comparator voltage reference.

- 3. Initialize the CTMU and enable time delay generation by setting the TGEN bit.

- 4. Set EDG1STAT.

When CTMUDS is cleared, as soon as CDELAY charges to the value of the voltage reference trip point, an output pulse is generated on CTPLS. When CTMUDS is set, as soon as CTDIN is set, an output pulse is generated on CTPLS.

## FIGURE 27-4: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

## 28.0 SPECIAL FEATURES OF THE CPU

The PIC18F87K22 family of devices includes several features intended to maximize reliability and minimize cost through elimination of external components. These include:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT) and On-chip Regulator

- · Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, the PIC18F87K22 family of devices has a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator (LF-INTOSC) also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

## 28.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location, 300000h.

The user will note that address, 300000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Software programming of the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In normal Operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 7.5 "Writing to Flash Program Memory".

#### 29.1.1 STANDARD INSTRUCTION SET

| Syntax<br>Operar |                        | ADDLW                              |                |                  |                   |                                                                       |                                                                                     |                         |  |  |

|------------------|------------------------|------------------------------------|----------------|------------------|-------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------|--|--|

| Operar           |                        | //DDLVV                            | k              |                  | Syntax:           | ADDWF                                                                 | f {,d {,a}}                                                                         |                         |  |  |

| 0 0 0.0.         | nds:                   | $0 \le k \le 255$                  |                |                  | Operands:         | $0 \le f \le 255$                                                     |                                                                                     |                         |  |  |

| Operat           | tion:                  | $(W) + k \to V$                    | N              |                  |                   | d ∈ [0,1]<br>a ∈ [0,1]                                                |                                                                                     |                         |  |  |

| Status           | Affected:              | N, OV, C, DC, Z                    |                | Operation:       | • •               | doct                                                                  |                                                                                     |                         |  |  |

| Encodi           | ing:                   | 0000 1111 kkkk kkkk                |                | Status Affected: | ( ) ()            | (W) + (f) $\rightarrow$ dest<br>N, OV, C, DC, Z                       |                                                                                     |                         |  |  |

| Description:     |                        | The contents of W are added to the |                |                  |                   | Encoding: 0010 01da                                                   |                                                                                     | f ffff                  |  |  |

|                  |                        |                                    | k' and the res | ult is placed in | Description:      |                                                                       |                                                                                     |                         |  |  |

| Words            |                        | W.<br>1                            |                |                  | Description.      |                                                                       | Add W to register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the |                         |  |  |

|                  |                        | 1                                  |                |                  |                   | result is sto                                                         | ored back in re                                                                     | gister 'f'.             |  |  |

| Cycles           |                        | I                                  |                |                  |                   |                                                                       | he Access Bar                                                                       |                         |  |  |

| Q Cyc            | cle Activity:<br>Q1    | Q2                                 | Q3             | Q4               |                   | If 'a' is '1', t<br>GPR bank.                                         | he BSR is use                                                                       | d to select the         |  |  |

|                  | Decode                 | Read                               | Process        | Write to         |                   |                                                                       | ind the extende                                                                     | ad instruction          |  |  |

|                  |                        | literal 'k'                        | Data           | W                |                   |                                                                       | led, this instruc                                                                   |                         |  |  |

|                  |                        |                                    |                |                  |                   |                                                                       | Literal Offset A                                                                    | •                       |  |  |

| <u>Examp</u>     | <u>ole:</u>            | ADDLW 1                            | .5h            |                  |                   | mode whenever $f \le 95$ (5Fh). See Section 29.2.3 "Byte-Oriented and |                                                                                     |                         |  |  |

| B                | efore Instruc          |                                    |                |                  |                   | Bit-Oriented Instructions in Indexe                                   |                                                                                     |                         |  |  |

| A                | W =<br>fter Instructio | 10h<br>m                           |                |                  |                   | Literal Off                                                           | set Mode" for                                                                       | details.                |  |  |

|                  | W =                    | 25h                                |                |                  | Words:            | 1                                                                     |                                                                                     |                         |  |  |

|                  |                        |                                    |                |                  | Cycles:           | 1                                                                     |                                                                                     |                         |  |  |

|                  |                        |                                    |                |                  | Q Cycle Activity: |                                                                       |                                                                                     |                         |  |  |

|                  |                        |                                    |                |                  | Q1                | Q2                                                                    | Q3                                                                                  | Q4                      |  |  |

|                  |                        |                                    |                |                  | Decode            | Read<br>register 'f'                                                  | Process<br>Data                                                                     | Write to<br>destination |  |  |

|                  |                        |                                    |                |                  |                   | regiotor r                                                            | Dulu                                                                                | dootindtion             |  |  |

|                  |                        |                                    |                |                  | Example:          | ADDWF                                                                 | REG, 0, 0                                                                           |                         |  |  |

|                  |                        |                                    | Before Instru  |                  |                   |                                                                       |                                                                                     |                         |  |  |

|                  |                        |                                    | W<br>REG       | = 17h<br>= 0C2h  |                   |                                                                       |                                                                                     |                         |  |  |

|                  |                        |                                    |                | After Instruct   |                   |                                                                       |                                                                                     |                         |  |  |

|                  |                        |                                    |                |                  | W<br>REG          | = 0D9h<br>= 0C2h                                                      |                                                                                     |                         |  |  |

|                  |                        |                                    |                |                  | ALC .             | 00211                                                                 |                                                                                     |                         |  |  |

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| BTFS                                                                                                                                                                                                                                                                             | SC                                                                            | Bit Test File                                                                  | , Skip if Clear                                                                                                             |                                        | BTFS                                                                          | SS                                                                                                     | Bit Test File                                                                 | , Skip if Set                                                                                                                   |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Synta                                                                                                                                                                                                                                                                            | ax:                                                                           | BTFSC f, b                                                                     | {,a}                                                                                                                        |                                        | Synta                                                                         | ax:                                                                                                    | BTFSS f, b {                                                                  | ,a}                                                                                                                             |                                                              |

| Opera                                                                                                                                                                                                                                                                            | ands:                                                                         | $0 \le f \le 255$ $0 \le b \le 7$                                              |                                                                                                                             |                                        | Oper                                                                          | ands:                                                                                                  | $0 \le f \le 255$<br>$0 \le b < 7$                                            |                                                                                                                                 |                                                              |

| -                                                                                                                                                                                                                                                                                |                                                                               | a ∈ [0,1]                                                                      |                                                                                                                             |                                        | -                                                                             |                                                                                                        | a ∈ [0,1]                                                                     |                                                                                                                                 |                                                              |

| Opera                                                                                                                                                                                                                                                                            |                                                                               | skip if (f <b>)</b>                                                            | = 0                                                                                                                         |                                        |                                                                               | ation:                                                                                                 | skip if (f <b>)</b>                                                           | = 1                                                                                                                             |                                                              |

| Statu                                                                                                                                                                                                                                                                            | s Affected:                                                                   | None                                                                           |                                                                                                                             |                                        |                                                                               | s Affected:                                                                                            | None                                                                          |                                                                                                                                 |                                                              |

| Enco                                                                                                                                                                                                                                                                             | ding:                                                                         | 1011                                                                           | bbba ff                                                                                                                     |                                        | Enco                                                                          | ding:                                                                                                  | 1010                                                                          | bbba ff                                                                                                                         | ff ffff                                                      |

| Description: If bit 'b' in register 'f' is '0', then the nexi<br>instruction is skipped. If bit 'b' is '0', the<br>the next instruction fetched during the<br>current instruction execution is discard<br>and a NOP is executed instead, making<br>this a two-cycle instruction. |                                                                               | 'b' is '0', then<br>during the<br>in is discarded<br>ead, making               | Desc                                                                                                                        | ription:                               | instruction is<br>the next instruction<br>current instruction<br>and a NOP is | gister 'f' is '1', t<br>skipped. If bit<br>ruction fetched<br>action executio<br>executed instruction. | 'b' is '1', then<br>during the<br>n is discarded<br>ead, making               |                                                                                                                                 |                                                              |

|                                                                                                                                                                                                                                                                                  |                                                                               |                                                                                | e Access Banł<br>BSR is used to                                                                                             | is selected. If select the             |                                                                               |                                                                                                        |                                                                               | e Access Bank<br>BSR is used to                                                                                                 |                                                              |

|                                                                                                                                                                                                                                                                                  |                                                                               | is enabled, ti<br>Indexed Lite<br>whenever f ≤<br>Section 29.2<br>Bit-Oriented | d the extended<br>his instruction<br>ral Offset Addr<br>95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | essing mode<br>ented and<br>in Indexed |                                                                               |                                                                                                        | set is enable<br>Indexed Lite<br>whenever f ≤<br>Section 29.2<br>Bit-Oriented | d the extended<br>d, this instructi<br>ral Offset Addr<br>g 95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | on operates in<br>essing mode<br>e<br>nted and<br>in Indexed |

| Word                                                                                                                                                                                                                                                                             | s:                                                                            | 1                                                                              |                                                                                                                             |                                        | Word                                                                          | s:                                                                                                     | 1                                                                             |                                                                                                                                 |                                                              |

| Cycle                                                                                                                                                                                                                                                                            | es:                                                                           |                                                                                | cles if skip and<br>2-word instruc                                                                                          |                                        | Cycle                                                                         | es:                                                                                                    |                                                                               | ycles if skip an<br>a 2-word instru                                                                                             |                                                              |

| QC                                                                                                                                                                                                                                                                               | cle Activity:                                                                 |                                                                                |                                                                                                                             |                                        | QC                                                                            | ycle Activity:                                                                                         |                                                                               |                                                                                                                                 |                                                              |