Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 16MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                          |

| Peripherals                | LCD, POR, PWM, WDT                                          |

| Number of I/O              | 99                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 4K x 8                                                      |

| RAM Size                   | 6K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                               |

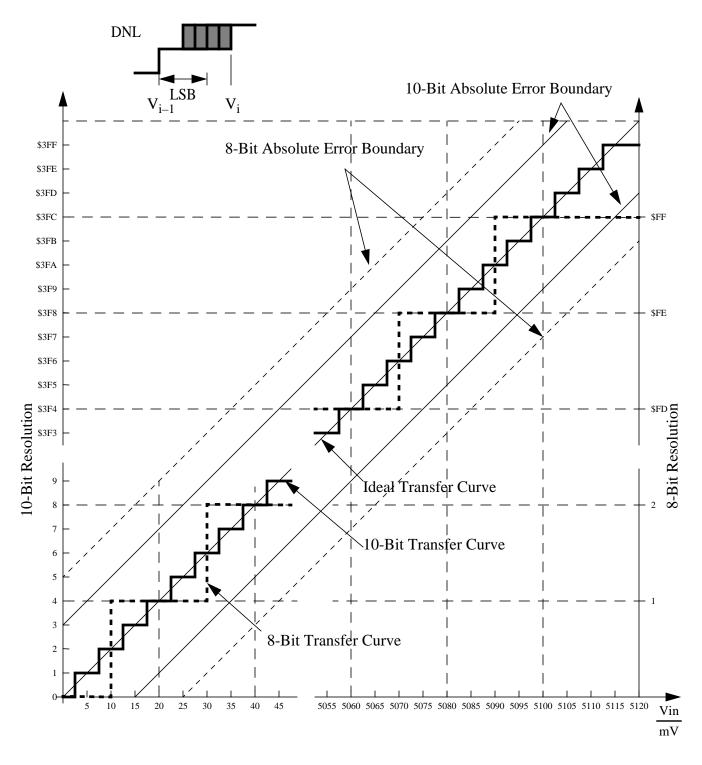

| Data Converters            | A/D 8x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 144-LQFP                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12h128vfve |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Inter-Integrated Circuit interface (IIC)

- Liquid Crystal Display driver with variable input voltage

- Configurable for up to 32 frontplanes and 4 backplanes or general purpose input or output

- 5 modes of operation allow for different display sizes to meet application requirements

- Unused frontplane and backplane pins can be used as general purpose I/O

- 16, 24 high current drivers suited for PWM motor control

- Each PWM channel switchable between two drivers in an H-bridge configuration

- Left, right and center aligned outputs

- Support for sine and cosine drive

- Dithering

- Output slew rate control

- 144-Pin or 112-Pin LQFP package

- I/O lines with 5V input and drive capability

- 5V A/D converter inputs

- Operation at 32MHz equivalent to 16MHz Bus Speed

- Development support

- − Single-wire background debug<sup>TM</sup> mode (BDM)

- On-chip hardware breakpoints

# **1.3 Modes of Operation**

User modes

- Normal and Emulation Operating Modes

- Normal Single-Chip Mode

- Normal Expanded Wide Mode

- Normal Expanded Narrow Mode

- Emulation Expanded Wide Mode

- Emulation Expanded Narrow Mode

- Special Operating Modes

- Special Single-Chip Mode with active Background Debug Mode

- Special Test Mode (Freescale Use Only)

- Special Peripheral Mode (Freescale Use Only)

Low power modes

#### \$0080 - \$00AF

#### ATD (Analog to Digital Converter 10 Bit 16 Channel)

| Address | Name     | [               | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0 |

|---------|----------|-----------------|---------|-------|-------|-------|-------|----------|-------|-------|

| \$009F  | ATDDR7L  | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

| ψ0031   | AIDDIGE  | Write:          |         |       |       |       |       |          |       |       |

| \$00A0  | ATDDR8H  | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

| φυυλίο  | A BBRON  | Write:          |         |       |       |       |       |          |       |       |

| \$00A1  | ATDDR8L  | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

| φουλι   | TIDDIGE  | Write:          |         |       |       |       |       |          |       |       |

| \$00A2  | ATDDR9H  | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

| φ00/ iL |          | Write:          |         |       |       |       |       |          |       |       |

| \$00A3  | ATDDR9L  | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

|         |          | Write:          |         |       |       |       |       |          |       |       |

| \$00A4  | ATDDR10H | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

|         | -        | Write:          |         |       |       | -     | -     | _        |       |       |

| \$00A5  | ATDDR10L | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

|         |          | Write:          | D:: 4 5 |       | 10    | 10    |       | 4.0      |       | Dite  |

| \$00A6  | ATDDR11H | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

|         |          | Write:          | D::/7   | 0     |       | 4     | 0     | 0        |       | D:10  |

| \$00A7  | ATDDR11L | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

|         |          | Write:          | Ditte   | 4.4   | 40    | 40    | 44    | 10       | 0     | D:40  |

| \$00A8  | ATDDR12H | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

|         |          | Write:          | D:47    | 0     |       | 4     | 2     | 0        | 4     | Dito  |

| \$00A9  | ATDDR12L | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

|         |          | Write:          | Dit1E   | 14    | 10    | 10    | 11    | 10       | 0     | Dit0  |

| \$00AA  | ATDDR13H | Read:<br>Write: | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

|         |          | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

| \$00AB  | ATDDR13L | Write:          | BILI    | 0     | 5     | 4     | 3     | 2        | I     | Bito  |

|         |          | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

| \$00AC  | ATDDR14H | Write:          | Dit15   | 14    | 15    | 12    | 11    | 10       | 3     | Dito  |

|         |          | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

| \$00AD  | ATDDR14L | Write:          |         | 0     | 5     | +     | 5     | <u> </u> | 1     | Ditt  |

|         |          | Read:           | Bit15   | 14    | 13    | 12    | 11    | 10       | 9     | Bit8  |

| \$00aE  | ATDDR15H | Write:          | Dit15   | 17    | 10    | 12    | 11    | 10       | 3     | Dito  |

|         |          | Read:           | Bit7    | 6     | 5     | 4     | 3     | 2        | 1     | Bit0  |

| \$00AF  | ATDDR15L | Write:          |         | 0     | 5     | Ŧ     | 0     | <u> </u> | 1     | Dito  |

|         |          | write.[         |         |       |       |       |       |          |       |       |

#### \$00B0 - \$00BF

#### Reserved

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$00B0 - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$00BF   | Reserved | Write: |       |       |       |       |       |       |       |       |

#### \$00C0 - \$00C7

#### IIC (Inter IC Bus)

| Address | Name | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$00C0  | IBAD | Read:<br>Write: | ADR7  | ADR6  | ADR5  | ADR4  | ADR3  | ADR2  | ADR1  | 0     |

| \$00E1  | IBFD | Read:<br>Write: | IBC7  | IBC6  | IBC5  | IBC4  | IBC3  | IBC2  | IBC1  | IBC0  |

\$0110 - \$011B

#### **EEPROM Control Register (eets4k)**

| Address | Name    |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0119  | EADDRLO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$011A  | EDATAHI | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$011B  | EDATALO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

#### \$011C - \$011F

#### **Reserved for RAM Control Register**

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$011C - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$011F   | Reserved | Write: |       |       |       |       |       |       |       |       |

#### \$0120 - \$0137

# LCD (Liquid Crystal Display 32 frontplanes, 4 backplanes)

| Address | Name     |                 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0      |

|---------|----------|-----------------|---------|---------|---------|---------|---------|---------|---------|------------|

| \$0120  | LCDCR0   | Read:<br>Write: | LCDEN   | 0       | LCLK2   | LCLK1   | LCLK0   | BIAS    | DUTY1   | DUTY0      |

| \$0121  | LCDCR1   | Read:           | 0       | 0       | 0       | 0       | 0       | 0       | LCDSWAI | LCDRPSTP   |

| ψυτΖτ   | LODOINT  | Write:          |         |         |         |         |         |         | LODOWN  | LODINI OII |

| \$0122  | FPENR0   | Read:<br>Write: | FPEN7   | FPEN6   | FPEN5   | FPEN4   | FPEN3   | FPEN2   | FPEN1   | FPEN0      |

| \$0123  | FPENR1   | Read:<br>Write: | FPEN15  | FPEN14  | FPEN13  | FPEN12  | FPEN11  | FPEN10  | FPEN9   | FPEN8      |

| \$0124  | FPENR2   | Read:<br>Write: | FPEN23  | FPEN22  | FPEN21  | FPEN20  | FPEN19  | FPEN18  | FPEN17  | FPEN16     |

| \$0125  | FPENR3   | Read:<br>Write: | FPEN31  | FPEN30  | FPEN29  | FPEN28  | FPEN27  | FPEN26  | FPEN25  | FPEN24     |

| \$0126  | Reserved | Read:           | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

| φ0120   | Received | Write:          |         |         |         |         |         |         |         |            |

| \$0127  | Reserved | Read:           | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0          |

|         |          | Write:          |         |         |         |         |         |         |         |            |

| \$0128  | LCDRAM0  | Read:<br>Write: | FP1BP3  | FP1BP2  | FP1BP1  | FP1BP0  | FP0BP3  | FP0BP2  | FP0BP1  | FP0BP0     |

| \$0129  | LCDRAM1  | Read:<br>Write: | FP3BP3  | FP3BP2  | FP3BP1  | FP3BP0  | FP2BP3  | FP2BP2  | FP2BP1  | FP2BP0     |

| \$012A  | LCDRAM2  | Read:<br>Write: | FP5BP3  | FP5BP2  | FP5BP1  | FP5BP0  | FP4BP3  | FP4BP2  | FP4BP1  | FP4BP0     |

| \$012B  | LCDRAM3  | Read:<br>Write: | FP7BP3  | FP7BP2  | FP7BP1  | FP7BP0  | FP6BP3  | FP6BP2  | FP6BP1  | FP6BP0     |

| \$012C  | LCDRAM4  | Read:<br>Write: | FP9BP3  | FP9BP2  | FP9BP1  | FP9BP0  | FP8BP3  | FP8BP2  | FP8BP1  | FP8BP0     |

| \$012D  | LCDRAM5  | Read:<br>Write: | FP11BP3 | FP11BP2 | FP11BP1 | FP11BP0 | FP10BP3 | FP10BP2 | FP10BP1 | FP10BP0    |

| \$012E  | LCDRAM6  | Read:<br>Write: | FP13BP3 | FP13BP2 | FP13BP1 | FP13BP0 | FP12BP3 | FP12BP2 | FP12BP1 | FP12BP0    |

| \$012F  | LCDRAM7  | Read:<br>Write: | FP15BP3 | FP15BP2 | FP15BP1 | FP15BP0 | FP14BP3 | FP14BP2 | FP14BP1 | FP14BP0    |

\$01C0 - \$01FF

# MC (Motor Controller 10bit 12 channels)

| S01CC         Reserved         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Address      | Name       | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$01CD         Reserved         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$01CC       | Reserved   | H      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Sonce         Reserved         Write         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ¢01CD        | Beconved   |        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| SUILE         Reserved         Write<br>Read         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th0< th="">         0</th0<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>JOICD</b> | Reserved   |        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| S01CF         Reserved         Read:<br>Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$01CE       | Reserved   | H      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| S01D0         MCCC0         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D1         MCCC1         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D2         MCCC2         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D3         MCCC3         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D4         MCCC4         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         0         O         CD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \$01CF       | Reserved   | H      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| SUID1         MICCC1         Write:         OM1         OM0         AM1         AM0         CD1         CD1         CD0           \$01D2         MCCC2         Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D3         MCCC3         Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D4         MCCC3         Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D4         MCCC4         Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D5         MCCC6         Read:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D6         MCCC6         Read:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D7         MCCC7         Read:         OM1         OM0         AM1         AM0         0         O         CD1         CD0           \$01D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$01D0       | MCCC0      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D2         MCCC2         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D3         MCCC3         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D4         MCCC4         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D4         MCCC4         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D5         MCCC5         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D6         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \$01D1       | MCCC1      | I      | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D3         MCCC3         Read:<br>Write:         OM1         OM0         AM1         AM0         O         CD1         CD0           \$01D4         MCCC4         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D4         MCCC4         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D5         MCCC5         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC11         Read:<br>Write:         O         O         O         O         O         O         O         O <td< td=""><td>\$01D2</td><td>MCCC2</td><td>Read:</td><td>OM1</td><td>OM0</td><td>AM1</td><td>AM0</td><td>0</td><td>0</td><td>CD1</td><td>CD0</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$01D2       | MCCC2      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D4         MCCC4         Read<br>Write:<br>Read:<br>\$01D5         OM1         OM0         AM1         AM0         O         CD1         CD0           \$01D5         MCCC5         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01DA         MCC11         Read:<br>Write:         O         O         O         O         O         O         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \$01D3       | MCCC3      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D5         MCCC5         Read:<br>Write:<br>\$01D6         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D6         MCCC6         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$01D4       | MCCC4      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D6         MCCC6         Read:<br>Write:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         CD1         CD0           \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         CD1         CD0           \$01D9         MCCC9         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 </td <td>\$01D5</td> <td>MCCC5</td> <td>Read:</td> <td>OM1</td> <td>OM0</td> <td>AM1</td> <td>AM0</td> <td>0</td> <td>0</td> <td>CD1</td> <td>CD0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$01D5       | MCCC5      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D7         MCCC7         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC8         Write:<br>Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D9         MCCC9         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D9         MCCC0         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01D8         MCCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         O         O         CD1         CD0           \$01DC         Reserved         Read:<br>Write:         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$01D6       | MCCC6      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D8         MCCC8         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D9         MCCC9         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01D8         MCCC9         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01DB         MCCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$01D7       | MCCC7      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01D9         MCCC9         Read:<br>Write:         OM1         OM0         AM1         AM0         0         O         CD1         CD0           \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         CD1         CD0           \$01DB         MCCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$01D8       | MCCC8      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| \$01DA         MCCC10         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01DB         MCCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         CD1         CD0           \$01DB         MCCC11         Read:<br>Write:         OM1         OM0         AM1         AM0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$01D9       | MCCC9      | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$01DA       | MCCC10     | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$01DB       | MCCC11     | Read:  | OM1   | OM0   | AM1   | AM0   | 0     | 0     | CD1   | CD0   |

| Write:         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< td=""><td>\$01DC</td><td>Reserved</td><td>Read:</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$01DC       | Reserved   | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$01DD       Reserved       Write:       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |            |        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$01DE       Reserved       Write:       Image: Constraint of the constraint of t | \$01DD       | Reserved   | Write: |       |       |       |       |       |       |       |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$01DE       | Reserved   |        | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$01DF       | Reserved   | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$01E0MCDC0 (hi)Write:SDiamon DiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamonDiamon<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |            | E      | -     | S     | S     | S     | S     |       |       |       |

| \$01E1       MCDC0 (i6)       Write:       D7       D6       D5       D4       D3       D2       D1       D0         \$01E2       MCDC1 (hi)       Read:<br>Write:       S       S       S       S       D10       D9       D8         \$01E3       MCDC1 (lo)       Read:<br>Write:       D7       D6       D5       D4       D3       D2       D1       D0         \$01E3       MCDC1 (lo)       Read:<br>Write:       D7       D6       D5       D4       D3       D2       D1       D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | \$01E0       | MCDC0 (hi) | Write: | S     |       |       |       |       | D10   | D9    | D8    |

| \$01E2         MCDC1 (hi)         Write:         S         D10         D9         D8           \$01E3         MCDC1 (lo)         Read:         D7         D6         D5         D4         D3         D2         D1         D0           Pead:         Pade:         Pade: <td>\$01E1</td> <td>MCDC0 (lo)</td> <td></td> <td>D7</td> <td></td> <td></td> <td></td> <td></td> <td>D2</td> <td>D1</td> <td>D0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | \$01E1       | MCDC0 (lo) |        | D7    |       |       |       |       | D2    | D1    | D0    |

| \$01E3 MCDC1 (10) Write: D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | \$01E2       | MCDC1 (hi) |        | S     | S     | S     | S     | S     | D10   | D9    | D8    |

| Read: S S S S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$01E3       | MCDC1 (lo) |        | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| \$01E4 MCDC2 (hi) Write: S S S D10 D9 D8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$01E4       | MCDC2 (hi) | Read:  | S     | S     | S     | S     | S     | D10   | D9    | D8    |

# 2.3.22 FreescalePL[7:4] / FP[31:28] - Port L I/O Pins [7:4]

PL7-PL4 are general purpose input or output pins. They can be configured as frontplane segment driver outputs FP31-FP28 of the LCD module.

**NOTE:** These pins are not available in the 112-pin LQFP version.

## 2.3.23 PL[3:0] / FP[19:16] — Port L I/O Pins [3:0]

PL3-PL0 are general purpose input or output pins. They can be configured as frontplane segment driver outputs FP19-FP16 of the LCD module.

## 2.3.24 PM5 / TXCAN1 — Port M I/O Pin 5

PM5 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN1 of the Freescale Scalable Controller Area Network controller 1 (CAN1)

#### 2.3.25 PM4 / RXCAN1 — Port M I/O Pin 4

PM4 is a general purpose input or output pin. It can be configured as the receive pin RXCAN1 of the Freescale Scalable Controller Area Network controller 1 (CAN1)

## 2.3.26 PM3 / TXCAN0 — Port M I/O Pin 3

PM3 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN0 of the Freescale Scalable Controller Area Network controller 0 (CAN0)

#### 2.3.27 PM2 / RXCAN0 — Port M I/O Pin 2

PM2 is a general purpose input or output pin. It can be configured as the receive pin RXCAN0 of the Freescale Scalable Controller Area Network controller 0 (CAN0)

## 2.3.28 PM1 / SCL — Port M I/O Pin 1

PM1 is a general purpose input or output pin. It can be configured as the serial clock pin SCL of the Inter-IC Bus Interface (IIC).

**NOTE:** This pin is not available in the 112-pin LQFP version.

## 2.3.29 PM0 / SDA — Port M I/O Pin 0

PM0 is a general purpose input or output pin. It can be configured as the serial data pin SDA of the Inter-IC Bus Interface (IIC).

**NOTE:** This pin is not available in the 112-pin LQFP version.

# 2.3.30 PP[5:2] / PWM[5:2] — Port P I/O Pins [5:2]

PP5-PP2 are general purpose input or output pins. They can be configured as Pulse Width Modulator (PWM) channel outputs PWM5-PWM2.

**NOTE:** These pins are not available in the 112-pin LQFP version.

# 2.3.31 PP[1:0] / PWM[1:0] — Port P I/O Pins [1:0]

PP1-PP0 are general purpose input or output pins. They can be configured as Pulse Width Modulator (PWM) channel outputs PWM1-PWM0.

# 2.3.32 PS7 / SS — Port S I/O Pin 7

PS7 is a general purpose input or output pin. It can be configured as slave select pin  $\overline{SS}$  of the Serial Peripheral Interface (SPI).

## 2.3.33 PS6 / SCK - Port S I/O Pin 6

PS6 is a general purpose input or output pin. It can be configured as serial clock pin SCK of the Serial Peripheral Interface (SPI).

## 2.3.34 PS5 / MOSI — Port S I/O Pin 5

PS5 is a general purpose input or output pin. It can be configured as the master output (during master mode) or slave input (during slave mode) pin MOSI of the Serial Peripheral Interface (SPI).

## 2.3.35 PS4 / MISO — Port S I/O Pin 4

PS4 is a general purpose input or output pin. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO for the Serial Peripheral Interface (SPI).

# 2.3.36 PS3 / TXD1 — Port S I/O Pin 3

PS3 is a general purpose input or output pin. It can be configured as transmit pin TXD1 of the Serial Communication Interface 1 (SCI1).

**NOTE:** This pin is not available in the 112-pin LQFP version.

# 2.3.37 PS2 / RXD1 — Port S I/O Pin 2

PS2 is a general purpose input or output pin. It can be configured as receive pin RXD1 of the Serial Communication Interface 1 (SCI1).

**NOTE:** This pin is not available in the 112-pin LQFP version.

#### MC9S12H256 Device User Guide - V01.20

If an internal access is made while E,  $R/\overline{W}$ , and  $\overline{LSTRB}$  are configured as bus control outputs and internal visibility is off (IVIS=0), E will remain low for the cycle,  $R/\overline{W}$  will remain high, and address, data and the  $\overline{LSTRB}$  pins will remain at their previous state.

When internal visibility is enabled (IVIS=1), certain internal cycles will be blocked from going external. During cycles when the BDM is selected,  $R/\overline{W}$  will remain high, data will maintain its previous state, and address and  $\overline{LSTRB}$  pins will be updated with the internal value. During CPU no access cycles when the BDM is not driving,  $R/\overline{W}$  will remain high, and address, data and the  $\overline{LSTRB}$  pins will remain at their previous state.

#### 4.2.1.5 Emulation Expanded Wide Mode

In expanded wide modes, Ports A and B are configured as a 16-bit multiplexed address and data bus and Port E provides bus control and status signals. These signals allow external memory and peripheral devices to be interfaced to the MCU. These signals can also be used by a logic analyzer to monitor the progress of application programs.

The bus control related pins in Port E (PE7/NOACC, PE6/MODB/IPIPE1, PE5/MODA/IPIPE0, PE4/ECLK, PE3/ $\overline{\text{LSTRB}}/\overline{\text{TAGLO}}$ , and PE2/ $\overline{\text{RW}}$ ) are all configured to serve their bus control output functions rather than general purpose I/O. Notice that writes to the bus control enable bits in the PEAR register in special mode are restricted.

#### 4.2.1.6 Emulation Expanded Narrow Mode

Expanded narrow modes are intended to allow connection of single 8-bit external memory devices for lower cost systems that do not need the performance of a full 16-bit external data bus. Accesses to internal resources that have been mapped external (i.e. PORTA, PORTB, DDRA, DDRB, PORTE, DDRE, PEAR, PUCR, RDRIV) will be accessed with a 16-bit data bus on Ports A and B. Accesses of 16-bit external words to addresses which are normally mapped external will be broken into two separate 8-bit accesses using Port A as an 8-bit data bus. Internal operations continue to use full 16-bit data paths. They are only visible externally as 16-bit information if IVIS=1.