#### Welcome to E-XFL.COM

### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 50MHz                                                                    |

| Co-Processors/DSP               | ·                                                                        |

| RAM Controllers                 | SDRAM                                                                    |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | ·                                                                        |

| Ethernet                        | 10Mbps (1)                                                               |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                        |

| Package / Case                  | 256-BBGA                                                                 |

| Supplier Device Package         | 256-PBGA (23x23)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc850dslczq50bu |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

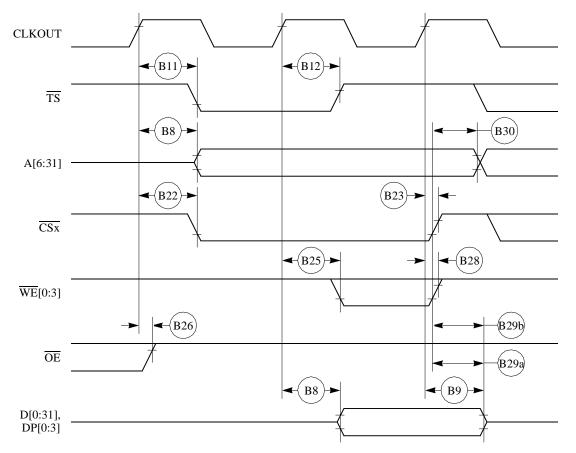

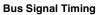

**Bus Signal Timing**

|      | <b>a</b>                                                                                                                | 50 MHz 66 MHz |       |       | 80 I  | MHz   |       | Cap Load | 11                 |      |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|----------|--------------------|------|

| Num  | Characteristic                                                                                                          | Min           | Max   | Min   | Max   | Min   | Мах   | FFACT    | (default<br>50 pF) | Unit |

| B9   | CLKOUT to A[6–31] RD/WR,<br>BURST, D[0–31], DP[0–3],<br>TSIZ[0–1], REG, RSV, AT[0–3],<br>PTR high-Z                     | 5.00          | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250    | 50.00              | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion                                                                   | 5.00          | 11.00 | 7.58  | 13.58 | 6.25  | 12.25 | 0.250    | 50.00              | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion,<br>(When driven by the memory<br>controller or PCMCIA interface) | 2.50          | 9.25  | 2.50  | 9.25  | 2.50  | 9.25  | —        | 50.00              | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation                                                                    | 5.00          | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250    | 50.00              | ns   |

| B12a | CLKOUT to TA, BI negation<br>(when driven by the memory<br>controller or PCMCIA interface)                              | 2.50          | 11.00 | 2.50  | 11.00 | 2.50  | 11.00 | —        | 50.00              | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ high-Z                                                                      | 5.00          | 19.00 | 7.58  | 21.58 | 6.25  | 20.25 | 0.250    | 50.00              | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ high-Z,<br>(when driven by the memory<br>controller or PCMCIA interface)    | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | —        | 50.00              | ns   |

| B14  | CLKOUT to $\overline{TEA}$ assertion                                                                                    | 2.50          | 10.00 | 2.50  | 10.00 | 2.50  | 10.00 | —        | 50.00              | ns   |

| B15  | CLKOUT to TEA high-Z                                                                                                    | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | —        | 50.00              | ns   |

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT(setup time) <sup>5</sup>                                | 9.75          | —     | 9.75  | —     | 9.75  | —     | —        | 50.00              | ns   |

| B16a | TEA, KR, RETRY, valid to CLKOUT (setup time) <sup>5</sup>                                                               | 10.00         | —     | 10.00 | —     | 10.00 | —     | —        | 50.00              | ns   |

| B16b | $\overline{\text{BB}}$ , $\overline{\text{BG}}$ , $\overline{\text{BR}}$ valid to CLKOUT (setup time) <sup>6</sup>      | 8.50          | _     | 8.50  | —     | 8.50  | —     | _        | 50.00              | ns   |

| B17  | $\frac{\text{CLKOUT to TA, TEA, BI, BB,}}{\text{BG, BR valid (Hold time).}^5}$                                          | 1.00          |       | 1.00  | —     | 1.00  | _     | _        | 50.00              | ns   |

| B17a | CLKOUT to KR, RETRY, except<br>TEA valid (hold time)                                                                    | 2.00          | —     | 2.00  | —     | 2.00  | —     | _        | 50.00              | ns   |

| B18  | D[0–31], DP[0–3] valid to<br>CLKOUT rising edge (setup<br>time) <sup>7</sup>                                            | 6.00          | _     | 6.00  |       | 6.00  |       | _        | 50.00              | ns   |

| B19  | CLKOUT rising edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>7</sup>                                             | 1.00          | _     | 1.00  |       | 1.00  |       | _        | 50.00              | ns   |

| B20  | D[0–31], DP[0–3] valid to<br>CLKOUT falling edge (setup<br>time) <sup>8</sup>                                           | 4.00          |       | 4.00  |       | 4.00  | —     | _        | 50.00              | ns   |

| B21  | CLKOUT falling edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>8</sup>                                            | 2.00          | —     | 2.00  |       | 2.00  | —     | —        | —                  |      |

| Table 6. | <b>Bus Operation Timing</b> | <sup>1</sup> (continued) |

|----------|-----------------------------|--------------------------|

|----------|-----------------------------|--------------------------|

**Bus Signal Timing**

| [    |                                                                                                                                             |               |       |       |       |       |       |                      |        |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|----------------------|--------|----|

| Num  | Characteristic                                                                                                                              | 50 MHz 66 MHz |       |       | 80    | MHz   | FFACT | Cap Load<br>(default | Unit   |    |

| -    |                                                                                                                                             | Min           | Max   | Min   | Max   | Min   | Max   | _                    | 50 pF) |    |

| B28c | CLKOUT falling edge to<br>WE[0–3] negated GPCM write<br>access TRLX = 0,1 CSNT = 1<br>write access TRLX = 0, CSNT =<br>1, EBDF = 1          | 7.00          | 14.00 | 11.00 | 18.00 | 9.00  | 16.00 | 0.375                | 50.00  | ns |

| B28d | CLKOUT falling edge to $\overline{CS}$<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 1               | _             | 14.00 | _     | 18.00 | _     | 16.00 | 0.375                | 50.00  | ns |

| B29  | $\overline{WE[0-3]}$ negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, CSNT = 0                                                   | 3.00          | _     | 6.00  | _     | 4.00  | _     | 0.250                | 50.00  | ns |

| B29a | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 0 CSNT = 1,<br>EBDF = 0                                          | 8.00          | _     | 13.00 | _     | 11.00 | _     | 0.500                | 50.00  | ns |

| B29b | CS negated to D[0–31],<br>DP[0–3], high-Z GPCM write<br>access, ACS = 00, TRLX = 0 &<br>CSNT = 0                                            | 3.00          |       | 6.00  |       | 4.00  |       | 0.250                | 50.00  | ns |

| B29c | $\overline{\text{CS}}$ negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 8.00          |       | 13.00 |       | 11.00 |       | 0.500                | 50.00  | ns |

| B29d | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                         | 28.00         |       | 43.00 |       | 36.00 |       | 1.500                | 50.00  | ns |

| B29e | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0                     | 28.00         |       | 43.00 |       | 36.00 |       | 1.500                | 50.00  | ns |

| B29f | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                          | 5.00          |       | 9.00  |       | 7.00  |       | 0.375                | 50.00  | ns |

| B29g | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1                      | 5.00          |       | 9.00  |       | 7.00  |       | 0.375                | 50.00  | ns |

| Table 6. | <b>Bus Operation</b> | Timing <sup>1</sup> | (continued) |

|----------|----------------------|---------------------|-------------|

|----------|----------------------|---------------------|-------------|

|      |                                                                                                                                                                                                                                                                                                                                                                                      | 50 MHz 66 MHz |     |       | 00.5 | /LI-   |     | Cap Load |          |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-------|------|--------|-----|----------|----------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                       |               |     |       |      | 80 MHz |     | FFACT    | (default | Unit |

|      |                                                                                                                                                                                                                                                                                                                                                                                      | Min           | Max | Min   | Мах  | Min    | Мах |          | 50 pF)   |      |

| B29h | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                   | 25.00         |     | 39.00 |      | 31.00  |     | 1.375    | 50.00    | ns   |

| B29i | $\overline{\text{CS}}$ negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1                                                                                                                                                                                                                                          | 25.00         | _   | 39.00 | _    | 31.00  | _   | 1.375    | 50.00    | ns   |

| B30  | CS, WE[0–3] negated to<br>A[6–31] invalid<br>GPCM write access <sup>9</sup>                                                                                                                                                                                                                                                                                                          | 3.00          | _   | 6.00  | _    | 4.00   | _   | 0.250    | 50.00    | ns   |

| B30a | $\label{eq:weighted} \hline \hline WE[0-3] \mbox{ negated to } A[6-31] \mbox{ invalid } \\ GPCM \mbox{ write access, } TRLX = 0, \\ CSNT = 1, \end{cases} \mbox{ CSNT = 1, } \hline CS \mbox{ negated to } \\ A[6-31] \mbox{ invalid GPCM write } \\ access \mbox{ TRLX = 0, } CSNT = 1, \\ ACS = 10 \mbox{ or } ACS = 11, \mbox{ EBDF = } \\ 0 \\ \hline \hline \end{array}$        | 8.00          |     | 13.00 |      | 11.00  |     | 0.500    | 50.00    | ns   |

| B30b | $\label{eq:weighted} \hline \hline WE[0-3] \mbox{ negated to } A[6-31] \mbox{ invalid } \\ GPCM \mbox{ write access, } TRLX = 1, \\ CSNT = 1. \ensuremath{\overline{CS}}\xspace$ negated to $ A[6-31] \mbox{ Invalid GPCM write $ access TRLX = 1, CSNT = 1, $ ACS = 10 \mbox{ or } ACS = 11, $ EBDF = $ 0 $ $ 0 $ $ $ $ $ $ $ $ $ $ $ $ $ $$                                        | 28.00         | _   | 43.00 | _    | 36.00  | _   | 1.500    | 50.00    | ns   |

| B30c | $\label{eq:WE[0-3]} \begin{array}{l} \mbox{megated to A[6-31]} \\ \mbox{invalid} \\ \mbox{GPCM write access, TRLX = 0,} \\ \mbox{CSNT = 1. } \hline CS \mbox{ negated to} \\ \mbox{A[6-31] invalid GPCM write} \\ \mbox{access, TRLX = 0, CSNT = 1,} \\ \mbox{ACS = 10 or ACS = 11, EBDF =} \\ \mbox{1} \end{array}$                                                                 | 5.00          | _   | 8.00  | _    | 6.00   |     | 0.375    | 50.00    | ns   |

| B30d | $\label{eq:WE[0-3]} \begin{array}{l} \hline WE[0-3] \mbox{ negated to } A[6-31] \\ \hline \mbox{ invalid GPCM write access} \\ \hline TRLX = 1, \mbox{ CSNT = 1}, \mbox{ CS} \\ \hline \mbox{ negated to } A[6-31] \mbox{ invalid} \\ \hline \mbox{ GPCM write access } TRLX = 1, \\ \hline \mbox{ CSNT = 1}, \mbox{ ACS = 10 or } ACS = \\ \hline \mbox{ 11, EBDF = 1} \end{array}$ | 25.00         |     | 39.00 |      | 31.00  |     | 1.375    | 50.00    | ns   |

| Num  | Characteristic                                                                                                                | 50 MHz 6 |       | 66 I  | MHz 80 |       | MHz   | FFACT | Cap Load<br>(default | Unit |

|------|-------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|--------|-------|-------|-------|----------------------|------|

|      |                                                                                                                               | Min      | Max   | Min   | Max    | Min   | Мах   | _     | 50 pF)               |      |

| B33a | CLKOUT rising edge to GPL<br>valid - as requested by control<br>bit GxT3 in the corresponding<br>word in the UPM              | 5.00     | 12.00 | 8.00  | 14.00  | 6.00  | 13.00 | 0.250 | 50.00                | ns   |

| B34  | A[6–31] and D[0–31] to CS valid<br>- as requested by control bit<br>CST4 in the corresponding<br>word in the UPM              | 3.00     | _     | 6.00  | _      | 4.00  | _     | 0.250 | 50.00                | ns   |

| B34a | A[6–31] and D[0–31] to $\overline{CS}$ valid<br>- as requested by control bit<br>CST1 in the corresponding<br>word in the UPM | 8.00     | _     | 13.00 | _      | 11.00 | _     | 0.500 | 50.00                | ns   |

| B34b | A[6–31] and D[0–31] to CS valid<br>- as requested by CST2 in the<br>corresponding word in UPM                                 | 13.00    | —     | 21.00 | —      | 17.00 | —     | 0.750 | 50.00                | ns   |

| B35  | A[6-31] to $\overline{CS}$ valid - as<br>requested by control bit BST4 in<br>the corresponding word in UPM                    | 3.00     | —     | 6.00  | —      | 4.00  | —     | 0.250 | 50.00                | ns   |

| B35a | A[6–31] and D[0–31] to BS valid<br>- as requested by BST1 in the<br>corresponding word in the UPM                             | 8.00     | —     | 13.00 | —      | 11.00 | —     | 0.500 | 50.00                | ns   |

| B35b | A[6–31] and D[0–31] to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM              | 13.00    | _     | 21.00 | _      | 17.00 | _     | 0.750 | 50.00                | ns   |

| B36  | A[6–31] and D[0–31] to GPL<br>valid - as requested by control<br>bit GxT4 in the corresponding<br>word in the UPM             | 3.00     | _     | 6.00  | _      | 4.00  | _     | 0.250 | 50.00                | ns   |

| B37  | UPWAIT valid to CLKOUT falling edge 10                                                                                        | 6.00     | —     | 6.00  | —      | 6.00  | —     | —     | 50.00                | ns   |

| B38  | CLKOUT falling edge to<br>UPWAIT valid <sup>10</sup>                                                                          | 1.00     | —     | 1.00  | —      | 1.00  | —     | —     | 50.00                | ns   |

| B39  | AS valid to CLKOUT rising edge                                                                                                | 7.00     | _     | 7.00  | _      | 7.00  | _     | —     | 50.00                | ns   |

| B40  | A[6–31], TSIZ[0–1], RD/WR,<br>BURST, valid to CLKOUT rising<br>edge.                                                          | 7.00     |       | 7.00  |        | 7.00  |       | —     | 50.00                | ns   |

| B41  | TS valid to CLKOUT rising edge (setup time)                                                                                   | 7.00     | _     | 7.00  | —      | 7.00  | —     | _     | 50.00                | ns   |

Figure 13 through Figure 15 provide the timing for the external bus write controlled by various GPCM factors.

Figure 13. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 1, CSNT = 1)

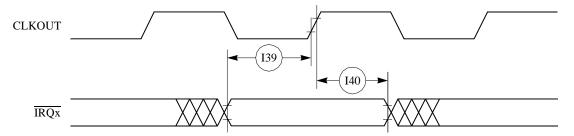

Table 7 provides interrupt timing for the MPC850.

| Num | Characteristic <sup>1</sup>                    | 50 MHz |     | 66N   | lHz | 80 N  | Unit |      |

|-----|------------------------------------------------|--------|-----|-------|-----|-------|------|------|

|     | Characteristic                                 |        | Max | Min   | Max | Min   | Max  | onit |

| 139 | IRQx valid to CLKOUT rising edge (set up time) | 6.00   |     | 6.00  | _   | 6.00  |      | ns   |

| 140 | IRQx hold time after CLKOUT.                   | 2.00   | _   | 2.00  |     | 2.00  |      | ns   |

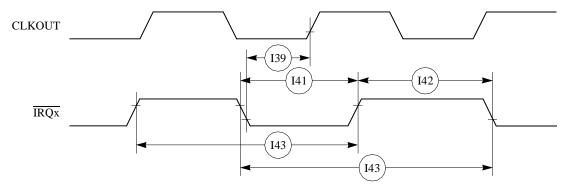

| l41 | IRQx pulse width low                           | 3.00   |     | 3.00  |     | 3.00  |      | ns   |

| 142 | IRQx pulse width high                          | 3.00   | _   | 3.00  |     | 3.00  | _    | ns   |

| 143 | IRQx edge-to-edge time                         | 80.00  | _   | 121.0 | _   | 100.0 | _    | ns   |

Table 7. Interrupt Timing

<sup>1</sup> The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry, and has no direct relation with the total system interrupt latency that the MPC850 is able to support

Figure 22 provides the interrupt detection timing for the external level-sensitive lines.

Figure 22. Interrupt Detection Timing for External Level Sensitive Lines

Figure 23 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 23. Interrupt Detection Timing for External Edge Sensitive Lines

**Bus Signal Timing**

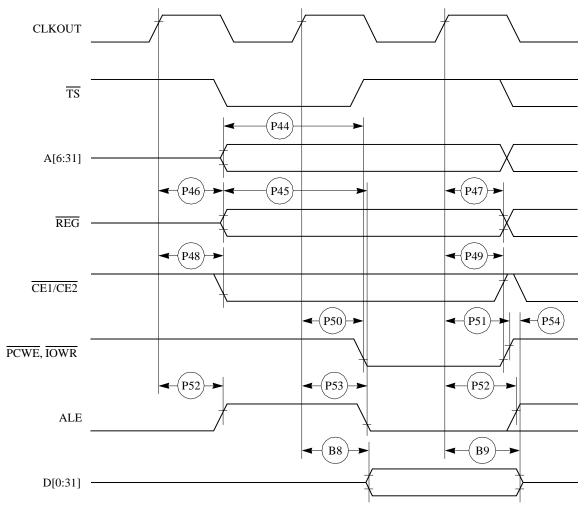

Figure 25 provides the PCMCIA access cycle timing for the external bus write.

Figure 25. PCMCIA Access Cycles Timing External Bus Write

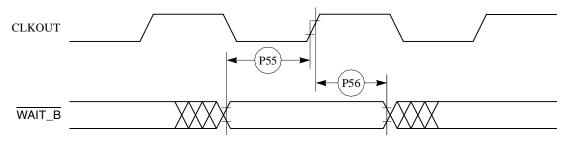

Figure 26 provides the PCMCIA WAIT signals detection timing.

Figure 26. PCMCIA WAIT Signal Detection Timing

**Bus Signal Timing**

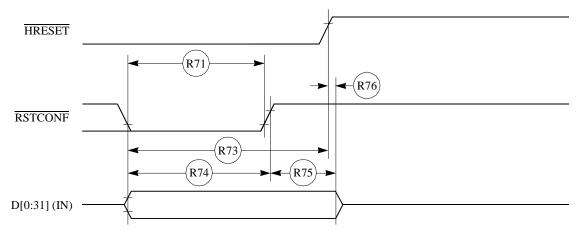

Figure 31 shows the reset timing for the data bus configuration.

Figure 31. Reset Timing—Configuration from Data Bus

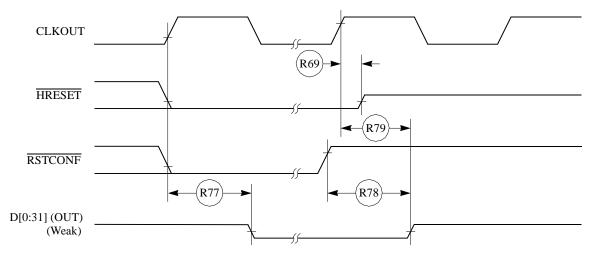

Figure 32 provides the reset timing for the data bus weak drive during configuration.

Figure 32. Reset Timing—Data Bus Weak Drive during Configuration

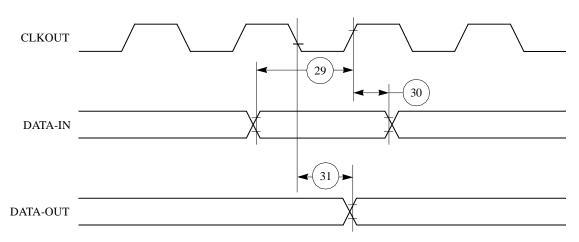

Figure 38. Parallel I/O Data-In/Data-Out Timing Diagram

# 8.2 IDMA Controller AC Electrical Specifications

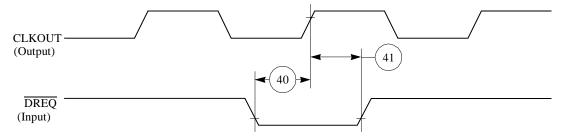

Table 14 provides the IDMA controller timings as shown in Figure 39 to Figure 42.

| Num | Characteristic                                                                                           | All Fred | Unit  |      |

|-----|----------------------------------------------------------------------------------------------------------|----------|-------|------|

| Num | Characteristic                                                                                           | Min      | Max   | Onic |

| 40  | DREQ setup time to clock high                                                                            | 7.00     | _     | ns   |

| 41  | DREQ hold time from clock high                                                                           | 3.00     | _     | ns   |

| 42  | SDACK assertion delay from clock high                                                                    | _        | 12.00 | ns   |

| 43  | SDACK negation delay from clock low                                                                      | _        | 12.00 | ns   |

| 44  | SDACK negation delay from TA low                                                                         | _        | 20.00 | ns   |

| 45  | SDACK negation delay from clock high                                                                     | _        | 15.00 | ns   |

| 46  | $\overline{TA}$ assertion to falling edge of the clock setup time (applies to external $\overline{TA}$ ) | 7.00     |       | ns   |

Table 14. IDMA Controller Timing

Figure 39. IDMA External Requests Timing Diagram

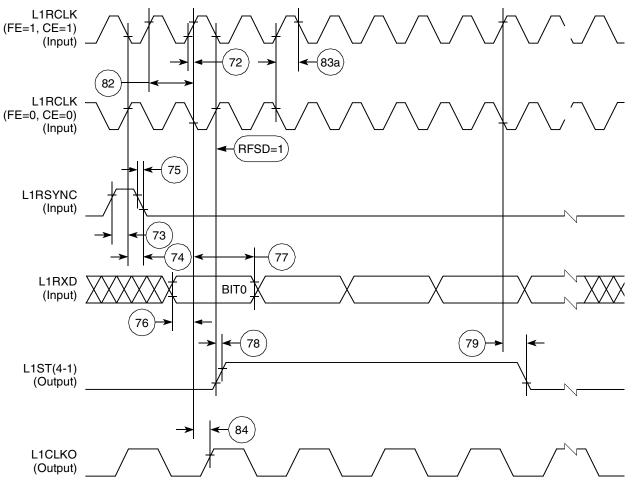

Figure 46. SI Receive Timing with Double-Speed Clocking (DSC = 1)

Figure 52. HDLC Bus Timing Diagram

# 8.7 Ethernet Electrical Specifications

Table 20 provides the Ethernet timings as shown in Figure 53 to Figure 55.

| Num | Characteristic                                                  |        | All Frequencies |      |

|-----|-----------------------------------------------------------------|--------|-----------------|------|

| Num |                                                                 |        | Max             | Unit |

| 120 | CLSN width high                                                 | 40.00  | _               | ns   |

| 121 | RCLKx rise/fall time (x = 2, 3 for all specs in this table)     | _      | 15.00           | ns   |

| 122 | RCLKx width low                                                 | 40.00  |                 | ns   |

| 123 | RCLKx clock period <sup>1</sup>                                 | 80.00  | 120.00          | ns   |

| 124 | RXDx setup time                                                 | 20.00  |                 | ns   |

| 125 | RXDx hold time                                                  | 5.00   |                 | ns   |

| 126 | RENA active delay (from RCLKx rising edge of the last data bit) | 10.00  | _               | ns   |

| 127 | RENA width low                                                  | 100.00 | _               | ns   |

| 128 | TCLKx rise/fall time                                            | —      | 15.00           | ns   |

| 129 | TCLKx width low                                                 | 40.00  |                 | ns   |

| 130 | TCLKx clock period <sup>1</sup>                                 | 99.00  | 101.00          | ns   |

| 131 | TXDx active delay (from TCLKx rising edge)                      |        | 50.00           | ns   |

| 132 | TXDx inactive delay (from TCLKx rising edge)                    | 10.00  | 50.00           | ns   |

| 133 | TENA active delay (from TCLKx rising edge)                      | 10.00  | 50.00           | ns   |

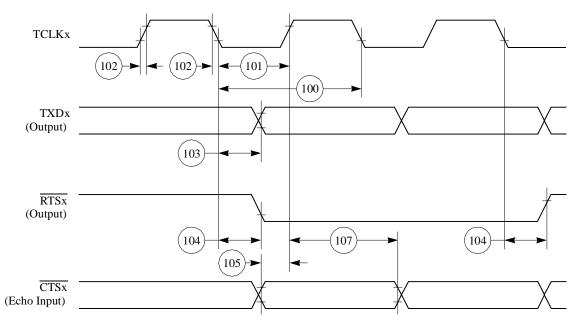

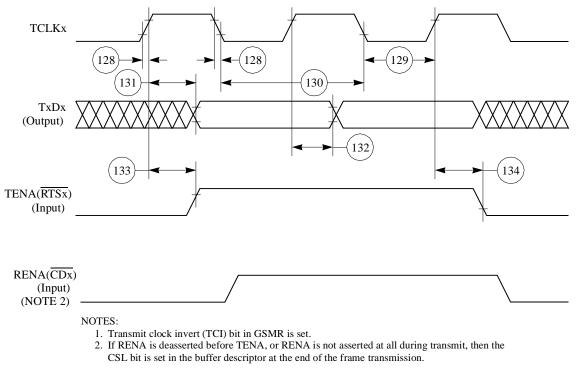

Figure 55. Ethernet Transmit Timing Diagram

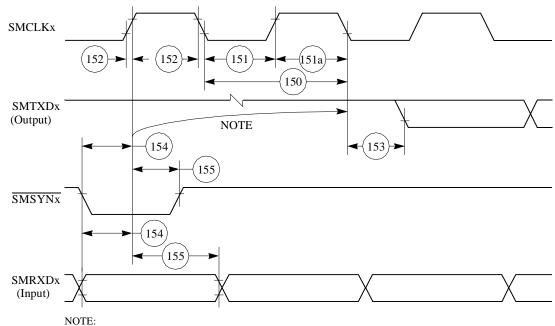

# 8.8 SMC Transparent AC Electrical Specifications

Figure 21 provides the SMC transparent timings as shown in Figure 56.

| Num  | Characteristic                                 | All Frequencies |       | Unit |

|------|------------------------------------------------|-----------------|-------|------|

|      | Characteristic                                 | Min             | Мах   | Unit |

| 150  | SMCLKx clock period <sup>1</sup>               | 100.00          | _     | ns   |

| 151  | SMCLKx width low                               | 50.00           | _     | ns   |

| 151a | SMCLKx width high                              | 50.00           | _     | ns   |

| 152  | SMCLKx rise/fall time                          | _               | 15.00 | ns   |

| 153  | SMTXDx active delay (from SMCLKx falling edge) | 10.00           | 50.00 | ns   |

| 154  | SMRXDx/SMSYNx setup time                       | 20.00           | _     | ns   |

| 155  | SMRXDx/SMSYNx hold time                        | 5.00            | _     | ns   |

| Table 21. | Serial | Management | Controller | Timing |

|-----------|--------|------------|------------|--------|

|-----------|--------|------------|------------|--------|

<sup>1</sup> The ratio SyncCLK/SMCLKx must be greater or equal to 2/1.

1. This delay is equal to an integer number of character-length clocks.

### Figure 56. SMC Transparent Timing Diagram

# 8.9 SPI Master AC Electrical Specifications

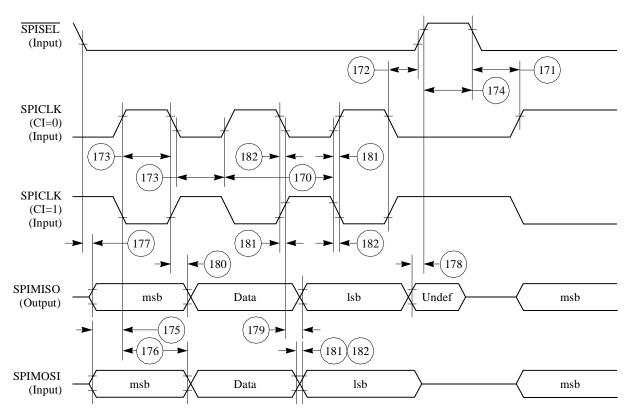

Table 22 provides the SPI master timings as shown in Figure 57 and Figure 58.

| Num   | Characteristic                      | All Frequencies |       | Unit             |

|-------|-------------------------------------|-----------------|-------|------------------|

| Nulli | Characteristic                      | Min             | Max   | onit             |

| 160   | MASTER cycle time                   | 4               | 1024  | t <sub>cyc</sub> |

| 161   | MASTER clock (SCK) high or low time | 2               | 512   | t <sub>cyc</sub> |

| 162   | MASTER data setup time (inputs)     | 50.00           | _     | ns               |

| 163   | Master data hold time (inputs)      | 0.00            | _     | ns               |

| 164   | Master data valid (after SCK edge)  | —               | 20.00 | ns               |

| 165   | Master data hold time (outputs)     | 0.00            | _     | ns               |

| 166   | Rise time output                    | —               | 15.00 | ns               |

| 167   | Fall time output                    | —               | 15.00 | ns               |

### Table 22. SPI Master Timing

Figure 59. SPI Slave (CP = 0) Timing Diagram

# 9 Mechanical Data and Ordering Information

Table 26 provides information on the MPC850 derivative devices.

| Table 26. | <b>MPC850</b> | Family | / Derivatives |

|-----------|---------------|--------|---------------|

|-----------|---------------|--------|---------------|

| Device    | Ethernet Support | Number of SCCs <sup>1</sup> | 32-Channel HDLC<br>Support | 64-Channel HDLC<br>Support <sup>2</sup> |

|-----------|------------------|-----------------------------|----------------------------|-----------------------------------------|

| MPC850    | N/A              | One                         | N/A                        | N/A                                     |

| MPC850DE  | Yes              | Two                         | N/A                        | N/A                                     |

| MPC850SR  | Yes              | Two                         | N/A                        | Yes                                     |

| MPC850DSL | Yes              | Two                         | No                         | No                                      |

<sup>1</sup> Serial Communication Controller (SCC)

<sup>2</sup> 50 MHz version supports 64 time slots on a time division multiplexed line using one SCC

Table 27 identifies the packages and operating frequencies available for the MPC850.

Table 27. MPC850 Package/Frequency/Availability

| Package Type                                     | Frequency (MHz) | Temperature (Tj) | Order Number                                                            |

|--------------------------------------------------|-----------------|------------------|-------------------------------------------------------------------------|

| 256-Lead Plastic Ball Grid Array<br>(ZT suffix)  | 50              | 0°C to 95°C      | XPC850ZT50BU<br>XPC850DEZT50BU<br>XPC850SRZT50BU<br>XPC850DSLZT50BU     |

|                                                  | 66              | 0°C to 95°C      | XPC850ZT66BU<br>XPC850DEZT66BU<br>XPC850SRZT66BU                        |

|                                                  | 80              | 0°C to 95°C      | XPC850ZT80BU<br>XPC850DEZT80BU<br>XPC850SRZT80BU                        |

| 256-Lead Plastic Ball Grid Array<br>(CZT suffix) | 50              | -40°C to 95°C    | XPC850CZT50BU<br>XPC850DECZT50BU<br>XPC850SRCZT50BU<br>XPC850DSLCZT50BU |

|                                                  | 66              |                  | XPC850CZT66BU<br>XPC850DECZT66BU<br>XPC850SRCZT66BU                     |

|                                                  | 80              |                  | XPC850CZT80B<br>XPC850DECZT80B<br>XPC850SRCZT80B                        |

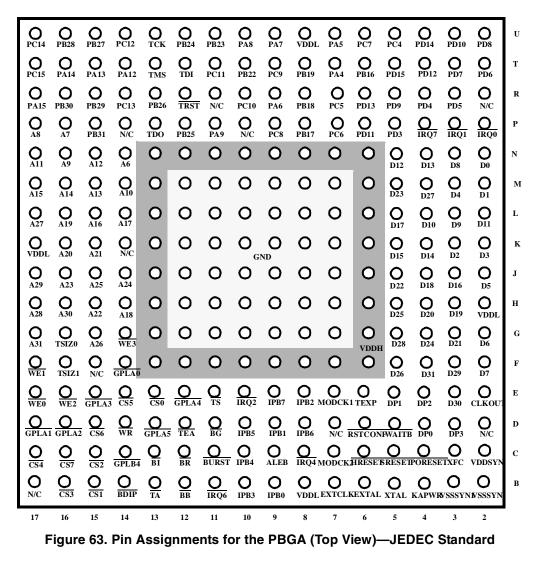

# 9.1 Pin Assignments and Mechanical Dimensions of the PBGA

The original pin numbering of the MPC850 conformed to a Freescale proprietary pin numbering scheme that has since been replaced by the JEDEC pin numbering standard for this package type. To support

Figure 63 shows the JEDEC pinout of the PBGA package as viewed from the top surface.

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to AN-1231/D, Plastic Ball Grid Array Application Note available from your local Freescale sales office.

### Mechanical Data and Ordering Information

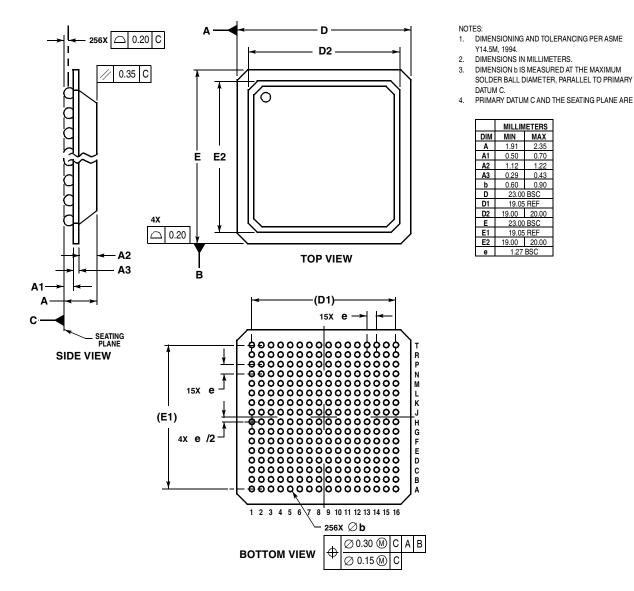

Figure 64 shows the non-JEDEC package dimensions of the PBGA.

Figure 64. Package Dimensions for the Plastic Ball Grid Array (PBGA)-non-JEDEC Standard

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK

### How to Reach Us:

Home Page: www.freescale.com

email: support@freescale.com

### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC850EC Rev. 2 07/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2005.