Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                          |

|---------------------------------|--------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                 |

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 50MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10Mbps (1)                                                               |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                          |

| Security Features               | -                                                                        |

| Package / Case                  | 256-BBGA                                                                 |

| Supplier Device Package         | 256-PBGA (23x23)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc850dezq50bur2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

The CPM of the MPC850 supports up to seven serial channels, as follows:

- One or two serial communications controllers (SCCs). The SCCs support Ethernet, ATM (MPC850SR and MPC850DSL), HDLC and a number of other protocols, along with a transparent mode of operation.

- One USB channel

- Two serial management controllers (SMCs)

- One I<sup>2</sup>C port

- One serial peripheral interface (SPI).

Table 1 shows the functionality supported by the members of the MPC850 family.

**Table 1. MPC850 Functionality Matrix**

| Part      | Number of<br>SCCs<br>Supported | Ethernet<br>Support | ATM Support | USB Support | Multi-channel<br>HDLC<br>Support | Number of PCMCIA Slots Supported |

|-----------|--------------------------------|---------------------|-------------|-------------|----------------------------------|----------------------------------|

| MPC850    | 1                              | Yes                 | -           | Yes         | -                                | 1                                |

| MPC850DE  | 2                              | Yes                 | -           | Yes         | -                                | 1                                |

| MPC850SR  | 2                              | Yes                 | Yes         | Yes         | Yes                              | 1                                |

| MPC850DSL | 2                              | Yes                 | Yes         | Yes         | No                               | 1                                |

Additional documentation may be provided for parts listed in Table 1.

#### **Features**

- 2-Kbyte instruction cache and 1-Kbyte data cache (Harvard architecture)

- Caches are two-way, set-associative

- Physically addressed

- Cache blocks can be updated with a 4-word line burst

- Least-recently used (LRU) replacement algorithm

- Lockable one-line granularity

- Memory management units (MMUs) with 8-entry translation lookaside buffers (TLBs) and fully-associative instruction and data TLBs

- MMUs support multiple page sizes of 4 Kbytes, 16 Kbytes, 256 Kbytes, 512 Kbytes, and

8 Mbytes; 16 virtual address spaces and eight protection groups

- Advanced on-chip emulation debug mode

- Data bus dynamic bus sizing for 8, 16, and 32-bit buses

- Supports traditional 68000 big-endian, traditional x86 little-endian and modified little-endian memory systems

- Twenty-six external address lines

- Completely static design (0–80 MHz operation)

- System integration unit (SIU)

- Hardware bus monitor

- Spurious interrupt monitor

- Software watchdog

- Periodic interrupt timer

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Memory controller (eight banks)

- Glueless interface to DRAM single in-line memory modules (SIMMs), synchronous DRAM (SDRAM), static random-access memory (SRAM), electrically programmable read-only memory (EPROM), flash EPROM, etc.

- Memory controller programmable to support most size and speed memory interfaces

- Boot chip-select available at reset (options for 8, 16, or 32-bit memory)

- Variable block sizes, 32 Kbytes to 256 Mbytes

- Selectable write protection

- On-chip bus arbiter supports one external bus master

- Special features for burst mode support

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

### Interrupts

- Eight external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Fifteen internal interrupt sources

- Programmable priority among SCCs and USB

- Programmable highest-priority request

- Single socket PCMCIA-ATA interface

- Master (socket) interface, release 2.1 compliant

- Single PCMCIA socket

- Supports eight memory or I/O windows

- Communications processor module (CPM)

- 32-bit, Harvard architecture, scalar RISC communications processor (CP)

- Protocol-specific command sets (for example, GRACEFUL STOP TRANSMIT stops transmission

after the current frame is finished or immediately if no frame is being sent and CLOSE RXBD

closes the receive buffer descriptor)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- Twenty serial DMA (SDMA) channels for the serial controllers, including eight for the four USB endpoints

- Three parallel I/O registers with open-drain capability

- Four independent baud-rate generators (BRGs)

- Can be connected to any SCC, SMC, or USB

- Allow changes during operation

- Autobaud support option

- Two SCCs (serial communications controllers)

- Ethernet/IEEE 802.3, supporting full 10-Mbps operation

- HDLC/SDLC<sup>TM</sup> (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk<sup>®</sup>

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

| Table 5.  | DC Electrical | <b>Specifications</b> | (continued)   |

|-----------|---------------|-----------------------|---------------|

| I abic 5. | DO LICCUITORI | Opcomoations          | (COIILIIIGCA) |

| Characteristic                                                                                                                                                                     | Symbol          | Min       | Max     | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|---------|------|

| Input low voltage                                                                                                                                                                  | VIL             | GND       | 0.8     | V    |

| EXTAL, EXTCLK input high voltage                                                                                                                                                   | VIHC            | 0.7*(VCC) | VCC+0.3 | V    |

| Input leakage current, Vin = 5.5 V (Except TMS, TRST, DSCK and DSDI pins)                                                                                                          | l <sub>in</sub> | _         | 100     | μΑ   |

| Input leakage current, Vin = 3.6V (Except TMS, TRST, DSCK and DSDI pins)                                                                                                           | I <sub>In</sub> | _         | 10      | μΑ   |

| Input leakage current, Vin = 0V (Except TMS, TRST, DSCK and DSDI pins)                                                                                                             | I <sub>In</sub> | _         | 10      | μΑ   |

| Input capacitance                                                                                                                                                                  | C <sub>in</sub> | _         | 20      | pF   |

| Output high voltage, IOH = -2.0 mA, VDDH = 3.0V except XTAL, XFC, and open-drain pins                                                                                              | VOH             | 2.4       | _       | V    |

| Output low voltage CLKOUT <sup>3</sup> IOL = 3.2 mA <sup>1</sup> IOL = 5.3 mA <sup>2</sup> IOL = 7.0 mA PA[14]/USBOE, PA[12]/TXD2 IOL = 8.9 mA TS, TA, TEA, BI, BB, HRESET, SRESET | VOL             | _         | 0.5     | V    |

A[6:31], TSIZO/REG, TSIZ1, D[0:31], DP[0:3]/IRQ[3:6], RD/WR, BURST, RSV/IRQ2, IP\_B[0:1]/IWP[0:1]/VFLS[0:1], IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, PA[15]/USBRXD, PA[13]/RXD2, PA[9]/L1TXDA/SMRXD2, PA[8]/L1RXDA/SMTXD2, PA[7]/CLK1/TIN1/L1RCLKA/BRGO1, PA[6]/CLK2/TOUT1/TIN3, PA[5]/CLK3/TIN2/L1TCLKA/BRGO2, PA[4]/CLK4/TOUT2/TIN4, PB[31]/SPISEL, PB[30]/SPICLK/TXD3, PB[29]/SPIMOSI /RXD3, PB[28]/SPIMISO/BRGO3, PB[27]/I2CSDA/BRGO1, PB[26]/I2CSCL/BRGO2, PB[25]/SMTXD1/TXD3, PB[24]/SMRXD1/RXD3, PB[23]/SMSYN1/SDACK1, PB[22]/SMSYN2/SDACK2, PB[19]/L1ST1, PB[18]/RTS2/L1ST2, PB[17]/L1ST3, PB[16]/L1RQa/L1ST4, PC[15]/DREQ0/L1ST5, PC[14]/DREQ1/RTS2/L1ST6, PC[13]/L1ST7/RTS3, PC[12]/L1RQa/L1ST8, PC[11]/USBRXP, PC[10]/TGATE1/USBRXN, PC[9]/CTS2, PC[8]/CD2/TGATE1, PC[7]/USBTXP, PC[6]/USBTXN, PC[5]/CTS3/L1TSYNCA/SDACK1, PD[4], PD[3]

# 5 Power Considerations

The average chip-junction temperature, T<sub>I</sub>, in °C can be obtained from the equation:

$$T_{\rm J} = T_{\rm A} + (P_{\rm D} \bullet \theta_{\rm JA})(1)$$

where

$T_A = Ambient temperature, °C$

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

BDIP/GPL\_B5, BR, BG, FRZ/IRQ6, CS[0:5], CS6/CE1\_B, CS7/CE2\_B, WE0/BS\_AB0/IORD, WE1/BS\_AB1/IOWR, WE2/BS\_AB2/PCOE, WE3/BS\_AB3/PCWE, GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A[2:3]/GPL\_B[2:3]/CS[2:3], UPWAITA/GPL\_A4/AS, UPWAITB/GPL\_B4, GPL\_A5, ALE\_B/DSCK/AT1, OP2/MODCK1/STS, OP3/MODCK2/DSDO

<sup>3</sup> The MPC850 IBIS model must be used to accurately model the behavior of the Clkout output driver for the full and half drive setting. Due to the nature of the Clkout output buffer, IOH and IOL for Clkout should be extracted from the IBIS model at any output voltage level.

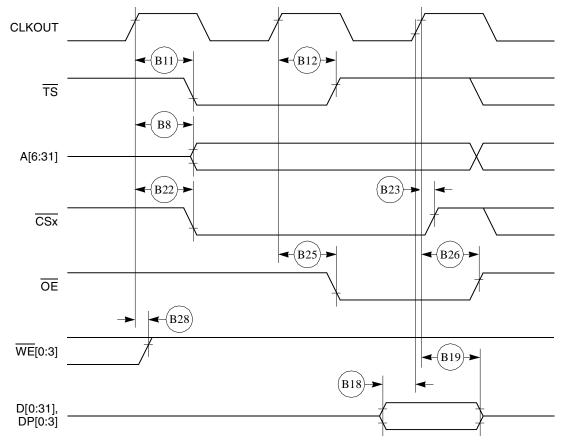

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nicons | Oh avaataviatia                                                                                                             | 50 I  | MHz   | 66 1  | ИНz   | 80 1  | ИНz   | FFACT | Cap Load           | Unit |

|--------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|------|

| Num    | Characteristic                                                                                                              | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) |      |

| B22    | CLKOUT rising edge to CS asserted GPCM ACS = 00                                                                             | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B22a   | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0,1                                            | _     | 8.00  | _     | 8.00  | _     | 8.00  | _     | 50.00              | ns   |

| B22b   | CLKOUT falling edge to CS asserted GPCM ACS = 11, TRLX = 0, EBDF = 0                                                        | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B22c   | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 11, TRLX = 0, EBDF = 1                                    | 7.00  | 14.00 | 11.00 | 18.00 | 9.00  | 16.00 | 0.375 | 50.00              | ns   |

| B23    | CLKOUT rising edge to $\overline{\text{CS}}$ negated GPCM read access, GPCM write access ACS = 00, TRLX = 0 & CSNT = 0      | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | _     | 50.00              | ns   |

| B24    | A[6-31] to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0.                                                         | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns   |

| B24a   | A[6–31] to $\overline{\text{CS}}$ asserted GPCM<br>ACS = 11, TRLX = 0                                                       | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns   |

| B25    | CLKOUT rising edge to OE, WE[0-3] asserted                                                                                  | _     | 9.00  | _     | 9.00  | _     | 9.00  | _     | 50.00              | ns   |

| B26    | CLKOUT rising edge to OE negated                                                                                            | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | _     | 50.00              | ns   |

| B27    | A[6–31] to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 1                                                          | 23.00 | _     | 36.00 | _     | 29.00 | _     | 1.250 | 50.00              | ns   |

| B27a   | A[6–31] to $\overline{\text{CS}}$ asserted GPCM<br>ACS = 11, TRLX = 1                                                       | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns   |

| B28    | CLKOUT rising edge to WE[0-3] negated GPCM write access CSNT = 0                                                            | _     | 9.00  | _     | 9.00  | _     | 9.00  | _     | 50.00              | ns   |

| B28a   | CLKOUT falling edge to WE[0-3] negated GPCM write access TRLX = 0,1 CSNT = 1, EBDF = 0                                      | 5.00  | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250 | 50.00              | ns   |

| B28b   | CLKOUT falling edge to $\overline{\text{CS}}$ negated GPCM write access TRLX = 0,1 CSNT = 1, ACS = 10 or ACS = 11, EBDF = 0 | _     | 12.00 | _     | 14.00 | _     | 13.00 | 0.250 | 50.00              | ns   |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Num  | Chavastavistis                                                                                                          | 50 I  | ИНz   | 66 I  | ИНz   | 80 1  | ИНz   | FEACT | Cap Load           | l lmit |

|------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|--------|

| Num  | Characteristic                                                                                                          | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit   |

| B28c | CLKOUT falling edge to WE[0-3] negated GPCM write access TRLX = 0,1 CSNT = 1 write access TRLX = 0, CSNT = 1, EBDF = 1  | 7.00  | 14.00 | 11.00 | 18.00 | 9.00  | 16.00 | 0.375 | 50.00              | ns     |

| B28d | CLKOUT falling edge to CS<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 1        | _     | 14.00 | _     | 18.00 | _     | 16.00 | 0.375 | 50.00              | ns     |

| B29  | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, CSNT = 0                                            | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns     |

| B29a | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 0 CSNT = 1,<br>EBDF = 0                      | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns     |

| B29b | CS negated to D[0-31],<br>DP[0-3], high-Z GPCM write<br>access, ACS = 00, TRLX = 0 &<br>CSNT = 0                        | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns     |

| B29c | CS negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns     |

| B29d | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>EBDF = 0                     | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns     |

| B29e | CS negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns     |

| B29f | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                      | 5.00  | _     | 9.00  | _     | 7.00  | _     | 0.375 | 50.00              | ns     |

| B29g | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1  | 5.00  | _     | 9.00  | _     | 7.00  | _     | 0.375 | 50.00              | ns     |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nive | Chavastavistis                                                                                                                                                                | 50 I  | ИНz | 66 1  | ИHz | 80 1  | ИНz | FEACT | Cap Load           | Hali |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|-------|-----|-------|--------------------|------|

| Num  | Characteristic                                                                                                                                                                | Min   | Max | Min   | Max | Min   | Max | FFACT | (default<br>50 pF) | Unit |

| B29h | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                            | 25.00 | _   | 39.00 | _   | 31.00 | _   | 1.375 | 50.00              | ns   |

| B29i | CS negated to D[0-31], DP[0-3] high-Z GPCM write access, TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF =                                                                     | 25.00 |     | 39.00 |     | 31.00 |     | 1.375 | 50.00              | ns   |

| B30  | CS, WE[0-3] negated to A[6-31] invalid GPCM write access 9                                                                                                                    | 3.00  | _   | 6.00  | _   | 4.00  | _   | 0.250 | 50.00              | ns   |

| B30a | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1, CS negated to A[6-31] invalid GPCM write access TRLX = 0, CSNT =1, ACS = 10 or ACS = 11, EBDF = 0   | 8.00  | _   | 13.00 | _   | 11.00 | _   | 0.500 | 50.00              | ns   |

| B30b | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A[6-31] Invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 0  | 28.00 |     | 43.00 | _   | 36.00 | _   | 1.500 | 50.00              | ns   |

| B30c | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1. CS negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 1 | 5.00  | ı   | 8.00  | 1   | 6.00  | 1   | 0.375 | 50.00              | ns   |

| B30d | WE[0-3] negated to A[6-31] invalid GPCM write access TRLX = 1, CSNT =1, CS negated to A[6-31] invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 1    | 25.00 |     | 39.00 | _   | 31.00 | _   | 1.375 | 50.00              | ns   |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nivee | Characteristic                                                                                                                       | 50 I  | ИНz   | 66 N  | ИHz   | 80 1  | MHz   | EEAOT | Cap Load           | Unit  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|-------|

| Num   | Characteristic                                                                                                                       | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Oiiit |

| B33a  | CLKOUT rising edge to GPL valid - as requested by control bit GxT3 in the corresponding word in the UPM                              | 5.00  | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250 | 50.00              | ns    |

| B34   | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid<br>- as requested by control bit<br>CST4 in the corresponding<br>word in the UPM | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns    |

| B34a  | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid - as requested by control bit CST1 in the corresponding word in the UPM          | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns    |

| B34b  | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid - as requested by CST2 in the corresponding word in UPM                          | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750 | 50.00              | ns    |

| B35   | A[6–31] to CS valid - as requested by control bit BST4 in the corresponding word in UPM                                              | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns    |

| B35a  | A[6–31] and D[0–31] to $\overline{BS}$ valid - as requested by BST1 in the corresponding word in the UPM                             | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns    |

| B35b  | A[6–31] and D[0–31] to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM                     | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750 | 50.00              | ns    |

| B36   | A[6–31] and D[0–31] to GPL valid - as requested by control bit GxT4 in the corresponding word in the UPM                             | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns    |

| B37   | UPWAIT valid to CLKOUT falling edge 10                                                                                               | 6.00  | _     | 6.00  | _     | 6.00  | _     | _     | 50.00              | ns    |

| B38   | CLKOUT falling edge to UPWAIT valid <sup>10</sup>                                                                                    | 1.00  | _     | 1.00  | _     | 1.00  | _     | _     | 50.00              | ns    |

| B39   | AS valid to CLKOUT rising edge                                                                                                       | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns    |

| B40   | A[6–31], TSIZ[0–1], RD/WR,<br>BURST, valid to CLKOUT rising<br>edge.                                                                 | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns    |

| B41   | TS valid to CLKOUT rising edge (setup time)                                                                                          | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns    |

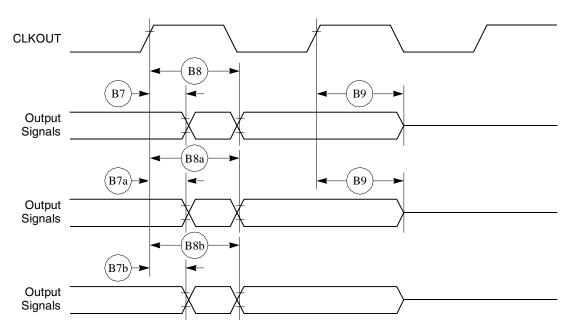

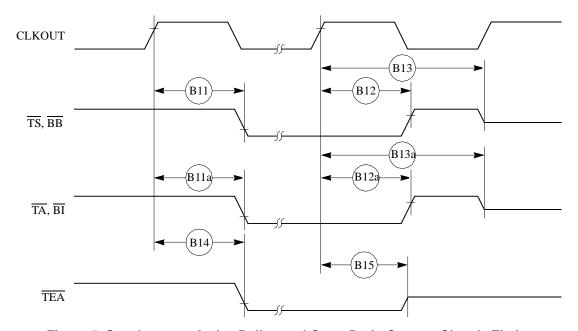

Figure 4 provides the timing for the synchronous output signals.

Figure 4. Synchronous Output Signals Timing

Figure 5 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 5. Synchronous Active Pullup and Open-Drain Outputs Signals Timing

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

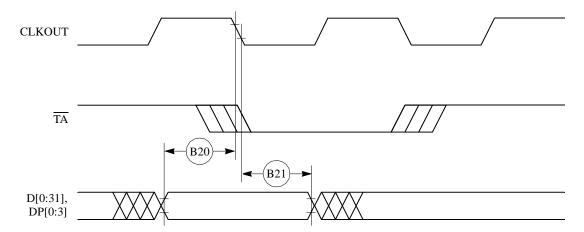

Figure 8 provides the timing for the input data controlled by the UPM in the memory controller.

Figure 8. Input Data Timing when Controlled by UPM in the Memory Controller

Figure 9 through Figure 12 provide the timing for the external bus read controlled by various GPCM factors.

Figure 9. External Bus Read Timing (GPCM Controlled—ACS = 00)

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

# Table 8 shows the PCMCIA timing for the MPC850.

# **Table 8. PCMCIA Timing**

| Num | Characteristic                                  | 501   | ЛНz   | 661   | ЛHz   | 80 1  | ИНz   | FFACTOR | Unit  |

|-----|-------------------------------------------------|-------|-------|-------|-------|-------|-------|---------|-------|

| Num | Cital acteristic                                | Min   | Max   | Min   | Max   | Min   | Max   | FFACTOR | Oiiit |

| P44 | A[6–31], REG valid to PCMCIA strobe asserted. 1 | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750   | ns    |

| P45 | A[6–31], REG valid to ALE negation.1            | 18.00 | _     | 28.00 | _     | 23.00 | _     | 1.000   | ns    |

| P46 | CLKOUT to REG valid                             | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P47 | CLKOUT to REG Invalid.                          | 6.00  | _     | 9.00  | _     | 7.00  | _     | 0.250   | ns    |

| P48 | CLKOUT to CE1, CE2 asserted.                    | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   |       |

| P49 | CLKOUT to CE1, CE2 negated.                     | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P50 | CLKOUT to PCOE, IORD, PCWE, IOWR assert time.   | _     | 11.00 | _     | 11.00 | _     | 11.00 | _       | ns    |

| P51 | CLKOUT to PCOE, IORD, PCWE, IOWR negate time.   | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | _       | ns    |

| P52 | CLKOUT to ALE assert time                       | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P53 | CLKOUT to ALE negate time                       | _     | 13.00 | _     | 16.00 | _     | 14.00 | 0.250   | ns    |

| P54 | PCWE, IOWR negated to D[0–31] invalid.1         | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250   | ns    |

| P55 | WAIT_B valid to CLKOUT rising edge.1            | 8.00  | _     | 8.00  | _     | 8.00  | _     | _       | ns    |

| P56 | CLKOUT rising edge to WAIT_B invalid.1          | 2.00  | _     | 2.00  | _     | 2.00  | _     | _       | ns    |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

These synchronous timings define when the WAIT\_B signal is detected in order to freeze (or relieve) the PCMCIA current cycle. The WAIT\_B assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See PCMCIA Interface in the MPC850 PowerQUICC User's Manual.

PSHT = 0. Otherwise add PSHT times cycle time.

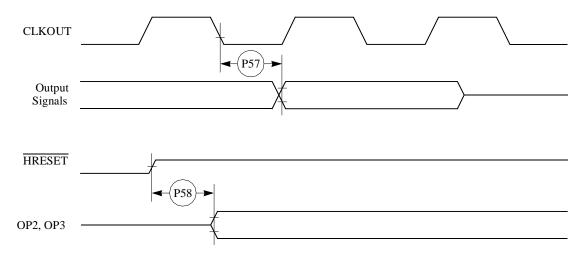

Table 9 shows the PCMCIA port timing for the MPC850.

**Table 9. PCMCIA Port Timing**

| Num | Characteristic                           | 50 MHz |       | 66 MHz |       | 80 MHz |       | Unit  |

|-----|------------------------------------------|--------|-------|--------|-------|--------|-------|-------|

| Num | Gilai acteristic                         | Min    | Max   | Min    | Max   | Min    | Max   | Oiiit |

| P57 | CLKOUT to OPx valid                      | _      | 19.00 | _      | 19.00 | _      | 19.00 | ns    |

| P58 | HRESET negated to OPx drive <sup>1</sup> | 18.00  | _     | 26.00  | _     | 22.00  | _     | ns    |

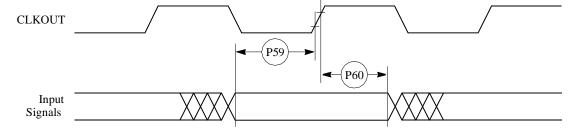

| P59 | IP_Xx valid to CLKOUT rising edge        | 5.00   | _     | 5.00   | _     | 5.00   | _     | ns    |

| P60 | CLKOUT rising edge to IP_Xx invalid      | 1.00   | _     | 1.00   | _     | 1.00   | _     | ns    |

OP2 and OP3 only.

Figure 27 provides the PCMCIA output port timing for the MPC850.

Figure 27. PCMCIA Output Port Timing

Figure 28 provides the PCMCIA output port timing for the MPC850.

Figure 28. PCMCIA Input Port Timing

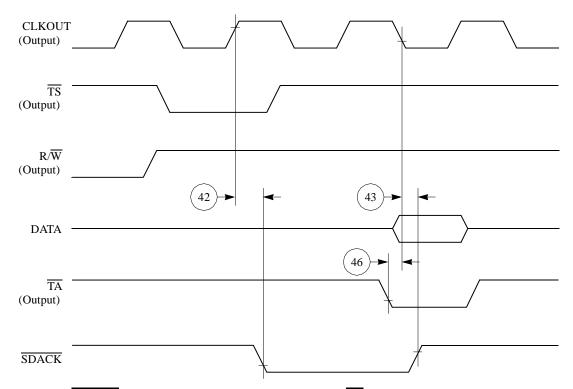

Figure 40. SDACK Timing Diagram—Peripheral Write, TA Sampled Low at the Falling Edge of the Clock

| Num   | Characteristic                                                       | All Free | quencies              | Unit   |  |

|-------|----------------------------------------------------------------------|----------|-----------------------|--------|--|

| Nulli | Characteristic                                                       | Min      | Max                   |        |  |

| 82    | L1RCLK, L1TCLK frequency (DSC =1)                                    | _        | 16.00 or<br>SYNCCLK/2 | MHz    |  |

| 83    | L1RCLK, L1TCLK width low (DSC =1)                                    | P + 10   | _                     | ns     |  |

| 83A   | L1RCLK, L1TCLK width high (DSC = 1) <sup>3</sup>                     | P + 10   | _                     | ns     |  |

| 84    | L1CLK edge to L1CLKO valid (DSC = 1)                                 | _        | 30.00                 | ns     |  |

| 85    | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>               | 1.00     | _                     | L1TCLK |  |

| 86    | L1GR setup time <sup>2</sup>                                         | 42.00    | _                     | ns     |  |

| 87    | L1GR hold time                                                       | 42.00    | _                     | ns     |  |

| 88    | L1xCLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00                  | ns     |  |

<sup>&</sup>lt;sup>1</sup> The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

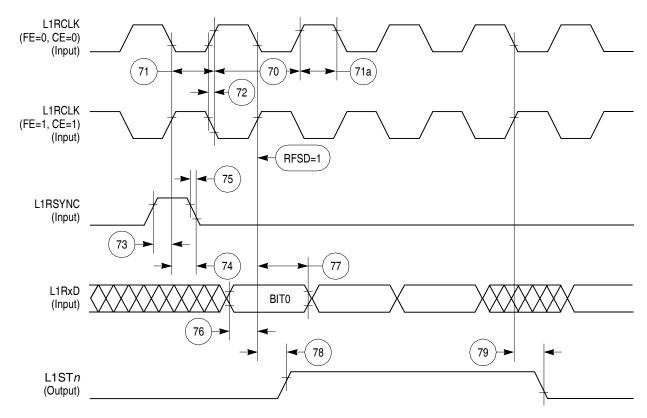

Figure 45. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

<sup>&</sup>lt;sup>2</sup> These specs are valid for IDL mode only.

$<sup>^{3}</sup>$  Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

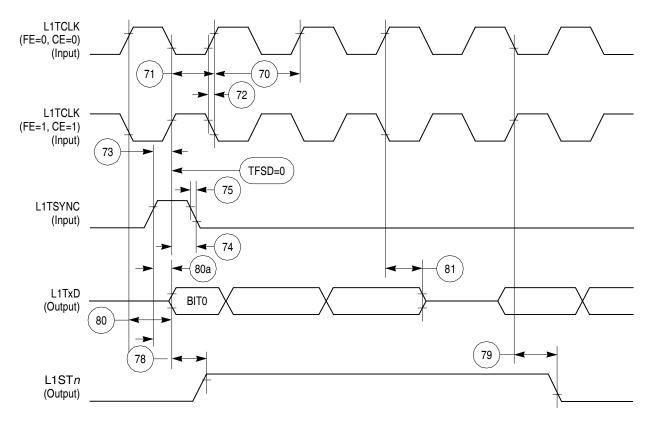

Figure 47. SI Transmit Timing Diagram

**CPM Electrical Characteristics**

# 8.6 SCC in NMSI Mode Electrical Specifications

Table 18 provides the NMSI external clock timing.

**Table 18. NMSI External Clock Timing**

| Num | Chavastavistis                                                        | All Frequencies |       | Unit |

|-----|-----------------------------------------------------------------------|-----------------|-------|------|

| Num | Characteristic                                                        | Min             | Max   | Unit |

| 100 | RCLKx and TCLKx frequency $^1$ (x = 2, 3 for all specs in this table) | 1/SYNCCLK       | _     | ns   |

| 101 | RCLKx and TCLKx width low                                             | 1/SYNCCLK +5    | _     | ns   |

| 102 | RCLKx and TCLKx rise/fall time                                        | _               | 15.00 | ns   |

| 103 | TXDx active delay (from TCLKx falling edge)                           | 0.00            | 50.00 | ns   |

| 104 | RTSx active/inactive delay (from TCLKx falling edge)                  | 0.00            | 50.00 | ns   |

| 105 | CTSx setup time to TCLKx rising edge                                  | 5.00            | _     | ns   |

| 106 | RXDx setup time to RCLKx rising edge                                  | 5.00            | _     | ns   |

| 107 | RXDx hold time from RCLKx rising edge <sup>2</sup>                    | 5.00            | _     | ns   |

| 108 | CDx setup time to RCLKx rising edge                                   | 5.00            | _     | ns   |

<sup>&</sup>lt;sup>1</sup> The ratios SyncCLK/RCLKx and SyncCLK/TCLKx must be greater than or equal to 2.25/1.

Table 19 provides the NMSI internal clock timing.

**Table 19. NMSI Internal Clock Timing**

| Num | Characteristic                                                        | All Frequencies |           | I I m i t |

|-----|-----------------------------------------------------------------------|-----------------|-----------|-----------|

|     |                                                                       | Min             | Max       | Unit      |

| 100 | RCLKx and TCLKx frequency $^1$ (x = 2, 3 for all specs in this table) | 0.00            | SYNCCLK/3 | MHz       |

| 102 | RCLKx and TCLKx rise/fall time                                        | _               | _         | ns        |

| 103 | TXDx active delay (from TCLKx falling edge)                           | 0.00            | 30.00     | ns        |

| 104 | RTSx active/inactive delay (from TCLKx falling edge)                  | 0.00            | 30.00     | ns        |

| 105 | CTSx setup time to TCLKx rising edge                                  | 40.00           | _         | ns        |

| 106 | RXDx setup time to RCLKx rising edge                                  | 40.00           | _         | ns        |

| 107 | RXDx hold time from RCLKx rising edge <sup>2</sup>                    | 0.00            | _         | ns        |

| 108 | CDx setup time to RCLKx rising edge                                   | 40.00           | _         | ns        |

The ratios SyncCLK/RCLKx and SyncCLK/TCLK1x must be greater or equal to 3/1.

<sup>&</sup>lt;sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

<sup>&</sup>lt;sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

| Table 20   | <b>Ethernet</b> | Timing (   | (continued)                |

|------------|-----------------|------------|----------------------------|

| I abic 20. |                 | I IIIIIIII | (COIILIIIA <del>C</del> A) |

| Num | Characteristic                               | All Frequencies |       | Unit  |

|-----|----------------------------------------------|-----------------|-------|-------|

|     |                                              | Min             | Max   | Oille |

| 134 | TENA inactive delay (from TCLKx rising edge) | 10.00           | 50.00 | ns    |

| 138 | CLKOUT low to SDACK asserted <sup>2</sup>    | _               | 20.00 | ns    |

| 139 | CLKOUT low to SDACK negated <sup>2</sup>     | _               | 20.00 | ns    |

<sup>&</sup>lt;sup>1</sup> The ratios SyncCLK/RCLKx and SyncCLK/TCLKx must be greater or equal to 2/1.

<sup>&</sup>lt;sup>2</sup> SDACK is asserted whenever the SDMA writes the incoming frame destination address into memory.

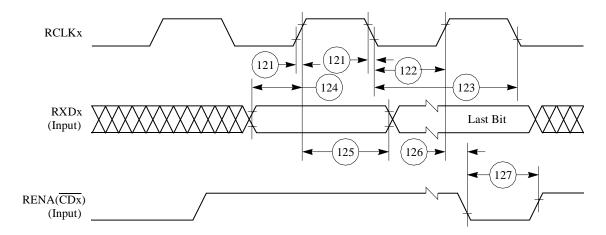

Figure 53. Ethernet Collision Timing Diagram

Figure 54. Ethernet Receive Timing Diagram

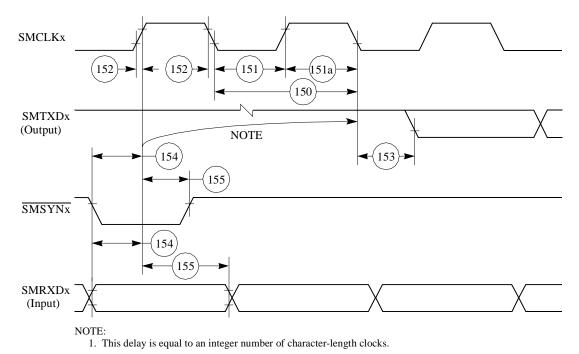

Figure 56. SMC Transparent Timing Diagram

# 8.9 SPI Master AC Electrical Specifications

Table 22 provides the SPI master timings as shown in Figure 57 and Figure 58.

**All Frequencies** Characteristic Unit Num Min Max 160 MASTER cycle time 4 1024 t<sub>cyc</sub> 161 MASTER clock (SCK) high or low time 2 512 t<sub>cyc</sub> 162 MASTER data setup time (inputs) 50.00 ns 163 Master data hold time (inputs) 0.00 ns 164 Master data valid (after SCK edge) 20.00 ns 165 Master data hold time (outputs) 0.00 ns 15.00 166 Rise time output ns 167 Fall time output 15.00 ns

Table 22. SPI Master Timing

### **Mechanical Data and Ordering Information**

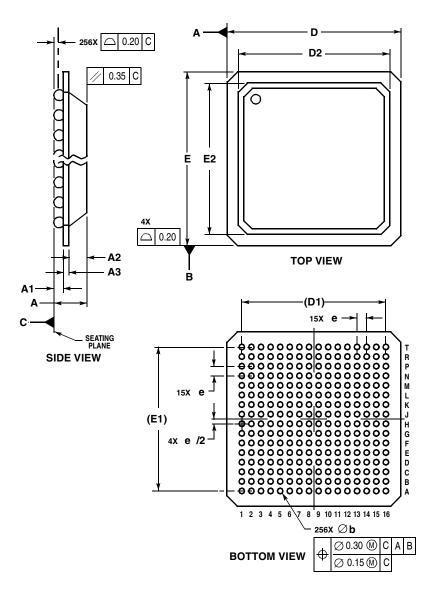

Figure 64 shows the non-JEDEC package dimensions of the PBGA.

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. DIMENSIONS IN MILLIMETERS.

- DIMENSION 6 IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C.

- 4. PRIMARY DATUM C AND THE SEATING PLANE ARE

|            | MILLIMETERS |       |  |

|------------|-------------|-------|--|

| DIM        | MIN         | MAX   |  |

| Α          | 1.91        | 2.35  |  |

| <b>A</b> 1 | 0.50        | 0.70  |  |

| A2         | 1.12        | 1.22  |  |

| A3         | 0.29        | 0.43  |  |

| b          | 0.60        | 0.90  |  |

| D          | 23.00 BSC   |       |  |

| D1         | 19.05 REF   |       |  |

| D2         | 19.00       | 20.00 |  |

| Е          | 23.00 BSC   |       |  |

| E1         | 19.05 REF   |       |  |

| E2         | 19.00       | 20.00 |  |

| е          | 1.27        | BSC   |  |

Figure 64. Package Dimensions for the Plastic Ball Grid Array (PBGA)—non-JEDEC Standard

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

# THIS PAGE INTENTIONALLY LEFT BLANK

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2