# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 80MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | · ·                                                                    |

| Ethernet                        | 10Mbps (1)                                                             |

| SATA                            | -                                                                      |

| USB                             | USB 1.x (1)                                                            |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 256-BBGA                                                               |

| Supplier Device Package         | 256-PBGA (23x23)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc850srzq80bu |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- 2-Kbyte instruction cache and 1-Kbyte data cache (Harvard architecture)

- Caches are two-way, set-associative

- Physically addressed

- Cache blocks can be updated with a 4-word line burst

- Least-recently used (LRU) replacement algorithm

- Lockable one-line granularity

- Memory management units (MMUs) with 8-entry translation lookaside buffers (TLBs) and fully-associative instruction and data TLBs

- MMUs support multiple page sizes of 4 Kbytes, 16 Kbytes, 256 Kbytes, 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and eight protection groups

- Advanced on-chip emulation debug mode

- Data bus dynamic bus sizing for 8, 16, and 32-bit buses

- Supports traditional 68000 big-endian, traditional x86 little-endian and modified little-endian memory systems

- Twenty-six external address lines

- Completely static design (0–80 MHz operation)

- System integration unit (SIU)

- Hardware bus monitor

- Spurious interrupt monitor

- Software watchdog

- Periodic interrupt timer

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Memory controller (eight banks)

- Glueless interface to DRAM single in-line memory modules (SIMMs), synchronous DRAM (SDRAM), static random-access memory (SRAM), electrically programmable read-only memory (EPROM), flash EPROM, etc.

- Memory controller programmable to support most size and speed memory interfaces

- Boot chip-select available at reset (options for 8, 16, or 32-bit memory)

- Variable block sizes, 32 Kbytes to 256 Mbytes

- Selectable write protection

- On-chip bus arbiter supports one external bus master

- Special features for burst mode support

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

Features

- QUICC multichannel controller (QMC) microcode features

- Up to 64 independent communication channels on a single SCC

- Arbitrary mapping of 0–31 channels to any of 0–31 TDM time slots

- Supports either transparent or HDLC protocols for each channel

- Independent TxBDs/Rx and event/interrupt reporting for each channel

- One universal serial bus controller (USB)

- Supports host controller and slave modes at 1.5 Mbps and 12 Mbps

- Two serial management controllers (SMCs)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division-multiplexed (TDM) channel

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C<sup>®</sup> (interprocessor-integrated circuit) port

- Supports master and slave modes

- Supports multimaster environment

- Time slot assigner

- Allows SCCs and SMCs to run in multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame syncs, clocking

- Allows dynamic changes

- Can be internally connected to four serial channels (two SCCs and two SMCs)

- Low-power support

- Full high: all units fully powered at high clock frequency

- Full low: all units fully powered at low clock frequency

- Doze: core functional units disabled except time base, decrementer, PLL, memory controller, real-time clock, and CPM in low-power standby

- Sleep: all units disabled except real-time clock and periodic interrupt timer. PLL is active for fast wake-up

- Deep sleep: all units disabled including PLL, except the real-time clock and periodic interrupt timer

- Low-power stop: to provide lower power dissipation

### Bus Signal Timing

$\theta_{IA}$  = Package thermal resistance, junction to ambient, °C/W

$\begin{aligned} \mathbf{P}_{\mathrm{D}} &= \mathbf{P}_{\mathrm{INT}} + \mathbf{P}_{\mathrm{I/O}} \\ \mathbf{P}_{\mathrm{INT}} &= \mathbf{I}_{\mathrm{DD}} \ge \mathbf{V}_{\mathrm{DD}}, \text{watts}\text{---chip internal power} \end{aligned}$

$P_{I/O}$  = Power dissipation on input and output pins—user determined

For most applications  $P_{I/O} < 0.3 \bullet P_{INT}$  and can be neglected. If  $P_{I/O}$  is neglected, an approximate relationship between  $P_D$  and  $T_I$  is:

$P_{\rm D} = K \div (T_{\rm I} + 273^{\circ} \rm C)(2)$

Solving equations (1) and (2) for K gives:

$\mathbf{K} = \mathbf{P}_{\mathrm{D}} \bullet (\mathbf{T}_{\mathrm{A}} + 273^{\circ}\mathrm{C}) + \mathbf{\theta}_{\mathrm{JA}} \bullet \mathbf{P}_{\mathrm{D}}^{2}(3)$

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

## 5.1 Layout Practices

Each  $V_{CC}$  pin on the MPC850 should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{CC}$  power supply should be bypassed to ground using at least four 0.1 µF by-pass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{CC}$  and GND should be kept to less than half an inch per capacitor lead. A four-layer board is recommended, employing two inner layers as  $V_{CC}$  and GND planes.

All output pins on the MPC850 have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data busses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

# 6 Bus Signal Timing

Table 6 provides the bus operation timing for the MPC850 at 50 MHz, 66 MHz, and 80 MHz. Timing information for other bus speeds can be interpolated by equation using the MPC850 Electrical Specifications Spreadsheet found at http://www.mot.com/netcomm.

The maximum bus speed supported by the MPC850 is 50 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC850 used at 66 MHz must be configured for a 33 MHz bus).

The timing for the MPC850 bus shown assumes a 50-pF load. This timing can be derated by 1 ns per 10 pF. Derating calculations can also be performed using the MPC850 Electrical Specifications Spreadsheet.

**Bus Signal Timing**

|      | Characteristic                                                                                                                          | 50 MHz 66 MHz |       |       | 80 1  | MHz   |       | Cap Load |                    |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|----------|--------------------|------|

| Num  |                                                                                                                                         | Min           | Max   | Min   | Max   | Min   | Max   | FFACT    | (default<br>50 pF) | Unit |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid - as requested by control bit CST4 in the corresponding word in the UPM                    | 1.50          | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | _        | 50.00              | ns   |

| B31a | CLKOUT falling edge to $\overline{CS}$<br>valid - as requested by control<br>bit CST1 in the corresponding<br>word in the UPM           | 5.00          | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250    | 50.00              | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid<br>- as requested by control bit<br>CST2 in the corresponding<br>word in the UPM            | 1.50          | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | _        | 50.00              | ns   |

| B31c | CLKOUT rising edge to CS valid<br>- as requested by control bit<br>CST3 in the corresponding<br>word in the UPM                         | 5.00          | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250    | 50.00              | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$<br>valid - as requested by control<br>bit CST1 in the corresponding<br>word in the UPM EBDF = 1  | 9.00          | 14.00 | 13.00 | 18.00 | 11.00 | 16.00 | 0.375    | 50.00              | ns   |

| B32  | CLKOUT falling edge to $\overline{\text{BS}}$<br>valid - as requested by control<br>bit BST4 in the corresponding<br>word in the UPM    | 1.50          | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | _        | 50.00              | ns   |

| B32a | CLKOUT falling edge to $\overline{BS}$<br>valid - as requested by control<br>bit BST1 in the corresponding<br>word in the UPM, EBDF = 0 | 5.00          | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250    | 50.00              | ns   |

| B32b | CLKOUT rising edge to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM                         | 1.50          | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | —        | 50.00              | ns   |

| B32c | CLKOUT rising edge to BS valid<br>- as requested by control bit<br>BST3 in the corresponding<br>word in the UPM                         | 5.00          | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250    | 50.00              | ns   |

| B32d | CLKOUT falling edge to $\overline{BS}$<br>valid - as requested by control<br>bit BST1 in the corresponding<br>word in the UPM, EBDF = 1 | 9.00          | 14.00 | 13.00 | 18.00 | 11.00 | 16.00 | 0.375    | 50.00              | ns   |

| B33  | CLKOUT falling edge to GPL<br>valid - as requested by control<br>bit GxT4 in the corresponding<br>word in the UPM                       | 1.50          | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  |          | 50.00              | ns   |

| Table 6. | <b>Bus Operation</b> | Timing | <sup>1</sup> (continued) |

|----------|----------------------|--------|--------------------------|

|----------|----------------------|--------|--------------------------|

| Num | Characteristic                                          | 50 MHz |     | 66 MHz |     | 80 MHz |     | FFACT | Cap Load<br>(default | Unit |

|-----|---------------------------------------------------------|--------|-----|--------|-----|--------|-----|-------|----------------------|------|

|     | Unaracteristic                                          | Min    | Max | Min    | Max | Min    | Max | ITACI | 50 pF)               | omit |

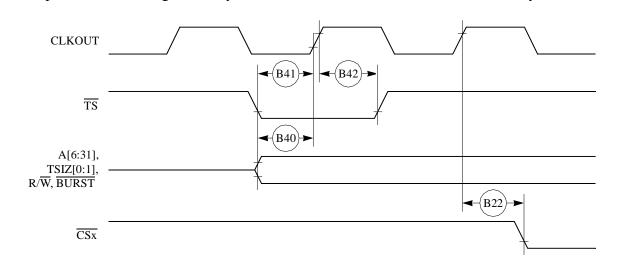

| B42 | CLKOUT rising edge to $\overline{TS}$ valid (hold time) | 2.00   | _   | 2.00   | _   | 2.00   | _   | —     | 50.00                | ns   |

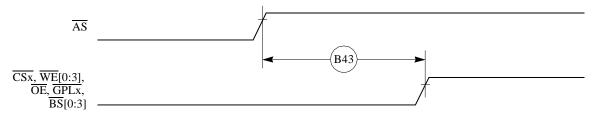

| B43 | AS negation to memory controller signals negation       | _      | TBD | _      | TBD | TBD    | _   | —     | 50.00                | ns   |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

The minima provided assume a 0 pF load, whereas maxima assume a 50pF load. For frequencies not marked on the part, new bus timing must be calculated for all frequency-dependent AC parameters. Frequency-dependent AC parameters are those with an entry in the FFactor column. AC parameters without an FFactor entry do not need to be calculated and can be taken directly from the frequency column corresponding to the frequency marked on the part. The following equations should be used in these calculations.

For a frequency F, the following equations should be applied to each one of the above parameters: For minima:

$$D = \frac{FFACTOR \times 1000}{F} + (D_{50} - 20 \times FFACTOR)$$

For maxima:

$$D = \frac{FFACTOR \times 1000}{F} + \frac{(D_{50} - 20 \times FFACTOR)}{F} + \frac{1 ns(CAP \ LOAD - 50) / 10}{F}$$

where:

D is the parameter value to the frequency required in ns

F is the operation frequency in MHz

D<sub>50</sub> is the parameter value defined for 50 MHz

CAP LOAD is the capacitance load on the signal in question.

FFACTOR is the one defined for each of the parameters in the table.

- <sup>2</sup> Phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed value.

- <sup>3</sup> If the rate of change of the frequency of EXTAL is slow (i.e. it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (i.e., it does not stay at an extreme value for a long time) then the maximum allowed jitter on EXTAL can be up to 2%.

- <sup>4</sup> The timing for BR output is relevant when the MPC850 is selected to work with external bus arbiter. The timing for BG output is relevant when the MPC850 is selected to work with internal bus arbiter.

- <sup>5</sup> The setup times required for TA, TEA, and BI are relevant only when they are supplied by an external device (and not when the memory controller or the PCMCIA interface drives them).

- <sup>6</sup> The timing required for BR input is relevant when the MPC850 is selected to work with the internal bus arbiter. The timing for BG input is relevant when the MPC850 is selected to work with the external bus arbiter.

- <sup>7</sup> The D[0–31] and DP[0–3] input timings B20 and B21 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

- <sup>8</sup> The D[0:31] and DP[0:3] input timings B20 and B21 refer to the falling edge of CLKOUT. This timing is valid only for read accesses controlled by chip-selects controlled by the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.

- <sup>9</sup> The timing B30 refers to  $\overline{CS}$  when ACS = '00' and to  $\overline{WE[0:3]}$  when CSNT = '0'.

- <sup>10</sup> The signal UPWAIT is considered asynchronous to CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals.

- <sup>11</sup> The  $\overline{\text{AS}}$  signal is considered asynchronous to CLKOUT.

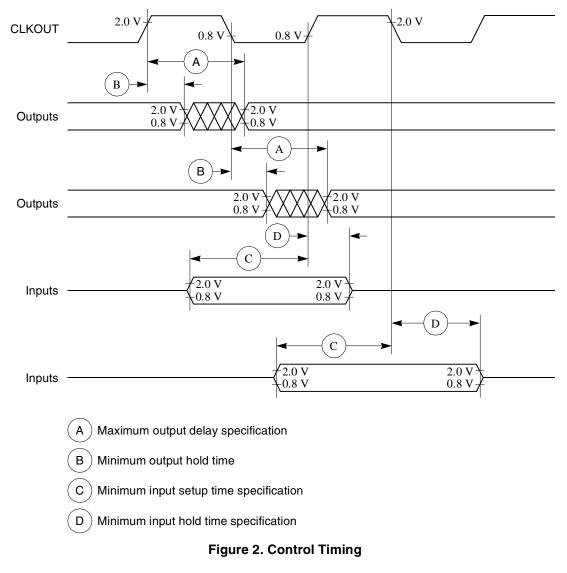

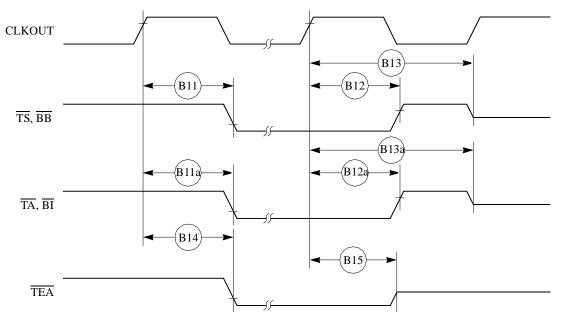

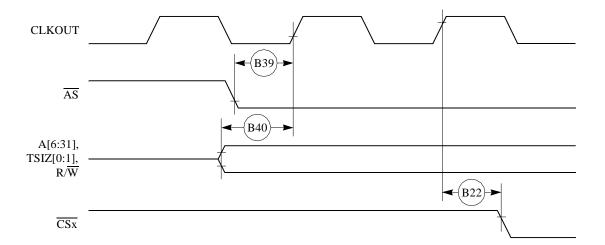

Figure 2 is the control timing diagram.

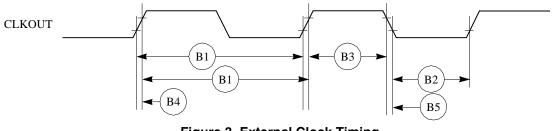

Figure 3 provides the timing for the external clock.

Figure 3. External Clock Timing

**Bus Signal Timing**

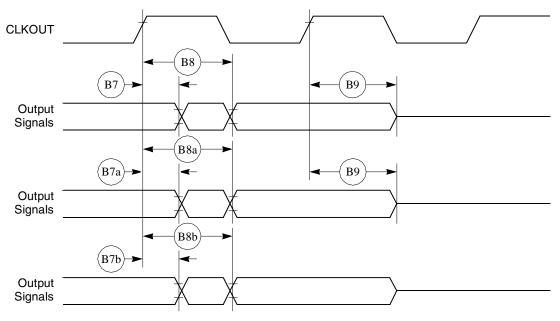

Figure 4 provides the timing for the synchronous output signals.

Figure 4. Synchronous Output Signals Timing

Figure 5 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 5. Synchronous Active Pullup and Open-Drain Outputs Signals Timing

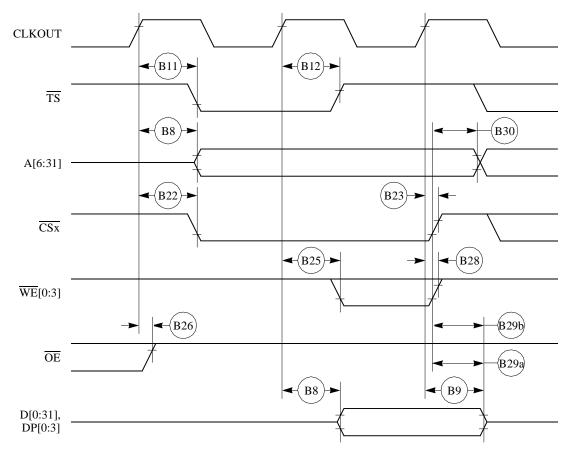

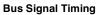

Figure 13 through Figure 15 provide the timing for the external bus write controlled by various GPCM factors.

Figure 13. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 1, CSNT = 1)

**Bus Signal Timing**

Figure 19 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 19. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 20 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 21 provides the timing for the asynchronous external master control signals negation.

Figure 21. Asynchronous External Master—Control Signals Negation Timing

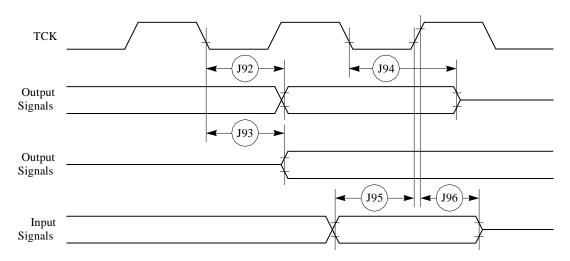

Figure 37. Boundary Scan (JTAG) Timing Diagram

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC850.

# 8.1 PIO AC Electrical Specifications

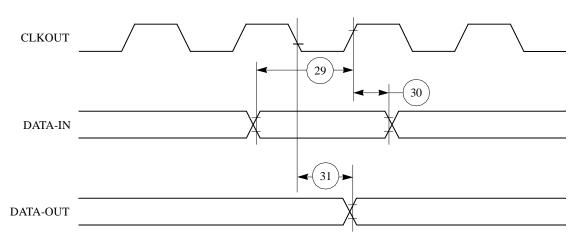

Table 13 provides the parallel I/O timings for the MPC850 as shown in Figure 38.

### Table 13. Parallel I/O Timing

| Num | Characteristic                                                       | All Freque | Unit |      |

|-----|----------------------------------------------------------------------|------------|------|------|

| Num | Characteristic                                                       | Min        | Max  | Unit |

| 29  | Data-in setup time to clock high                                     | 15         | _    | ns   |

| 30  | Data-in hold time from clock high                                    | 7.5        | _    | ns   |

| 31  | Clock low to data-out valid (CPU writes data, control, or direction) | -          | 25   | ns   |

Figure 38. Parallel I/O Data-In/Data-Out Timing Diagram

# 8.2 IDMA Controller AC Electrical Specifications

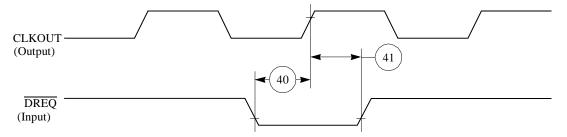

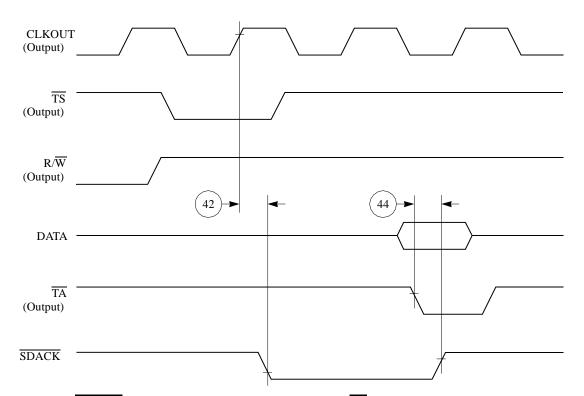

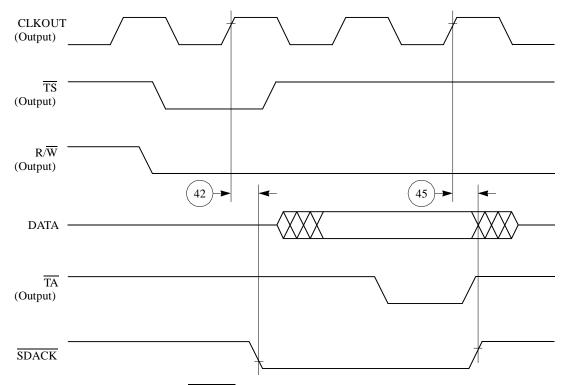

Table 14 provides the IDMA controller timings as shown in Figure 39 to Figure 42.

| Num | Characteristic                                                                                           |      | All Frequencies |      |  |

|-----|----------------------------------------------------------------------------------------------------------|------|-----------------|------|--|

| Num | Characteristic                                                                                           | Min  | Max             | Unit |  |

| 40  | DREQ setup time to clock high                                                                            | 7.00 | _               | ns   |  |

| 41  | DREQ hold time from clock high                                                                           | 3.00 | _               | ns   |  |

| 42  | SDACK assertion delay from clock high                                                                    | _    | 12.00           | ns   |  |

| 43  | SDACK negation delay from clock low                                                                      | _    | 12.00           | ns   |  |

| 44  | SDACK negation delay from TA low                                                                         | _    | 20.00           | ns   |  |

| 45  | SDACK negation delay from clock high                                                                     | _    | 15.00           | ns   |  |

| 46  | $\overline{TA}$ assertion to falling edge of the clock setup time (applies to external $\overline{TA}$ ) | 7.00 |                 | ns   |  |

### Table 14. IDMA Controller Timing

Figure 39. IDMA External Requests Timing Diagram

Figure 41. SDACK Timing Diagram—Peripheral Write, TA Sampled High at the Falling Edge of the Clock

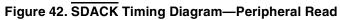

|           |                                                                         |        | СРМ                   | Electrical Ch |

|-----------|-------------------------------------------------------------------------|--------|-----------------------|---------------|

|           | Table 17. SI Timing (cont                                               | inued) |                       |               |

| Num       | Characteristic                                                          |        | quencies              | Unit          |

| Num<br>82 | Cildracteristic                                                         | Min    | Мах                   | Unit          |

| 82        | L1RCLK, L1TCLK frequency (DSC =1)                                       | —      | 16.00 or<br>SYNCCLK/2 | MHz           |

| 83        | L1RCLK, L1TCLK width low (DSC =1)                                       | P + 10 | —                     | ns            |

| 83A       | L1RCLK, L1TCLK width high (DSC = $1$ ) <sup>3</sup>                     | P + 10 | —                     | ns            |

| 84        | L1CLK edge to L1CLKO valid (DSC = 1)                                    | —      | 30.00                 | ns            |

| 85        | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>                  | 1.00   | —                     | L1TCLK        |

| 86        | L1GR setup time <sup>2</sup>                                            | 42.00  | —                     | ns            |

| 87        | L1GR hold time                                                          | 42.00  | —                     | ns            |

| 88        | L1xCLK edge to L1SYNC valid (FSD = 00) CNT =<br>0000, BYT = 0, DSC = 0) | —      | 0.00                  | ns            |

1 The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

- 2 These specs are valid for IDL mode only.

- <sup>3</sup> Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

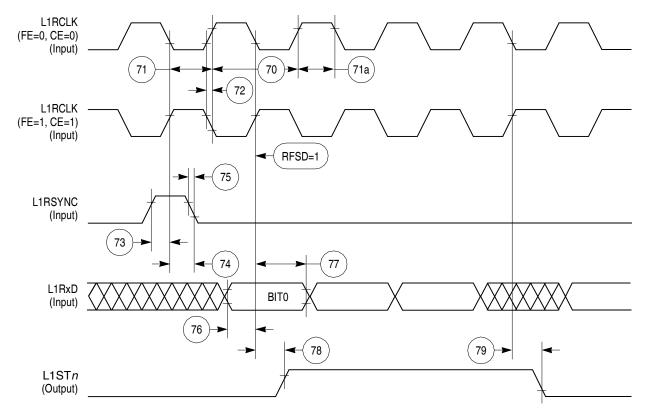

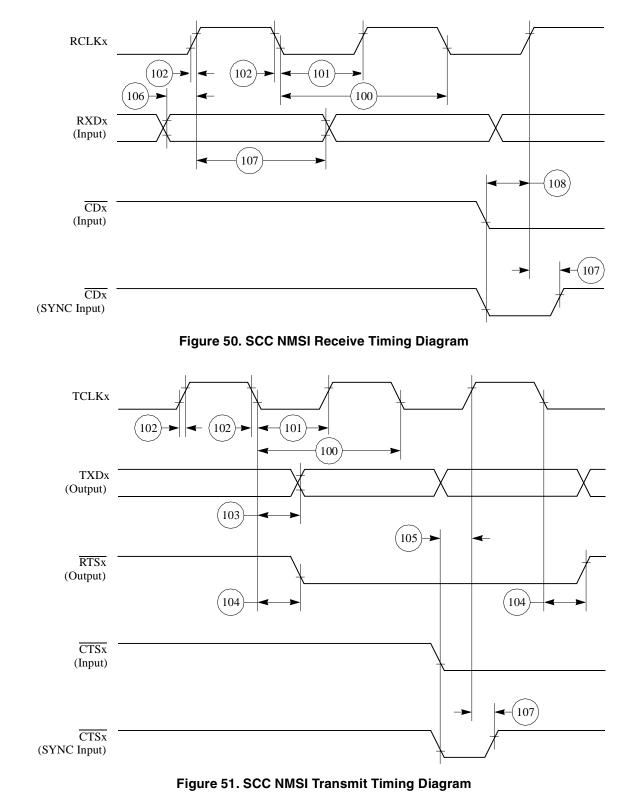

# 8.6 SCC in NMSI Mode Electrical Specifications

Table 18 provides the NMSI external clock timing.

| Num | Characteristic                                                          | All Frequencie | Unit  |     |

|-----|-------------------------------------------------------------------------|----------------|-------|-----|

| Num | onaracteristic                                                          | Min            | Max   | Ont |

| 100 | RCLKx and TCLKx frequency $^{1}$ (x = 2, 3 for all specs in this table) | 1/SYNCCLK      | -     | ns  |

| 101 | RCLKx and TCLKx width low                                               | 1/SYNCCLK +5   | _     | ns  |

| 102 | RCLKx and TCLKx rise/fall time                                          | _              | 15.00 | ns  |

| 103 | TXDx active delay (from TCLKx falling edge)                             | 0.00           | 50.00 | ns  |

| 104 | RTSx active/inactive delay (from TCLKx falling edge)                    | 0.00           | 50.00 | ns  |

| 105 | CTSx setup time to TCLKx rising edge                                    | 5.00           |       | ns  |

| 106 | RXDx setup time to RCLKx rising edge                                    | 5.00           | _     | ns  |

| 107 | RXDx hold time from RCLKx rising edge <sup>2</sup>                      | 5.00           | _     | ns  |

| 108 | CDx setup time to RCLKx rising edge                                     | 5.00           | _     | ns  |

<sup>1</sup> The ratios SyncCLK/RCLKx and SyncCLK/TCLKx must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Table 19 provides the NMSI internal clock timing.

Table 19. NMSI Internal Clock Timing

| Num   | Characteristic                                                          | All Fr | Unit      |      |

|-------|-------------------------------------------------------------------------|--------|-----------|------|

| Nulli | Characteristic                                                          | Min    | Мах       | Onit |

| 100   | RCLKx and TCLKx frequency $^{1}$ (x = 2, 3 for all specs in this table) | 0.00   | SYNCCLK/3 | MHz  |

| 102   | RCLKx and TCLKx rise/fall time                                          |        | —         | ns   |

| 103   | TXDx active delay (from TCLKx falling edge)                             | 0.00   | 30.00     | ns   |

| 104   | RTSx active/inactive delay (from TCLKx falling edge)                    | 0.00   | 30.00     | ns   |

| 105   | CTSx setup time to TCLKx rising edge                                    | 40.00  | —         | ns   |

| 106   | RXDx setup time to RCLKx rising edge                                    | 40.00  | —         | ns   |

| 107   | RXDx hold time from RCLKx rising edge <sup>2</sup>                      | 0.00   | —         | ns   |

| 108   | CDx setup time to RCLKx rising edge                                     | 40.00  | —         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLKx and SyncCLK/TCLK1x must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

**CPM Electrical Characteristics**

Figure 50 through Figure 52 show the NMSI timings.

| Num | Characteristic            | All Frequ | Unit   |      |

|-----|---------------------------|-----------|--------|------|

|     | onaracteristic            | Min       | Мах    | onne |

| 210 | SDL/SCL fall time         | _         | 300.00 | ns   |

| 211 | Stop condition setup time | 4.70      | _      | μs   |

Table 24. I<sup>2</sup>C Timing (SCL < 100 KHz) (CONTINUED)

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

Table 25 provides the  $I^2C$  (SCL > 100 KHz) timings.

Table 25.  $I^2C$  Timing (SCL > 100 KHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| Num | Undractensite                             | Expression | Min             | Max           | Unit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

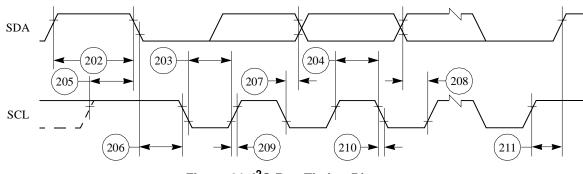

| 202 | Bus free time between transmissions       |            | 1/(2.2 * fSCL)  | —             | S    |

| 203 | Low period of SCL                         |            | 1/(2.2 * fSCL)  | —             | S    |

| 204 | High period of SCL                        |            | 1/(2.2 * fSCL)  | —             | s    |

| 205 | Start condition setup time                |            | 1/(2.2 * fSCL)  | _             | s    |

| 206 | Start condition hold time                 |            | 1/(2.2 * fSCL)  | _             | s    |

| 207 | Data hold time                            |            | 0               | —             | S    |

| 208 | Data setup time                           |            | 1/(40 * fSCL)   | —             | S    |

| 209 | SDL/SCL rise time                         |            | _               | 1/(10 * fSCL) | S    |

| 210 | SDL/SCL fall time                         |            | —               | 1/(33 * fSCL) | s    |

| 211 | Stop condition setup time                 |            | 1/2(2.2 * fSCL) | _             | S    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

Figure 61 shows the  $I^2C$  bus timing.

Figure 61. I<sup>2</sup>C Bus Timing Diagram

#### Mechanical Data and Ordering Information

customers that are currently using the non-JEDEC pin numbering scheme, two sets of pinouts, JEDEC and non-JEDEC, are presented in this document.

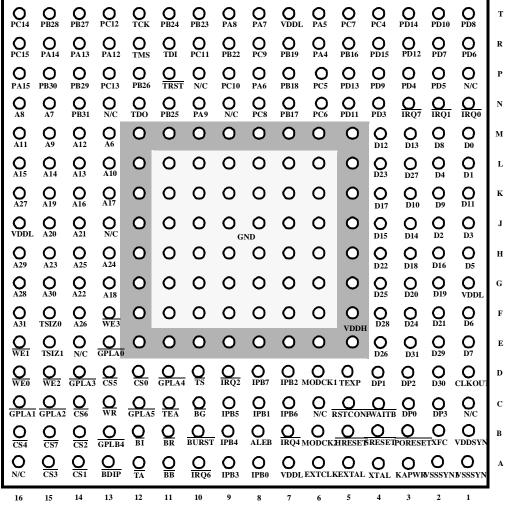

Figure 62 shows the non-JEDEC pinout of the PBGA package as viewed from the top surface.

Figure 62. Pin Assignments for the PBGA (Top View)—non-JEDEC Standard

### Mechanical Data and Ordering Information

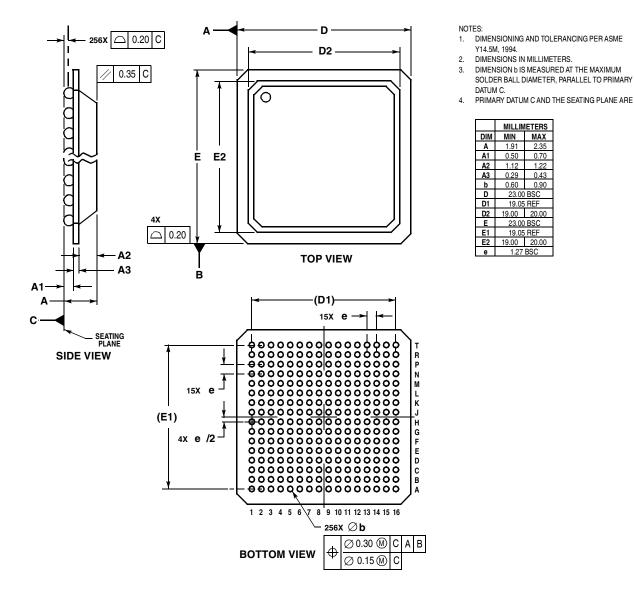

Figure 64 shows the non-JEDEC package dimensions of the PBGA.

Figure 64. Package Dimensions for the Plastic Ball Grid Array (PBGA)-non-JEDEC Standard

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK