# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 66MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                  |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10Mbps (1)                                                           |

| SATA                            | -                                                                    |

| USB                             | USB 1.x (1)                                                          |

| Voltage - I/O                   | 3.3V                                                                 |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                      |

| Security Features               | -                                                                    |

| Package / Case                  | 256-BBGA                                                             |

| Supplier Device Package         | 256-PBGA (23x23)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc850vr66bu |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Interrupt can be masked on reference match and event capture

- Interrupts

- Eight external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Fifteen internal interrupt sources

- Programmable priority among SCCs and USB

- Programmable highest-priority request

- Single socket PCMCIA-ATA interface

- Master (socket) interface, release 2.1 compliant

- Single PCMCIA socket

- Supports eight memory or I/O windows

- Communications processor module (CPM)

- 32-bit, Harvard architecture, scalar RISC communications processor (CP)

- Protocol-specific command sets (for example, GRACEFUL STOP TRANSMIT stops transmission after the current frame is finished or immediately if no frame is being sent and CLOSE RXBD closes the receive buffer descriptor)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- Twenty serial DMA (SDMA) channels for the serial controllers, including eight for the four USB endpoints

- Three parallel I/O registers with open-drain capability

- Four independent baud-rate generators (BRGs)

- Can be connected to any SCC, SMC, or USB

- Allow changes during operation

- Autobaud support option

- Two SCCs (serial communications controllers)

- Ethernet/IEEE 802.3, supporting full 10-Mbps operation

- HDLC/SDLC<sup>TM</sup> (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk<sup>®</sup>

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

- Separate power supply input to operate internal logic at 2.2 V when operating at or below 25 MHz

- Can be dynamically shifted between high frequency (3.3 V internal) and low frequency (2.2 V internal) operation

- Debug interface

(GND = 0V)

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- The MPC850 can compare using the =,  $\neq$ , <, and > conditions to generate watchpoints

- Each watchpoint can generate a breakpoint internally

- 3.3-V operation with 5-V TTL compatibility on all general purpose I/O pins.

## 3 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC850. Table 2 provides the maximum ratings.

| Rating                            | Symbol           | Value                                      | Unit |

|-----------------------------------|------------------|--------------------------------------------|------|

| Supply voltage                    | VDDH             | -0.3 to 4.0                                | V    |

|                                   | VDDL             | -0.3 to 4.0                                | V    |

|                                   | KAPWR            | -0.3 to 4.0                                | V    |

|                                   | VDDSYN           | -0.3 to 4.0                                | V    |

| Input voltage <sup>1</sup>        | V <sub>in</sub>  | GND-0.3 to VDDH + 2.5 V                    | V    |

| Junction temperature <sup>2</sup> | Тј               | 0 to 95 (standard)<br>-40 to 95 (extended) | °C   |

| Storage temperature range         | T <sub>stg</sub> | -55 to +150                                | °C   |

| Table 2. Maximum Ra |

|---------------------|

|---------------------|

<sup>1</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. CAUTION: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction

applies to power-up and normal operation (that is, if the MPC850 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>2</sup> The MPC850, a high-frequency device in a BGA package, does not provide a guaranteed maximum ambient temperature. Only maximum junction temperature is guaranteed. It is the responsibility of the user to consider power dissipation and thermal management. Junction temperature ratings are the same regardless of frequency rating of the device.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ). Table 3 provides the package thermal characteristics for the MPC850.

Thermal Characteristics

## 4 Thermal Characteristics

Table 3 shows the thermal characteristics for the MPC850.

**Table 3. Thermal Characteristics**

| Characteristic                                | Symbol          | Value           | Unit |

|-----------------------------------------------|-----------------|-----------------|------|

| Thermal resistance for BGA <sup>1</sup>       | θ <sub>JA</sub> | 40 <sup>2</sup> | °C/W |

|                                               | $\theta_{JA}$   | 31 <sup>3</sup> | °C/W |

|                                               | θ <sub>JA</sub> | 24 <sup>4</sup> | °C/W |

| Thermal Resistance for BGA (junction-to-case) | θJC             | 8               | °C/W |

<sup>1</sup> For more information on the design of thermal vias on multilayer boards and BGA layout considerations in general, refer to AN-1231/D, Plastic Ball Grid Array Application Note available from your local Freescale sales office.

<sup>2</sup> Assumes natural convection and a single layer board (no thermal vias).

<sup>3</sup> Assumes natural convection, a multilayer board with thermal vias<sup>4</sup>, 1 watt MPC850 dissipation, and a board temperature rise of 20°C above ambient.

<sup>4</sup> Assumes natural convection, a multilayer board with thermal vias<sup>4</sup>, 1 watt MPC850 dissipation, and a board temperature rise of 13°C above ambient.

$\begin{aligned} T_J &= T_A + (P_D \bullet \theta_{JA}) \\ P_D &= (V_{DD} \bullet I_{DD}) + P_{I/O} \\ \text{where:} \end{aligned}$

$P_{I/O}$  is the power dissipation on pins

Table 4 provides power dissipation information.

Table 4. Power Dissipation (P<sub>D</sub>)

| Characteristic              | Frequency (MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|-----------------------------|-----------------|----------------------|----------------------|------|

| Power Dissipation           | 33              | TBD                  | 515                  | mW   |

| All Revisions<br>(1:1) Mode | 40              | TBD                  | 590                  | mW   |

|                             | 50              | TBD                  | 725                  | mW   |

<sup>1</sup> Typical power dissipation is measured at 3.3V

<sup>2</sup> Maximum power dissipation is measured at 3.65 V

Table 5 provides the DC electrical characteristics for the MPC850.

## **Table 5. DC Electrical Specifications**

| Characteristic                                                                                | Symbol                       | Min   | Max   | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------|-------|-------|------|

| Operating voltage at 40 MHz or less                                                           | VDDH, VDDL,<br>KAPWR, VDDSYN | 3.0   | 3.6   | V    |

| Operating voltage at 40 MHz or higher                                                         | VDDH, VDDL,<br>KAPWR, VDDSYN | 3.135 | 3.465 | V    |

| Input high voltage (address bus, data bus, EXTAL, EXTCLK, and all bus control/status signals) | VIH                          | 2.0   | 3.6   | V    |

| Input high voltage (all general purpose I/O and peripheral pins)                              | VIH                          | 2.0   | 5.5   | V    |

| NP |

|----|

|----|

| Table 6. | Bus | Operation | Timing | 1 |

|----------|-----|-----------|--------|---|

|----------|-----|-----------|--------|---|

|     | Characteristic                                                                               | 50 MHz |       | 66 MHz |       | 80 MHz |       |       | Cap Load           |      |

|-----|----------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|-------|--------------------|------|

| Num |                                                                                              | Min    | Max   | Min    | Max   | Min    | Max   | FFACT | (default<br>50 pF) | Unit |

| B1  | CLKOUT period                                                                                | 20     | _     | 30.30  | _     | 25     | _     | _     |                    | ns   |

| B1a | EXTCLK to CLKOUT phase<br>skew (EXTCLK > 15 MHz and<br>MF <= 2)                              | -0.90  | 0.90  | -0.90  | 0.90  | -0.90  | 0.90  | _     | 50.00              | ns   |

| B1b | EXTCLK to CLKOUT phase<br>skew (EXTCLK > 10 MHz and<br>MF < 10)                              | -2.30  | 2.30  | -2.30  | 2.30  | -2.30  | 2.30  | —     | 50.00              | ns   |

| B1c | CLKOUT phase jitter (EXTCLK > 15 MHz and MF <= 2) $^{2}$                                     | -0.60  | 0.60  | -0.60  | 0.60  | -0.60  | 0.60  | _     | 50.00              | ns   |

| B1d | CLKOUT phase jitter <sup>2</sup>                                                             | -2.00  | 2.00  | -2.00  | 2.00  | -2.00  | 2.00  | —     | 50.00              | ns   |

| B1e | CLKOUT frequency jitter (MF < 10) <sup>2</sup>                                               | —      | 0.50  | —      | 0.50  | _      | 0.50  | _     | 50.00              | %    |

| B1f | CLKOUT frequency jitter (10 < MF < 500) $^2$                                                 | —      | 2.00  | —      | 2.00  | _      | 2.00  | —     | 50.00              | %    |

| B1g | CLKOUT frequency jitter (MF > 500) <sup>2</sup>                                              | _      | 3.00  | _      | 3.00  | _      | 3.00  | _     | 50.00              | %    |

| B1h | Frequency jitter on EXTCLK <sup>3</sup>                                                      | —      | 0.50  | —      | 0.50  | —      | 0.50  | —     | 50.00              | %    |

| B2  | CLKOUT pulse width low                                                                       | 8.00   |       | 12.12  | —     | 10.00  |       | —     | 50.00              | ns   |

| B3  | CLKOUT width high                                                                            | 8.00   | _     | 12.12  | —     | 10.00  | _     | —     | 50.00              | ns   |

| B4  | CLKOUT rise time                                                                             | —      | 4.00  | —      | 4.00  | —      | 4.00  | —     | 50.00              | ns   |

| B5  | CLKOUT fall time                                                                             | _      | 4.00  | _      | 4.00  | —      | 4.00  | —     | 50.00              | ns   |

| B7  | CLKOUT to A[6–31],<br>RD/WR, BURST, D[0–31],<br>DP[0–3] invalid                              | 5.00   | —     | 7.58   | —     | 6.25   | _     | 0.250 | 50.00              | ns   |

| B7a | CLKOUT to TSIZ[0–1], REG,<br>RSV, AT[0–3], BDIP, PTR<br>invalid                              | 5.00   |       | 7.58   | _     | 6.25   | _     | 0.250 | 50.00              | ns   |

| B7b | CLKOUT to BR, BG, FRZ,<br>VFLS[0–1], VF[0–2] IWP[0–2],<br>LWP[0–1], STS invalid <sup>4</sup> | 5.00   |       | 7.58   | _     | 6.25   | _     | 0.250 | 50.00              | ns   |

| B8  | CLKOUT to A[6–31],<br>RD/WR, BURST, D[0–31],<br>DP[0–3] valid                                | 5.00   | 11.75 | 7.58   | 14.33 | 6.25   | 13.00 | 0.250 | 50.00              | ns   |

| B8a | CLKOUT to TSIZ[0-1], REG,<br>RSV, AT[0-3] BDIP, PTR valid                                    | 5.00   | 11.75 | 7.58   | 14.33 | 6.25   | 13.00 | 0.250 | 50.00              | ns   |

| B8b | CLKOUT to BR, BG,<br>VFLS[0–1], VF[0–2], IWP[0–2],<br>FRZ, LWP[0–1], STS valid <sup>4</sup>  | 5.00   | 11.74 | 7.58   | 14.33 | 6.25   | 13.00 | 0.250 | 50.00              | ns   |

**Bus Signal Timing**

|      | Characteristic                                                                                                          | 50 MHz 66 MHz |       |       | 80 I  | MHz   |       | Cap Load | 11                 |      |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|----------|--------------------|------|

| Num  |                                                                                                                         | Min           | Max   | Min   | Max   | Min   | Мах   | FFACT    | (default<br>50 pF) | Unit |

| B9   | CLKOUT to A[6–31] RD/WR,<br>BURST, D[0–31], DP[0–3],<br>TSIZ[0–1], REG, RSV, AT[0–3],<br>PTR high-Z                     | 5.00          | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250    | 50.00              | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion                                                                   | 5.00          | 11.00 | 7.58  | 13.58 | 6.25  | 12.25 | 0.250    | 50.00              | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion,<br>(When driven by the memory<br>controller or PCMCIA interface) | 2.50          | 9.25  | 2.50  | 9.25  | 2.50  | 9.25  | —        | 50.00              | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation                                                                    | 5.00          | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250    | 50.00              | ns   |

| B12a | CLKOUT to TA, BI negation<br>(when driven by the memory<br>controller or PCMCIA interface)                              | 2.50          | 11.00 | 2.50  | 11.00 | 2.50  | 11.00 | —        | 50.00              | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ high-Z                                                                      | 5.00          | 19.00 | 7.58  | 21.58 | 6.25  | 20.25 | 0.250    | 50.00              | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ high-Z,<br>(when driven by the memory<br>controller or PCMCIA interface)    | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | —        | 50.00              | ns   |

| B14  | CLKOUT to $\overline{TEA}$ assertion                                                                                    | 2.50          | 10.00 | 2.50  | 10.00 | 2.50  | 10.00 | —        | 50.00              | ns   |

| B15  | CLKOUT to TEA high-Z                                                                                                    | 2.50          | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | —        | 50.00              | ns   |

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT(setup time) <sup>5</sup>                                | 9.75          | —     | 9.75  | —     | 9.75  | —     | —        | 50.00              | ns   |

| B16a | TEA, KR, RETRY, valid to CLKOUT (setup time) <sup>5</sup>                                                               | 10.00         | —     | 10.00 | —     | 10.00 | —     | —        | 50.00              | ns   |

| B16b | $\overline{\text{BB}}$ , $\overline{\text{BG}}$ , $\overline{\text{BR}}$ valid to CLKOUT (setup time) <sup>6</sup>      | 8.50          | _     | 8.50  | —     | 8.50  | —     | _        | 50.00              | ns   |

| B17  | $\frac{\text{CLKOUT to TA, TEA, BI, BB,}}{\text{BG, BR valid (Hold time).}^5}$                                          | 1.00          |       | 1.00  | —     | 1.00  | _     | _        | 50.00              | ns   |

| B17a | CLKOUT to KR, RETRY, except<br>TEA valid (hold time)                                                                    | 2.00          | —     | 2.00  | —     | 2.00  | —     | _        | 50.00              | ns   |

| B18  | D[0–31], DP[0–3] valid to<br>CLKOUT rising edge (setup<br>time) <sup>7</sup>                                            | 6.00          | _     | 6.00  |       | 6.00  |       | _        | 50.00              | ns   |

| B19  | CLKOUT rising edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>7</sup>                                             | 1.00          | _     | 1.00  |       | 1.00  |       | _        | 50.00              | ns   |

| B20  | D[0–31], DP[0–3] valid to<br>CLKOUT falling edge (setup<br>time) <sup>8</sup>                                           | 4.00          |       | 4.00  |       | 4.00  | —     | _        | 50.00              | ns   |

| B21  | CLKOUT falling edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>8</sup>                                            | 2.00          | —     | 2.00  |       | 2.00  | —     | —        | —                  |      |

| Table 6. | <b>Bus Operation Timing</b> | <sup>1</sup> (continued) |

|----------|-----------------------------|--------------------------|

|----------|-----------------------------|--------------------------|

|          |                                                                                                                               | 50                 | MHz                 | 66          | MHz                 | 80    | MHz                 |       | Cap Load               |      |

|----------|-------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-------------|---------------------|-------|---------------------|-------|------------------------|------|

| Num      | Characteristic                                                                                                                |                    |                     |             |                     | Min   |                     | FFACT | (default               | Unit |

| B22      | CLKOUT rising edge to $\overline{CS}$                                                                                         | <b>Min</b><br>5.00 | <b>Max</b><br>11.75 | Min<br>7.58 | <b>Max</b><br>14.33 | 6.25  | <b>Max</b><br>13.00 | 0.250 | <b>50 pF)</b><br>50.00 | ns   |

| <b>.</b> | asserted GPCM ACS = 00                                                                                                        |                    |                     |             |                     |       | 0.00                |       | 50.00                  |      |

| B22a     | CLKOUT falling edge to $\overline{CS}$<br>asserted GPCM ACS = 10,<br>TRLX = 0,1                                               | _                  | 8.00                | _           | 8.00                |       | 8.00                | _     | 50.00                  | ns   |

| B22b     | CLKOUT falling edge to $\overline{CS}$<br>asserted GPCM ACS = 11,<br>TRLX = 0, EBDF = 0                                       | 5.00               | 11.75               | 7.58        | 14.33               | 6.25  | 13.00               | 0.250 | 50.00                  | ns   |

| B22c     | CLKOUT falling edge to $\overline{CS}$<br>asserted GPCM ACS = 11,<br>TRLX = 0, EBDF = 1                                       | 7.00               | 14.00               | 11.00       | 18.00               | 9.00  | 16.00               | 0.375 | 50.00                  | ns   |

| B23      | CLKOUT rising edge to $\overline{CS}$<br>negated GPCM read access,<br>GPCM write access ACS = 00,<br>TRLX = 0 & CSNT = 0      | 2.00               | 8.00                | 2.00        | 8.00                | 2.00  | 8.00                |       | 50.00                  | ns   |

| B24      | A[6-31] to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = 0.                                                               | 3.00               | —                   | 6.00        | —                   | 4.00  | —                   | 0.250 | 50.00                  | ns   |

| B24a     | A[6–31] to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 0                                                                | 8.00               | —                   | 13.00       | _                   | 11.00 | —                   | 0.500 | 50.00                  | ns   |

| B25      | $\frac{CLKOUT}{WE[0-3]} \text{ asserted}$                                                                                     | —                  | 9.00                | _           | 9.00                | —     | 9.00                | —     | 50.00                  | ns   |

| B26      | CLKOUT rising edge to $\overline{OE}$ negated                                                                                 | 2.00               | 9.00                | 2.00        | 9.00                | 2.00  | 9.00                | —     | 50.00                  | ns   |

| B27      | A[6–31] to $\overline{CS}$ asserted GPCM<br>ACS = 10, TRLX = 1                                                                | 23.00              | —                   | 36.00       | —                   | 29.00 | —                   | 1.250 | 50.00                  | ns   |

| B27a     | A[6–31] to $\overline{CS}$ asserted GPCM<br>ACS = 11, TRLX = 1                                                                | 28.00              | —                   | 43.00       | —                   | 36.00 | —                   | 1.500 | 50.00                  | ns   |

| B28      | CLKOUT rising edge to<br>WE[0–3] negated GPCM write<br>access CSNT = 0                                                        | —                  | 9.00                | —           | 9.00                | —     | 9.00                | —     | 50.00                  | ns   |

| B28a     | CLKOUT falling edge to<br>WE[0–3] negated GPCM write<br>access TRLX = 0,1 CSNT = 1,<br>EBDF = 0                               | 5.00               | 12.00               | 8.00        | 14.00               | 6.00  | 13.00               | 0.250 | 50.00                  | ns   |

| B28b     | CLKOUT falling edge to $\overline{CS}$<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 0 | _                  | 12.00               |             | 14.00               | _     | 13.00               | 0.250 | 50.00                  | ns   |

| Table 6. Bus Operation Timing | 1 | (continued) |

|-------------------------------|---|-------------|

|-------------------------------|---|-------------|

**Bus Signal Timing**

| [    |                                                                                                                                             |             |       |       | -        |       |       |       |                      |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|----------|-------|-------|-------|----------------------|------|

| Num  | Characteristic                                                                                                                              | 50 MHz 66 I |       | 66 I  | /Hz 80 M |       | MHz   | FFACT | Cap Load<br>(default | Unit |

| -    |                                                                                                                                             | Min         | Max   | Min   | Max      | Min   | Max   |       | 50 pF)               | •    |

| B28c | CLKOUT falling edge to<br>WE[0–3] negated GPCM write<br>access TRLX = 0,1 CSNT = 1<br>write access TRLX = 0, CSNT =<br>1, EBDF = 1          | 7.00        | 14.00 | 11.00 | 18.00    | 9.00  | 16.00 | 0.375 | 50.00                | ns   |

| B28d | CLKOUT falling edge to $\overline{CS}$<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 1               | _           | 14.00 | _     | 18.00    | _     | 16.00 | 0.375 | 50.00                | ns   |

| B29  | $\overline{WE[0-3]}$ negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, CSNT = 0                                                   | 3.00        |       | 6.00  |          | 4.00  |       | 0.250 | 50.00                | ns   |

| B29a | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 0 CSNT = 1,<br>EBDF = 0                                          | 8.00        | _     | 13.00 | _        | 11.00 | _     | 0.500 | 50.00                | ns   |

| B29b | CS negated to D[0–31],<br>DP[0–3], high-Z GPCM write<br>access, ACS = 00, TRLX = 0 &<br>CSNT = 0                                            | 3.00        |       | 6.00  |          | 4.00  |       | 0.250 | 50.00                | ns   |

| B29c | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                       | 8.00        | _     | 13.00 | _        | 11.00 | _     | 0.500 | 50.00                | ns   |

| B29d | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                         | 28.00       |       | 43.00 |          | 36.00 |       | 1.500 | 50.00                | ns   |

| B29e | $\overline{\text{CS}}$ negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 28.00       | _     | 43.00 | _        | 36.00 | _     | 1.500 | 50.00                | ns   |

| B29f | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                          | 5.00        |       | 9.00  |          | 7.00  |       | 0.375 | 50.00                | ns   |

| B29g | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1                      | 5.00        |       | 9.00  |          | 7.00  |       | 0.375 | 50.00                | ns   |

| Table 6. | <b>Bus Operation</b> | Timing <sup>1</sup> | (continued) |

|----------|----------------------|---------------------|-------------|

|----------|----------------------|---------------------|-------------|

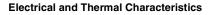

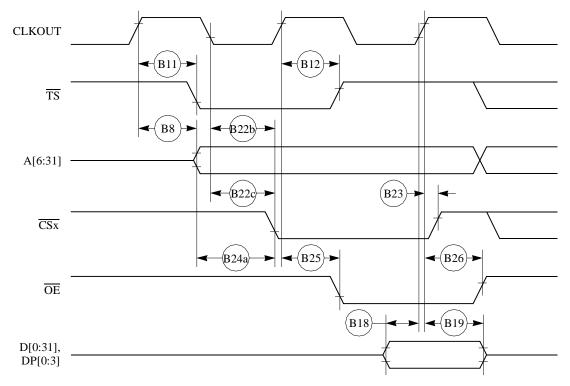

Figure 10. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 10)

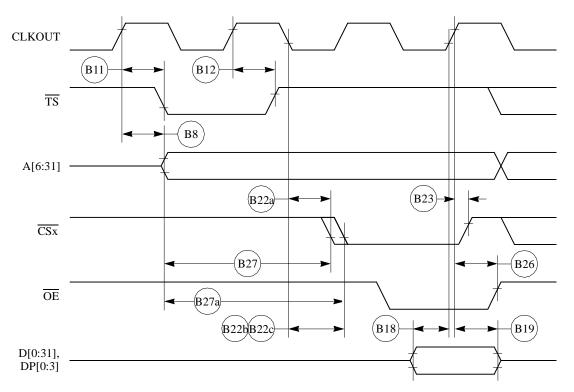

Figure 11. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

**Bus Signal Timing**

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 1, ACS = 10, ACS = 11)

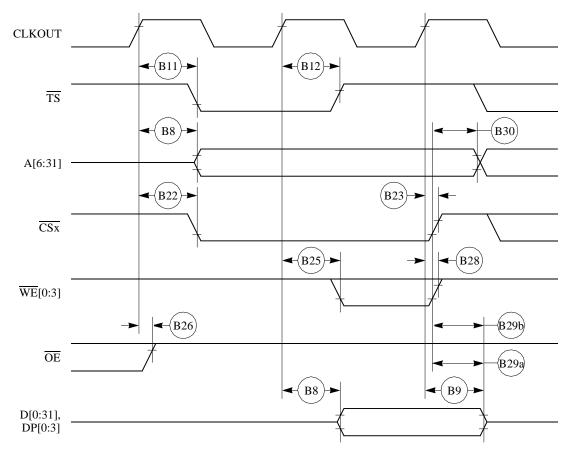

Figure 13 through Figure 15 provide the timing for the external bus write controlled by various GPCM factors.

Figure 13. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

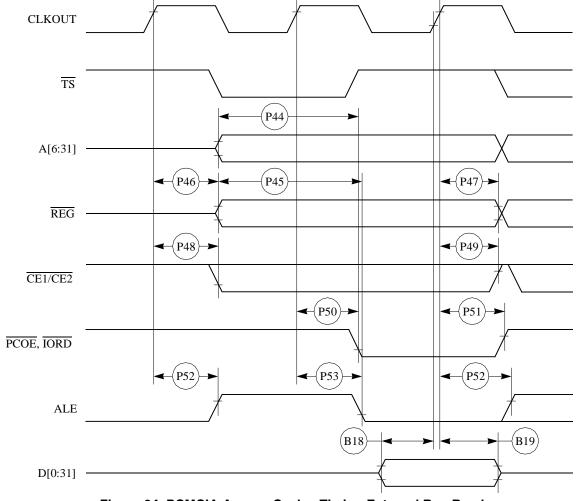

Figure 24 provides the PCMCIA access cycle timing for the external bus read.

Figure 24. PCMCIA Access Cycles Timing External Bus Read

Bus Signal Timing

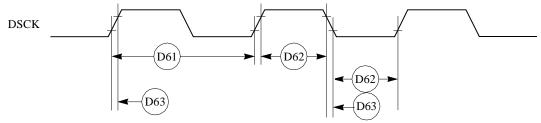

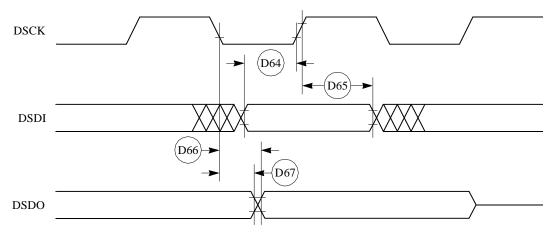

Table 10 shows the debug port timing for the MPC850.

| Num | Characteristic              | 50 I  | MHz 66 MHz |       |       | 80 MHz |       | Unit |

|-----|-----------------------------|-------|------------|-------|-------|--------|-------|------|

|     | Characteristic              | Min   | Max        | Min   | Max   | Min    | Max   | Unit |

| D61 | DSCK cycle time             | 60.00 |            | 91.00 |       | 75.00  | _     | ns   |

| D62 | DSCK clock pulse width      | 25.00 |            | 38.00 |       | 31.00  | —     | ns   |

| D63 | DSCK rise and fall times    | 0.00  | 3.00       | 0.00  | 3.00  | 0.00   | 3.00  | ns   |

| D64 | DSDI input data setup time  | 8.00  | _          | 8.00  | _     | 8.00   | —     | ns   |

| D65 | DSDI data hold time         | 5.00  | _          | 5.00  | _     | 5.00   | —     | ns   |

| D66 | DSCK low to DSDO data valid | 0.00  | 15.00      | 0.00  | 15.00 | 0.00   | 15.00 | ns   |

| D67 | DSCK low to DSDO invalid    | 0.00  | 2.00       | 0.00  | 2.00  | 0.00   | 2.00  | ns   |

Table 10. Debug Port Timing

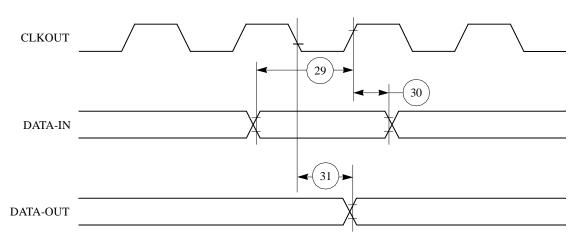

Figure 29 provides the input timing for the debug port clock.

Figure 29. Debug Port Clock Input Timing

Figure 30 provides the timing for the debug port.

Figure 30. Debug Port Timings

**CPM Electrical Characteristics**

Figure 38. Parallel I/O Data-In/Data-Out Timing Diagram

## 8.2 IDMA Controller AC Electrical Specifications

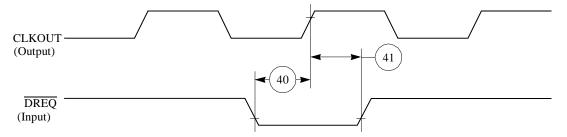

Table 14 provides the IDMA controller timings as shown in Figure 39 to Figure 42.

| Num | Num Characteristic                                                                                       |      | All Frequencies |      |  |

|-----|----------------------------------------------------------------------------------------------------------|------|-----------------|------|--|

| Num | Characteristic                                                                                           | Min  | Max             | Unit |  |

| 40  | DREQ setup time to clock high                                                                            | 7.00 | _               | ns   |  |

| 41  | DREQ hold time from clock high                                                                           | 3.00 | _               | ns   |  |

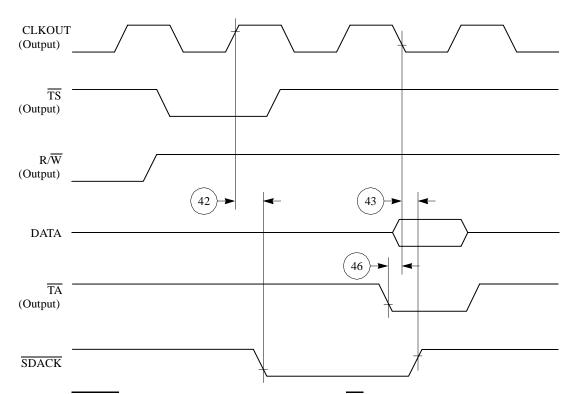

| 42  | SDACK assertion delay from clock high                                                                    | _    | 12.00           | ns   |  |

| 43  | SDACK negation delay from clock low                                                                      | _    | 12.00           | ns   |  |

| 44  | SDACK negation delay from TA low                                                                         | _    | 20.00           | ns   |  |

| 45  | SDACK negation delay from clock high                                                                     | _    | 15.00           | ns   |  |

| 46  | $\overline{TA}$ assertion to falling edge of the clock setup time (applies to external $\overline{TA}$ ) | 7.00 |                 | ns   |  |

### Table 14. IDMA Controller Timing

Figure 39. IDMA External Requests Timing Diagram

Figure 40. SDACK Timing Diagram—Peripheral Write, TA Sampled Low at the Falling Edge of the Clock

|     |                                                                         |        | СРМ                   | Electrical Ch |  |

|-----|-------------------------------------------------------------------------|--------|-----------------------|---------------|--|

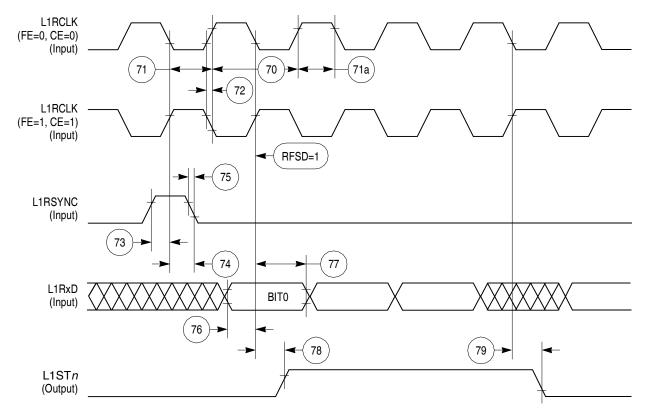

|     | Table 17. SI Timing (cont                                               | inued) |                       |               |  |

| Num | All Frequencies                                                         |        |                       |               |  |

| Num | Characteristic                                                          | Min    | Мах                   | Unit          |  |

| 82  | L1RCLK, L1TCLK frequency (DSC =1)                                       | —      | 16.00 or<br>SYNCCLK/2 | MHz           |  |

| 83  | L1RCLK, L1TCLK width low (DSC =1)                                       | P + 10 | —                     | ns            |  |

| 83A | L1RCLK, L1TCLK width high (DSC = $1$ ) <sup>3</sup>                     | P + 10 | —                     | ns            |  |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                    | —      | 30.00                 | ns            |  |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>                  | 1.00   | —                     | L1TCLK        |  |

| 86  | L1GR setup time <sup>2</sup>                                            | 42.00  | —                     | ns            |  |

| 87  | L1GR hold time                                                          | 42.00  | —                     | ns            |  |

| 88  | L1xCLK edge to L1SYNC valid (FSD = 00) CNT =<br>0000, BYT = 0, DSC = 0) | —      | 0.00                  | ns            |  |

1 The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

- 2 These specs are valid for IDL mode only.

- <sup>3</sup> Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

**CPM Electrical Characteristics**

Figure 52. HDLC Bus Timing Diagram

## 8.7 Ethernet Electrical Specifications

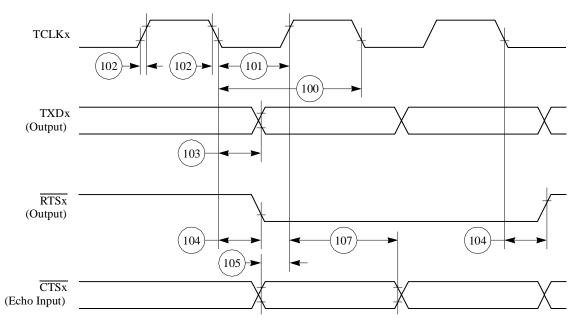

Table 20 provides the Ethernet timings as shown in Figure 53 to Figure 55.

| Num | Characteristic                                                  | All Fred | All Frequencies |      |

|-----|-----------------------------------------------------------------|----------|-----------------|------|

| Num | Characteristic                                                  | Min      | Max             | Unit |

| 120 | CLSN width high                                                 | 40.00    | _               | ns   |

| 121 | RCLKx rise/fall time (x = 2, 3 for all specs in this table)     | _        | 15.00           | ns   |

| 122 | RCLKx width low                                                 | 40.00    |                 | ns   |

| 123 | RCLKx clock period <sup>1</sup>                                 | 80.00    | 120.00          | ns   |

| 124 | RXDx setup time                                                 | 20.00    |                 | ns   |

| 125 | RXDx hold time                                                  | 5.00     |                 | ns   |

| 126 | RENA active delay (from RCLKx rising edge of the last data bit) | 10.00    | _               | ns   |

| 127 | RENA width low                                                  | 100.00   | _               | ns   |

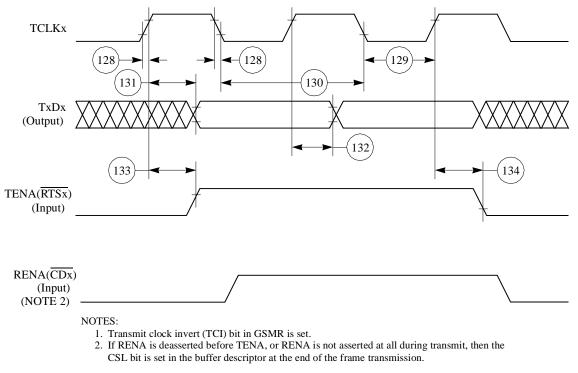

| 128 | TCLKx rise/fall time                                            | —        | 15.00           | ns   |

| 129 | TCLKx width low                                                 | 40.00    |                 | ns   |

| 130 | TCLKx clock period <sup>1</sup>                                 | 99.00    | 101.00          | ns   |

| 131 | TXDx active delay (from TCLKx rising edge)                      | 10.00    | 50.00           | ns   |

| 132 | TXDx inactive delay (from TCLKx rising edge)                    | 10.00    | 50.00           | ns   |

| 133 | TENA active delay (from TCLKx rising edge)                      | 10.00    | 50.00           | ns   |

**CPM Electrical Characteristics**

Figure 55. Ethernet Transmit Timing Diagram

## 8.8 SMC Transparent AC Electrical Specifications

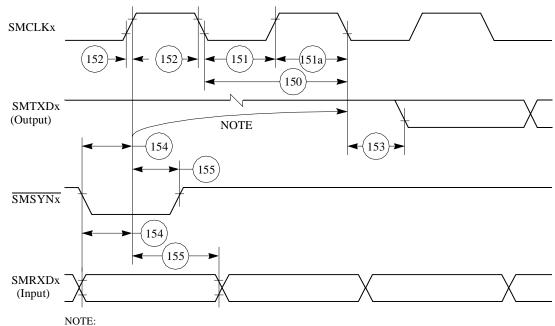

Figure 21 provides the SMC transparent timings as shown in Figure 56.

| Num  | Characteristic                                 | All Frequ | iencies | Unit |

|------|------------------------------------------------|-----------|---------|------|

| Num  |                                                | Min       | Мах     | Unit |

| 150  | SMCLKx clock period <sup>1</sup>               | 100.00    | _       | ns   |

| 151  | SMCLKx width low                               | 50.00     | _       | ns   |

| 151a | SMCLKx width high                              | 50.00     | _       | ns   |

| 152  | SMCLKx rise/fall time                          | _         | 15.00   | ns   |

| 153  | SMTXDx active delay (from SMCLKx falling edge) | 10.00     | 50.00   | ns   |

| 154  | SMRXDx/SMSYNx setup time                       | 20.00     | _       | ns   |

| 155  | SMRXDx/SMSYNx hold time                        | 5.00      | _       | ns   |

| Table 21. | Serial | Management | Controller | Timing |

|-----------|--------|------------|------------|--------|

|-----------|--------|------------|------------|--------|

<sup>1</sup> The ratio SyncCLK/SMCLKx must be greater or equal to 2/1.

1. This delay is equal to an integer number of character-length clocks.

### Figure 56. SMC Transparent Timing Diagram

## 8.9 SPI Master AC Electrical Specifications

Table 22 provides the SPI master timings as shown in Figure 57 and Figure 58.

| Num | Characteristic                      | All Frequ | Unit  |                  |

|-----|-------------------------------------|-----------|-------|------------------|

| Num |                                     |           | Max   | Unit             |

| 160 | MASTER cycle time                   | 4         | 1024  | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time | 2         | 512   | t <sub>cyc</sub> |

| 162 | MASTER data setup time (inputs)     | 50.00     | _     | ns               |

| 163 | Master data hold time (inputs)      | 0.00      | _     | ns               |

| 164 | Master data valid (after SCK edge)  | —         | 20.00 | ns               |

| 165 | Master data hold time (outputs)     | 0.00      | _     | ns               |

| 166 | Rise time output                    | —         | 15.00 | ns               |

| 167 | Fall time output                    | —         | 15.00 | ns               |

### Table 22. SPI Master Timing

#### Mechanical Data and Ordering Information

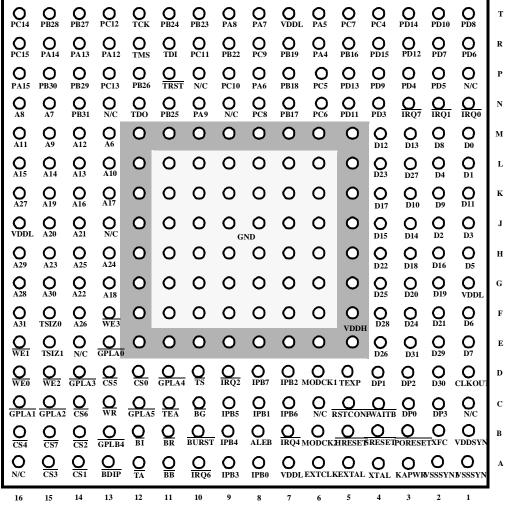

customers that are currently using the non-JEDEC pin numbering scheme, two sets of pinouts, JEDEC and non-JEDEC, are presented in this document.

Figure 62 shows the non-JEDEC pinout of the PBGA package as viewed from the top surface.

Figure 62. Pin Assignments for the PBGA (Top View)—non-JEDEC Standard

**Document Revision History**

## THIS PAGE INTENTIONALLY LEFT BLANK