# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 50MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                  |

| RAM Controllers                 | DRAM                                                                 |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10Mbps (1)                                                           |

| SATA                            | -                                                                    |

| USB                             | USB 1.x (1)                                                          |

| Voltage - I/O                   | 3.3V                                                                 |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                      |

| Security Features               | -                                                                    |

| Package / Case                  | 256-BBGA                                                             |

| Supplier Device Package         | 256-PBGA (23x23)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc850zq50bu |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# NP,

# 2 Features

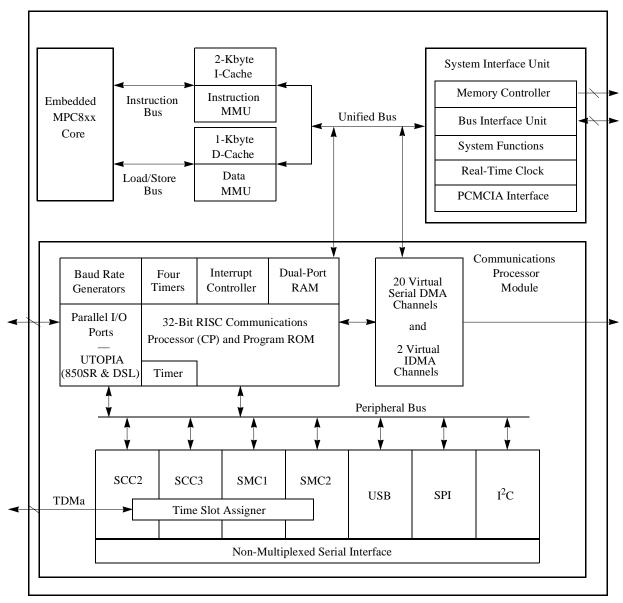

Figure 1 is a block diagram of the MPC850, showing its major components and the relationships among those components:

Figure 1. MPC850 Microprocessor Block Diagram

The following list summarizes the main features of the MPC850:

- Embedded single-issue, 32-bit MPC8xx core (implementing the PowerPC architecture) with thirty-two 32-bit general-purpose registers (GPRs)

- Performs branch folding and branch prediction with conditional prefetch, but without conditional execution

Features

- QUICC multichannel controller (QMC) microcode features

- Up to 64 independent communication channels on a single SCC

- Arbitrary mapping of 0–31 channels to any of 0–31 TDM time slots

- Supports either transparent or HDLC protocols for each channel

- Independent TxBDs/Rx and event/interrupt reporting for each channel

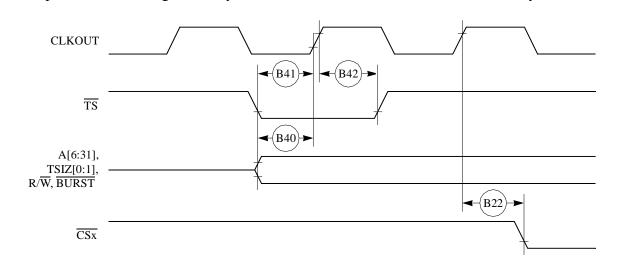

- One universal serial bus controller (USB)

- Supports host controller and slave modes at 1.5 Mbps and 12 Mbps

- Two serial management controllers (SMCs)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division-multiplexed (TDM) channel

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C<sup>®</sup> (interprocessor-integrated circuit) port

- Supports master and slave modes

- Supports multimaster environment

- Time slot assigner

- Allows SCCs and SMCs to run in multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame syncs, clocking

- Allows dynamic changes

- Can be internally connected to four serial channels (two SCCs and two SMCs)

- Low-power support

- Full high: all units fully powered at high clock frequency

- Full low: all units fully powered at low clock frequency

- Doze: core functional units disabled except time base, decrementer, PLL, memory controller, real-time clock, and CPM in low-power standby

- Sleep: all units disabled except real-time clock and periodic interrupt timer. PLL is active for fast wake-up

- Deep sleep: all units disabled including PLL, except the real-time clock and periodic interrupt timer

- Low-power stop: to provide lower power dissipation

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 MHz 66 MHz |     |       | 00.5      | /LI-  |       | Contract             |        |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|-------|-----------|-------|-------|----------------------|--------|----|

| Num  | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |     | MHZ   | Hz 80 MHz |       | FFACT | Cap Load<br>(default | Unit   |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | Max | Min   | Мах       | Min   | Мах   |                      | 50 pF) |    |

| B29h | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25.00         |     | 39.00 |           | 31.00 |       | 1.375                | 50.00  | ns |

| B29i | $\overline{\text{CS}}$ negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25.00         | _   | 39.00 | _         | 31.00 | _     | 1.375                | 50.00  | ns |

| B30  | CS, WE[0–3] negated to<br>A[6–31] invalid<br>GPCM write access <sup>9</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.00          | _   | 6.00  | _         | 4.00  | _     | 0.250                | 50.00  | ns |

| B30a | $\label{eq:weighted} \hline \hline WE[0-3] \ negated to \ A[6-31] \\ invalid \\ GPCM write \ access, TRLX = 0, \\ CSNT = 1, \ \overline{CS} \ negated to \\ A[6-31] \ invalid \ GPCM \ write \\ access \ TRLX = 0, \ CSNT = 1, \\ ACS = 10 \ or \ ACS = 11, \ EBDF = 0 \\ 0 \\ \hline \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.00          | _   | 13.00 | _         | 11.00 | _     | 0.500                | 50.00  | ns |

| B30b | $eq:weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_$                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28.00         | _   | 43.00 | _         | 36.00 | _     | 1.500                | 50.00  | ns |

| B30c | $\label{eq:weighted} \hline \hline WE[0-3] \mbox{ negated to } A[6-31] \mbox{ invalid } \\ GPCM \mbox{ write access, TRLX = 0, } \\ CSNT = 1. \ensuremath{\overline{CS}}\xspace$ negated to } \\ A[6-31] \mbox{ invalid GPCM write } \\ access, TRLX = 0, \ensuremath{CSNT}\xspace = 1, \\ ACS = 10 \mbox{ or } ACS = 11, \ensuremath{EBDF}\xspace = 1 \\ \hline 1 \\ \hline \hline \hline \ensuremath{\mathbb{R}}\xspace \ensuremath$ | 5.00          | _   | 8.00  |           | 6.00  |       | 0.375                | 50.00  | ns |

| B30d | $\label{eq:WE[0-3]} \begin{array}{l} \hline WE[0-3] \mbox{ negated to } A[6-31] \\ \hline \mbox{invalid GPCM write access} \\ \hline TRLX = 1, \mbox{ CSNT = 1, } \hline CS \\ \hline \mbox{ negated to } A[6-31] \mbox{ invalid } \\ \hline GPCM \mbox{ write access } TRLX = 1, \\ \hline CSNT = 1, \mbox{ ACS = 10 or } ACS = \\ \hline 11, \mbox{ EBDF = 1} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25.00         |     | 39.00 |           | 31.00 |       | 1.375                | 50.00  | ns |

|      |                                                                                                                               |       |               |       |       |       |       |                      | _               |    |

|------|-------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|-------|-------|-------|----------------------|-----------------|----|

| Num  | Characteristic                                                                                                                |       | 50 MHz 66 MHz |       | 80 1  | MHz   | FFACT | Cap Load<br>(default | Unit            |    |

|      |                                                                                                                               | Min   | Max           | Min   | Max   | Min   | Max   |                      | <b>`</b> 50 pF) |    |

| B33a | CLKOUT rising edge to GPL<br>valid - as requested by control<br>bit GxT3 in the corresponding<br>word in the UPM              | 5.00  | 12.00         | 8.00  | 14.00 | 6.00  | 13.00 | 0.250                | 50.00           | ns |

| B34  | A[6–31] and D[0–31] to CS valid<br>- as requested by control bit<br>CST4 in the corresponding<br>word in the UPM              | 3.00  | _             | 6.00  | _     | 4.00  | _     | 0.250                | 50.00           | ns |

| B34a | A[6–31] and D[0–31] to $\overline{CS}$ valid<br>- as requested by control bit<br>CST1 in the corresponding<br>word in the UPM | 8.00  | _             | 13.00 | _     | 11.00 | _     | 0.500                | 50.00           | ns |

| B34b | A[6–31] and D[0–31] to CS valid<br>- as requested by CST2 in the<br>corresponding word in UPM                                 | 13.00 | _             | 21.00 |       | 17.00 |       | 0.750                | 50.00           | ns |

| B35  | A[6-31] to $\overline{CS}$ valid - as<br>requested by control bit BST4 in<br>the corresponding word in UPM                    | 3.00  | _             | 6.00  | _     | 4.00  | _     | 0.250                | 50.00           | ns |

| B35a | A[6–31] and D[0–31] to BS valid<br>- as requested by BST1 in the<br>corresponding word in the UPM                             | 8.00  | _             | 13.00 | _     | 11.00 | _     | 0.500                | 50.00           | ns |

| B35b | A[6–31] and D[0–31] to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM              | 13.00 | _             | 21.00 | _     | 17.00 | _     | 0.750                | 50.00           | ns |

| B36  | A[6–31] and D[0–31] to GPL<br>valid - as requested by control<br>bit GxT4 in the corresponding<br>word in the UPM             | 3.00  |               | 6.00  |       | 4.00  |       | 0.250                | 50.00           | ns |

| B37  | UPWAIT valid to CLKOUT falling edge 10                                                                                        | 6.00  |               | 6.00  |       | 6.00  |       | —                    | 50.00           | ns |

| B38  | CLKOUT falling edge to<br>UPWAIT valid <sup>10</sup>                                                                          | 1.00  | —             | 1.00  | _     | 1.00  | _     | —                    | 50.00           | ns |

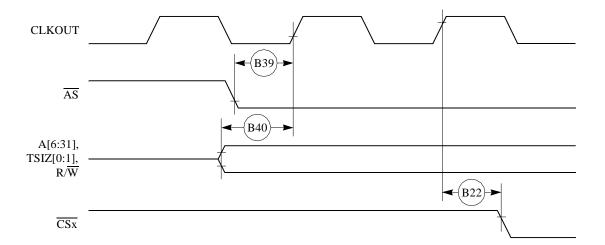

| B39  | AS valid to CLKOUT rising edge                                                                                                | 7.00  |               | 7.00  | —     | 7.00  | —     | —                    | 50.00           | ns |

| B40  | A[6-31], TSIZ[0-1], RD/WR,<br>BURST, valid to CLKOUT rising<br>edge.                                                          | 7.00  |               | 7.00  |       | 7.00  |       | —                    | 50.00           | ns |

| B41  | TS valid to CLKOUT rising edge (setup time)                                                                                   | 7.00  | _             | 7.00  | _     | 7.00  | _     | _                    | 50.00           | ns |

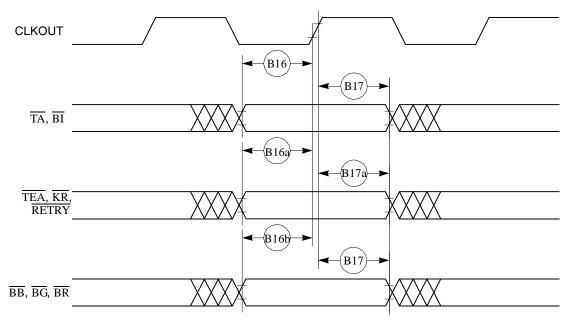

Figure 6 provides the timing for the synchronous input signals.

### Figure 6. Synchronous Input Signals Timing

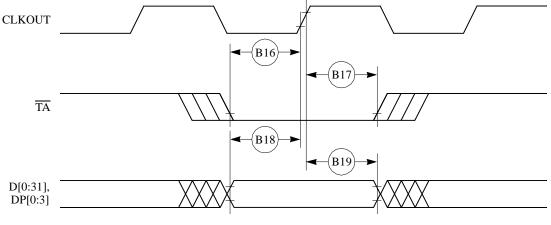

Figure 7 provides normal case timing for input data.

Figure 7. Input Data Timing in Normal Case

**Bus Signal Timing**

Figure 8 provides the timing for the input data controlled by the UPM in the memory controller.

Figure 8. Input Data Timing when Controlled by UPM in the Memory Controller

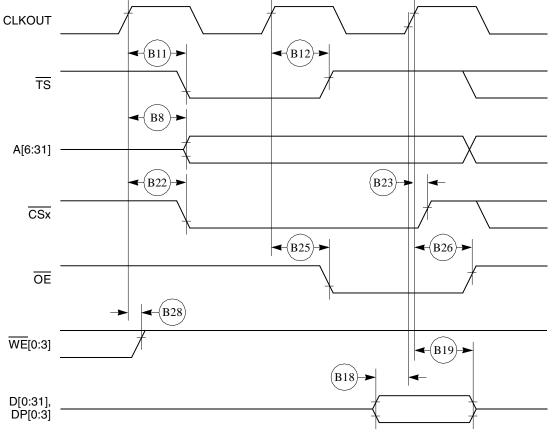

Figure 9 through Figure 12 provide the timing for the external bus read controlled by various GPCM factors.

Figure 9. External Bus Read Timing (GPCM Controlled—ACS = 00)

**Bus Signal Timing**

Figure 19 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 19. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 20 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 21 provides the timing for the asynchronous external master control signals negation.

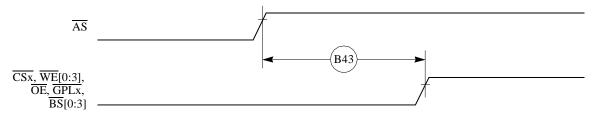

Figure 21. Asynchronous External Master—Control Signals Negation Timing

**Bus Signal Timing**

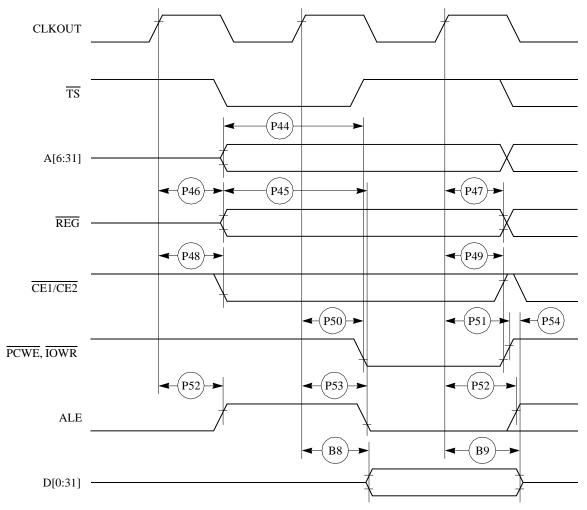

Figure 25 provides the PCMCIA access cycle timing for the external bus write.

Figure 25. PCMCIA Access Cycles Timing External Bus Write

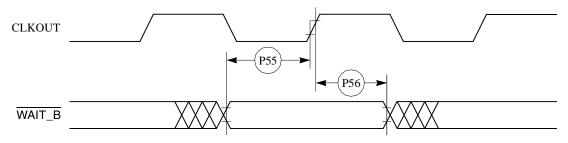

Figure 26 provides the PCMCIA WAIT signals detection timing.

Figure 26. PCMCIA WAIT Signal Detection Timing

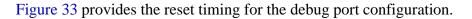

Figure 33. Reset Timing—Debug Port Configuration

## 7 IEEE 1149.1 Electrical Specifications

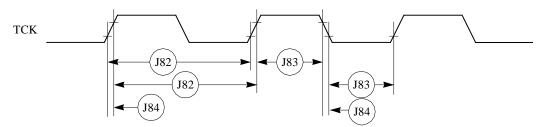

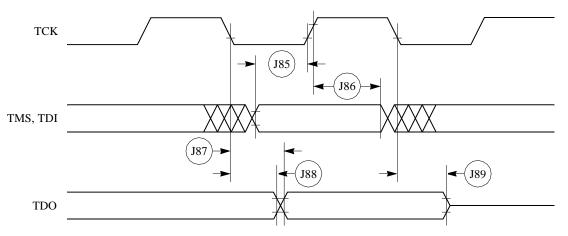

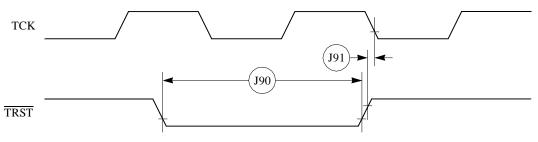

Table 12 provides the JTAG timings for the MPC850 as shown in Figure 34 to Figure 37.

Table 12. JTAG Timing

| Num | Characteristic                                         | 50 MHz |       | 66MHz  |       | 80 MHz |       | Unit |

|-----|--------------------------------------------------------|--------|-------|--------|-------|--------|-------|------|

| num | Characteristic                                         | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| J82 | TCK cycle time                                         | 100.00 | _     | 100.00 | _     | 100.00 | _     | ns   |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00  |       | 40.00  |       | 40.00  |       | ns   |

| J84 | TCK rise and fall times                                | 0.00   | 10.00 | 0.00   | 10.00 | 0.00   | 10.00 | ns   |

| J85 | TMS, TDI data setup time                               | 5.00   |       | 5.00   |       | 5.00   |       | ns   |

| J86 | TMS, TDI data hold time                                | 25.00  |       | 25.00  |       | 25.00  |       | ns   |

| J87 | TCK low to TDO data valid                              | —      | 27.00 | —      | 27.00 | —      | 27.00 | ns   |

| J88 | TCK low to TDO data invalid                            | 0.00   |       | 0.00   |       | 0.00   |       | ns   |

| J89 | TCK low to TDO high impedance                          | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| J90 | TRST assert time                                       | 100.00 |       | 100.00 |       | 100.00 |       | ns   |

| J91 | TRST setup time to TCK low                             | 40.00  |       | 40.00  |       | 40.00  |       | ns   |

| J92 | TCK falling edge to output valid                       | —      | 50.00 | _      | 50.00 | —      | 50.00 | ns   |

| J93 | TCK falling edge to output valid out of high impedance | —      | 50.00 | _      | 50.00 | —      | 50.00 | ns   |

| J94 | TCK falling edge to output high impedance              | —      | 50.00 | —      | 50.00 | —      | 50.00 | ns   |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00  | _     | 50.00  | _     | 50.00  | _     | ns   |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00  | _     | 50.00  | _     | 50.00  | _     | ns   |

IEEE 1149.1 Electrical Specifications

Figure 34. JTAG Test Clock Input Timing

Figure 35. JTAG Test Access Port Timing Diagram

Figure 36. JTAG TRST Timing Diagram

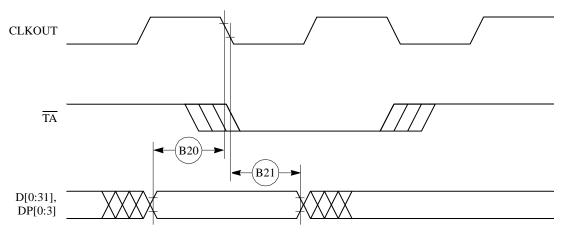

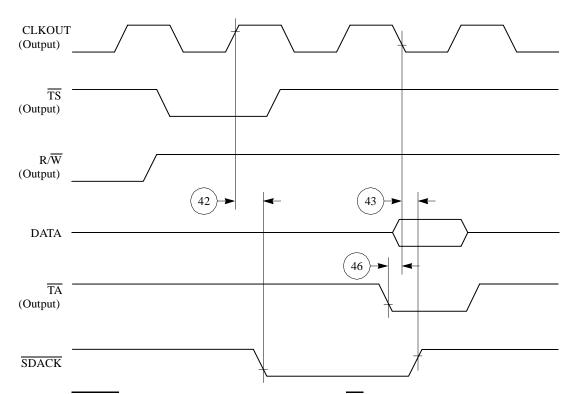

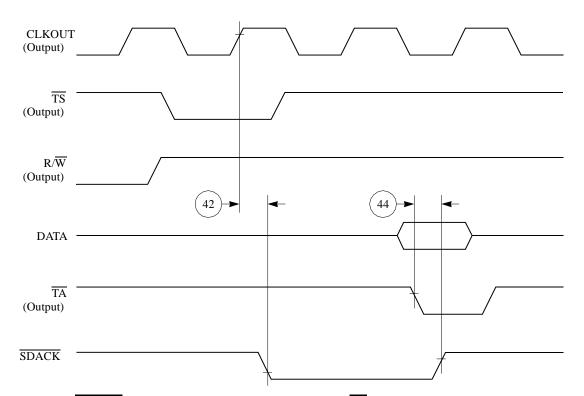

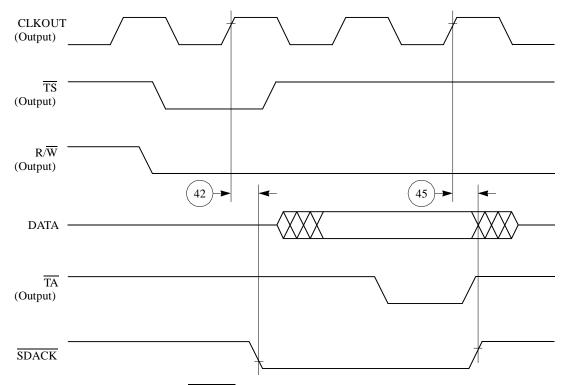

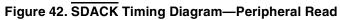

Figure 40. SDACK Timing Diagram—Peripheral Write, TA Sampled Low at the Falling Edge of the Clock

**CPM Electrical Characteristics**

Figure 41. SDACK Timing Diagram—Peripheral Write, TA Sampled High at the Falling Edge of the Clock

### 8.3 Baud Rate Generator AC Electrical Specifications

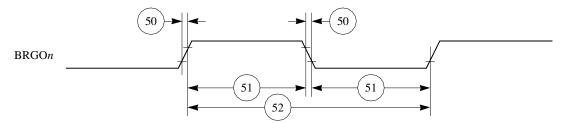

Table 15 provides the baud rate generator timings as shown in Figure 43.

Table 15. Baud Rate Generator Timing

| Num | Characteristic          | All Frequ | Unit  |      |

|-----|-------------------------|-----------|-------|------|

| Num | Characteristic          | Min       | Max   | Unit |

| 50  | BRGO rise and fall time | _         | 10.00 | ns   |

| 51  | BRGO duty cycle         | 40.00     | 60.00 | %    |

| 52  | BRGO cycle              | 40.00     | —     | ns   |

Figure 43. Baud Rate Generator Timing Diagram

### 8.4 Timer AC Electrical Specifications

Table 16 provides the baud rate generator timings as shown in Figure 44.

| Num | Characteristic               | All Frequ | Unit  |      |

|-----|------------------------------|-----------|-------|------|

|     | Characteristic               | Min       | Мах   | Unit |

| 61  | TIN/TGATE rise and fall time | 10.00     |       | ns   |

| 62  | TIN/TGATE low time           | 1.00      | _     | clk  |

| 63  | TIN/TGATE high time          | 2.00      | _     | clk  |

| 64  | TIN/TGATE cycle time         | 3.00      | _     | clk  |

| 65  | CLKO high to TOUT valid      | 3.00      | 25.00 | ns   |

### Table 16. Timer Timing

**CPM Electrical Characteristics**

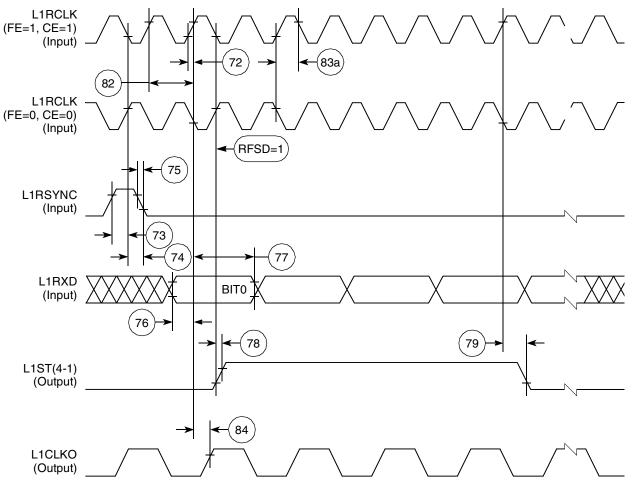

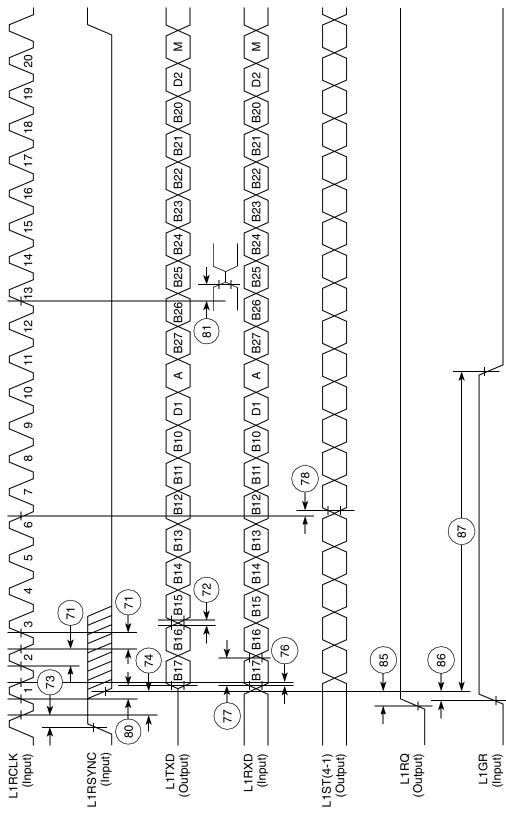

Figure 46. SI Receive Timing with Double-Speed Clocking (DSC = 1)

Figure 49. IDL Timing

**CPM Electrical Characteristics**

Figure 52. HDLC Bus Timing Diagram

### 8.7 Ethernet Electrical Specifications

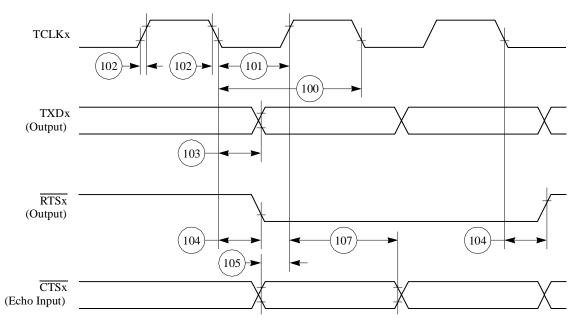

Table 20 provides the Ethernet timings as shown in Figure 53 to Figure 55.

| Num | Characteristic                                                  | All Fred | Unit   |      |

|-----|-----------------------------------------------------------------|----------|--------|------|

| Num | Characteristic                                                  | Min      | Max    | Unit |

| 120 | CLSN width high                                                 | 40.00    | _      | ns   |

| 121 | RCLKx rise/fall time (x = 2, 3 for all specs in this table)     | _        | 15.00  | ns   |

| 122 | RCLKx width low                                                 | 40.00    |        | ns   |

| 123 | RCLKx clock period <sup>1</sup>                                 | 80.00    | 120.00 | ns   |

| 124 | RXDx setup time                                                 | 20.00    |        | ns   |

| 125 | RXDx hold time                                                  | 5.00     |        | ns   |

| 126 | RENA active delay (from RCLKx rising edge of the last data bit) | 10.00    | _      | ns   |

| 127 | RENA width low                                                  | 100.00   | _      | ns   |

| 128 | TCLKx rise/fall time                                            | —        | 15.00  | ns   |

| 129 | TCLKx width low                                                 | 40.00    |        | ns   |

| 130 | TCLKx clock period <sup>1</sup>                                 | 99.00    | 101.00 | ns   |

| 131 | TXDx active delay (from TCLKx rising edge)                      | 10.00    | 50.00  | ns   |

| 132 | TXDx inactive delay (from TCLKx rising edge)                    | 10.00    | 50.00  | ns   |

| 133 | TENA active delay (from TCLKx rising edge)                      | 10.00    | 50.00  | ns   |

### Mechanical Data and Ordering Information

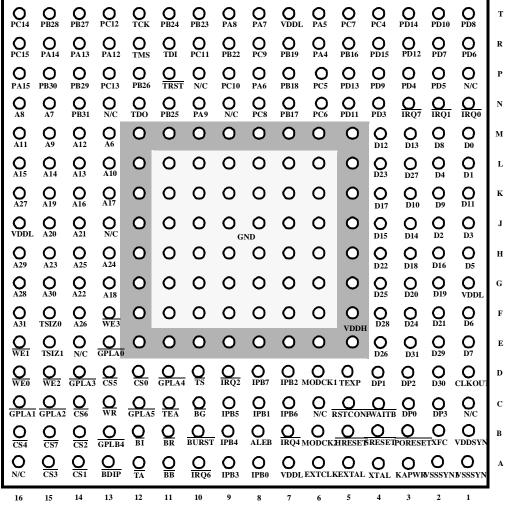

customers that are currently using the non-JEDEC pin numbering scheme, two sets of pinouts, JEDEC and non-JEDEC, are presented in this document.

Figure 62 shows the non-JEDEC pinout of the PBGA package as viewed from the top surface.

Figure 62. Pin Assignments for the PBGA (Top View)—non-JEDEC Standard

**Document Revision History**

## **10 Document Revision History**

Table 28 lists significant changes between revisions of this document.

### Table 28. Document Revision History

| Revision | Date    | Change                                                                                                                                                                                           |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 7/2005  | Added footnote 3 to Table 5 (previously Table 4.5) and deleted IOL limit.                                                                                                                        |

| 1        | 10/2002 | Added MPC850DSL. Corrected Figure 25 on page 34.                                                                                                                                                 |

| 0.2      | 04/2002 | Updated power numbers and added Rev. C                                                                                                                                                           |

| 0.1      | 11/2001 | Removed reference to 5 Volt tolerance capability on peripheral interface pins.<br>Replaced SI and IDL timing diagrams with better images. Updated to new<br>template, added this revision table. |

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK