# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 50MHz                                                                   |

| Co-Processors/DSP               | Communications; CPM                                                     |

| RAM Controllers                 | DRAM                                                                    |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10Mbps (1)                                                              |

| SATA                            | -                                                                       |

| USB                             | USB 1.x (1)                                                             |

| Voltage - I/O                   | 3.3V                                                                    |

| Operating Temperature           | -40°C ~ 95°C (TA)                                                       |

| Security Features               | -                                                                       |

| Package / Case                  | 256-BBGA                                                                |

| Supplier Device Package         | 256-PBGA (23x23)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/xpc850cvr50bur2 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# NP,

# 2 Features

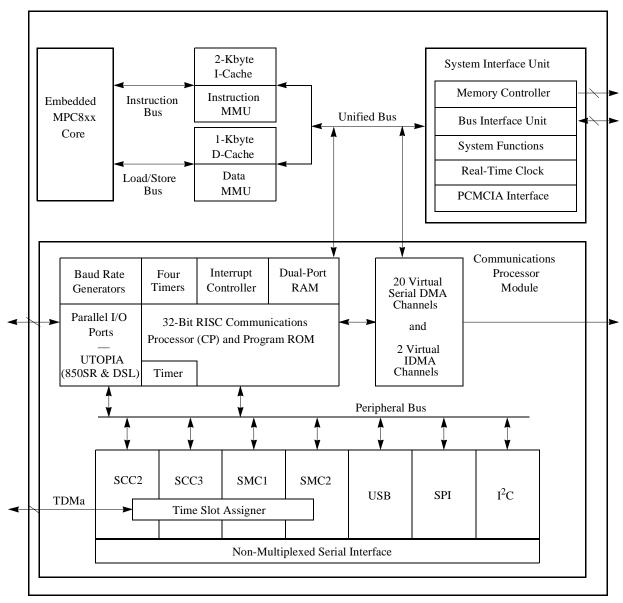

Figure 1 is a block diagram of the MPC850, showing its major components and the relationships among those components:

Figure 1. MPC850 Microprocessor Block Diagram

The following list summarizes the main features of the MPC850:

- Embedded single-issue, 32-bit MPC8xx core (implementing the PowerPC architecture) with thirty-two 32-bit general-purpose registers (GPRs)

- Performs branch folding and branch prediction with conditional prefetch, but without conditional execution

Features

- 2-Kbyte instruction cache and 1-Kbyte data cache (Harvard architecture)

- Caches are two-way, set-associative

- Physically addressed

- Cache blocks can be updated with a 4-word line burst

- Least-recently used (LRU) replacement algorithm

- Lockable one-line granularity

- Memory management units (MMUs) with 8-entry translation lookaside buffers (TLBs) and fully-associative instruction and data TLBs

- MMUs support multiple page sizes of 4 Kbytes, 16 Kbytes, 256 Kbytes, 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and eight protection groups

- Advanced on-chip emulation debug mode

- Data bus dynamic bus sizing for 8, 16, and 32-bit buses

- Supports traditional 68000 big-endian, traditional x86 little-endian and modified little-endian memory systems

- Twenty-six external address lines

- Completely static design (0–80 MHz operation)

- System integration unit (SIU)

- Hardware bus monitor

- Spurious interrupt monitor

- Software watchdog

- Periodic interrupt timer

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Memory controller (eight banks)

- Glueless interface to DRAM single in-line memory modules (SIMMs), synchronous DRAM (SDRAM), static random-access memory (SRAM), electrically programmable read-only memory (EPROM), flash EPROM, etc.

- Memory controller programmable to support most size and speed memory interfaces

- Boot chip-select available at reset (options for 8, 16, or 32-bit memory)

- Variable block sizes, 32 Kbytes to 256 Mbytes

- Selectable write protection

- On-chip bus arbiter supports one external bus master

- Special features for burst mode support

- General-purpose timers

- Four 16-bit timers or two 32-bit timers

- Separate power supply input to operate internal logic at 2.2 V when operating at or below 25 MHz

- Can be dynamically shifted between high frequency (3.3 V internal) and low frequency (2.2 V internal) operation

- Debug interface

(GND = 0V)

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- The MPC850 can compare using the =,  $\neq$ , <, and > conditions to generate watchpoints

- Each watchpoint can generate a breakpoint internally

- 3.3-V operation with 5-V TTL compatibility on all general purpose I/O pins.

# 3 Electrical and Thermal Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC850. Table 2 provides the maximum ratings.

| Rating                            | Symbol           | Value                                      | Unit |

|-----------------------------------|------------------|--------------------------------------------|------|

| Supply voltage                    | VDDH             | -0.3 to 4.0                                | V    |

|                                   | VDDL             | -0.3 to 4.0                                | V    |

|                                   | KAPWR            | -0.3 to 4.0                                | V    |

|                                   | VDDSYN           | -0.3 to 4.0                                | V    |

| Input voltage <sup>1</sup>        | V <sub>in</sub>  | GND-0.3 to VDDH + 2.5 V                    | V    |

| Junction temperature <sup>2</sup> | Тј               | 0 to 95 (standard)<br>-40 to 95 (extended) | °C   |

| Storage temperature range         | T <sub>stg</sub> | -55 to +150                                | °C   |

| Table 2. Maximum Ra |

|---------------------|

|---------------------|

<sup>1</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. CAUTION: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction

applies to power-up and normal operation (that is, if the MPC850 is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>2</sup> The MPC850, a high-frequency device in a BGA package, does not provide a guaranteed maximum ambient temperature. Only maximum junction temperature is guaranteed. It is the responsibility of the user to consider power dissipation and thermal management. Junction temperature ratings are the same regardless of frequency rating of the device.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ). Table 3 provides the package thermal characteristics for the MPC850.

|      |                                                                                                                         | 50 MHz 66 MHz |       | 80 MHz |       |       | Cap Load | 11    |                    |      |

|------|-------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------|-------|-------|----------|-------|--------------------|------|

| Num  | Characteristic                                                                                                          | Min           | Max   | Min    | Max   | Min   | Мах      | FFACT | (default<br>50 pF) | Unit |

| B9   | CLKOUT to A[6–31] RD/WR,<br>BURST, D[0–31], DP[0–3],<br>TSIZ[0–1], REG, RSV, AT[0–3],<br>PTR high-Z                     | 5.00          | 11.75 | 7.58   | 14.33 | 6.25  | 13.00    | 0.250 | 50.00              | ns   |

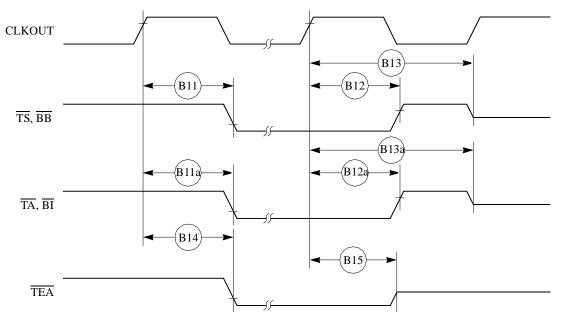

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion                                                                   | 5.00          | 11.00 | 7.58   | 13.58 | 6.25  | 12.25    | 0.250 | 50.00              | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion,<br>(When driven by the memory<br>controller or PCMCIA interface) | 2.50          | 9.25  | 2.50   | 9.25  | 2.50  | 9.25     | —     | 50.00              | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation                                                                    | 5.00          | 11.75 | 7.58   | 14.33 | 6.25  | 13.00    | 0.250 | 50.00              | ns   |

| B12a | CLKOUT to TA, BI negation<br>(when driven by the memory<br>controller or PCMCIA interface)                              | 2.50          | 11.00 | 2.50   | 11.00 | 2.50  | 11.00    | —     | 50.00              | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ high-Z                                                                      | 5.00          | 19.00 | 7.58   | 21.58 | 6.25  | 20.25    | 0.250 | 50.00              | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ high-Z,<br>(when driven by the memory<br>controller or PCMCIA interface)    | 2.50          | 15.00 | 2.50   | 15.00 | 2.50  | 15.00    | —     | 50.00              | ns   |

| B14  | CLKOUT to $\overline{TEA}$ assertion                                                                                    | 2.50          | 10.00 | 2.50   | 10.00 | 2.50  | 10.00    | —     | 50.00              | ns   |

| B15  | CLKOUT to TEA high-Z                                                                                                    | 2.50          | 15.00 | 2.50   | 15.00 | 2.50  | 15.00    | —     | 50.00              | ns   |

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT(setup time) <sup>5</sup>                                | 9.75          | —     | 9.75   | —     | 9.75  | —        | —     | 50.00              | ns   |

| B16a | TEA, KR, RETRY, valid to CLKOUT (setup time) <sup>5</sup>                                                               | 10.00         | —     | 10.00  | —     | 10.00 | —        | —     | 50.00              | ns   |

| B16b | $\overline{\text{BB}}$ , $\overline{\text{BG}}$ , $\overline{\text{BR}}$ valid to CLKOUT (setup time) <sup>6</sup>      | 8.50          | _     | 8.50   | —     | 8.50  | —        | _     | 50.00              | ns   |

| B17  | $\frac{\text{CLKOUT to TA, TEA, BI, BB,}}{\text{BG, BR valid (Hold time).}^5}$                                          | 1.00          |       | 1.00   | —     | 1.00  | _        | _     | 50.00              | ns   |

| B17a | CLKOUT to KR, RETRY, except<br>TEA valid (hold time)                                                                    | 2.00          | —     | 2.00   | —     | 2.00  | —        | _     | 50.00              | ns   |

| B18  | D[0–31], DP[0–3] valid to<br>CLKOUT rising edge (setup<br>time) <sup>7</sup>                                            | 6.00          | _     | 6.00   |       | 6.00  |          | _     | 50.00              | ns   |

| B19  | CLKOUT rising edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>7</sup>                                             | 1.00          | _     | 1.00   |       | 1.00  |          | _     | 50.00              | ns   |

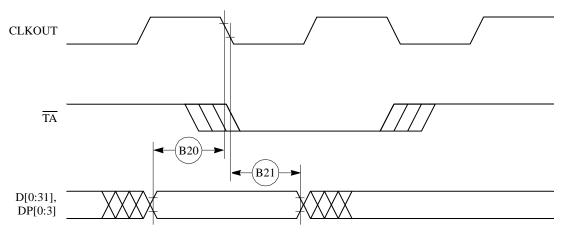

| B20  | D[0–31], DP[0–3] valid to<br>CLKOUT falling edge (setup<br>time) <sup>8</sup>                                           | 4.00          |       | 4.00   |       | 4.00  | —        | _     | 50.00              | ns   |

| B21  | CLKOUT falling edge to<br>D[0–31], DP[0–3] valid (hold<br>time) <sup>8</sup>                                            | 2.00          | —     | 2.00   |       | 2.00  | —        | —     | —                  |      |

| Table 6. | <b>Bus Operation Timing</b> | <sup>1</sup> (continued) |

|----------|-----------------------------|--------------------------|

|----------|-----------------------------|--------------------------|

| [    |                                                                                                                                             |               |       |        |       |       |                      |       |        |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------|-------|-------|----------------------|-------|--------|----|

| Num  | Characteristic                                                                                                                              | 50 MHz 66 MHz |       | 80 MHz |       | FFACT | Cap Load<br>(default | Unit  |        |    |

| -    |                                                                                                                                             | Min           | Max   | Min    | Max   | Min   | Max                  | _     | 50 pF) |    |

| B28c | CLKOUT falling edge to<br>WE[0–3] negated GPCM write<br>access TRLX = 0,1 CSNT = 1<br>write access TRLX = 0, CSNT =<br>1, EBDF = 1          | 7.00          | 14.00 | 11.00  | 18.00 | 9.00  | 16.00                | 0.375 | 50.00  | ns |

| B28d | CLKOUT falling edge to $\overline{CS}$<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 1               | _             | 14.00 | _      | 18.00 | _     | 16.00                | 0.375 | 50.00  | ns |

| B29  | $\overline{WE[0-3]}$ negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, CSNT = 0                                                   | 3.00          | _     | 6.00   | _     | 4.00  | _                    | 0.250 | 50.00  | ns |

| B29a | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 0 CSNT = 1,<br>EBDF = 0                                          | 8.00          | _     | 13.00  | _     | 11.00 | _                    | 0.500 | 50.00  | ns |

| B29b | CS negated to D[0–31],<br>DP[0–3], high-Z GPCM write<br>access, ACS = 00, TRLX = 0 &<br>CSNT = 0                                            | 3.00          |       | 6.00   |       | 4.00  |                      | 0.250 | 50.00  | ns |

| B29c | $\overline{\text{CS}}$ negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 8.00          |       | 13.00  |       | 11.00 |                      | 0.500 | 50.00  | ns |

| B29d | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>EBDF = 0                                         | 28.00         |       | 43.00  |       | 36.00 |                      | 1.500 | 50.00  | ns |

| B29e | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0                     | 28.00         |       | 43.00  |       | 36.00 |                      | 1.500 | 50.00  | ns |

| B29f | WE[0–3] negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                          | 5.00          |       | 9.00   |       | 7.00  |                      | 0.375 | 50.00  | ns |

| B29g | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1                      | 5.00          |       | 9.00   |       | 7.00  |                      | 0.375 | 50.00  | ns |

| Table 6. | <b>Bus Operation</b> | Timing <sup>1</sup> | (continued) |

|----------|----------------------|---------------------|-------------|

|----------|----------------------|---------------------|-------------|

| Num | Characteristic                                          | 50 MHz |     | 66 MHz |     | 80 MHz |     | FFACT | Cap Load<br>(default | Unit |

|-----|---------------------------------------------------------|--------|-----|--------|-----|--------|-----|-------|----------------------|------|

| Num | Unaracteristic                                          | Min    | Max | Min    | Max | Min    | Max | 11401 | 50 pF)               | Unit |

| B42 | CLKOUT rising edge to $\overline{TS}$ valid (hold time) | 2.00   | _   | 2.00   | _   | 2.00   | _   | _     | 50.00                | ns   |

| B43 | AS negation to memory controller signals negation       | _      | TBD | _      | TBD | TBD    | _   | —     | 50.00                | ns   |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

The minima provided assume a 0 pF load, whereas maxima assume a 50pF load. For frequencies not marked on the part, new bus timing must be calculated for all frequency-dependent AC parameters. Frequency-dependent AC parameters are those with an entry in the FFactor column. AC parameters without an FFactor entry do not need to be calculated and can be taken directly from the frequency column corresponding to the frequency marked on the part. The following equations should be used in these calculations.

For a frequency F, the following equations should be applied to each one of the above parameters: For minima:

$$D = \frac{FFACTOR \times 1000}{F} + (D_{50} - 20 \times FFACTOR)$$

For maxima:

$$D = \frac{FFACTOR \times 1000}{F} + \frac{(D_{50} - 20 \times FFACTOR)}{F} + \frac{1 ns(CAP \ LOAD - 50) / 10}{F}$$

where:

D is the parameter value to the frequency required in ns

F is the operation frequency in MHz

D<sub>50</sub> is the parameter value defined for 50 MHz

CAP LOAD is the capacitance load on the signal in question.

FFACTOR is the one defined for each of the parameters in the table.

- <sup>2</sup> Phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed value.

- <sup>3</sup> If the rate of change of the frequency of EXTAL is slow (i.e. it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (i.e., it does not stay at an extreme value for a long time) then the maximum allowed jitter on EXTAL can be up to 2%.

- <sup>4</sup> The timing for BR output is relevant when the MPC850 is selected to work with external bus arbiter. The timing for BG output is relevant when the MPC850 is selected to work with internal bus arbiter.

- <sup>5</sup> The setup times required for TA, TEA, and BI are relevant only when they are supplied by an external device (and not when the memory controller or the PCMCIA interface drives them).

- <sup>6</sup> The timing required for BR input is relevant when the MPC850 is selected to work with the internal bus arbiter. The timing for BG input is relevant when the MPC850 is selected to work with the external bus arbiter.

- <sup>7</sup> The D[0–31] and DP[0–3] input timings B20 and B21 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

- <sup>8</sup> The D[0:31] and DP[0:3] input timings B20 and B21 refer to the falling edge of CLKOUT. This timing is valid only for read accesses controlled by chip-selects controlled by the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.

- <sup>9</sup> The timing B30 refers to  $\overline{CS}$  when ACS = '00' and to  $\overline{WE[0:3]}$  when CSNT = '0'.

- <sup>10</sup> The signal UPWAIT is considered asynchronous to CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals.

- <sup>11</sup> The  $\overline{\text{AS}}$  signal is considered asynchronous to CLKOUT.

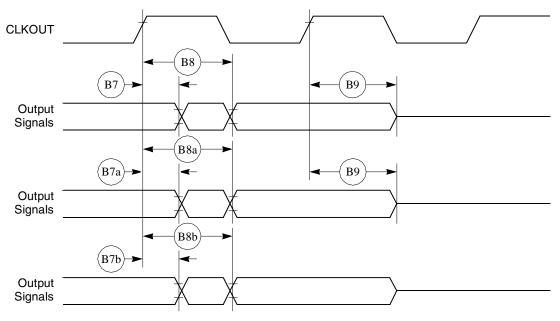

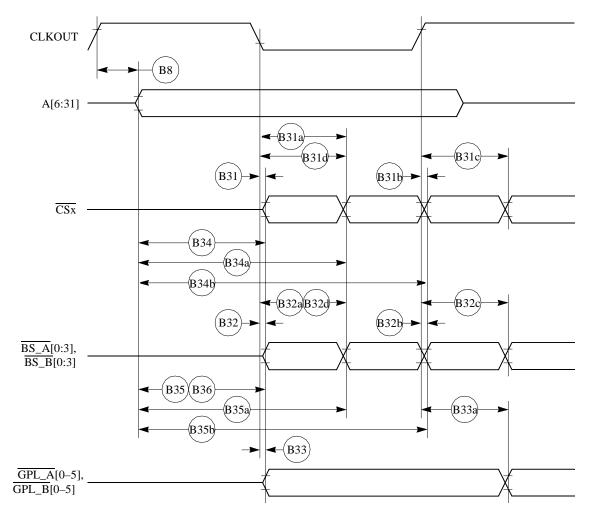

Figure 4 provides the timing for the synchronous output signals.

Figure 4. Synchronous Output Signals Timing

Figure 5 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 5. Synchronous Active Pullup and Open-Drain Outputs Signals Timing

Figure 8 provides the timing for the input data controlled by the UPM in the memory controller.

Figure 8. Input Data Timing when Controlled by UPM in the Memory Controller

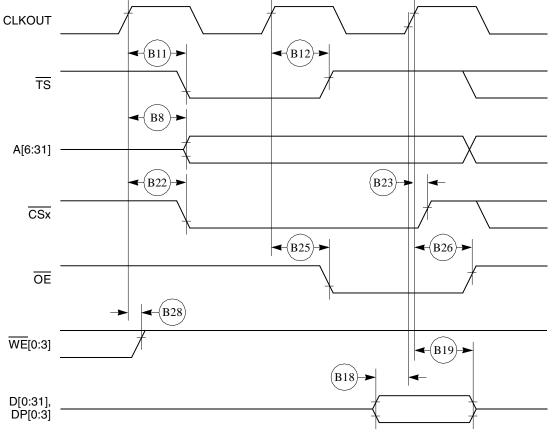

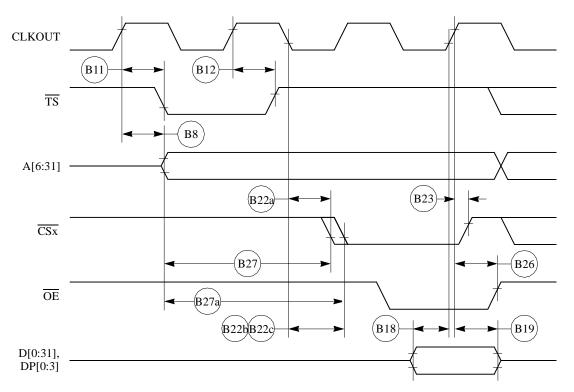

Figure 9 through Figure 12 provide the timing for the external bus read controlled by various GPCM factors.

Figure 9. External Bus Read Timing (GPCM Controlled—ACS = 00)

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 1, ACS = 10, ACS = 11)

Figure 16 provides the timing for the external bus controlled by the UPM.

Figure 16. External Bus Timing (UPM Controlled Signals)

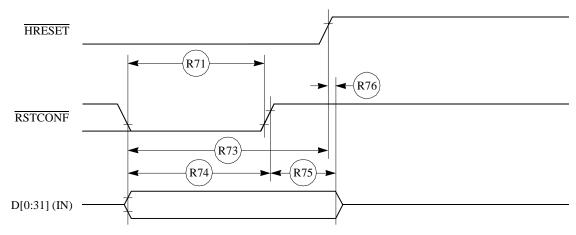

Figure 31 shows the reset timing for the data bus configuration.

Figure 31. Reset Timing—Configuration from Data Bus

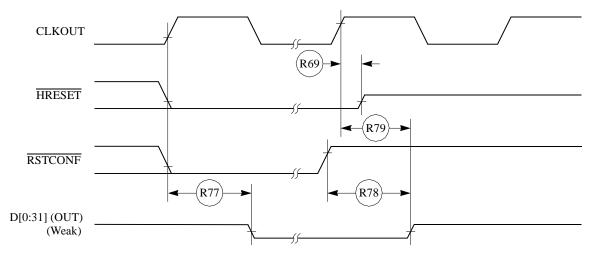

Figure 32 provides the reset timing for the data bus weak drive during configuration.

Figure 32. Reset Timing—Data Bus Weak Drive during Configuration

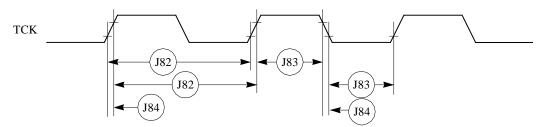

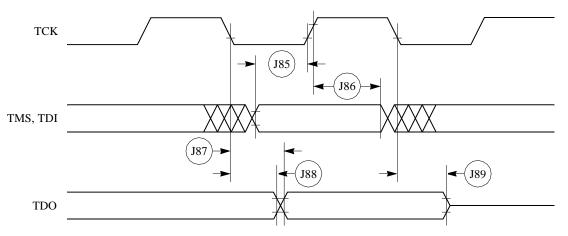

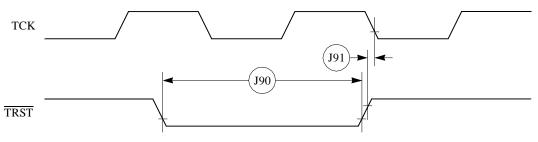

IEEE 1149.1 Electrical Specifications

Figure 34. JTAG Test Clock Input Timing

Figure 35. JTAG Test Access Port Timing Diagram

Figure 36. JTAG TRST Timing Diagram

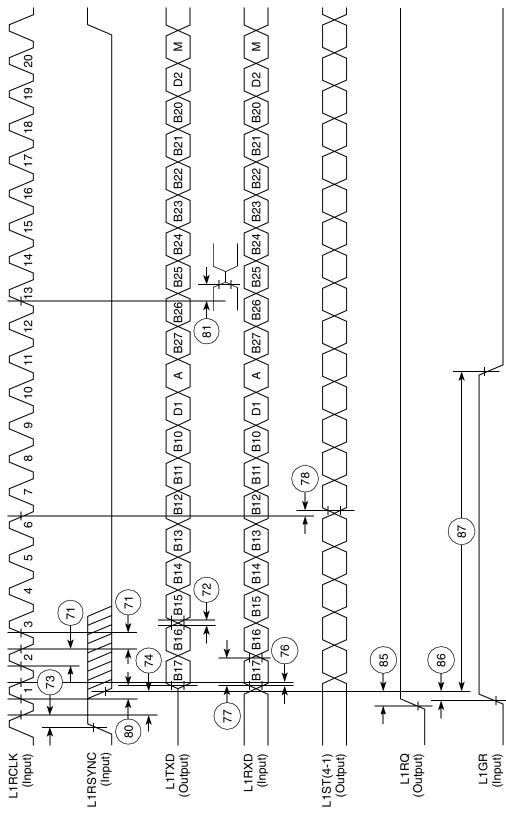

Figure 49. IDL Timing

1. This delay is equal to an integer number of character-length clocks.

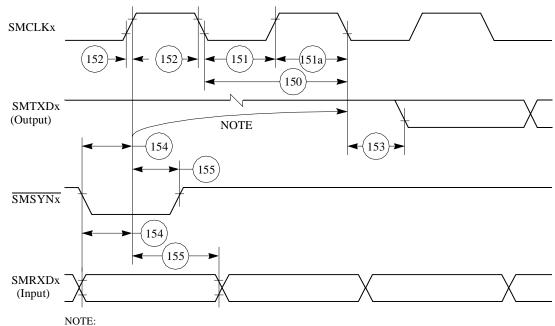

### Figure 56. SMC Transparent Timing Diagram

# 8.9 SPI Master AC Electrical Specifications

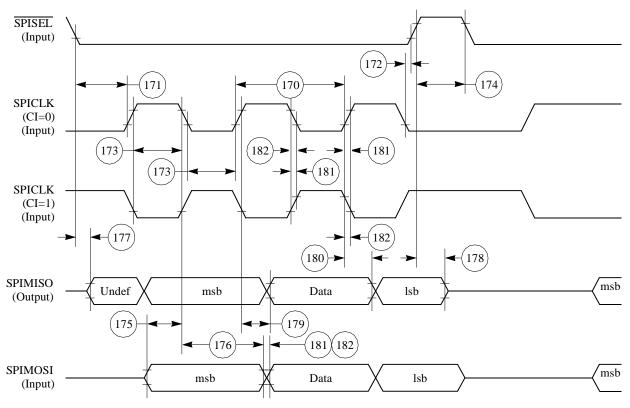

Table 22 provides the SPI master timings as shown in Figure 57 and Figure 58.

| Num | Characteristic                      | All Frequ | Unit  |                  |

|-----|-------------------------------------|-----------|-------|------------------|

| Num | Characteristic                      | Min       | Max   | Unit             |

| 160 | MASTER cycle time                   | 4         | 1024  | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time | 2         | 512   | t <sub>cyc</sub> |

| 162 | MASTER data setup time (inputs)     | 50.00     | _     | ns               |

| 163 | Master data hold time (inputs)      | 0.00      | _     | ns               |

| 164 | Master data valid (after SCK edge)  | —         | 20.00 | ns               |

| 165 | Master data hold time (outputs)     | 0.00      | _     | ns               |

| 166 | Rise time output                    | —         | 15.00 | ns               |

| 167 | Fall time output                    | —         | 15.00 | ns               |

### Table 22. SPI Master Timing

**CPM Electrical Characteristics**

Figure 60. SPI Slave (CP = 1) Timing Diagram

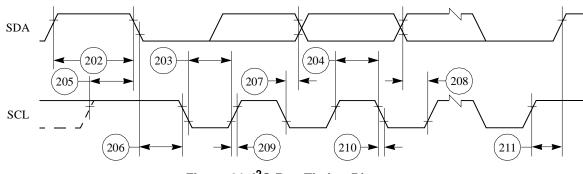

# 8.11 I<sup>2</sup>C AC Electrical Specifications

Table 24 provides the  $I^2C$  (SCL < 100 KHz) timings.

| Table 24. | I <sup>2</sup> C Timing | (SCL < 100 KHz) |

|-----------|-------------------------|-----------------|

|-----------|-------------------------|-----------------|

| Num | Characteristic                            | All Frequ | Unit   |      |

|-----|-------------------------------------------|-----------|--------|------|

| Num |                                           |           | Мах    | Unit |

| 200 | SCL clock frequency (slave)               | 0.00      | 100.00 | KHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.50      | 100.00 | KHz  |

| 202 | Bus free time between transmissions       | 4.70      | _      | μs   |

| 203 | Low period of SCL                         | 4.70      | _      | μs   |

| 204 | High period of SCL                        | 4.00      |        | μs   |

| 205 | Start condition setup time                | 4.70      | _      | μs   |

| 206 | Start condition hold time                 | 4.00      |        | μs   |

| 207 | Data hold time                            | 0.00      |        | μs   |

| 208 | Data setup time                           | 250.00    |        | ns   |

| 209 | SDL/SCL rise time                         | _         | 1.00   | μs   |

**CPM Electrical Characteristics**

| Num | Characteristic            | All Frequ | Unit   |      |

|-----|---------------------------|-----------|--------|------|

| Num | onaracteristic            | Min       | Мах    | onit |

| 210 | SDL/SCL fall time         | _         | 300.00 | ns   |

| 211 | Stop condition setup time | 4.70      | _      | μs   |

Table 24. I<sup>2</sup>C Timing (SCL < 100 KHz) (CONTINUED)

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

Table 25 provides the  $I^2C$  (SCL > 100 KHz) timings.

Table 25.  $I^2C$  Timing (SCL > 100 KHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| num |                                           |            | Min             | Max           | Unit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202 | Bus free time between transmissions       |            | 1/(2.2 * fSCL)  | —             | s    |

| 203 | Low period of SCL                         |            | 1/(2.2 * fSCL)  | —             | s    |

| 204 | High period of SCL                        |            | 1/(2.2 * fSCL)  | —             | s    |

| 205 | Start condition setup time                |            | 1/(2.2 * fSCL)  | _             | s    |

| 206 | Start condition hold time                 |            | 1/(2.2 * fSCL)  | _             | s    |

| 207 | Data hold time                            |            | 0               | _             | s    |

| 208 | Data setup time                           |            | 1/(40 * fSCL)   | _             | s    |

| 209 | SDL/SCL rise time                         |            | —               | 1/(10 * fSCL) | s    |

| 210 | SDL/SCL fall time                         |            | —               | 1/(33 * fSCL) | s    |

| 211 | Stop condition setup time                 |            | 1/2(2.2 * fSCL) | _             | S    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

Figure 61 shows the  $I^2C$  bus timing.

Figure 61. I<sup>2</sup>C Bus Timing Diagram

# 9 Mechanical Data and Ordering Information

Table 26 provides information on the MPC850 derivative devices.

| Table 26. | <b>MPC850</b> | Family | / Derivatives |

|-----------|---------------|--------|---------------|

|-----------|---------------|--------|---------------|

| Device    | Ethernet Support | Number of SCCs <sup>1</sup> | 32-Channel HDLC<br>Support | 64-Channel HDLC<br>Support <sup>2</sup> |

|-----------|------------------|-----------------------------|----------------------------|-----------------------------------------|

| MPC850    | N/A              | One                         | N/A                        | N/A                                     |

| MPC850DE  | Yes              | Two                         | N/A                        | N/A                                     |

| MPC850SR  | Yes              | Two                         | N/A                        | Yes                                     |

| MPC850DSL | Yes              | Two                         | No                         | No                                      |

<sup>1</sup> Serial Communication Controller (SCC)

<sup>2</sup> 50 MHz version supports 64 time slots on a time division multiplexed line using one SCC

Table 27 identifies the packages and operating frequencies available for the MPC850.

Table 27. MPC850 Package/Frequency/Availability

| Package Type                                     | Frequency (MHz) | Temperature (Tj) | Order Number                                                            |

|--------------------------------------------------|-----------------|------------------|-------------------------------------------------------------------------|

| 256-Lead Plastic Ball Grid Array<br>(ZT suffix)  | 50              | 0°C to 95°C      | XPC850ZT50BU<br>XPC850DEZT50BU<br>XPC850SRZT50BU<br>XPC850DSLZT50BU     |

|                                                  | 66              | 0°C to 95°C      | XPC850ZT66BU<br>XPC850DEZT66BU<br>XPC850SRZT66BU                        |

|                                                  | 80              | 0°C to 95°C      | XPC850ZT80BU<br>XPC850DEZT80BU<br>XPC850SRZT80BU                        |

| 256-Lead Plastic Ball Grid Array<br>(CZT suffix) | 50              | -40°C to 95°C    | XPC850CZT50BU<br>XPC850DECZT50BU<br>XPC850SRCZT50BU<br>XPC850DSLCZT50BU |

|                                                  | 66              |                  | XPC850CZT66BU<br>XPC850DECZT66BU<br>XPC850SRCZT66BU                     |

|                                                  | 80              |                  | XPC850CZT80B<br>XPC850DECZT80B<br>XPC850SRCZT80B                        |

# 9.1 Pin Assignments and Mechanical Dimensions of the PBGA

The original pin numbering of the MPC850 conformed to a Freescale proprietary pin numbering scheme that has since been replaced by the JEDEC pin numbering standard for this package type. To support

**Document Revision History**

# **10 Document Revision History**

Table 28 lists significant changes between revisions of this document.

### Table 28. Document Revision History

| Revision | Date    | Change                                                                                                                                                                                           |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 7/2005  | Added footnote 3 to Table 5 (previously Table 4.5) and deleted IOL limit.                                                                                                                        |

| 1        | 10/2002 | Added MPC850DSL. Corrected Figure 25 on page 34.                                                                                                                                                 |

| 0.2      | 04/2002 | Updated power numbers and added Rev. C                                                                                                                                                           |

| 0.1      | 11/2001 | Removed reference to 5 Volt tolerance capability on peripheral interface pins.<br>Replaced SI and IDL timing diagrams with better images. Updated to new<br>template, added this revision table. |

**Document Revision History**

## THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

email: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC850EC Rev. 2 07/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2005.