Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                          |

|---------------------------------|--------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                 |

| Core Processor                  | MPC8xx                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 50MHz                                                                    |

| Co-Processors/DSP               | Communications; CPM                                                      |

| RAM Controllers                 | DRAM                                                                     |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10Mbps (1)                                                               |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 3.3V                                                                     |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                          |

| Security Features               | -                                                                        |

| Package / Case                  | 256-BGA                                                                  |

| Supplier Device Package         | 256-PBGA (23x23)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/xpc850dezt50bur2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

### Interrupts

- Eight external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Fifteen internal interrupt sources

- Programmable priority among SCCs and USB

- Programmable highest-priority request

- Single socket PCMCIA-ATA interface

- Master (socket) interface, release 2.1 compliant

- Single PCMCIA socket

- Supports eight memory or I/O windows

- Communications processor module (CPM)

- 32-bit, Harvard architecture, scalar RISC communications processor (CP)

- Protocol-specific command sets (for example, GRACEFUL STOP TRANSMIT stops transmission

after the current frame is finished or immediately if no frame is being sent and CLOSE RXBD

closes the receive buffer descriptor)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- Twenty serial DMA (SDMA) channels for the serial controllers, including eight for the four USB endpoints

- Three parallel I/O registers with open-drain capability

- Four independent baud-rate generators (BRGs)

- Can be connected to any SCC, SMC, or USB

- Allow changes during operation

- Autobaud support option

- Two SCCs (serial communications controllers)

- Ethernet/IEEE 802.3, supporting full 10-Mbps operation

- HDLC/SDLC<sup>TM</sup> (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk<sup>®</sup>

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

### **Features**

- QUICC multichannel controller (QMC) microcode features

- Up to 64 independent communication channels on a single SCC

- Arbitrary mapping of 0–31 channels to any of 0–31 TDM time slots

- Supports either transparent or HDLC protocols for each channel

- Independent TxBDs/Rx and event/interrupt reporting for each channel

- One universal serial bus controller (USB)

- Supports host controller and slave modes at 1.5 Mbps and 12 Mbps

- Two serial management controllers (SMCs)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division-multiplexed (TDM) channel

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- One I<sup>2</sup>C<sup>®</sup> (interprocessor-integrated circuit) port

- Supports master and slave modes

- Supports multimaster environment

- Time slot assigner

- Allows SCCs and SMCs to run in multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame syncs, clocking

- Allows dynamic changes

- Can be internally connected to four serial channels (two SCCs and two SMCs)

- Low-power support

- Full high: all units fully powered at high clock frequency

- Full low: all units fully powered at low clock frequency

- Doze: core functional units disabled except time base, decrementer, PLL, memory controller, real-time clock, and CPM in low-power standby

- Sleep: all units disabled except real-time clock and periodic interrupt timer. PLL is active for fast wake-up

- Deep sleep: all units disabled including PLL, except the real-time clock and periodic interrupt timer

- Low-power stop: to provide lower power dissipation

# 4 Thermal Characteristics

Table 3 shows the thermal characteristics for the MPC850.

**Table 3. Thermal Characteristics**

| Characteristic                                | Symbol               | Value           | Unit |

|-----------------------------------------------|----------------------|-----------------|------|

| Thermal resistance for BGA <sup>1</sup>       | $\theta_{JA}$        | 40 <sup>2</sup> | °C/W |

|                                               | $\theta_{JA}$        | 31 <sup>3</sup> | °C/W |

|                                               | $\theta_{JA}$        | 24 <sup>4</sup> | °C/W |

| Thermal Resistance for BGA (junction-to-case) | $\theta_{\text{JC}}$ | 8               | °C/W |

For more information on the design of thermal vias on multilayer boards and BGA layout considerations in general, refer to AN-1231/D, Plastic Ball Grid Array Application Note available from your local Freescale sales office.

$$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA})$$

$$P_{D} = (V_{DD} \bullet I_{DD}) + P_{I/O}$$

P<sub>I/O</sub> is the power dissipation on pins

Table 4 provides power dissipation information.

Table 4. Power Dissipation (P<sub>D</sub>)

| Characteristic              | Frequency (MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|-----------------------------|-----------------|----------------------|----------------------|------|

| Power Dissipation           | 33              | TBD                  | 515                  | mW   |

| All Revisions<br>(1:1) Mode | 40              | TBD                  | 590                  | mW   |

| (111) 111040                | 50              | TBD                  | 725                  | mW   |

<sup>1</sup> Typical power dissipation is measured at 3.3V

Table 5 provides the DC electrical characteristics for the MPC850.

**Table 5. DC Electrical Specifications**

| Characteristic                                                                                | Symbol                       | Min   | Max   | Unit |

|-----------------------------------------------------------------------------------------------|------------------------------|-------|-------|------|

| Operating voltage at 40 MHz or less                                                           | VDDH, VDDL,<br>KAPWR, VDDSYN | 3.0   | 3.6   | V    |

| Operating voltage at 40 MHz or higher                                                         | VDDH, VDDL,<br>KAPWR, VDDSYN | 3.135 | 3.465 | V    |

| Input high voltage (address bus, data bus, EXTAL, EXTCLK, and all bus control/status signals) | VIH                          | 2.0   | 3.6   | ٧    |

| Input high voltage (all general purpose I/O and peripheral pins)                              | VIH                          | 2.0   | 5.5   | V    |

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

<sup>&</sup>lt;sup>2</sup> Assumes natural convection and a single layer board (no thermal vias).

Assumes natural convection, a multilayer board with thermal vias<sup>4</sup>, 1 watt MPC850 dissipation, and a board temperature rise of 20°C above ambient.

<sup>&</sup>lt;sup>4</sup> Assumes natural convection, a multilayer board with thermal vias<sup>4</sup>, 1 watt MPC850 dissipation, and a board temperature rise of 13°C above ambient.

<sup>&</sup>lt;sup>2</sup> Maximum power dissipation is measured at 3.65 V

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Num  | Characteristic                                                                                      | 50 [  | ИНz   | 66 [  | ИНz   | 1 08  | ИНz   | FEACT | Cap Load           | Hait |

|------|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|------|

| Num  | Characteristic                                                                                      | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit |

| В9   | CLKOUT to A[6–31] RD/WR,<br>BURST, D[0–31], DP[0–3],<br>TSIZ[0–1], REG, RSV, AT[0–3],<br>PTR high-Z | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B11  | CLKOUT to TS, BB assertion                                                                          | 5.00  | 11.00 | 7.58  | 13.58 | 6.25  | 12.25 | 0.250 | 50.00              | ns   |

| B11a | CLKOUT to TA, BI assertion,<br>(When driven by the memory<br>controller or PCMCIA interface)        | 2.50  | 9.25  | 2.50  | 9.25  | 2.50  | 9.25  | _     | 50.00              | ns   |

| B12  | CLKOUT to TS, BB negation                                                                           | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B12a | CLKOUT to TA, BI negation<br>(when driven by the memory<br>controller or PCMCIA interface)          | 2.50  | 11.00 | 2.50  | 11.00 | 2.50  | 11.00 | _     | 50.00              | ns   |

| B13  | CLKOUT to TS, BB high-Z                                                                             | 5.00  | 19.00 | 7.58  | 21.58 | 6.25  | 20.25 | 0.250 | 50.00              | ns   |

| B13a | CLKOUT to TA, BI high-Z,<br>(when driven by the memory<br>controller or PCMCIA interface)           | 2.50  | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | _     | 50.00              | ns   |

| B14  | CLKOUT to TEA assertion                                                                             | 2.50  | 10.00 | 2.50  | 10.00 | 2.50  | 10.00 | _     | 50.00              | ns   |

| B15  | CLKOUT to TEA high-Z                                                                                | 2.50  | 15.00 | 2.50  | 15.00 | 2.50  | 15.00 | _     | 50.00              | ns   |

| B16  | TA, BI valid to CLKOUT(setup time) 5                                                                | 9.75  | _     | 9.75  | _     | 9.75  | _     | _     | 50.00              | ns   |

| B16a | TEA, KR, RETRY, valid to CLKOUT (setup time) 5                                                      | 10.00 | _     | 10.00 | _     | 10.00 | _     | _     | 50.00              | ns   |

| B16b | BB, BG, BR valid to CLKOUT (setup time) 6                                                           | 8.50  | _     | 8.50  | _     | 8.50  | _     | _     | 50.00              | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (Hold time).5                                               | 1.00  | _     | 1.00  | _     | 1.00  |       | _     | 50.00              | ns   |

| B17a | CLKOUT to KR, RETRY, except TEA valid (hold time)                                                   | 2.00  | _     | 2.00  | _     | 2.00  | _     | _     | 50.00              | ns   |

| B18  | D[0–31], DP[0–3] valid to CLKOUT rising edge (setup time) <sup>7</sup>                              | 6.00  | _     | 6.00  | _     | 6.00  | _     | _     | 50.00              | ns   |

| B19  | CLKOUT rising edge to D[0–31], DP[0–3] valid (hold time) <sup>7</sup>                               | 1.00  | _     | 1.00  | _     | 1.00  | _     | _     | 50.00              | ns   |

| B20  | D[0-31], DP[0-3] valid to<br>CLKOUT falling edge (setup<br>time) <sup>8</sup>                       | 4.00  | _     | 4.00  | _     | 4.00  | _     | _     | 50.00              | ns   |

| B21  | CLKOUT falling edge to D[0-31], DP[0-3] valid (hold time) <sup>8</sup>                              | 2.00  | —     | 2.00  | _     | 2.00  | _     | _     | _                  | _    |

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nivers | Oh avaataviatia                                                                                                             | 50 I  | MHz   | 66 1  | ИНz   | 80 1  | ИНz   | FFACT | Cap Load           | I I m ! A |

|--------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|-----------|

| Num    | Characteristic                                                                                                              | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit      |

| B22    | CLKOUT rising edge to CS asserted GPCM ACS = 00                                                                             | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns        |

| B22a   | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0,1                                            | _     | 8.00  | _     | 8.00  | _     | 8.00  | _     | 50.00              | ns        |

| B22b   | CLKOUT falling edge to CS asserted GPCM ACS = 11, TRLX = 0, EBDF = 0                                                        | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns        |

| B22c   | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 11, TRLX = 0, EBDF = 1                                    | 7.00  | 14.00 | 11.00 | 18.00 | 9.00  | 16.00 | 0.375 | 50.00              | ns        |

| B23    | CLKOUT rising edge to $\overline{\text{CS}}$ negated GPCM read access, GPCM write access ACS = 00, TRLX = 0 & CSNT = 0      | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | _     | 50.00              | ns        |

| B24    | A[6-31] to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0.                                                         | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns        |

| B24a   | A[6–31] to $\overline{\text{CS}}$ asserted GPCM<br>ACS = 11, TRLX = 0                                                       | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns        |

| B25    | CLKOUT rising edge to OE, WE[0-3] asserted                                                                                  | _     | 9.00  | _     | 9.00  | _     | 9.00  | _     | 50.00              | ns        |

| B26    | CLKOUT rising edge to OE negated                                                                                            | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | _     | 50.00              | ns        |

| B27    | A[6–31] to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 1                                                          | 23.00 | _     | 36.00 | _     | 29.00 | _     | 1.250 | 50.00              | ns        |

| B27a   | A[6–31] to $\overline{\text{CS}}$ asserted GPCM<br>ACS = 11, TRLX = 1                                                       | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns        |

| B28    | CLKOUT rising edge to WE[0-3] negated GPCM write access CSNT = 0                                                            | _     | 9.00  | _     | 9.00  | _     | 9.00  | _     | 50.00              | ns        |

| B28a   | CLKOUT falling edge to WE[0-3] negated GPCM write access TRLX = 0,1 CSNT = 1, EBDF = 0                                      | 5.00  | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250 | 50.00              | ns        |

| B28b   | CLKOUT falling edge to $\overline{\text{CS}}$ negated GPCM write access TRLX = 0,1 CSNT = 1, ACS = 10 or ACS = 11, EBDF = 0 | _     | 12.00 | _     | 14.00 | _     | 13.00 | 0.250 | 50.00              | ns        |

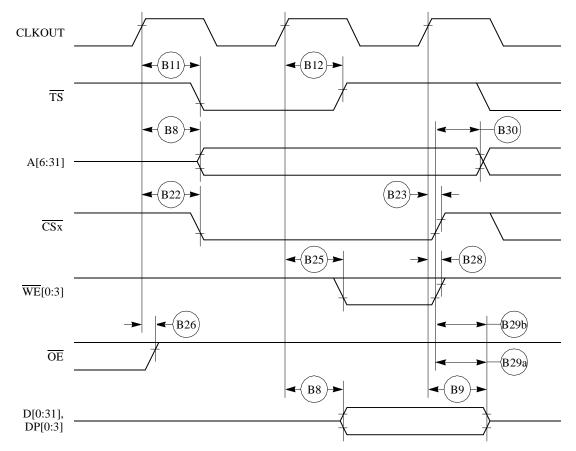

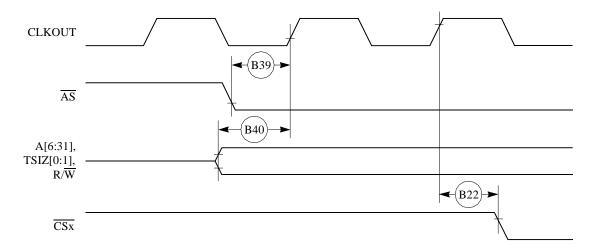

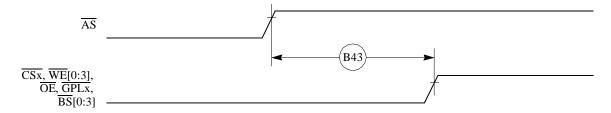

Figure 13 through Figure 15 provide the timing for the external bus write controlled by various GPCM factors.

Figure 13. External Bus Write Timing (GPCM Controlled—TRLX = 0, CSNT = 0)

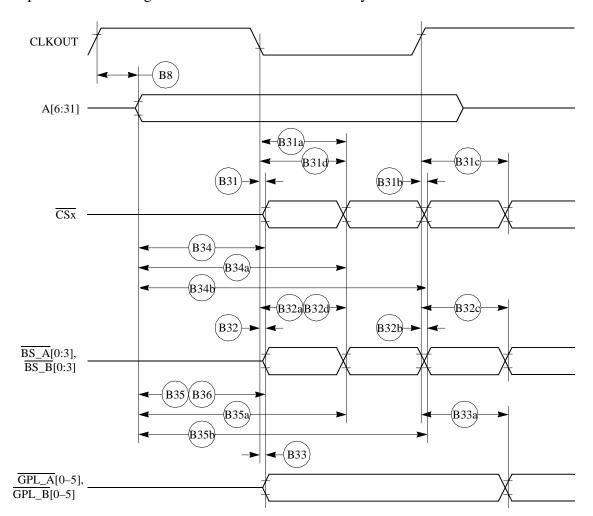

Figure 16 provides the timing for the external bus controlled by the UPM.

Figure 16. External Bus Timing (UPM Controlled Signals)

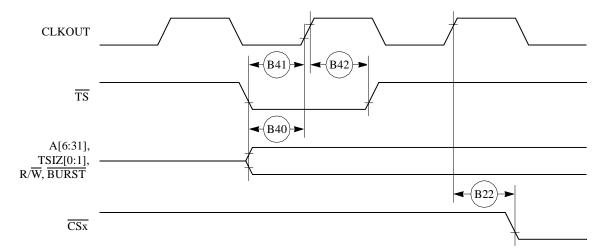

Figure 19 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 19. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 20 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 20. Asynchronous External Master Memory Access Timing (GPCM Controlled—ACS = 00)

Figure 21 provides the timing for the asynchronous external master control signals negation.

Figure 21. Asynchronous External Master—Control Signals Negation Timing

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

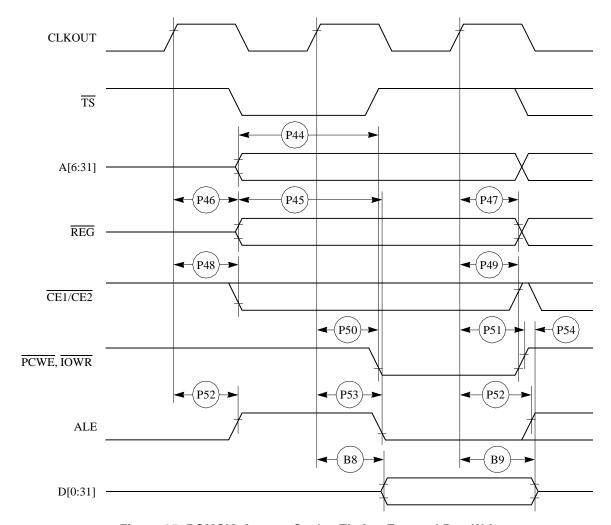

## Table 8 shows the PCMCIA timing for the MPC850.

## **Table 8. PCMCIA Timing**

| Num | Characteristic                                  | 501   | ЛНz   | 661   | ЛHz   | 80 1  | ИНz   | FFACTOR | Unit  |

|-----|-------------------------------------------------|-------|-------|-------|-------|-------|-------|---------|-------|

| Num | iii Gilai astoristis                            |       | Max   | Min   | Max   | Min   | Max   | FFACION | Oiiit |

| P44 | A[6–31], REG valid to PCMCIA strobe asserted. 1 | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750   | ns    |

| P45 | A[6–31], REG valid to ALE negation.1            | 18.00 | _     | 28.00 | _     | 23.00 | _     | 1.000   | ns    |

| P46 | CLKOUT to REG valid                             | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P47 | CLKOUT to REG Invalid.                          | 6.00  | _     | 9.00  | _     | 7.00  | _     | 0.250   | ns    |

| P48 | CLKOUT to CE1, CE2 asserted.                    | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   |       |

| P49 | CLKOUT to CE1, CE2 negated.                     | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P50 | CLKOUT to PCOE, IORD, PCWE, IOWR assert time.   | _     | 11.00 | _     | 11.00 | _     | 11.00 | _       | ns    |

| P51 | CLKOUT to PCOE, IORD, PCWE, IOWR negate time.   | 2.00  | 11.00 | 2.00  | 11.00 | 2.00  | 11.00 | _       | ns    |

| P52 | CLKOUT to ALE assert time                       | 5.00  | 13.00 | 8.00  | 16.00 | 6.00  | 14.00 | 0.250   | ns    |

| P53 | CLKOUT to ALE negate time                       | _     | 13.00 | _     | 16.00 | _     | 14.00 | 0.250   | ns    |

| P54 | PCWE, IOWR negated to D[0-31] invalid.1         | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250   | ns    |

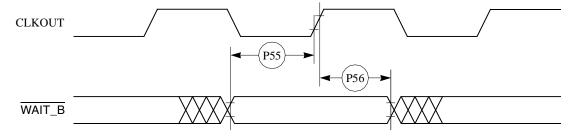

| P55 | WAIT_B valid to CLKOUT rising edge.1            | 8.00  | _     | 8.00  | _     | 8.00  | _     | _       | ns    |

| P56 | CLKOUT rising edge to WAIT_B invalid.1          | 2.00  | _     | 2.00  | _     | 2.00  | _     | _       | ns    |

<sup>1</sup> PSST = 1. Otherwise add PSST times cycle time.

These synchronous timings define when the WAIT\_B signal is detected in order to freeze (or relieve) the PCMCIA current cycle. The WAIT\_B assertion will be effective only if it is detected 2 cycles before the PSL timer expiration. See PCMCIA Interface in the MPC850 PowerQUICC User's Manual.

PSHT = 0. Otherwise add PSHT times cycle time.

Figure 25 provides the PCMCIA access cycle timing for the external bus write.

Figure 25. PCMCIA Access Cycles Timing External Bus Write

Figure 26 provides the PCMCIA WAIT signals detection timing.

Figure 26. PCMCIA WAIT Signal Detection Timing

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

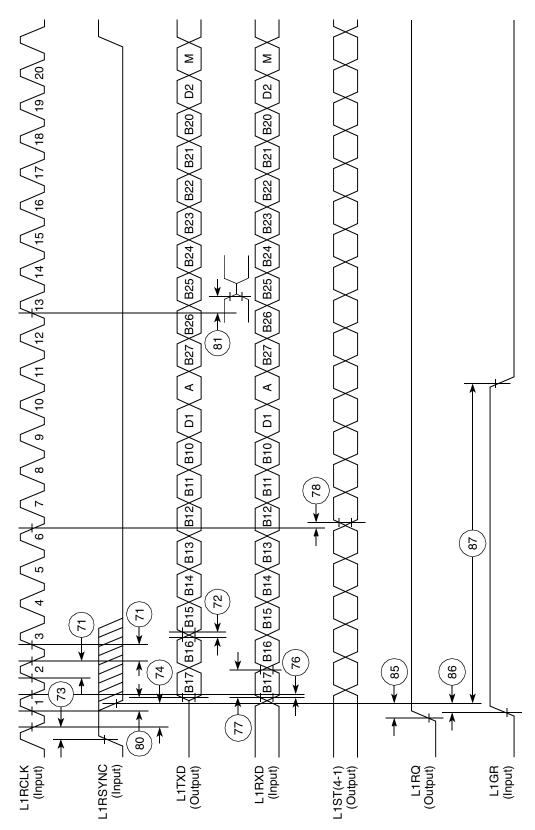

## Table 11 shows the reset timing for the MPC850.

## Table 11. Reset Timing

| Num    | Characteristic                                                                      | 50 N   | ЛНz   | 66N    | ЛHz   | 80 1   | ИНz   | FFACTOR | Unit |

|--------|-------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|---------|------|

| INUIII | Characteristic                                                                      | Min    | Max   | Min    | Max   | Min    | Max   | FFACION | Onit |

| R69    | CLKOUT to HRESET high impedance                                                     | _      | 20.00 | _      | 20.00 | _      | 20.00 | _       | ns   |

| R70    | CLKOUT to SRESET high impedance                                                     | _      | 20.00 | _      | 20.00 | _      | 20.00 | _       | ns   |

| R71    | RSTCONF pulse width                                                                 | 340.00 | _     | 515.00 | _     | 425.00 | _     | 17.000  | ns   |

| R72    |                                                                                     | _      | _     | _      | _     | _      | _     | _       |      |

| R73    | Configuration data to HRESET rising edge set up time                                | 350.00 | _     | 505.00 | _     | 425.00 | _     | 15.000  | ns   |

| R74    | Configuration data to RSTCONF rising edge set up time                               | 350.00 | _     | 350.00 | _     | 350.00 | _     | _       | ns   |

| R75    | Configuration data hold time after RSTCONF negation                                 | 0.00   | _     | 0.00   | _     | 0.00   | _     | _       | ns   |

| R76    | Configuration data hold time after HRESET negation                                  | 0.00   | _     | 0.00   | _     | 0.00   | _     | _       | ns   |

| R77    | HRESET and RSTCONF asserted to data out drive                                       | _      | 25.00 | _      | 25.00 | _      | 25.00 | _       | ns   |

| R78    | RSTCONF negated to data out high impedance.                                         | _      | 25.00 | _      | 25.00 | _      | 25.00 | _       | ns   |

| R79    | CLKOUT of last rising edge before chip tristates HRESET to data out high impedance. | _      | 25.00 | _      | 25.00 | _      | 25.00 | _       | ns   |

| R80    | DSDI, DSCK set up                                                                   | 60.00  | _     | 90.00  | _     | 75.00  | _     | 3.000   | ns   |

| R81    | DSDI, DSCK hold time                                                                | 0.00   | _     | 0.00   | _     | 0.00   | _     | _       | ns   |

| R82    | SRESET negated to CLKOUT rising edge for DSDI and DSCK sample                       | 160.00 | _     | 242.00 | _     | 200.00 | _     | 8.000   | ns   |

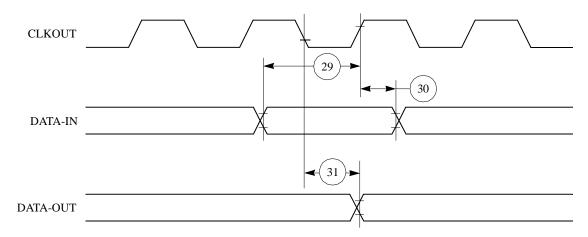

Figure 38. Parallel I/O Data-In/Data-Out Timing Diagram

# 8.2 IDMA Controller AC Electrical Specifications

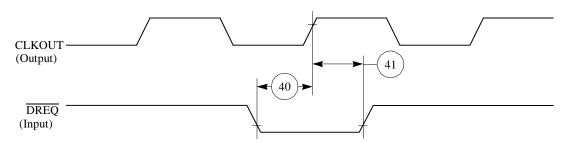

Table 14 provides the IDMA controller timings as shown in Figure 39 to Figure 42.

| Num   | Characteristic                                                                | All Fred | Unit  |            |

|-------|-------------------------------------------------------------------------------|----------|-------|------------|

| Nulli | Characteristic                                                                | Min      | Max   | Unit<br>ns |

| 40    | DREQ setup time to clock high                                                 | 7.00     | _     | ns         |

| 41    | DREQ hold time from clock high                                                | 3.00     | _     | ns         |

| 42    | SDACK assertion delay from clock high                                         | _        | 12.00 | ns         |

| 43    | SDACK negation delay from clock low                                           | _        | 12.00 | ns         |

| 44    | SDACK negation delay from TA low                                              | _        | 20.00 | ns         |

| 45    | SDACK negation delay from clock high                                          | _        | 15.00 | ns         |

| 46    | TA assertion to falling edge of the clock setup time (applies to external TA) | 7.00     |       | ns         |

**Table 14. IDMA Controller Timing**

Figure 39. IDMA External Requests Timing Diagram

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Figure 49. IDL Timing

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

**CPM Electrical Characteristics**

# 8.6 SCC in NMSI Mode Electrical Specifications

Table 18 provides the NMSI external clock timing.

**Table 18. NMSI External Clock Timing**

| Num | Characteristic                                                        | All Frequencie | Unit  |      |

|-----|-----------------------------------------------------------------------|----------------|-------|------|

| Num | Characteristic                                                        | Min            | Max   | Unit |

| 100 | RCLKx and TCLKx frequency $^1$ (x = 2, 3 for all specs in this table) | 1/SYNCCLK      | _     | ns   |

| 101 | RCLKx and TCLKx width low                                             | 1/SYNCCLK +5   | _     | ns   |

| 102 | RCLKx and TCLKx rise/fall time                                        | _              | 15.00 | ns   |

| 103 | TXDx active delay (from TCLKx falling edge)                           | 0.00           | 50.00 | ns   |

| 104 | RTSx active/inactive delay (from TCLKx falling edge)                  | 0.00           | 50.00 | ns   |

| 105 | CTSx setup time to TCLKx rising edge                                  | 5.00           | _     | ns   |

| 106 | RXDx setup time to RCLKx rising edge                                  | 5.00           | _     | ns   |

| 107 | RXDx hold time from RCLKx rising edge <sup>2</sup>                    | 5.00           | _     | ns   |

| 108 | CDx setup time to RCLKx rising edge                                   | 5.00           | _     | ns   |

<sup>&</sup>lt;sup>1</sup> The ratios SyncCLK/RCLKx and SyncCLK/TCLKx must be greater than or equal to 2.25/1.

Table 19 provides the NMSI internal clock timing.

**Table 19. NMSI Internal Clock Timing**

| Nive | Characteristic                                                        | All Fr | Unit      |      |

|------|-----------------------------------------------------------------------|--------|-----------|------|

| Num  | Characteristic                                                        | Min    | Max       | Onit |

| 100  | RCLKx and TCLKx frequency $^1$ (x = 2, 3 for all specs in this table) | 0.00   | SYNCCLK/3 | MHz  |

| 102  | RCLKx and TCLKx rise/fall time                                        | _      | _         | ns   |

| 103  | TXDx active delay (from TCLKx falling edge)                           | 0.00   | 30.00     | ns   |

| 104  | RTSx active/inactive delay (from TCLKx falling edge)                  | 0.00   | 30.00     | ns   |

| 105  | CTSx setup time to TCLKx rising edge                                  | 40.00  | _         | ns   |

| 106  | RXDx setup time to RCLKx rising edge                                  | 40.00  | _         | ns   |

| 107  | RXDx hold time from RCLKx rising edge <sup>2</sup>                    | 0.00   | _         | ns   |

| 108  | CDx setup time to RCLKx rising edge                                   | 40.00  | _         | ns   |

The ratios SyncCLK/RCLKx and SyncCLK/TCLK1x must be greater or equal to 3/1.

<sup>&</sup>lt;sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

<sup>&</sup>lt;sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

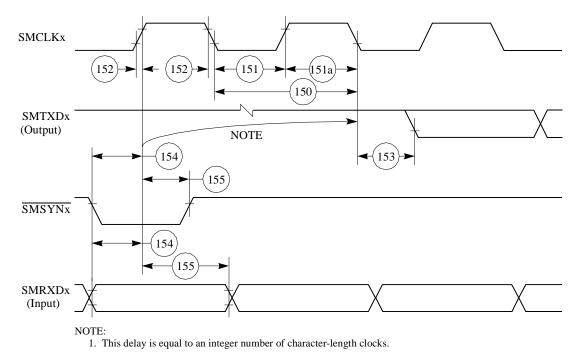

Figure 56. SMC Transparent Timing Diagram

# 8.9 SPI Master AC Electrical Specifications

Table 22 provides the SPI master timings as shown in Figure 57 and Figure 58.

**All Frequencies** Characteristic Unit Num Min Max 160 MASTER cycle time 4 1024 t<sub>cyc</sub> 161 MASTER clock (SCK) high or low time 2 512 t<sub>cyc</sub> 162 MASTER data setup time (inputs) 50.00 ns 163 Master data hold time (inputs) 0.00 ns 164 Master data valid (after SCK edge) 20.00 ns 165 Master data hold time (outputs) 0.00 ns 15.00 166 Rise time output ns 167 Fall time output 15.00 ns

Table 22. SPI Master Timing

### **Mechanical Data and Ordering Information**

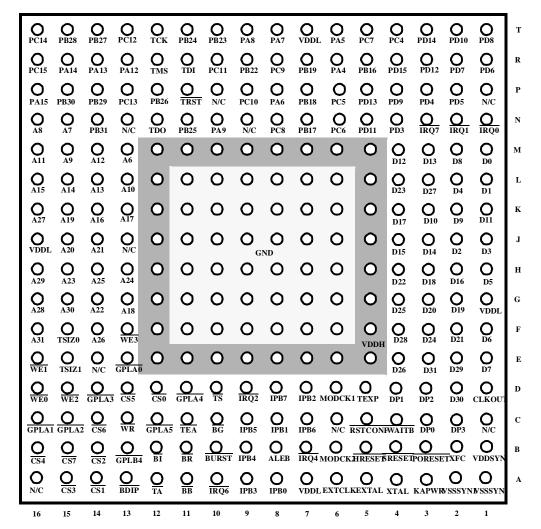

customers that are currently using the non-JEDEC pin numbering scheme, two sets of pinouts, JEDEC and non-JEDEC, are presented in this document.

Figure 62 shows the non-JEDEC pinout of the PBGA package as viewed from the top surface.

Figure 62. Pin Assignments for the PBGA (Top View)—non-JEDEC Standard

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

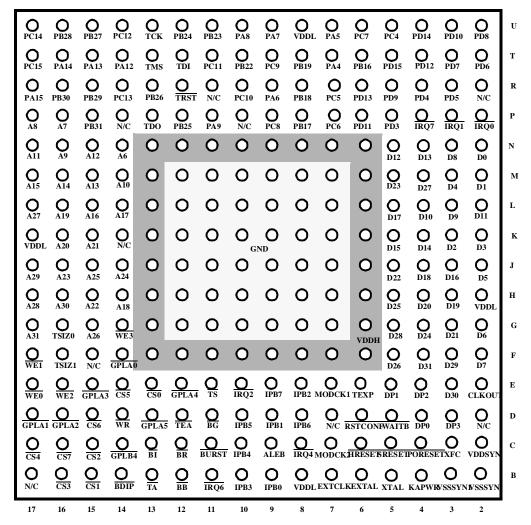

Figure 63 shows the JEDEC pinout of the PBGA package as viewed from the top surface.

Figure 63. Pin Assignments for the PBGA (Top View)—JEDEC Standard

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to AN-1231/D, Plastic Ball Grid Array Application Note available from your local Freescale sales office.

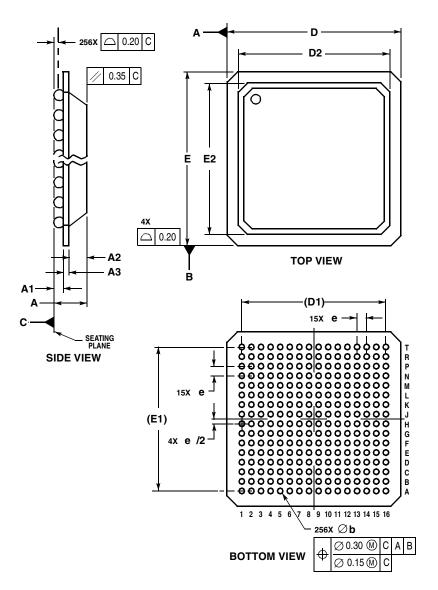

### **Mechanical Data and Ordering Information**

Figure 64 shows the non-JEDEC package dimensions of the PBGA.

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. DIMENSIONS IN MILLIMETERS.

- DIMENSION 6 IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C.

- 4. PRIMARY DATUM C AND THE SEATING PLANE ARE

|            | MILLIN    | IETERS |  |  |  |  |

|------------|-----------|--------|--|--|--|--|

| DIM        | MIN       | MAX    |  |  |  |  |

| Α          | 1.91      | 2.35   |  |  |  |  |

| <b>A</b> 1 | 0.50      | 0.70   |  |  |  |  |

| A2         | 1.12      | 1.22   |  |  |  |  |

| A3         | 0.29      | 0.43   |  |  |  |  |

| b          | 0.60      | 0.90   |  |  |  |  |

| D          | 23.00     | BSC    |  |  |  |  |

| D1         | 19.05     | REF    |  |  |  |  |

| D2         | 19.00     | 20.00  |  |  |  |  |

| Е          | 23.00     | BSC    |  |  |  |  |

| E1         | 19.05 REF |        |  |  |  |  |

| E2         | 19.00     | 20.00  |  |  |  |  |

| е          | 1.27      | BSC    |  |  |  |  |

Figure 64. Package Dimensions for the Plastic Ball Grid Array (PBGA)—non-JEDEC Standard

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

## THIS PAGE INTENTIONALLY LEFT BLANK

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

### How to Reach Us:

### Home Page:

www.freescale.com

### email

support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate,

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

(800) 441-2447

303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor

@ hibbertgroup.com

Document Number: MPC850EC

Rev. 2 07/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2005.