Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 66MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1)                                                             |

| SATA                            | -                                                                      |

| USB                             | USB 1.x (1)                                                            |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 256-BGA                                                                |

| Supplier Device Package         | 256-PBGA (23x23)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/xpc850srzt66bu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

### Interrupts

- Eight external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- Fifteen internal interrupt sources

- Programmable priority among SCCs and USB

- Programmable highest-priority request

- Single socket PCMCIA-ATA interface

- Master (socket) interface, release 2.1 compliant

- Single PCMCIA socket

- Supports eight memory or I/O windows

- Communications processor module (CPM)

- 32-bit, Harvard architecture, scalar RISC communications processor (CP)

- Protocol-specific command sets (for example, GRACEFUL STOP TRANSMIT stops transmission

after the current frame is finished or immediately if no frame is being sent and CLOSE RXBD

closes the receive buffer descriptor)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8 Kbytes of dual-port RAM

- Twenty serial DMA (SDMA) channels for the serial controllers, including eight for the four USB endpoints

- Three parallel I/O registers with open-drain capability

- Four independent baud-rate generators (BRGs)

- Can be connected to any SCC, SMC, or USB

- Allow changes during operation

- Autobaud support option

- Two SCCs (serial communications controllers)

- Ethernet/IEEE 802.3, supporting full 10-Mbps operation

- HDLC/SDLC<sup>TM</sup> (all channels supported at 2 Mbps)

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk<sup>®</sup>

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

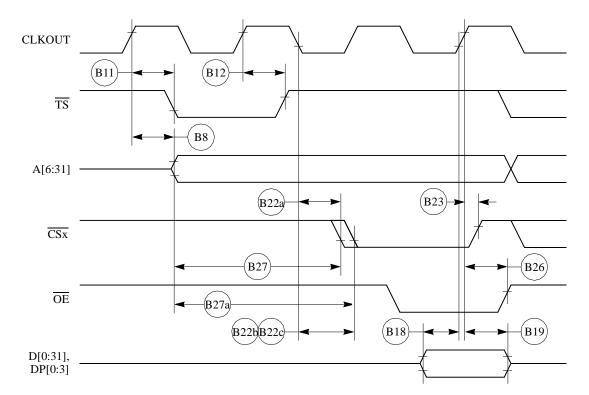

## Table 6. Bus Operation Timing <sup>1</sup>

| N   | Oh ava atawiatia                                                                             | 50 I  | ИНz   | 66 1  | ИНz   | 1 08  | ИНz   | FEAGE | Cap Load           | 11!4 |

|-----|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|------|

| Num | Characteristic                                                                               | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit |

| B1  | CLKOUT period                                                                                | 20    | _     | 30.30 | _     | 25    | _     | _     | _                  | ns   |

| B1a | EXTCLK to CLKOUT phase<br>skew (EXTCLK > 15 MHz and<br>MF <= 2)                              | -0.90 | 0.90  | -0.90 | 0.90  | -0.90 | 0.90  | _     | 50.00              | ns   |

| B1b | EXTCLK to CLKOUT phase<br>skew (EXTCLK > 10 MHz and<br>MF < 10)                              | -2.30 | 2.30  | -2.30 | 2.30  | -2.30 | 2.30  | _     | 50.00              | ns   |

| B1c | CLKOUT phase jitter (EXTCLK > 15 MHz and MF <= 2) <sup>2</sup>                               | -0.60 | 0.60  | -0.60 | 0.60  | -0.60 | 0.60  | _     | 50.00              | ns   |

| B1d | CLKOUT phase jitter <sup>2</sup>                                                             | -2.00 | 2.00  | -2.00 | 2.00  | -2.00 | 2.00  | _     | 50.00              | ns   |

| B1e | CLKOUT frequency jitter (MF < 10) <sup>2</sup>                                               | _     | 0.50  | _     | 0.50  | _     | 0.50  | _     | 50.00              | %    |

| B1f | CLKOUT frequency jitter (10 < MF < 500) <sup>2</sup>                                         | _     | 2.00  | _     | 2.00  | _     | 2.00  | _     | 50.00              | %    |

| B1g | CLKOUT frequency jitter (MF > 500) <sup>2</sup>                                              | _     | 3.00  | _     | 3.00  | _     | 3.00  | _     | 50.00              | %    |

| B1h | Frequency jitter on EXTCLK <sup>3</sup>                                                      | _     | 0.50  | _     | 0.50  | _     | 0.50  | _     | 50.00              | %    |

| B2  | CLKOUT pulse width low                                                                       | 8.00  | _     | 12.12 | _     | 10.00 | _     | _     | 50.00              | ns   |

| В3  | CLKOUT width high                                                                            | 8.00  | _     | 12.12 | _     | 10.00 | _     | _     | 50.00              | ns   |

| B4  | CLKOUT rise time                                                                             | _     | 4.00  | _     | 4.00  | _     | 4.00  | _     | 50.00              | ns   |

| B5  | CLKOUT fall time                                                                             | _     | 4.00  | _     | 4.00  | _     | 4.00  | _     | 50.00              | ns   |

| В7  | CLKOUT to A[6-31],<br>RD/WR, BURST, D[0-31],<br>DP[0-3] invalid                              | 5.00  | _     | 7.58  | _     | 6.25  | _     | 0.250 | 50.00              | ns   |

| В7а | CLKOUT to TSIZ[0-1], REG,<br>RSV, AT[0-3], BDIP, PTR<br>invalid                              | 5.00  | _     | 7.58  |       | 6.25  | _     | 0.250 | 50.00              | ns   |

| B7b | CLKOUT to BR, BG, FRZ,<br>VFLS[0–1], VF[0–2] IWP[0–2],<br>LWP[0–1], STS invalid <sup>4</sup> | 5.00  | _     | 7.58  | _     | 6.25  | _     | 0.250 | 50.00              | ns   |

| B8  | CLKOUT to A[6–31],<br>RD/WR, BURST, D[0–31],<br>DP[0–3] valid                                | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B8a | CLKOUT to TSIZ[0-1], REG,<br>RSV, AT[0-3] BDIP, PTR valid                                    | 5.00  | 11.75 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

| B8b | CLKOUT to BR, BG,<br>VFLS[0–1], VF[0–2], IWP[0–2],<br>FRZ, LWP[0–1], STS valid <sup>4</sup>  | 5.00  | 11.74 | 7.58  | 14.33 | 6.25  | 13.00 | 0.250 | 50.00              | ns   |

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Num  | Chavastavistis                                                                                                          | 50 I  | ИНz   | 66 I  | ИНz   | 80 1  | ИНz   | FEACT | Cap Load           | l lmit |

|------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|--------|

| Num  | Characteristic                                                                                                          | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit   |

| B28c | CLKOUT falling edge to WE[0-3] negated GPCM write access TRLX = 0,1 CSNT = 1 write access TRLX = 0, CSNT = 1, EBDF = 1  | 7.00  | 14.00 | 11.00 | 18.00 | 9.00  | 16.00 | 0.375 | 50.00              | ns     |

| B28d | CLKOUT falling edge to CS<br>negated GPCM write access<br>TRLX = 0,1 CSNT = 1, ACS =<br>10 or ACS = 11, EBDF = 1        | _     | 14.00 | _     | 18.00 | _     | 16.00 | 0.375 | 50.00              | ns     |

| B29  | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, CSNT = 0                                            | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns     |

| B29a | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 0 CSNT = 1,<br>EBDF = 0                      | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns     |

| B29b | CS negated to D[0-31],<br>DP[0-3], high-Z GPCM write<br>access, ACS = 00, TRLX = 0 &<br>CSNT = 0                        | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns     |

| B29c | CS negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns     |

| B29d | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>EBDF = 0                     | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns     |

| B29e | CS negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access, TRLX = 1, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>0 | 28.00 | _     | 43.00 | _     | 36.00 | _     | 1.500 | 50.00              | ns     |

| B29f | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                      | 5.00  | _     | 9.00  | _     | 7.00  | _     | 0.375 | 50.00              | ns     |

| B29g | CS negated to D[0–31],<br>DP[0–3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>ACS = 10 or ACS = 11, EBDF =<br>1  | 5.00  | _     | 9.00  | _     | 7.00  | _     | 0.375 | 50.00              | ns     |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nive | Chavastavistis                                                                                                                                                                | 50 I  | ИНz | 66 1  | ИHz | 80 1  | ИНz | FEACT | Cap Load           | Hali |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|-------|-----|-------|--------------------|------|

| Num  | Characteristic                                                                                                                                                                | Min   | Max | Min   | Max | Min   | Max | FFACT | (default<br>50 pF) | Unit |

| B29h | WE[0-3] negated to D[0-31],<br>DP[0-3] high-Z GPCM write<br>access TRLX = 0, CSNT = 1,<br>EBDF = 1                                                                            | 25.00 | _   | 39.00 | _   | 31.00 | _   | 1.375 | 50.00              | ns   |

| B29i | CS negated to D[0-31], DP[0-3] high-Z GPCM write access, TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF =                                                                     | 25.00 |     | 39.00 |     | 31.00 |     | 1.375 | 50.00              | ns   |

| B30  | CS, WE[0-3] negated to A[6-31] invalid GPCM write access 9                                                                                                                    | 3.00  | _   | 6.00  | _   | 4.00  | _   | 0.250 | 50.00              | ns   |

| B30a | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1, CS negated to A[6-31] invalid GPCM write access TRLX = 0, CSNT =1, ACS = 10 or ACS = 11, EBDF = 0   | 8.00  | _   | 13.00 | _   | 11.00 | _   | 0.500 | 50.00              | ns   |

| B30b | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A[6-31] Invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 0  | 28.00 |     | 43.00 | _   | 36.00 | _   | 1.500 | 50.00              | ns   |

| B30c | WE[0-3] negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1. CS negated to A[6-31] invalid GPCM write access, TRLX = 0, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 1 | 5.00  | ı   | 8.00  | 1   | 6.00  | 1   | 0.375 | 50.00              | ns   |

| B30d | WE[0-3] negated to A[6-31] invalid GPCM write access TRLX = 1, CSNT =1, CS negated to A[6-31] invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10 or ACS = 11, EBDF = 1    | 25.00 |     | 39.00 | _   | 31.00 | _   | 1.375 | 50.00              | ns   |

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| NI   | Oh ava ataviatia                                                                                                            | 50 I | MHz   | 66 1  | ИHz   | 80 1  | ИHz   | EEA OT | Cap Load           | 11!4 |

|------|-----------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|-------|-------|--------|--------------------|------|

| Num  | Characteristic                                                                                                              | Min  | Max   | Min   | Max   | Min   | Max   | FFACT  | (default<br>50 pF) | Unit |

| B31  | CLKOUT falling edge to CS valid - as requested by control bit CST4 in the corresponding word in the UPM                     | 1.50 | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | _      | 50.00              | ns   |

| B31a | CLKOUT falling edge to $\overline{\text{CS}}$ valid - as requested by control bit CST1 in the corresponding word in the UPM | 5.00 | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250  | 50.00              | ns   |

| B31b | CLKOUT rising edge to CS valid<br>- as requested by control bit<br>CST2 in the corresponding<br>word in the UPM             | 1.50 | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | _      | 50.00              | ns   |

| B31c | CLKOUT rising edge to CS valid - as requested by control bit CST3 in the corresponding word in the UPM                      | 5.00 | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250  | 50.00              | ns   |

| B31d | CLKOUT falling edge to CS valid - as requested by control bit CST1 in the corresponding word in the UPM EBDF = 1            | 9.00 | 14.00 | 13.00 | 18.00 | 11.00 | 16.00 | 0.375  | 50.00              | ns   |

| B32  | CLKOUT falling edge to BS valid - as requested by control bit BST4 in the corresponding word in the UPM                     | 1.50 | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | _      | 50.00              | ns   |

| B32a | CLKOUT falling edge to BS valid - as requested by control bit BST1 in the corresponding word in the UPM, EBDF = 0           | 5.00 | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250  | 50.00              | ns   |

| B32b | CLKOUT rising edge to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM             | 1.50 | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | _      | 50.00              | ns   |

| B32c | CLKOUT rising edge to BS valid<br>- as requested by control bit<br>BST3 in the corresponding<br>word in the UPM             | 5.00 | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250  | 50.00              | ns   |

| B32d | CLKOUT falling edge to BS valid - as requested by control bit BST1 in the corresponding word in the UPM, EBDF = 1           | 9.00 | 14.00 | 13.00 | 18.00 | 11.00 | 16.00 | 0.375  | 50.00              | ns   |

| B33  | CLKOUT falling edge to GPL valid - as requested by control bit GxT4 in the corresponding word in the UPM                    | 1.50 | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | _      | 50.00              | ns   |

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Table 6. Bus Operation Timing <sup>1</sup> (continued)

| Nivee | Characteristic                                                                                                                       | 50 I  | ИНz   | 66 N  | ИHz   | 80 1  | MHz   | EEAOT | Cap Load           | Unit |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------|------|

| Num   | Characteristic                                                                                                                       | Min   | Max   | Min   | Max   | Min   | Max   | FFACT | (default<br>50 pF) | Unit |

| B33a  | CLKOUT rising edge to GPL valid - as requested by control bit GxT3 in the corresponding word in the UPM                              | 5.00  | 12.00 | 8.00  | 14.00 | 6.00  | 13.00 | 0.250 | 50.00              | ns   |

| B34   | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid<br>- as requested by control bit<br>CST4 in the corresponding<br>word in the UPM | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns   |

| B34a  | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid - as requested by control bit CST1 in the corresponding word in the UPM          | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns   |

| B34b  | A[6–31] and D[0–31] to $\overline{\text{CS}}$ valid - as requested by CST2 in the corresponding word in UPM                          | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750 | 50.00              | ns   |

| B35   | A[6–31] to CS valid - as requested by control bit BST4 in the corresponding word in UPM                                              | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns   |

| B35a  | A[6–31] and D[0–31] to $\overline{BS}$ valid - as requested by BST1 in the corresponding word in the UPM                             | 8.00  | _     | 13.00 | _     | 11.00 | _     | 0.500 | 50.00              | ns   |

| B35b  | A[6–31] and D[0–31] to BS valid<br>- as requested by control bit<br>BST2 in the corresponding<br>word in the UPM                     | 13.00 | _     | 21.00 | _     | 17.00 | _     | 0.750 | 50.00              | ns   |

| B36   | A[6–31] and D[0–31] to GPL valid - as requested by control bit GxT4 in the corresponding word in the UPM                             | 3.00  | _     | 6.00  | _     | 4.00  | _     | 0.250 | 50.00              | ns   |

| B37   | UPWAIT valid to CLKOUT falling edge 10                                                                                               | 6.00  | _     | 6.00  | _     | 6.00  | _     | _     | 50.00              | ns   |

| B38   | CLKOUT falling edge to UPWAIT valid <sup>10</sup>                                                                                    | 1.00  | _     | 1.00  | _     | 1.00  | _     | _     | 50.00              | ns   |

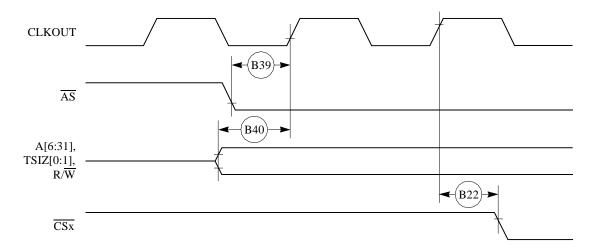

| B39   | AS valid to CLKOUT rising edge                                                                                                       | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns   |

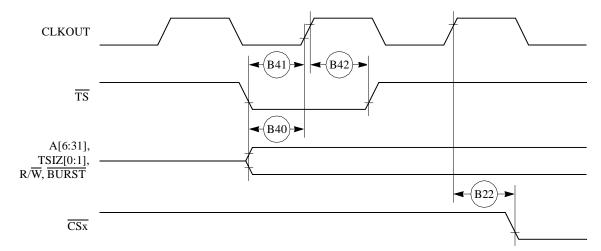

| B40   | A[6–31], TSIZ[0–1], RD/WR,<br>BURST, valid to CLKOUT rising<br>edge.                                                                 | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns   |

| B41   | TS valid to CLKOUT rising edge (setup time)                                                                                          | 7.00  | _     | 7.00  | _     | 7.00  | _     | _     | 50.00              | ns   |

Figure 12. External Bus Read Timing (GPCM Controlled—TRLX = 1, ACS = 10, ACS = 11)

Figure 19 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 19. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 20 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 20. Asynchronous External Master Memory Access Timing (GPCM Controlled—ACS = 00)

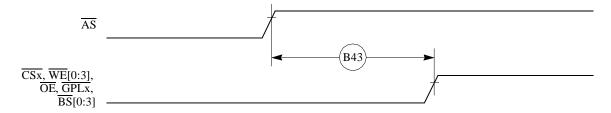

Figure 21 provides the timing for the asynchronous external master control signals negation.

Figure 21. Asynchronous External Master—Control Signals Negation Timing

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Table 9 shows the PCMCIA port timing for the MPC850.

**Table 9. PCMCIA Port Timing**

| Num | Characteristic                           | 50 MHz |       | 66 MHz |       | 80 MHz |       | Unit  |

|-----|------------------------------------------|--------|-------|--------|-------|--------|-------|-------|

| Num | Gilai acteristic                         | Min    | Max   | Min    | Max   | Min    | Max   | Oiiit |

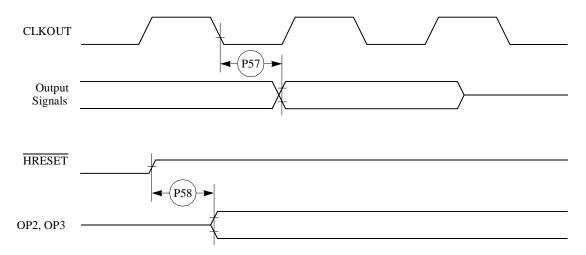

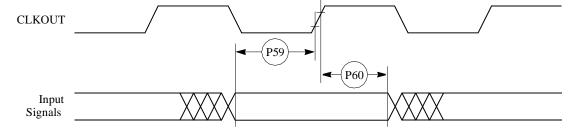

| P57 | CLKOUT to OPx valid                      | _      | 19.00 | _      | 19.00 | _      | 19.00 | ns    |

| P58 | HRESET negated to OPx drive <sup>1</sup> | 18.00  | _     | 26.00  | _     | 22.00  | _     | ns    |

| P59 | IP_Xx valid to CLKOUT rising edge        | 5.00   | _     | 5.00   | _     | 5.00   | _     | ns    |

| P60 | CLKOUT rising edge to IP_Xx invalid      | 1.00   | _     | 1.00   | _     | 1.00   | _     | ns    |

OP2 and OP3 only.

Figure 27 provides the PCMCIA output port timing for the MPC850.

Figure 27. PCMCIA Output Port Timing

Figure 28 provides the PCMCIA output port timing for the MPC850.

Figure 28. PCMCIA Input Port Timing

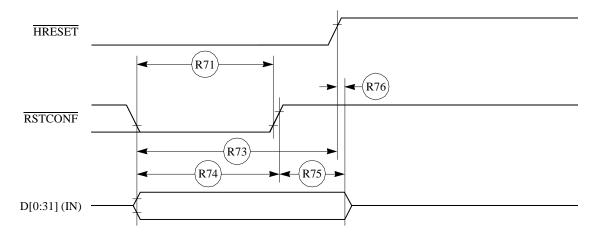

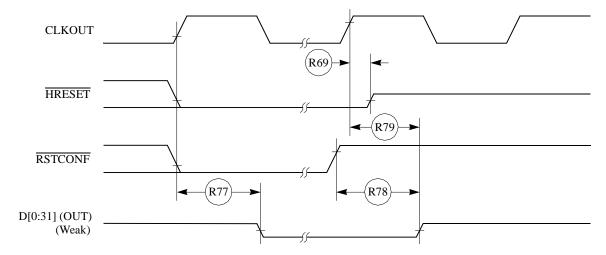

Figure 31 shows the reset timing for the data bus configuration.

Figure 31. Reset Timing—Configuration from Data Bus

Figure 32 provides the reset timing for the data bus weak drive during configuration.

Figure 32. Reset Timing—Data Bus Weak Drive during Configuration

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

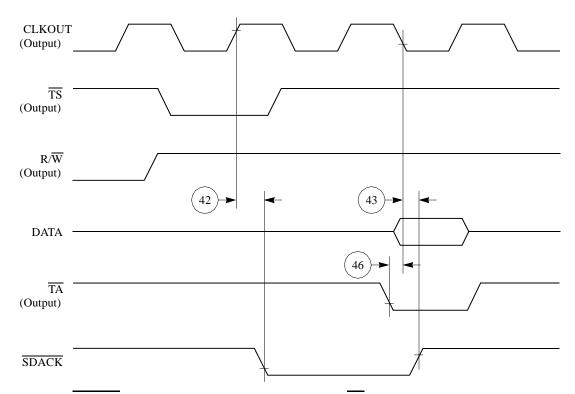

Figure 40. SDACK Timing Diagram—Peripheral Write, TA Sampled Low at the Falling Edge of the Clock

#### **CPM Electrical Characteristics**

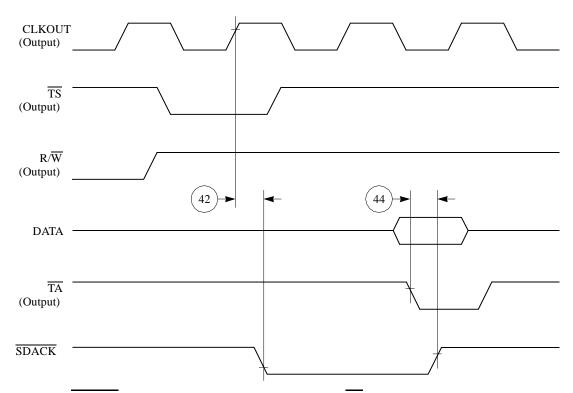

Figure 41. SDACK Timing Diagram—Peripheral Write, TA Sampled High at the Falling Edge of the Clock

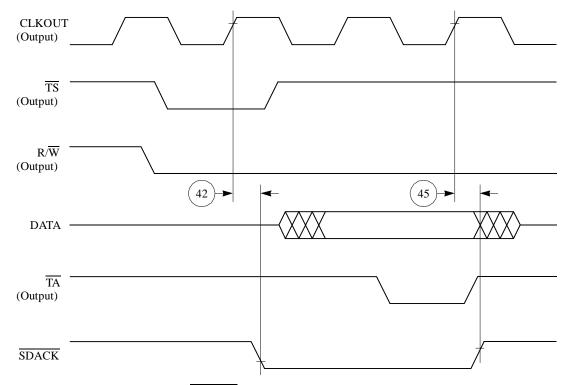

Figure 42. SDACK Timing Diagram—Peripheral Read

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

| Num   | Characteristic                                                       | All Free | quencies              | Unit   |

|-------|----------------------------------------------------------------------|----------|-----------------------|--------|

| Nulli | Characteristic                                                       | Min      | Max                   | Oliit  |

| 82    | L1RCLK, L1TCLK frequency (DSC =1)                                    | _        | 16.00 or<br>SYNCCLK/2 | MHz    |

| 83    | L1RCLK, L1TCLK width low (DSC =1)                                    | P + 10   | _                     | ns     |

| 83A   | L1RCLK, L1TCLK width high (DSC = 1) <sup>3</sup>                     | P + 10   | _                     | ns     |

| 84    | L1CLK edge to L1CLKO valid (DSC = 1)                                 | _        | 30.00                 | ns     |

| 85    | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>               | 1.00     | _                     | L1TCLK |

| 86    | L1GR setup time <sup>2</sup>                                         | 42.00    | _                     | ns     |

| 87    | L1GR hold time                                                       | 42.00    | _                     | ns     |

| 88    | L1xCLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00                  | ns     |

<sup>&</sup>lt;sup>1</sup> The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

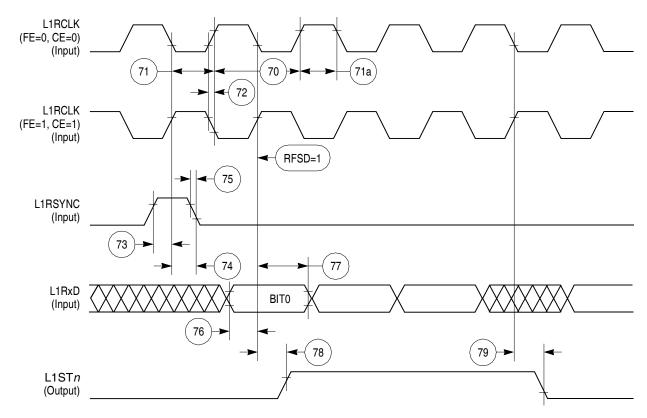

Figure 45. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

<sup>&</sup>lt;sup>2</sup> These specs are valid for IDL mode only.

$<sup>^{3}</sup>$  Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

Figure 47. SI Transmit Timing Diagram

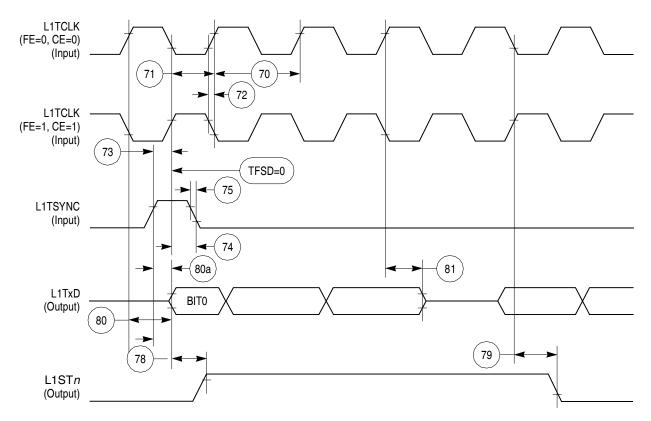

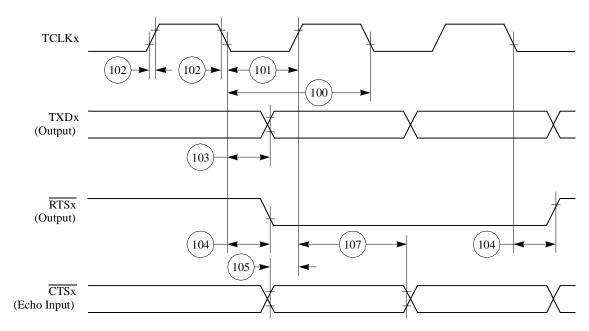

Figure 50 through Figure 52 show the NMSI timings.

Figure 50. SCC NMSI Receive Timing Diagram

Figure 51. SCC NMSI Transmit Timing Diagram

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

Figure 52. HDLC Bus Timing Diagram

## 8.7 Ethernet Electrical Specifications

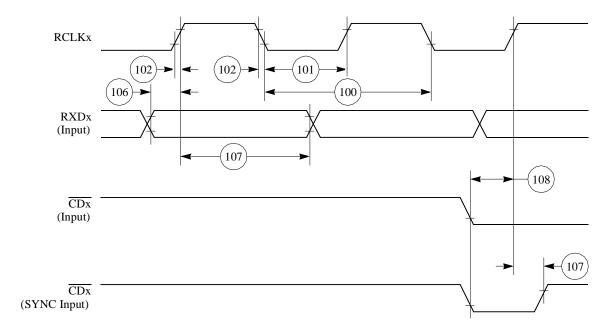

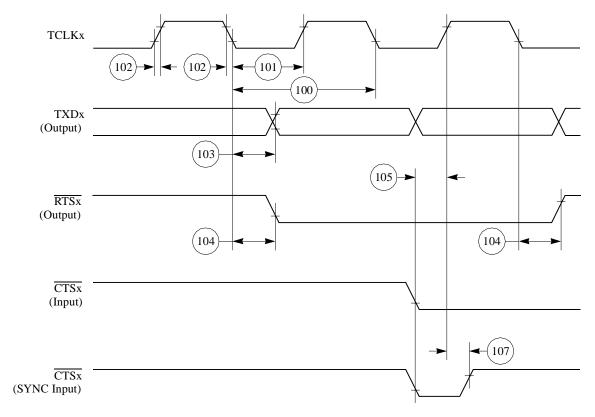

Table 20 provides the Ethernet timings as shown in Figure 53 to Figure 55.

**Table 20. Ethernet Timing**

| Num | Characteristic                                                  | All Fred | luencies | Unit |

|-----|-----------------------------------------------------------------|----------|----------|------|

| Num | Characteristic                                                  | Min      | Max      | Unit |

| 120 | CLSN width high                                                 | 40.00    | _        | ns   |

| 121 | RCLKx rise/fall time (x = 2, 3 for all specs in this table)     | _        | 15.00    | ns   |

| 122 | RCLKx width low                                                 | 40.00    | _        | ns   |

| 123 | RCLKx clock period <sup>1</sup>                                 | 80.00    | 120.00   | ns   |

| 124 | RXDx setup time                                                 | 20.00    | _        | ns   |

| 125 | RXDx hold time                                                  | 5.00     | _        | ns   |

| 126 | RENA active delay (from RCLKx rising edge of the last data bit) | 10.00    | _        | ns   |

| 127 | RENA width low                                                  | 100.00   | _        | ns   |

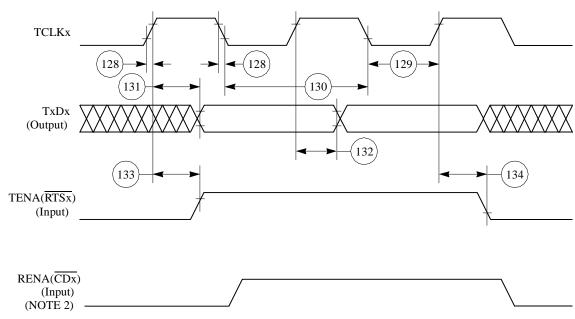

| 128 | TCLKx rise/fall time                                            | _        | 15.00    | ns   |

| 129 | TCLKx width low                                                 | 40.00    | _        | ns   |

| 130 | TCLKx clock period <sup>1</sup>                                 | 99.00    | 101.00   | ns   |

| 131 | TXDx active delay (from TCLKx rising edge)                      | 10.00    | 50.00    | ns   |

| 132 | TXDx inactive delay (from TCLKx rising edge)                    | 10.00    | 50.00    | ns   |

| 133 | TENA active delay (from TCLKx rising edge)                      | 10.00    | 50.00    | ns   |

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

#### **CPM Electrical Characteristics**

- NOTES:

- 1. Transmit clock invert (TCI) bit in GSMR is set.

- If RENA is deasserted before TENA, or RENA is not asserted at all during transmit, then the CSL bit is set in the buffer descriptor at the end of the frame transmission.

Figure 55. Ethernet Transmit Timing Diagram

## 8.8 SMC Transparent AC Electrical Specifications

Figure 21 provides the SMC transparent timings as shown in Figure 56.

**Table 21. Serial Management Controller Timing**

| Num  | Characteristic                                 | All Frequ | encies | Unit  |

|------|------------------------------------------------|-----------|--------|-------|

| Num  | Characteristic                                 | Min       | Max    | Oilit |

| 150  | SMCLKx clock period <sup>1</sup>               | 100.00    | _      | ns    |

| 151  | SMCLKx width low                               | 50.00     | _      | ns    |

| 151a | SMCLKx width high                              | 50.00     | _      | ns    |

| 152  | SMCLKx rise/fall time                          | _         | 15.00  | ns    |

| 153  | SMTXDx active delay (from SMCLKx falling edge) | 10.00     | 50.00  | ns    |

| 154  | SMRXDx/SMSYNx setup time                       | 20.00     | _      | ns    |

| 155  | SMRXDx/SMSYNx hold time                        | 5.00      | _      | ns    |

<sup>1</sup> The ratio SyncCLK/SMCLKx must be greater or equal to 2/1.

## 9 Mechanical Data and Ordering Information

Table 26 provides information on the MPC850 derivative devices.

Table 26. MPC850 Family Derivatives

| Device    | Ethernet Support | Number of SCCs <sup>1</sup> | 32-Channel HDLC<br>Support | 64-Channel HDLC<br>Support <sup>2</sup> |

|-----------|------------------|-----------------------------|----------------------------|-----------------------------------------|

| MPC850    | N/A              | One                         | N/A                        | N/A                                     |

| MPC850DE  | Yes              | Two                         | N/A                        | N/A                                     |

| MPC850SR  | Yes              | Two                         | N/A                        | Yes                                     |

| MPC850DSL | Yes              | Two                         | No                         | No                                      |

Serial Communication Controller (SCC)

Table 27 identifies the packages and operating frequencies available for the MPC850.

Table 27. MPC850 Package/Frequency/Availability

| Package Type                                     | Frequency (MHz) | Temperature (Tj) | Order Number                                                            |

|--------------------------------------------------|-----------------|------------------|-------------------------------------------------------------------------|

| 256-Lead Plastic Ball Grid Array (ZT suffix)     | 50              | 0°C to 95°C      | XPC850ZT50BU<br>XPC850DEZT50BU<br>XPC850SRZT50BU<br>XPC850DSLZT50BU     |

|                                                  | 66              | 0°C to 95°C      | XPC850ZT66BU<br>XPC850DEZT66BU<br>XPC850SRZT66BU                        |

|                                                  | 80              | 0°C to 95°C      | XPC850ZT80BU<br>XPC850DEZT80BU<br>XPC850SRZT80BU                        |

| 256-Lead Plastic Ball Grid Array<br>(CZT suffix) | 50              | -40°C to 95°C    | XPC850CZT50BU<br>XPC850DECZT50BU<br>XPC850SRCZT50BU<br>XPC850DSLCZT50BU |

|                                                  | 66              |                  | XPC850CZT66BU<br>XPC850DECZT66BU<br>XPC850SRCZT66BU                     |

|                                                  | 80              |                  | XPC850CZT80B<br>XPC850DECZT80B<br>XPC850SRCZT80B                        |

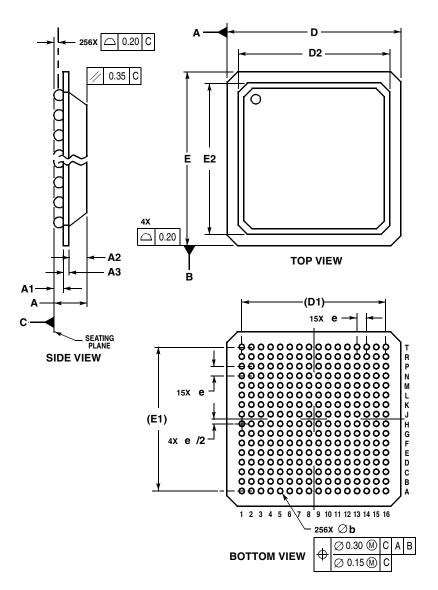

## 9.1 Pin Assignments and Mechanical Dimensions of the PBGA

The original pin numbering of the MPC850 conformed to a Freescale proprietary pin numbering scheme that has since been replaced by the JEDEC pin numbering standard for this package type. To support

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

<sup>&</sup>lt;sup>2</sup> 50 MHz version supports 64 time slots on a time division multiplexed line using one SCC

### **Mechanical Data and Ordering Information**

Figure 64 shows the non-JEDEC package dimensions of the PBGA.

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. DIMENSIONS IN MILLIMETERS.

- DIMENSION 6 IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO PRIMARY DATUM C.

- 4. PRIMARY DATUM C AND THE SEATING PLANE ARE

|            | MILLIMETERS |       |  |

|------------|-------------|-------|--|

| DIM        | MIN         | MAX   |  |

| Α          | 1.91        | 2.35  |  |

| <b>A</b> 1 | 0.50        | 0.70  |  |

| A2         | 1.12        | 1.22  |  |

| A3         | 0.29        | 0.43  |  |

| b          | 0.60        | 0.90  |  |

| D          | 23.00 BSC   |       |  |

| D1         | 19.05 REF   |       |  |

| D2         | 19.00       | 20.00 |  |

| Е          | 23.00 BSC   |       |  |

| E1         | 19.05 REF   |       |  |

| E2         | 19.00       | 20.00 |  |

| е          | 1.27 BSC    |       |  |

Figure 64. Package Dimensions for the Plastic Ball Grid Array (PBGA)—non-JEDEC Standard

MPC850 PowerQUICC™ Integrated Communications Processor Hardware Specifications, Rev. 2

**Document Revision History**

# 10 Document Revision History

Table 28 lists significant changes between revisions of this document.

**Table 28. Document Revision History**

| Revision | Date    | Change                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 7/2005  | Added footnote 3 to Table 5 (previously Table 4.5) and deleted IOL limit.                                                                                                                  |

| 1        | 10/2002 | Added MPC850DSL. Corrected Figure 25 on page 34.                                                                                                                                           |

| 0.2      | 04/2002 | Updated power numbers and added Rev. C                                                                                                                                                     |

| 0.1      | 11/2001 | Removed reference to 5 Volt tolerance capability on peripheral interface pins. Replaced SI and IDL timing diagrams with better images. Updated to new template, added this revision table. |