Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Supplier Device Package Purchase URL | 48-LQFP (7x7)<br>https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303cct6 |

|--------------------------------------|----------------------------------------------------------------------------------------|

| Package / Case                       | 48-LQFP                                                                                |

| Mounting Type                        | Surface Mount                                                                          |

| Operating Temperature                | -40°C ~ 85°C (TA)                                                                      |

| Oscillator Type                      | Internal                                                                               |

| Data Converters                      | A/D 15x12b; D/A 2x12b                                                                  |

| Voltage - Supply (Vcc/Vdd)           | 2V ~ 3.6V                                                                              |

| RAM Size                             | 40K x 8                                                                                |

| EEPROM Size                          | -                                                                                      |

| Program Memory Type                  | FLASH                                                                                  |

| Program Memory Size                  | 256КВ (256К х 8)                                                                       |

| Number of I/O                        | 37                                                                                     |

| Peripherals                          | DMA, I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Connectivity                         | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                           |

| Speed                                | 72MHz                                                                                  |

| Core Size                            | 32-Bit Single-Core                                                                     |

| Core Processor                       | ARM® Cortex®-M4                                                                        |

| Product Status                       | Active                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F303xB/STM32F303xC block diagram                                            | 12       |

|------------|----------------------------------------------------------------------------------|----------|

| Figure 2.  | Clock tree                                                                       | 18       |

| Figure 3.  | Infrared transmitter                                                             |          |

| Figure 4.  | STM32F303xB/STM32F303xC LQFP48 pinout                                            | 31       |

| Figure 5.  | STM32F303xB/STM32F303xC LQFP64 pinout                                            | 32       |

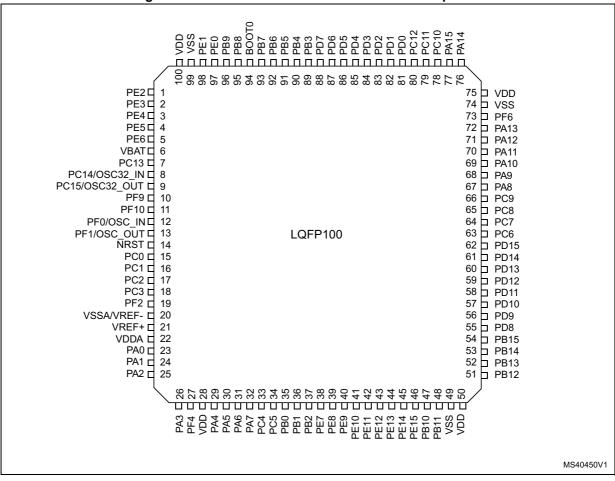

| Figure 6.  | STM32F303xB/STM32F303xC LQFP100 pinout                                           | 33       |

| Figure 7.  | STM32F303xB/STM32F303xC WLCSP100 pinout                                          |          |

| Figure 8.  | STM32F303xB/STM32F303xC memory map                                               |          |

| Figure 9.  | Pin loading conditions.                                                          |          |

| Figure 10. | Pin input voltage                                                                |          |

| Figure 11. | Power supply scheme                                                              |          |

| Figure 12. | Current consumption measurement scheme                                           |          |

| Figure 13. | Typical V <sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00') |          |

| Figure 14. | High-speed external clock source AC timing diagram                               |          |

| Figure 15. | Low-speed external clock source AC timing diagram                                |          |

| Figure 16. | Typical application with an 8 MHz crystal.                                       |          |

| Figure 17. | Typical application with a 32.768 kHz crystal                                    |          |

| Figure 18. | HSI oscillator accuracy characterization results for soldered parts              |          |

| Figure 19. | TC and TTa I/O input characteristics - CMOS port.                                |          |

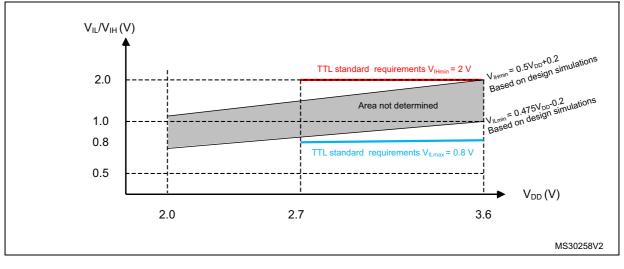

| Figure 20. | TC and TTa I/O input characteristics - TTL port                                  |          |

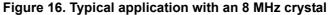

| Figure 21. | Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port.           |          |

| Figure 22. | Five volt tolerant (FT and FTf) I/O input characteristics - TTL port.            |          |

| Figure 23. | I/O AC characteristics definition                                                |          |

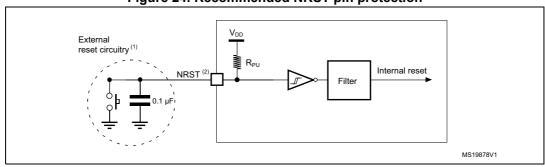

| Figure 24. | Recommended NRST pin protection                                                  |          |

| Figure 25. | I <sup>2</sup> C bus AC waveforms and measurement circuit                        |          |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 0                                     |          |

| Figure 27. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                             | 07       |

| Figure 28. | SPI timing diagram - master mode <sup>(1)</sup>                                  | 08<br>08 |

| Figure 29. | $I^2S$ slave timing diagram (Philips protocol) <sup>(1)</sup>                    | 100      |

| Figure 30. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>         | 100      |

| Figure 31. | USB timings: definition of data signal rise and fall time                        |          |

| Figure 32. | ADC typical current consumption on VDDA pin                                      |          |

| Figure 33. | ADC typical current consumption on VREF+ pin                                     |          |

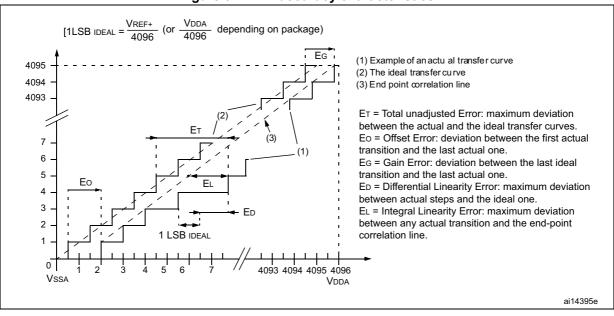

| Figure 34. | ADC accuracy characteristics                                                     |          |

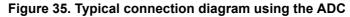

| Figure 35. | Typical connection diagram using the ADC                                         |          |

| Figure 36. | 12-bit buffered /non-buffered DAC                                                |          |

| Figure 30. | Maximum VREFINT scaler startup time from power down                              |          |

| Figure 37. | OPAMP voltage noise versus frequency                                             |          |

| •          |                                                                                  |          |

| Figure 39. | LQFP100 – 14 x 14 mm, low-profile quad flat package outline                      |          |

| Figure 40. |                                                                                  |          |

| Figure 41. | LQFP100 – 14 x 14 mm, low-profile quad flat package top view example             |          |

| Figure 42. | LQFP64 – 10 x 10 mm, low-profile quad flat package outline                       |          |

| Figure 43. | LQFP64 – 10 x 10 mm, low-profile quad flat package recommended footprint         |          |

| Figure 44. | LQFP64 – 10 x 10 mm, low-profile quad flat package top view example              |          |

| Figure 45. | LQFP48 – 7 x 7 mm, low-profile quad flat package outline                         |          |

| Figure 46. | LQFP48 - 7 x 7 mm, low-profile quad flat package recommended footprint.          |          |

| Figure 47. | LQFP48 - 7 x 7 mm, low-profile quad flat package top view example                |          |

| Figure 48. | WLCSP100 – 100L, 4.166 x 4.628 mm 0.4 mm pitch wafer level chip scale            |          |

#### 3.17.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.17.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.17.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 3.18 Real-time clock (RTC) and backup registers

The RTC and the 16 backup registers are supplied through a switch that takes power from either the  $V_{DD}$  supply when present or the  $V_{BAT}$  pin. The backup registers are sixteen 32-bit registers used to store 64 bytes of user application data when  $V_{DD}$  power is not present.

They are not reset by a system or power reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter.It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Automatic correction for 28, 29 (leap year), 30 and 31 days of the month.

- Two programmable alarms with wake up from Stop and Standby mode capability.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stopand Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

#### Figure 6. STM32F303xB/STM32F303xC LQFP100 pinout

|          | Pin nu  | umber  |        |                                                |          |               |       | Pin fu                                                                                | nctions                                                 |  |

|----------|---------|--------|--------|------------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset)       | Pin type | I/O structure | Notes | Alternate functions                                                                   | Additional functions                                    |  |

| C9       | 7       | 2      | 2      | PC13 <sup>(2)</sup>                            | I/O      | тс            | -     | TIM1_CH1N                                                                             | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT                    |  |

| C10      | 8       | 3      | 3      | PC14 <sup>(2)</sup><br>OSC32_IN<br>(PC14)      | I/O      | тс            | -     | -                                                                                     | OSC32_IN                                                |  |

| D9       | 9       | 4      | 4      | PC15 <sup>(2)</sup><br>OSC32_<br>OUT<br>(PC15) | I/O      | тс            | -     | -                                                                                     | OSC32_OUT                                               |  |

| D10      | 10      | -      | -      | PF9                                            | I/O      | FT            | (1)   | TIM15_CH1, SPI2_SCK,<br>EVENTOUT                                                      | -                                                       |  |

| E10      | 11      | -      | -      | PF10                                           | I/O      | FT            | (1)   | TIM15_CH2, SPI2_SCK,<br>EVENTOUT                                                      | -                                                       |  |

| F10      | 12      | 5      | 5      | PF0-<br>OSC_IN<br>(PF0)                        | I/O      | FTf           | -     | TIM1_CH3N, I2C2_SDA,                                                                  | OSC_IN                                                  |  |

| F9       | 13      | 6      | 6      | PF1-<br>OSC_OUT<br>(PF1)                       | I/O      | FTf           | -     | I2C2_SCL                                                                              | OSC_OUT                                                 |  |

| E9       | 14      | 7      | 7      | NRST                                           | I/O      | RS<br>T       |       | Device reset input / intern                                                           | al reset output (active low)                            |  |

| G10      | 15      | 8      | -      | PC0                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN6, COMP7_INM                                    |  |

| G9       | 16      | 9      | 1      | PC1                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN7, COMP7_INP                                    |  |

| G8       | 17      | 10     | -      | PC2                                            | I/O      | TTa           | (1)   | COMP7_OUT, EVENTOUT                                                                   | ADC12_IN8                                               |  |

| H10      | 18      | 11     | -      | PC3                                            |          | TTa           |       | TIM1_BKIN2, EVENTOUT                                                                  | ADC12_IN9                                               |  |

| E8       | 19      | -      | -      | PF2                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN10                                              |  |

| H8       | 20      | 12     | 8      | VSSA/<br>VREF-                                 | S        | -             | -     | Analog ground/Nega                                                                    | tive reference voltage                                  |  |

| J8       | 21      | -      | -      | VREF+ <sup>(3)</sup>                           | s        |               | -     | Positive reference voltage                                                            |                                                         |  |

| J10      | 22      | -      | -      | VDDA                                           | S        | -             | -     | Analog power supply                                                                   |                                                         |  |

| -        | -       | 13     | 9      | VDDA/<br>VREF+                                 | S        | -             | -     | Analog power supply/Positive reference voltage                                        |                                                         |  |

| H9       | 23      | 14     | 10     | PA0                                            | I/O      | ТТа           | (4)   | USART2_CTS,<br>TIM2_CH1_ETR,TIM8_BKIN,<br>TIM8_ETR,TSC_G1_IO1,<br>COMP1_OUT, EVENTOUT | ADC1_IN1, COMP1_INM,<br>RTC_ TAMP2, WKUP1,<br>COMP7_INP |  |

### Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

|                           | Pin nı  | umber  |        |                                          |          |               |       | Pin fur                                                                                                                              | nctions              |  |  |

|---------------------------|---------|--------|--------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| WLCSP100                  | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                  | Additional functions |  |  |

| В5                        | 90      | 56     | 40     | PB4                                      | I/O      | FT            | -     | SPI3_MISO, I2S3ext_SD,<br>SPI1_MISO, USART2_RX,<br>TIM3_CH1, TIM16_CH1,<br>TIM17_BKIN, TIM8_CH2N,<br>TSC_G5_IO2, NJTRST,<br>EVENTOUT | -                    |  |  |

| A6                        | 91      | 57     | 41     | PB5                                      | I/O      | FT            | -     | SPI3_MOSI, SPI1_MOSI,<br>I2S3_SD, I2C1_SMBA,<br>USART2_CK, TIM16_BKIN,<br>TIM3_CH2, TIM8_CH3N,<br>TIM17_CH1, EVENTOUT                | -                    |  |  |

| В6                        | 92      | 58     | 42     | PB6                                      | I/O      | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N, TIM4_CH1,<br>TIM8_CH1,TSC_G5_IO3,<br>TIM8_ETR, TIM8_BKIN2,<br>EVENTOUT                           | -                    |  |  |

| C5                        | 93      | 59     | 43     | PB7                                      | I/O      | FTf           | -     | I2C1_SDA, USART1_RX,<br>TIM3_CH4, TIM4_CH2,<br>TIM17_CH1N, TIM8_BKIN,<br>TSC_G5_IO4, EVENTOUT                                        | -                    |  |  |

| A7                        | 94      | 60     | 44     | BOOT0                                    |          | В             | -     | Boot memo                                                                                                                            | ry selection         |  |  |

| D5                        | 95      | 61     | 45     | PB8                                      | I/O      | FTf           | -     | I2C1_SCL, CAN_RX,<br>TIM16_CH1, TIM4_CH3,<br>TIM8_CH2, TIM1_BKIN,<br>TSC_SYNC, COMP1_OUT,<br>EVENTOUT                                | -                    |  |  |

| C6                        | 96      | 62     | 46     | PB9                                      | I/O      | FTf           | -     | I2C1_SDA, CAN_TX,<br>TIM17_CH1, TIM4_CH4,<br>TIM8_CH3, IR_OUT,<br>COMP2_OUT, EVENTOUT                                                | -                    |  |  |

| B7                        | 97      | -      | -      | PE0                                      | I/O      | FT            | (1)   | USART1_TX, TIM4_ETR,<br>TIM16_CH1, EVENTOUT                                                                                          |                      |  |  |

| A8                        | 98      | -      | -      | PE1                                      | I/O      | FT            | (1)   | USART1_RX, TIM17_CH1,<br>EVENTOUT                                                                                                    | -                    |  |  |

| C7                        | 99      | 63     | 47     | VSS                                      | S        | -             | -     | Gro                                                                                                                                  | und                  |  |  |

| A9,<br>A10,<br>B10,<br>B8 | 100     | 64     | 48     | VDD                                      | S        | -             | -     | Digital power supply                                                                                                                 |                      |  |  |

#### Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

| Bus  | Boundary address          | Size<br>(bytes) | Peripheral         |

|------|---------------------------|-----------------|--------------------|

|      | 0x4000 8000 - 0x4000 FFFF | 32 K            | Reserved           |

|      | 0x4000 7800 - 0x4000 7FFF | 2 K             | Reserved           |

|      | 0x4000 7400 - 0x4000 77FF | 1 K             | DAC (dual)         |

|      | 0x4000 7000 - 0x4000 73FF | 1 K             | PWR                |

|      | 0x4000 6800 - 0x4000 6FFF | 2 K             | Reserved           |

|      | 0x4000 6400 - 0x4000 67FF | 1 K             | bxCAN              |

|      | 0x4000 6000 - 0x4000 63FF | 1 K             | USB SRAM 512 bytes |

|      | 0x4000 5C00 - 0x4000 5FFF | 1 K             | USB device FS      |

|      | 0x4000 5800 - 0x4000 5BFF | 1 K             | I2C2               |

|      | 0x4000 5400 - 0x4000 57FF | 1 K             | I2C1               |

|      | 0x4000 5000 - 0x4000 53FF | 1 K             | UART5              |

|      | 0x4000 4C00 - 0x4000 4FFF | 1 K             | UART4              |

|      | 0x4000 4800 - 0x4000 4BFF | 1 K             | USART3             |

|      | 0x4000 4400 - 0x4000 47FF | 1 K             | USART2             |

| APB1 | 0x4000 4000 - 0x4000 43FF | 1 K             | I2S3ext            |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | 1 K             | SPI3/I2S3          |

|      | 0x4000 3800 - 0x4000 3BFF | 1 K             | SPI2/I2S2          |

|      | 0x4000 3400 - 0x4000 37FF | 1 K             | I2S2ext            |

|      | 0x4000 3000 - 0x4000 33FF | 1 K             | IWDG               |

|      | 0x4000 2C00 - 0x4000 2FFF | 1 K             | WWDG               |

|      | 0x4000 2800 - 0x4000 2BFF | 1 K             | RTC                |

|      | 0x4000 1800 - 0x4000 27FF | 4 K             | Reserved           |

|      | 0x4000 1400 - 0x4000 17FF | 1 K             | TIM7               |

|      | 0x4000 1000 - 0x4000 13FF | 1 K             | TIM6               |

|      | 0x4000 0C00 - 0x4000 0FFF | 1 K             | Reserved           |

|      | 0x4000 0800 - 0x4000 0BFF | 1 K             | TIM4               |

|      | 0x4000 0400 - 0x4000 07FF | 1 K             | ТІМЗ               |

|      | 0x4000 0000 - 0x4000 03FF | 1 K             | TIM2               |

# Table 20. STM32F303xB/STM32F303xC memory map, peripheral register boundary addresses (continued)

# 6.3 Operating conditions

### 6.3.1 General operating conditions

| Table 24. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Symbol             | Parameter                                            | Conditions                                                              | Min  | Max                   | Unit |  |  |

|--------------------|------------------------------------------------------|-------------------------------------------------------------------------|------|-----------------------|------|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                         | -                                                                       | 0    | 72                    |      |  |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                        | -                                                                       | 0    | 36                    | MHz  |  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                        | -                                                                       | 0    | 72                    |      |  |  |

| V <sub>DD</sub>    | Standard operating voltage                           | -                                                                       | 2    | 3.6                   | V    |  |  |

| M                  | Analog operating voltage<br>(OPAMP and DAC not used) | Must have a potential                                                   | 2    | 3.6                   | V    |  |  |

| V <sub>DDA</sub>   | Analog operating voltage (OPAMP and DAC used)        | equal to or higher than<br>V <sub>DD</sub>                              | 2.4  | 3.6                   | V    |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                             | -                                                                       | 1.65 | 3.6                   | V    |  |  |

|                    |                                                      | TC I/O                                                                  | -0.3 | V <sub>DD</sub> +0.3  |      |  |  |

| V                  | I/O input voltage                                    | TTa I/O                                                                 | -0.3 | V <sub>DDA</sub> +0.3 | V    |  |  |

| V <sub>IN</sub>    | I/O Input voltage                                    | FT and FTf I/O <sup>(1)</sup>                                           | -0.3 | 5.5                   | v    |  |  |

|                    |                                                      | BOOT0                                                                   | 0    | 5.5                   |      |  |  |

|                    |                                                      | WLCSP100                                                                | -    | 500                   |      |  |  |

| р                  | Power dissipation at $T_A =$                         | LQFP100                                                                 | -    | 488                   | - mW |  |  |

| $P_{D}$            | 105 °C for suffix $7^{(2)}$                          | LQFP64                                                                  | -    | 444                   |      |  |  |

|                    |                                                      | er dissipation at $T_A =$<br>C for suffix 6 or $T_A =$<br>UQFP100 - 488 | 364  |                       |      |  |  |

|                    | Ambient temperature for 6 suffix version             | Maximum power<br>dissipation                                            | -40  | 85                    | °C   |  |  |

| Та                 |                                                      | Low-power dissipation <sup>(3)</sup>                                    | -40  | 105                   |      |  |  |

| IA                 | Ambient temperature for 7 suffix version             | Maximum power<br>dissipation                                            | -40  | 105                   | °C   |  |  |

|                    |                                                      | Low-power dissipation <sup>(3)</sup>                                    | -40  | 125                   |      |  |  |

| т.                 | lunction tomporature reaso                           | 6 suffix version                                                        | -40  | 105                   | °C   |  |  |

| TJ                 | Junction temperature range                           | 7 suffix version                                                        | -40  | 125                   | − °C |  |  |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

#### 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 39* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep mode: the wakeup event is WFE.

- WKUP1 (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                | Parameter                   | Conditions                        | Typ @Vdd, V <sub>DD</sub> = V <sub>DDA</sub> |       |       |      |       |       | Мах  | Unit                   |

|-----------------------|-----------------------------|-----------------------------------|----------------------------------------------|-------|-------|------|-------|-------|------|------------------------|

| Symbol                | Parameter                   |                                   | 2.0 V                                        | 2.4 V | 2.7 V | 3 V  | 3.3 V | 3.6 V | wiax | Unit                   |

| <sup>t</sup> wustop   | Wakeup from<br>Stop mode    | Regulator in run mode             | 4.1                                          | 3.9   | 3.8   | 3.7  | 3.6   | 3.5   | 4.5  |                        |

|                       |                             | Regulator in<br>low-power<br>mode | 7.9                                          | 6.7   | 6.1   | 5.7  | 5.4   | 5.2   | 9    | μs                     |

| $t_{WUSTANDBY}^{(1)}$ | Wakeup from<br>Standby mode | LSI and<br>IWDG OFF               | 69.2                                         | 60.3  | 56.4  | 53.7 | 51.7  | 50    | 100  |                        |

| t <sub>WUSLEEP</sub>  | Wakeup from<br>Sleep mode   | -                                 |                                              | 6     |       |      |       |       | -    | CPU<br>clock<br>cycles |

Table 39. Low-power mode wakeup timings

1. Guaranteed by characterization results.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 16*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53.

Figure 21. Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port

Figure 22. Five volt tolerant (FT and FTf) I/O input characteristics - TTL port

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 23* and *Table 56*, respectively.

Unless otherwise specified, the parameters given are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| OSPEEDRy [1:0]<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                                                | Min               | Max                | Unit |  |

|----------------------------------------|-------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|--------------------|------|--|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                    | -                 | 2 <sup>(3)</sup>   | MHz  |  |

| x0                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | -C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                   | -                 | 125 <sup>(3)</sup> | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | -C <sub>L</sub> - 50 μr, v <sub>DD</sub> - 2 v to 3.6 v                   | -                 | 125 <sup>(3)</sup> | 115  |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                    | -                 | 10 <sup>(3)</sup>  | MHz  |  |

| 01                                     | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | -C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                   | -                 | 25 <sup>(3)</sup>  |      |  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | $V_{\rm L} = 50  \text{pr},  V_{\rm DD} = 2  \text{V}  10  3.6  \text{V}$ | -                 | 25 <sup>(3)</sup>  | ns   |  |

|                                        | f <sub>max(IO)out</sub> |                                                                 | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -                 | 50 <sup>(3)</sup>  | MHz  |  |

|                                        |                         | Maximum frequency <sup>(2)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -                 | 30 <sup>(3)</sup>  | MHz  |  |

|                                        |                         |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                  | -                 | 20 <sup>(3)</sup>  | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   |                                                                 | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -                 | 5 <sup>(3)</sup>   |      |  |

| 11                                     |                         | Output high to low level fall time                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -                 | 8 <sup>(3)</sup>   | - ns |  |

|                                        |                         |                                                                 | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                    | -                 | 12 <sup>(3)</sup>  |      |  |

|                                        |                         |                                                                 | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                                  | -                 | 5 <sup>(3)</sup>   |      |  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                                | -                 | 8 <sup>(3)</sup>   |      |  |

|                                        |                         |                                                                 | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                                    | -                 | 12 <sup>(3)</sup>  |      |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                |                                                                           | -                 | 2 <sup>(4)</sup>   | MHz  |  |

| FM+<br>configuration <sup>(4)</sup>    | t <sub>f(IO)out</sub>   | Output high to low level fall time                              | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V                    | -                 | 12 <sup>(4)</sup>  | 20   |  |

|                                        | t <sub>r(IO)out</sub>   | Output low to high level rise time                              |                                                                           | -                 | 34 <sup>(4)</sup>  | ns   |  |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                                         | 10 <sup>(3)</sup> | -                  | ns   |  |

Table 56. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the RM0316 reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 23*.

3. Guaranteed by design.

4. The I/O speed configuration is bypassed in FM+ I/O mode. Refer to the STM32F303x STM32F313xx reference manual RM0316 for a description of FM+ I/O mode configuration.

Figure 24. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 57. Otherwise the reset will not be taken into account by the device.

#### 6.3.16 Timer characteristics

The parameters given in *Table 58* are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                   | Conditions                              | Min    | Мах                     | Unit                 |  |

|------------------------|-----------------------------|-----------------------------------------|--------|-------------------------|----------------------|--|

|                        |                             | -                                       | 1      | -                       | t <sub>TIMxCLK</sub> |  |

| t <sub>res(TIM)</sub>  | Timer resolution time       | f <sub>TIMxCLK</sub> = 72 MHz           | 13.9   | -                       | ns                   |  |

|                        |                             | f <sub>TIMxCLK</sub> = 144 MHz<br>x=1.8 | 6.95   | -                       | ns                   |  |

| f <sub>EXT</sub>       | Timer external clock        | -                                       | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| 'EXT                   | frequency on CH1 to CH4     | f <sub>TIMxCLK</sub> = 72 MHz           | 0      | 36                      | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution            | TIMx (except TIM2)                      | -      | 16                      | bit                  |  |

| TC31M                  |                             | TIM2                                    | -      | 32                      | DIL                  |  |

|                        |                             | -                                       | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

| t <sub>COUNTER</sub>   | 16-bit counter clock period | f <sub>TIMxCLK</sub> = 72 MHz           | 0.0139 | 910                     | μs                   |  |

| OCONTER                |                             | f <sub>TIMxCLK</sub> = 144 MHz<br>x=1.8 | 0.0069 | 455                     | μs                   |  |

|                        |                             | -                                       | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count      | f <sub>TIMxCLK</sub> = 72 MHz           | -      | 59.65                   | S                    |  |

| MAX_COUNT              | with 32-bit counter         | f <sub>TIMxCLK</sub> = 144 MHz<br>x=1.8 | -      | 29.825                  | S                    |  |

Table 58. TIMx<sup>(1)(2)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4, TIM8, TIM15, TIM16 and TIM17 timers.

2. Guaranteed by design.

3. Channels available on PA2, PA6, PB1, PB12.

| Symbol               | Parameter                                      | (                                    | Conditions                    |                     | Min<br>(3)          | Тур                 | Max<br>(3)   | Unit                |      |    |

|----------------------|------------------------------------------------|--------------------------------------|-------------------------------|---------------------|---------------------|---------------------|--------------|---------------------|------|----|

|                      |                                                |                                      | Cingle ended                  | Fast channel 5.1 Ms | -                   | ±3.5                | ±4.5         |                     |      |    |

| ET                   | Total                                          |                                      | Single ended                  | Slow channel 4.8 Ms | -                   | <u>±4</u>           | ±4.5         |                     |      |    |

|                      | unadjusted<br>error                            |                                      | Differential                  | Fast channel 5.1 Ms | -                   | ±3                  | ±3           |                     |      |    |

|                      |                                                |                                      | Dillerential                  | Slow channel 4.8 Ms | -                   | ±3                  | ±3           |                     |      |    |

|                      |                                                |                                      | Single ended                  | Fast channel 5.1 Ms | -                   | ±1                  | ±1.5         | 1                   |      |    |

| EO                   | Offset error                                   |                                      | Single ended                  | Slow channel 4.8 Ms | -                   | ±1                  | ±2.5         |                     |      |    |

| EO                   | Olisetenoi                                     |                                      | Differential                  | Fast channel 5.1 Ms | -                   | ±1                  | ±1.5         |                     |      |    |

|                      |                                                |                                      | Dillerential                  | Slow channel 4.8 Ms | -                   | ±1                  | ±1.5         |                     |      |    |

|                      |                                                |                                      | Single ended                  | Fast channel 5.1 Ms | -                   | ±3                  | ±4           | - LSB               |      |    |

| FC                   | Coin orror                                     | ain error                            | Single ended                  | Slow channel 4.8 Ms | -                   | ±3.5                | ±4           |                     |      |    |

| EG                   | Gain error                                     |                                      | Differential                  | Fast channel 5.1 Ms | -                   | ±1.5                | ±2.5         |                     |      |    |

|                      |                                                |                                      |                               | Slow channel 4.8 Ms | -                   | ±2                  | ±2.5         |                     |      |    |

| ED                   | Differential<br>linearity<br>error             |                                      | ADC clock freq. $\leq$ 72 MHz | Single ended        | Fast channel 5.1 Ms | -                   | ±1           | ±1.5                | 1    |    |

|                      |                                                | hearity $V_{DDA} = V_{REF+} = 3.3 V$ | Single ended                  | Slow channel 4.8 Ms | -                   | ±1                  | ±1.5         |                     |      |    |

|                      |                                                |                                      | Differential                  | Fast channel 5.1 Ms | -                   | ±1                  | ±1           |                     |      |    |

|                      |                                                |                                      |                               |                     | 1                   | 100-pin package     | Dillerential | Slow channel 4.8 Ms | -    | ±1 |

| EL                   | Integral<br>linearity<br>error                 | linearity                            |                               | Single ended        | Fast channel 5.1 Ms | -                   | ±1.5         | ±2                  |      |    |

|                      |                                                |                                      |                               |                     | Slow channel 4.8 Ms | -                   | ±1.5         | ±3                  |      |    |

|                      |                                                |                                      | -                             |                     | Differential        | Fast channel 5.1 Ms | -            | ±1                  | ±1.5 |    |

|                      |                                                |                                      |                               |                     | Dillerential        | Slow channel 4.8 Ms | -            | ±1                  | ±1.5 |    |

| ENOB <sup>(4)</sup>  | Effective<br>number of<br>bits                 | number of                            | Single ended                  | Fast channel 5.1 Ms | 10.7                | 10.8                | -            | - bits              |      |    |

|                      |                                                |                                      |                               | Slow channel 4.8 Ms | 10.7                | 10.8                | -            |                     |      |    |

|                      |                                                |                                      |                               | Fast channel 5.1 Ms | 11.2                | 11.3                | -            |                     |      |    |

|                      |                                                |                                      |                               | Slow channel 4.8 Ms | 11.1                | 11.3                | -            |                     |      |    |

| SINAD <sup>(4)</sup> | Signal-to-<br>noise and<br>distortion<br>ratio | noise and<br>distortion              | Single ended                  | Fast channel 5.1 Ms | 66                  | 67                  | -            | - dB                |      |    |

|                      |                                                |                                      |                               | Slow channel 4.8 Ms | 66                  | 67                  | -            |                     |      |    |

| SINAD' /             |                                                |                                      |                               | Fast channel 5.1 Ms | 69                  | 70                  | -            |                     |      |    |

|                      |                                                |                                      |                               | Slow channel 4.8 Ms | 69                  | 70                  | -            |                     |      |    |

| Table 10. Abc accuracy - infined lest conditions, 100-pin packages | Table 70. ADC accuracy | y - limited test condition | ıs, 100-pin packages <sup>(1)</sup> | (2) |

|--------------------------------------------------------------------|------------------------|----------------------------|-------------------------------------|-----|

|--------------------------------------------------------------------|------------------------|----------------------------|-------------------------------------|-----|

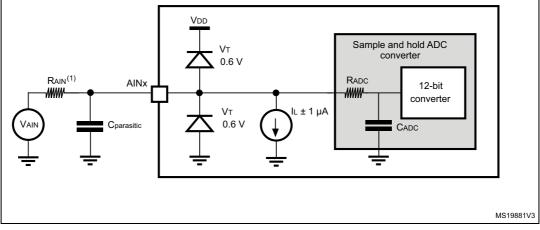

#### Figure 34. ADC accuracy characteristics

1. Refer to *Table 68* for the values of R<sub>AIN</sub>.

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 11*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### **Electrical characteristics**

| Symbol           | Parameter             | Conditio                                 | ons                   | Min | Тур | Max | Unit |

|------------------|-----------------------|------------------------------------------|-----------------------|-----|-----|-----|------|

|                  |                       | No hysteresis<br>(COMPxHYST[1:0]=00)     | -                     | -   | 0   | -   |      |

| V <sub>hys</sub> |                       |                                          | High speed mode       | 3   |     | 13  |      |

|                  | Comparator hysteresis | Low hysteresis<br>(COMPxHYST[1:0]=01)    | All other power modes | 5   | 8   | 10  | m∨   |

|                  |                       | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7   | 15  | 26  |      |

|                  |                       |                                          | All other power modes | 9   |     | 19  |      |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | High speed mode       | 18  | 31  | 49  |      |

|                  |                       |                                          | All other power modes | 19  |     | 40  |      |

| Table 76. Comparator characteristics <sup>(1)</sup> (co | ontinued) |

|---------------------------------------------------------|-----------|

|---------------------------------------------------------|-----------|

1. Data guaranteed by design.

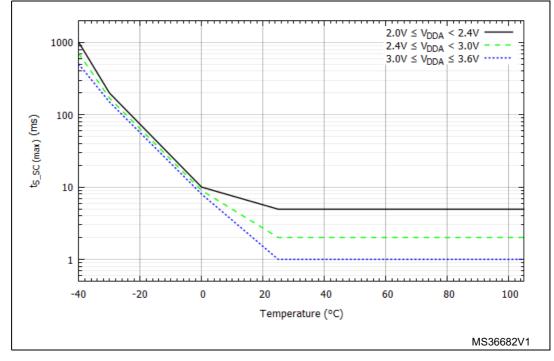

2. For more details and conditions, see Figure 37 Maximum V\_{REFINT} scaler startup time from power down.

#### Figure 37. Maximum $V_{REFINT}$ scaler startup time from power down

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

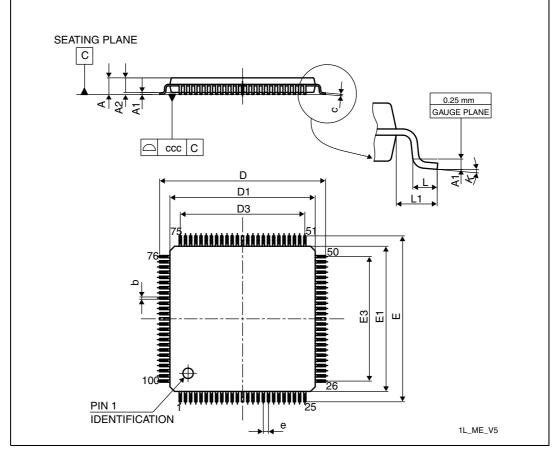

# 7.1 LQFP100 – 14 x 14 mm, low-profile quad flat package information

Figure 39. LQFP100 – 14 x 14 mm, low-profile quad flat package outline

1. Drawing is not to scale.

Table 81. LQPF100 – 14 x 14 mm, low-profile quad flat package mechanical data

| Symbol |      | millimeters |      |       | inches <sup>(1)</sup> |        |

|--------|------|-------------|------|-------|-----------------------|--------|

| Symbol | Min  | Тур         | Max  | Min   | Тур                   | Max    |

| А      | -    | -           | 1.60 | -     | -                     | 0.063  |

| A1     | 0.05 | -           | 0.15 | 0.002 | -                     | 0.0059 |

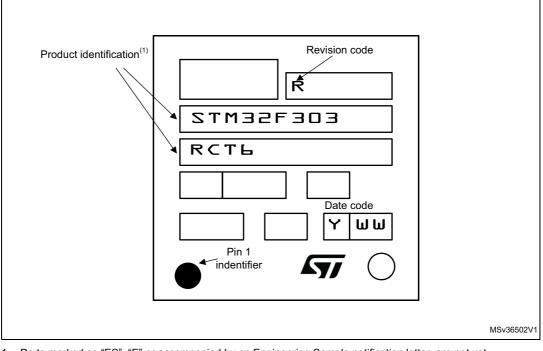

#### Device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 44. LQFP64 – 10 x 10 mm, low-profile quad flat package top view example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Table 88. Document revision history (continued) |          |                                                                                                                               |  |  |

|-------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                       |  |  |

|                                                 |          | Updated first page<br>Removed references to VDDSDx and VSSSD                                                                  |  |  |

|                                                 |          | Added reference to PM0214 in Section 1                                                                                        |  |  |

|                                                 |          | Moved Temp. sensor calibartion values to Table 79 and VREF calibration                                                        |  |  |

|                                                 |          | values to Table 29                                                                                                            |  |  |

|                                                 |          | Updated Table 3: STM32F303xx family device features and peripheral                                                            |  |  |

|                                                 |          | counts                                                                                                                        |  |  |

|                                                 |          | Updated Section 3.4: Embedded SRAM                                                                                            |  |  |

|                                                 |          | Updated Section 3.2: Memory protection unit (MPU)                                                                             |  |  |

|                                                 |          | Updated Section 3.24: Universal serial bus (USB)                                                                              |  |  |

|                                                 |          | Modified Section 3.26: Touch sensing controller (TSC)                                                                         |  |  |

|                                                 |          | Updated heading of Table 11: USART features                                                                                   |  |  |

|                                                 |          | Updated Table 16: STM32F302xB/STM32F302xC pin definitions                                                                     |  |  |

|                                                 |          | Added notes to PC13, PC14 and PC15 in <i>Table 16:</i>                                                                        |  |  |

|                                                 |          | STM32F302xB/STM32F302xC pin definitions                                                                                       |  |  |

|                                                 |          | Updated Figure 11: Power supply scheme                                                                                        |  |  |

|                                                 |          | Modified Table 21: Voltage characteristics<br>Modified Table 22: Current characteristics                                      |  |  |

|                                                 |          | Modified Table 22: Current characteristics<br>Modified Table 24: General operating conditions                                 |  |  |

|                                                 |          | Modified Figure 13: Typical VBAT current consumption (LSE and RTC                                                             |  |  |

|                                                 |          | ON/LSEDRV[1:0] = '00')                                                                                                        |  |  |

|                                                 |          | Updated Section 6.3.14: I/O port characteristics                                                                              |  |  |

|                                                 |          | Updated Table 30: Typical and maximum current consumption from VDD                                                            |  |  |

|                                                 |          | supply at VDD = 3.6V and Table 31: Typical and maximum current                                                                |  |  |

|                                                 |          | consumption from the VDDA supply                                                                                              |  |  |

|                                                 |          | Updated Table 32: Typical and maximum VDD consumption in Stop and                                                             |  |  |

| 05-Dec-2012                                     | 4        | Standby modes and Table 33: Typical and maximum VDDA consumption                                                              |  |  |

|                                                 |          | in Stop and Standby modes                                                                                                     |  |  |

|                                                 |          | Updated Table 34: Typical and maximum current consumption from                                                                |  |  |

|                                                 |          | VBAT supply                                                                                                                   |  |  |

|                                                 |          | Added Figure 13: Typical VBAT current consumption (LSE and RTC                                                                |  |  |

|                                                 |          | ON/LSEDRV[1:0] = '00')                                                                                                        |  |  |

|                                                 |          | Updated Table 35: Typical current consumption in Run mode, code with                                                          |  |  |

|                                                 |          | data processing running from Flash and Table 36: Typical current<br>consumption in Sleep mode, code running from Flash or RAM |  |  |

|                                                 |          | Added Table 38: Peripheral current consumption                                                                                |  |  |

|                                                 |          | Added Table 37: Switching output I/O current consumption                                                                      |  |  |

|                                                 |          | Updated Section 6.3.6: Wakeup time from low-power mode                                                                        |  |  |

|                                                 |          | Modified ESD absolute maximum ratings                                                                                         |  |  |

|                                                 |          | Modified Table 55: Output voltage characteristics                                                                             |  |  |

|                                                 |          | Updated EMI characteristics                                                                                                   |  |  |

|                                                 |          | Updated Table 56: I/O AC characteristics                                                                                      |  |  |

|                                                 |          | Updated Table 53: I/O current injection susceptibility                                                                        |  |  |

|                                                 |          | Updated Table 58: TIMx characteristics                                                                                        |  |  |

|                                                 |          | Updated Section 7.4: WLCSP100 - 0.4 mm pitch wafer level chip scale                                                           |  |  |

|                                                 |          | package information                                                                                                           |  |  |

|                                                 |          | Added Table 69: Maximum ADC RAIN                                                                                              |  |  |

|                                                 |          | Added Table 70: ADC accuracy - limited test conditions, 100-pin                                                               |  |  |

|                                                 |          | packages                                                                                                                      |  |  |

|                                                 |          | Updated Table 64: ADC accuracy - limited test conditions 2)                                                                   |  |  |

|                                                 |          | Updated Table 75: DAC characteristics                                                                                         |  |  |

|                                                 |          | Updated Table 77: Operational amplifier characteristics<br>Updated figures and tables in Section 7: Package information       |  |  |

|                                                 |          |                                                                                                                               |  |  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |          | Updated <i>Table 50: EMI characteristics</i> conditions :3.3v replaced by 3.6V.<br>Updated <i>Section 6.3.17: Communications interfaces</i> I <sup>2</sup> C interface.<br>Updated <i>Table 77: Operational amplifier characteristics</i> adding<br>TS_OPAMP_VOUT row.<br>Updated <i>Section 3.13: Fast analog-to-digital converter (ADC).</i><br>updated ARM and Cortex trademark.<br>Updated <i>Table 32: Typical and maximum VDD consumption in Stop and</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 18-Apr-2014 | 8        | Standby modes with Max value at 85°C and 105°C.<br>Updated Table 70: ADC accuracy - limited test conditions, 100-pin<br>packages and Table 71: ADC accuracy, 100-pin packages for 100-pin<br>package.<br>Added Table 72: ADC accuracy - limited test conditions, 64-pin<br>packages and Table 73: ADC accuracy, 64-pin packagesfor 64-pin<br>package.<br>Added Table 74: ADC accuracy at 1MSPS for 1MSPS sampling<br>frequency.<br>Updated Table 63: SPI characteristics.<br>Updated Table 75: DAC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 09-Dec-2014 | 9        | Updated core description in cover page.<br>Updated HSI characteristics <i>Table 44: HSI oscillator characteristics</i> and<br><i>Figure 18: HSI oscillator accuracy characterization results for soldered</i><br><i>parts.</i><br>Updated <i>Table 58: TIMx characteristics.</i><br>Updated <i>Table 16: STM32F302xB/STM32F302xC pin definitions</i> adding<br>note for I/Os featuring an analog output function<br>(DAC_OUT,OPAMP_OUT).<br>Updated <i>Table 68: ADC characteristics</i> adding IDDA & IREF<br>consumptions.<br>Added <i>Figure 32: ADC typical current consumption on VDDA pin</i> and<br><i>Figure 33: ADC typical current consumption on VDDA pin</i> and<br><i>Figure 33: ADC typical current consumption on VREF+ pin.</i><br>Added Section 3.8: Interconnect matrix.<br>Updated <i>Figure 5: Clock tree.</i><br>Added note after <i>Table 32: Typical and maximum VDD consumption in</i><br><i>Stop and Standby modes.</i><br>Updated Section : In order to meet environmental requirements, ST<br>offers these devices in different grades of ECOPACK® packages,<br>depending on their level of environmental compliance. ECOPACK®<br>specifications, grade definitions and product status are available at:<br><i>www.st.com. ECOPACK® is an ST trademark.</i> with new LQFP100,<br>LQFP64, LQFP48 package marking.<br>Updated <i>Table 16: STM32F302xB/STM32F302xC pin definitions</i> and<br>alternate functions tables replacing usart_rts by usart_rts_de. |  |  |

| 29-Jan-2015 | 10       | Updated Section 6.3.20: Comparator characteristics modifying ts_sc characteristics in Table 76 and adding Figure 37: Maximum VREFINT scaler startup time from power down.<br>Updated I <sub>DD</sub> data in Table 42: HSE oscillator characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Table 88. D | Ocument revision | history | (continued) |

|-------------|------------------|---------|-------------|

|-------------|------------------|---------|-------------|