Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 52                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303rbt6tr |

# List of tables

| Table 1.  | Device summary                                                                                                                                                                                    | . 1 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F303xB/STM32F303xC family device features and peripheral counts                                                                                                                              |     |

| Table 3.  | External analog supply values for analog peripherals                                                                                                                                              |     |

| Table 4.  | STM32F303xB/STM32F303xC peripheral interconnect matrix                                                                                                                                            |     |

| Table 5.  | Timer feature comparison                                                                                                                                                                          |     |

| Table 6.  | Comparison of I2C analog and digital filters                                                                                                                                                      |     |

| Table 7.  | STM32F303xB/STM32F303xC I <sup>2</sup> C implementation                                                                                                                                           |     |

| Table 8.  | USART features                                                                                                                                                                                    |     |

| Table 9.  | STM32F303xB/STM32F303xC SPI/I2S implementation                                                                                                                                                    |     |

| Table 10. | Capacitive sensing GPIOs available on STM32F303xB/STM32F303xC devices                                                                                                                             |     |

| Table 11. | No. of capacitive sensing channels available on STM32F303xB/STM32F303xC devices . 2                                                                                                               |     |

| Table 12. | Legend/abbreviations used in the pinout table                                                                                                                                                     |     |

| Table 13. | STM32F303xB/STM32F303xC pin definitions                                                                                                                                                           |     |

| Table 14. | Alternate functions for port A                                                                                                                                                                    |     |

| Table 15. | Alternate functions for port B                                                                                                                                                                    |     |

| Table 16. | Alternate functions for port C                                                                                                                                                                    |     |

| Table 17. | Alternate functions for port D                                                                                                                                                                    |     |

| Table 18. | Alternate functions for port E                                                                                                                                                                    |     |

| Table 19. | Alternate functions for port F                                                                                                                                                                    |     |

| Table 20. | STM32F303xB/STM32F303xC memory map, peripheral register boundary addresses §                                                                                                                      |     |

| Table 21. | Voltage characteristics                                                                                                                                                                           |     |

| Table 22. | Current characteristics                                                                                                                                                                           |     |

| Table 23. | Thermal characteristics                                                                                                                                                                           | 58  |

| Table 24. | General operating conditions                                                                                                                                                                      | 59  |

| Table 25. | Operating conditions at power-up / power-down                                                                                                                                                     |     |

| Table 26. | Embedded reset and power control block characteristics                                                                                                                                            |     |

| Table 27. | Programmable voltage detector characteristics                                                                                                                                                     |     |

| Table 28. | Embedded internal reference voltage                                                                                                                                                               |     |

| Table 29. | Internal reference voltage calibration values                                                                                                                                                     |     |

| Table 30. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD} = 3.6V \dots \dots$ |     |

| Table 31. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                                                                                                                          |     |

| Table 32. | Typical and maximum V <sub>DD</sub> consumption in Stop and Standby modes                                                                                                                         |     |

| Table 33. | Typical and maximum V <sub>DDA</sub> consumption in Stop and Standby modes                                                                                                                        |     |

| Table 34. | Typical and maximum current consumption from V <sub>BAT</sub> supply                                                                                                                              |     |

| Table 35. | Typical current consumption in Run mode, code with data processing running from Flash6                                                                                                            | 37  |

| Table 36. | Typical current consumption in Sleep mode, code running from Flash or RAM                                                                                                                         | 38  |

| Table 37. | Switching output I/O current consumption                                                                                                                                                          |     |

| Table 38. | Peripheral current consumption                                                                                                                                                                    | 71  |

| Table 39. | Low-power mode wakeup timings                                                                                                                                                                     | 73  |

| Table 40. | High-speed external user clock characteristics                                                                                                                                                    | 74  |

| Table 41. | Low-speed external user clock characteristics                                                                                                                                                     | 75  |

| Table 42. | HSE oscillator characteristics                                                                                                                                                                    | 76  |

| Table 43. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                                                                                                                    | 78  |

| Table 44. | HSI oscillator characteristics                                                                                                                                                                    |     |

| Table 45. | LSI oscillator characteristics                                                                                                                                                                    | 80  |

| Table 46. | PLL characteristics                                                                                                                                                                               |     |

| Table 47. | Flash memory characteristics                                                                                                                                                                      | 81  |

| Table 48. | Flash memory endurance and data retention                                                                                                                                                         |     |

#### 3.10 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current capable except for analog inputs.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allows I/O toggling up to 36 MHz.

#### 3.11 Direct memory access (DMA)

The flexible general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each of the 12 DMA channels is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers, DAC and ADC.

### 3.12 Interrupts and events

#### 3.12.1 Nested vectored interrupt controller (NVIC)

The STM32F303xB/STM32F303xC devices embed a nested vectored interrupt controller (NVIC) able to handle up to 66 maskable interrupt channels and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

|          | Pin nu  | ımber  |        |                                          |          |               |       | Pin fu                                                                                   | nctions                                             |

|----------|---------|--------|--------|------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------|-----------------------------------------------------|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                      | Additional functions                                |

| J3       | 52      | 34     | 26     | PB13                                     | I/O      | ТТа           | (4)   | SPI2_SCK,I2S2_CK,USART3<br>_CTS, TIM1_CH1N,<br>TSC_G6_IO3, EVENTOUT                      | ADC3_IN5, COMP5_INP,<br>OPAMP4_VINP,<br>OPAMP3_VINP |

| J2       | 53      | 35     | 27     | PB14                                     | I/O      | TTa           | (4)   | SPI2_MISO,I2S2ext_SD,<br>USART3_RTS_DE,<br>TIM1_CH2N, TIM15_CH1,<br>TSC_G6_IO4, EVENTOUT | COMP3_INP, ADC4_IN4,<br>OPAMP2_VINP                 |

| H4       | 54      | 36     | 28     | PB15                                     | I/O      | ТТа           | (4)   | SPI2_MOSI, I2S2_SD,<br>TIM1_CH3N, RTC_REFIN,<br>TIM15_CH1N, TIM15_CH2,<br>EVENTOUT       | ADC4_IN5, COMP6_INM                                 |

| -        | 55      | -      | ı      | PD8                                      | I/O      | TTa           | (1)   | USART3_TX, EVENTOUT                                                                      | ADC4_IN12, OPAMP4_VINM                              |

| G4       | 56      | -      | ı      | PD9                                      | I/O      | TTa           | (1)   | USART3_RX, EVENTOUT                                                                      | ADC4_IN13                                           |

| Н3       | 57      | ı      | ı      | PD10                                     | 9        | TTa           | (1)   | USART3_CK, EVENTOUT                                                                      | ADC34_IN7, COMP6_INM                                |

| H2       | 58      | 1      | -      | PD11                                     | I/O      | ТТа           | (1)   | USART3_CTS, EVENTOUT                                                                     | ADC34_IN8, COMP6_INP,<br>OPAMP4_VINP                |

| H1       | 59      | 1      | -      | PD12                                     | I/O      | ТТа           | (1)   | USART3_RTS_DE,<br>TIM4_CH1, TSC_G8_IO1,<br>EVENTOUT                                      | ADC34_IN9, COMP5_INP                                |

| G3       | 60      | 1      | -      | PD13                                     | I/O      | ТТа           | (1)   | TIM4_CH2, TSC_G8_IO2,<br>EVENTOUT                                                        | ADC34_IN10, COMP5_INM                               |

| G2       | 61      | -      | -      | PD14                                     | I/O      | ТТа           | (1)   | TIM4_CH3, TSC_G8_IO3,<br>EVENTOUT                                                        | COMP3_INP, ADC34_IN11,<br>OPAMP2_VINP               |

| G1       | 62      |        | -      | PD15                                     | I/O      | ТТа           | (1)   | SPI2_NSS, TIM4_CH4,<br>TSC_G8_IO4, EVENTOUT                                              | COMP3_INM                                           |

| F4       | 63      | 37     | -      | PC6                                      | I/O      | FT            | (1)   | I2S2_MCK, COMP6_OUT,<br>TIM8_CH1, TIM3_CH1,<br>EVENTOUT                                  | -                                                   |

| F2       | 64      | 38     | -      | PC7                                      | I/O      | FT            | (1)   | I2S3_MCK, TIM8_CH2,<br>TIM3_CH2, COMP5_OUT,<br>EVENTOUT                                  | -                                                   |

| F1       | 65      | 39     | -      | PC8                                      | I/O      | FT            | (1)   | TIM8_CH3, TIM3_CH3,<br>COMP3_OUT, EVENTOUT                                               | -                                                   |

| F3       | 66      | 40     | -      | PC9                                      | I/O      | FT            | (1)   | TIM8_CH4,<br>TIM8_BKIN2,TIM3_CH4,<br>I2S_CKIN, EVENTOUT                                  | -                                                   |

Table 27. Programmable voltage detector characteristics

| Symbol                              | Parameter               | Conditions   | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup>                                                                                                                                                                                                                                                                           | Unit |

|-------------------------------------|-------------------------|--------------|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V                                   | PVD threshold 0         | Rising edge  | 2.1                | 2.18 | 2.26                                                                                                                                                                                                                                                                                         |      |

| V <sub>PVD0</sub>                   | F VD tillesiloid 0      | Falling edge | 2                  | 2.08 | 2.16                                                                                                                                                                                                                                                                                         |      |

| V                                   | PVD threshold 1         | Rising edge  | 2.19               | 2.28 | 2.37                                                                                                                                                                                                                                                                                         |      |

| V <sub>PVD1</sub>                   | F VD tillesiloid i      | Falling edge | 2.09               | 2.18 | 2.27                                                                                                                                                                                                                                                                                         |      |

| V                                   | PVD threshold 2         | Rising edge  | 2.28               | 2.38 | 2.48                                                                                                                                                                                                                                                                                         |      |

| V <sub>PVD2</sub>                   | 1 VD tilleshold 2       | Falling edge | 2.18               | 2.28 | 2.38                                                                                                                                                                                                                                                                                         |      |

| V                                   | PVD threshold 3         | Rising edge  | 2.38               | 2.48 | 2.58                                                                                                                                                                                                                                                                                         |      |

| V <sub>PVD3</sub>                   | PVD tillesiloid 3       | Falling edge | 2.28               | 2.38 | 2.48                                                                                                                                                                                                                                                                                         | V    |

| V                                   | PVD threshold 4         | Rising edge  | 2.47               | 2.58 | 2.69                                                                                                                                                                                                                                                                                         | V    |

| $V_{PVD4}$                          | PVD tillesiloid 4       | Falling edge | 2.37               | 2.48 | 2.59                                                                                                                                                                                                                                                                                         |      |

| V                                   | PVD threshold 5         | Rising edge  | 2.57               | 2.68 | 2.79                                                                                                                                                                                                                                                                                         |      |

| V <sub>PVD5</sub>                   | PVD threshold 5         | Falling edge | 2.47               | 2.58 | 2.08     2.16       2.28     2.37       2.18     2.27       2.38     2.48       2.28     2.38       2.48     2.58       2.38     2.48       2.58     2.69       2.48     2.59       2.68     2.79       2.58     2.69       2.78     2.9       2.68     3       2.78     2.9       100     - |      |

| V                                   | PVD threshold 6         | Rising edge  | 2.66               | 2.78 | 2.9                                                                                                                                                                                                                                                                                          |      |

| V <sub>PVD6</sub>                   | PVD threshold 6         | Falling edge | 2.56               | 2.68 | 2.8                                                                                                                                                                                                                                                                                          |      |

| V                                   | D\/D throohold 7        | Rising edge  | 2.76               | 2.88 | 3                                                                                                                                                                                                                                                                                            |      |

| V <sub>PVD7</sub>                   | PVD threshold 7         | Falling edge | 2.66               | 2.78 | 2.9                                                                                                                                                                                                                                                                                          |      |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis          | -            | -                  | 100  | -                                                                                                                                                                                                                                                                                            | mV   |

| IDD(PVD)                            | PVD current consumption | -            | -                  | 0.15 | 0.26                                                                                                                                                                                                                                                                                         | μA   |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> Guaranteed by design.

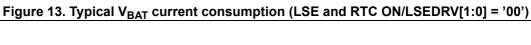

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

| Symbol               | Para              | /4\                                                                                           |       | Typ @V <sub>BAT</sub> |      |      |      |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |     |                           | Unit |

|----------------------|-------------------|-----------------------------------------------------------------------------------------------|-------|-----------------------|------|------|------|------|------|------|-------------------------------------------------|-----|---------------------------|------|

| Symbol               | meter             |                                                                                               | 1.65V | 1.8V                  | 2V   | 2.4V | 2.7V | 3V   | 3.3V | 3.6V | T <sub>A</sub> = 25°C                           |     | T <sub>A</sub> =<br>105°C | Ome  |

| I <sub>DD_VBAT</sub> | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48  | 0.50                  | 0.52 | 0.58 | 0.65 | 0.72 | 0.80 | 0.90 | 1.1                                             | 1.5 | 2.0                       |      |

|                      | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83  | 0.86                  | 0.90 | 0.98 | 1.03 | 1.10 | 1.20 | 1.30 | 1.5                                             | 2.2 | 2.9                       | μΑ   |

<sup>1.</sup> Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

<sup>2.</sup> Guaranteed by characterization results.

#### **Typical current consumption**

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins available on each package are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait states from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz), and Flash prefetch is ON

- When the peripherals are enabled, f<sub>APB1</sub> = f<sub>AHB/2</sub>, f<sub>APB2</sub> = f<sub>AHB</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8,16 and 64 is used for the frequencies 4 MHz, 2 MHz, 1 MHz, 500 kHz and 125 kHz respectively.

Table 35. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 |                      |                   | Ту                     | ур                      |             |  |  |

|-------------------------------------|---------------------------------|----------------------|-------------------|------------------------|-------------------------|-------------|--|--|

| Symbol                              | Parameter                       | Conditions           | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit        |  |  |

|                                     |                                 |                      | 72 MHz            | 61.3                   | 28.0                    |             |  |  |

|                                     |                                 |                      | 64 MHz            | 54.8                   | 25.4                    | 1           |  |  |

|                                     |                                 |                      | 48 MHz            | 41.9                   | 19.3                    |             |  |  |

|                                     |                                 |                      | 32 MHz            | 28.5                   | 13.3                    |             |  |  |

|                                     |                                 |                      | 24 MHz            | 21.8                   | 10.4                    |             |  |  |

|                                     | Supply current in Run mode from |                      | 16 MHz            | 14.9                   | 7.2                     | mA          |  |  |

| I <sub>DD</sub>                     | V <sub>DD</sub> supply          |                      | 8 MHz             | 7.7                    | 3.9                     | IIIA        |  |  |

|                                     | 100 2044.9                      |                      | 4 MHz             | 4.5                    | 2.5                     | -<br>-<br>- |  |  |

|                                     |                                 | Running from HSE     | 2 MHz             | 2.8                    | 1.7                     |             |  |  |

|                                     |                                 |                      | 1 MHz             | 1.9                    | 1.3                     |             |  |  |

|                                     |                                 |                      | 500 kHz           | 1.4                    | 1.1                     |             |  |  |

|                                     |                                 | crystal clock 8 MHz, | 125 kHz           | 1.1 0.9                | 0.9                     |             |  |  |

|                                     |                                 | code executing from  | 72 MHz            | 240.3                  | 239.5                   |             |  |  |

|                                     |                                 | Flash                | 64 MHz            | 210.9                  | 210.3                   | μΑ          |  |  |

|                                     |                                 |                      | 48 MHz            | 155.8                  | 155.6                   |             |  |  |

|                                     |                                 |                      | 32 MHz            | 105.7                  | 105.6                   |             |  |  |

|                                     |                                 |                      | 24 MHz            | 82.1                   | 82.0                    |             |  |  |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Run mode from |                      | 16 MHz            | 58.8                   | 58.8                    |             |  |  |

| IDDA` / ` /                         | V <sub>DDA</sub> supply         |                      | 8 MHz             | 2.4                    | 2.4                     |             |  |  |

|                                     | DDA SAFE.)                      |                      | 4 MHz             | 2.4                    | 2.4                     |             |  |  |

|                                     |                                 |                      | 2 MHz             | 2.4                    | 2.4                     |             |  |  |

|                                     |                                 |                      | 1 MHz             | 2.4                    | 2.4                     |             |  |  |

|                                     |                                 |                      | 500 kHz           | 2.4                    | 2.4                     |             |  |  |

|                                     |                                 |                      | 125 kHz           | 2.4                    | 2.4                     |             |  |  |

V<sub>DDA</sub> monitoring is ON.

When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

Table 36. Typical current consumption in Sleep mode, code running from Flash or RAM

|                                     |                                   |                                       |                   | Т                      | ур                      |                  |  |  |

|-------------------------------------|-----------------------------------|---------------------------------------|-------------------|------------------------|-------------------------|------------------|--|--|

| Symbol                              | Parameter                         | Conditions                            | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit             |  |  |

|                                     |                                   |                                       | 72 MHz            | 44.1                   | 7.0                     |                  |  |  |

|                                     |                                   |                                       | 64 MHz            | 39.7                   | 6.3                     |                  |  |  |

|                                     |                                   |                                       | 48 MHz            | 30.3                   | 4.9                     |                  |  |  |

|                                     |                                   |                                       | 32 MHz            | 20.5                   | 3.5                     |                  |  |  |

|                                     |                                   |                                       | 24 MHz            | 15.4                   | 2.8                     |                  |  |  |

|                                     | Supply current in Sleep mode from |                                       | 16 MHz            | 10.6                   | 2.0                     | ] <sub>m</sub> ^ |  |  |

| $I_{DD}$                            | V <sub>DD</sub> supply            |                                       | 8 MHz             | 5.4                    | 1.1                     | mA               |  |  |

|                                     |                                   |                                       | 4 MHz             | 3.2                    | 1.0                     | -<br>-<br>-      |  |  |

|                                     |                                   | Running from HSE crystal clock 8 MHz, | 2 MHz             | 2.1                    | 0.9                     |                  |  |  |

|                                     |                                   |                                       | 1 MHz             | 1.5                    | 0.8                     |                  |  |  |

|                                     |                                   |                                       | 500 kHz           | 1.2                    | 0.8                     |                  |  |  |

|                                     |                                   |                                       |                   | 125 kHz                | 1.0                     | 0.8              |  |  |

|                                     |                                   | code executing from                   | 72 MHz            | 239.7                  | 238.5                   |                  |  |  |

|                                     |                                   | Flash or RAM                          | 64 MHz            | 210.5                  | 209.6                   |                  |  |  |

|                                     |                                   |                                       | 48 MHz            | 155.0                  | 155.6                   |                  |  |  |

|                                     |                                   |                                       | 32 MHz            | 105.3                  | 105.2                   |                  |  |  |

|                                     |                                   |                                       | 24 MHz            | 81.9                   | 81.8                    |                  |  |  |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Sleep mode from |                                       | 16 MHz            | 58.7                   | 58.6                    | Ī                |  |  |

| IDDA` ´ ` ´                         | V <sub>DDA</sub> supply           |                                       | 8 MHz             | 2.4                    | 2.4                     | μA               |  |  |

|                                     |                                   |                                       | 4 MHz             | 2.4                    | 2.4                     |                  |  |  |

|                                     |                                   |                                       | 2 MHz             | 2.4                    | 2.4                     |                  |  |  |

|                                     |                                   |                                       | 1 MHz             | 2.4                    | 2.4                     |                  |  |  |

|                                     |                                   |                                       | 500 kHz           | 2.4                    | 2.4                     |                  |  |  |

|                                     |                                   |                                       | 125 kHz           | 2.4                    | 2.4                     |                  |  |  |

<sup>1.</sup>  $V_{DDA}$  monitoring is ON.

<sup>2.</sup> When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 43*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 43. LSE oscillator | characteristics | $(f_{LSF} = 32.768 \text{ kHz})$ |

|--------------------------|-----------------|----------------------------------|

|--------------------------|-----------------|----------------------------------|

| Symbol                   | Parameter               | Conditions <sup>(1)</sup>                     | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|--------------------------|-------------------------|-----------------------------------------------|--------------------|-----|--------------------|------|

|                          |                         | LSEDRV[1:0]=00<br>lower driving capability    | -                  | 0.5 | 0.9                |      |

| ,                        | LSE current consumption | LSEDRV[1:0]=10 medium low driving capability  | -                  | -   | 1                  | ^    |

| I <sub>DD</sub>          | LSE current consumption | LSEDRV[1:0]=01 medium high driving capability | -                  | -   | 1.3                | μA   |

|                          |                         | LSEDRV[1:0]=11 higher driving capability      | -                  | -   | 1.6                |      |

|                          |                         | LSEDRV[1:0]=00 lower driving capability       | 5                  | -   | -                  |      |

| <u> </u>                 | Oscillator              | LSEDRV[1:0]=10 medium low driving capability  | 8                  | -   | -                  | μΑ/V |

| 9 <sub>m</sub>           | transconductance        | LSEDRV[1:0]=01 medium high driving capability | 15                 | -   | -                  | μΑνν |

|                          |                         | LSEDRV[1:0]=11 higher driving capability      | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> (3) | Startup time            | V <sub>DD</sub> is stabilized                 | -                  | 2   | -                  | s    |

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

Table 52. Electrical sensitivities

| Symbol | Parameter             | Conditions                                     | Class      |

|--------|-----------------------|------------------------------------------------|------------|

| LU     | Static latch-up class | T <sub>A</sub> = +105 °C conforming to JESD78A | II level A |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \,\mu\text{A}/+0 \,\mu\text{A}$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 53.

#### 6.3.17 Communications interfaces

#### I<sup>2</sup>C interface characteristics

The I<sup>2</sup>C interface meets the timings requirements of the I<sup>2</sup>C-bus specification and user manual rev.03 for:

- Standard-mode (Sm): with a bit rate up to 100 Kbits/s

- Fast-mode (Fm): with a bit rate up to 400 Kbits/s

- Fast-mode Plus (Fm+): with a bit rate up to 1Mbits/s

The I<sup>2</sup>C timings requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics.

All I<sup>2</sup>C I/Os embed an analog filter. refer to the *Table 62: I2C analog filter characteristics*.

Table 61. I2C timings specification (see I2C specification, rev.03, June 2007)<sup>(1)</sup>

| Cumbal              | Downwater                                                                                 | Standa | rd mode             | Fast m | ode                | Fast Mo | de Plus             | I I m i 4 |

|---------------------|-------------------------------------------------------------------------------------------|--------|---------------------|--------|--------------------|---------|---------------------|-----------|

| Symbol              | Parameter                                                                                 | Min    | Max                 | Min    | Max                | Min     | Max                 | Unit      |

| f <sub>SCL</sub>    | SCL clock frequency                                                                       | 0      | 100                 | 0      | 400                | 0       | 1000                | KHz       |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                               | 4.7    | -                   | 1.3    | -                  | 0.5     | -                   | μs        |

| t <sub>HIGH</sub>   | High Period of the SCL clock                                                              | 4      |                     | 0.6    |                    | 0.26    | -                   | μs        |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                     | -      | 1000                | -      | 300                | -       | 120                 | ns        |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                     | -      | 300                 | -      | 300                | -       | 120                 | ns        |

| t <sub>HD;DAT</sub> | Data hold time                                                                            | 0      | -                   | 0      | -                  | 0       | -                   | μs        |

| t <sub>VD;DAT</sub> | Data valid time                                                                           | -      | 3.45 <sup>(2)</sup> | -      | 0.9 <sup>(2)</sup> | -       | 0.45 <sup>(2)</sup> | μs        |

| t <sub>VD;ACK</sub> | Data valid acknowledge time                                                               | -      | 3.45 <sup>(2)</sup> | -      | 0.9 <sup>(2)</sup> | -       | 0.45 <sup>(2)</sup> | μs        |

| t <sub>SU;DAT</sub> | Data setup time                                                                           | 250    | -                   | 100    | -                  | 50      | -                   | ns        |

| t <sub>HD:STA</sub> | Hold time (repeated) START condition                                                      | 4.0    | -                   | 0.6    | -                  | 0.26    | -                   | μs        |

| t <sub>SU:STA</sub> | Set-up time for a repeated START condition                                                | 4.7    | -                   | 0.6    | -                  | 0.26    |                     | μs        |

| t <sub>SU:STO</sub> | Set-up time for STOP condition                                                            | 4.0    | -                   | 0.6    | -                  | 0.26    | -                   | μs        |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                          | 4.7    | -                   | 1.3    | -                  | 0.5     | -                   | μs        |

| C <sub>b</sub>      | Capacitive load for each bus line                                                         | -      | 400                 | -      | 400                | -       | 550                 | pF        |

| t <sub>SP</sub>     | Pulse width of spikes that are suppressed by the analog filter for Standard and Fast mode | 0      | 50 <sup>(3)</sup>   | 0      | 50 <sup>(3)</sup>  | -       | -                   | ns        |

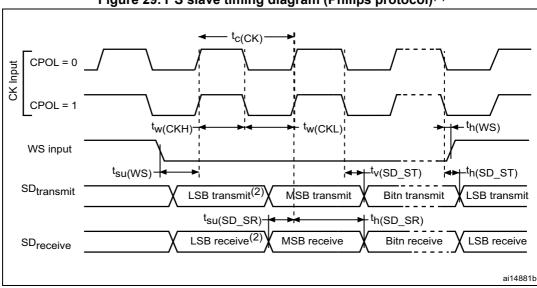

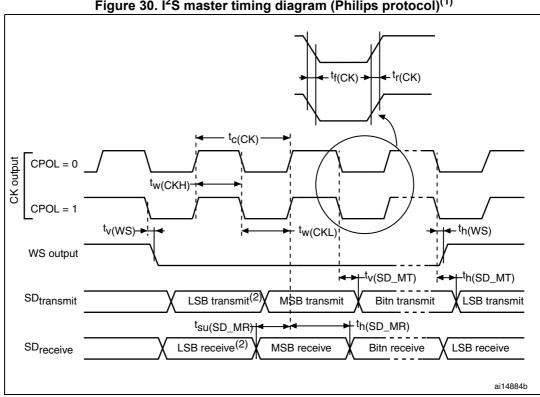

Figure 29. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- Measurement points are done at  $0.5V_{DD}$  and with external  $C_L$ =30 pF.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first

Figure 30. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  and with external  $C_L$ =30 pF.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first

Table 71. ADC accuracy, 100-pin packages<sup>(1)(2)(3)</sup>

| Symbol | Parameter           | С                                                                                   | onditions                 |                     | Min <sup>(4)</sup>  | Max <sup>(4)</sup>                                           | Unit |

|--------|---------------------|-------------------------------------------------------------------------------------|---------------------------|---------------------|---------------------|--------------------------------------------------------------|------|

|        |                     |                                                                                     | Single                    | Fast channel 5.1 Ms | -                   | ±6.5                                                         |      |

| ГТ     | Total               |                                                                                     | Ended                     | Slow channel 4.8 Ms | -                   | ±6.5                                                         |      |

| ET     | unadjusted<br>error |                                                                                     | Differential              | Fast channel 5.1 Ms | -                   | <u>±4</u>                                                    |      |

|        |                     |                                                                                     | Dillerential              | Slow channel 4.8 Ms | -                   | <u>±4</u>                                                    |      |

|        |                     |                                                                                     | Single                    | Fast channel 5.1 Ms | -                   | ±3                                                           |      |

| EO     | Offset error        |                                                                                     | Ended                     | Slow channel 4.8 Ms | -                   | ±3                                                           |      |

| EO     | Oliset ellor        | set error                                                                           | Differential              | Fast channel 5.1 Ms | -                   | <u>+2</u>                                                    |      |

|        |                     |                                                                                     | Dillerential              | Slow channel 4.8 Ms | -                   | <u>+2</u>                                                    |      |

|        |                     |                                                                                     | Single                    | Fast channel 5.1 Ms | -                   | ±6                                                           |      |

| EG     | Gain error          | sain error                                                                          | Ended                     | Slow channel 4.8 Ms | -                   | ±6                                                           | LSB  |

| EG     |                     | Gain Choi                                                                           | ADC clock freq. ≤ 72 MHz, | Differential        | Fast channel 5.1 Ms | -                                                            | ±3   |

|        |                     | Sampling freq. ≤ 5 Msps                                                             | . Dinordina               | Slow channel 4.8 Ms | -                   | ±6.5<br>±6.5<br>±4<br>±4<br>±3<br>±3<br>±2<br>±2<br>±6<br>±6 |      |

|        |                     | $2 \text{ V} \leq \text{V}_{\text{DDA}}, \text{V}_{\text{REF+}} \leq 3.6 \text{ V}$ | Single                    | Fast channel 5.1 Ms | -                   | ±1.5                                                         |      |

| ED     | Dilleteritial       | 100-pin package                                                                     | Ended                     | Slow channel 4.8 Ms | -                   | ±1.5                                                         |      |

|        | linearity<br>error  | - I                                                                                 | Differential              | Fast channel 5.1 Ms | -                   | ±1.5                                                         |      |

|        |                     |                                                                                     | Dillerential              | Slow channel 4.8 Ms | -                   | ±1.5                                                         |      |

|        |                     |                                                                                     | Single                    | Fast channel 5.1 Ms | ı                   | <u>+2</u>                                                    |      |

| EL     | Integral linearity  |                                                                                     | Ended                     | Slow channel 4.8 Ms | -                   | ±3                                                           |      |

|        | error               |                                                                                     | Differential              | Fast channel 5.1 Ms | -                   | <u>±2</u>                                                    |      |

|        |                     |                                                                                     | Dillerential              | Slow channel 4.8 Ms | ı                   | <u>+2</u>                                                    |      |

|        |                     |                                                                                     | Single                    | Fast channel 5.1 Ms | 10.4                | ı                                                            |      |

| ENOB   | Effective number of |                                                                                     | Ended                     | Slow channel 4.8 Ms | 10.2                | -                                                            | bits |

| (5)    | bits                |                                                                                     | Differential              | Fast channel 5.1 Ms | 10.8                | -                                                            | טונס |

|        |                     |                                                                                     | חווכובווומו               | Slow channel 4.8 Ms | 10.8                | _                                                            |      |

Table 72. ADC accuracy - limited test conditions, 64-pin packages<sup>(1)(2)</sup> (continued)

| Symbol             | Parameter                       | C                                                  | Min<br>(3)                                           | Тур                 | Max<br>(3) | Unit |     |    |

|--------------------|---------------------------------|----------------------------------------------------|------------------------------------------------------|---------------------|------------|------|-----|----|

|                    | Signal-to-<br>noise ratio       |                                                    | Single ended Fast channel 5.1 Ms Slow channel 4.8 Ms | 66                  | 67         | -    |     |    |

| SNR <sup>(4)</sup> |                                 | ADC clock freq. ≤ 72 MHz Sampling freq ≤ 5 Msps    |                                                      | Slow channel 4.8 Ms | 66         | 67   | -   | -  |

|                    |                                 |                                                    | Differential                                         | Fast channel 5.1 Ms | 69         | 70   | -   |    |

|                    |                                 |                                                    |                                                      | Slow channel 4.8 Ms | 69         | 70   | -   | dB |

|                    |                                 | V <sub>DDA</sub> = 3.3 V<br>25°C<br>64-pin package | Cinalo ondod                                         | Fast channel 5.1 Ms | -          | -80  | -80 | uБ |

| THD <sup>(4)</sup> | Total<br>harmonic<br>distortion |                                                    | Single ended                                         | Slow channel 4.8 Ms | -          | -78  | -77 |    |

|                    |                                 |                                                    | Differential                                         | Fast channel 5.1 Ms | -          | -83  | -82 |    |

|                    |                                 |                                                    |                                                      | Slow channel 4.8 Ms | -          | -81  | -80 |    |

<sup>1.</sup> ADC DC accuracy values are measured after internal calibration.

<sup>2.</sup> ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

<sup>3.</sup> Guaranteed by characterization results.

<sup>4.</sup> Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

## 6.3.19 DAC electrical specifications

**Table 75. DAC characteristics**

| Symbol                           | Parameter                                                                                                                                           | Conditions                                                                                                                                                |                               | Min   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|-----|-------------------------|------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                                                               | -                                                                                                                                                         |                               | 2.4 - |     | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load                                                                                                                                      |                                                                                                                                                           | Connected to V <sub>SSA</sub> | 5     | -   | -                       | kΩ   |

|                                  | ixesistive load                                                                                                                                     | buffer ON                                                                                                                                                 | Connected to V <sub>DDA</sub> | 25    | -   | -                       | K22  |

| R <sub>O</sub> <sup>(1)</sup>    | Output impedance                                                                                                                                    | DAC output                                                                                                                                                | buffer OFF                    | -     | -   | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                                                                     | DAC output                                                                                                                                                | buffer ON                     | -     | -   | 50                      | pF   |

| V <sub>DAC_OUT</sub> (1)         | Voltage on DAC_OUT output                                                                                                                           | Corresponds to 12-bit input code (0x0E0) to (0xF1C) at V <sub>DDA</sub> = 3.6 V and (0x155) and (0xEAB) at V <sub>DDA</sub> = 2.4 V DAC output buffer ON. |                               | 0.2   | 1   | V <sub>DDA</sub> – 0.2  | V    |

|                                  |                                                                                                                                                     | DAC output                                                                                                                                                | buffer OFF                    | -     | 0.5 | V <sub>DDA</sub> - 1LSB | mV   |

| I <sub>DDA</sub> <sup>(3)</sup>  | DAC DC current consumption in quiescent                                                                                                             | With no load, middle code (0x800) on the input.                                                                                                           |                               | -     | ı   | 380                     | μΑ   |

| 'DDA'                            | mode (Standby mode) <sup>(2)</sup>                                                                                                                  | With no load, worst code (0xF1C) on the input.                                                                                                            |                               | -     | -   | 480                     | μΑ   |

| <b>5</b> (3)                     | Differential non linearity                                                                                                                          | Given for a 10-bit input code                                                                                                                             |                               | -     | -   | ±0.5                    | LSB  |

| DNL <sup>(3)</sup>               | Difference between two consecutive code-1LSB)                                                                                                       | Given for a 12-bit input code                                                                                                                             |                               | -     | -   | ±2                      | LSB  |

|                                  | Integral non linearity                                                                                                                              | Given for a 10-bit input code                                                                                                                             |                               | -     | -   | ±1                      | LSB  |

| INL <sup>(3)</sup>               | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 4095)                 | Given for a 12-bit input code                                                                                                                             |                               | -     | -   | ±4                      | LSB  |

|                                  |                                                                                                                                                     |                                                                                                                                                           | -                             | -     | -   | ±10                     | mV   |

| Offset <sup>(3)</sup>            | Offset error (difference between measured value at Code (0x800) and the ideal                                                                       | Given for a 10-bit input code at V <sub>DDA</sub> = 3.6 V                                                                                                 |                               | -     | -   | ±3                      | LSB  |

|                                  | value = V <sub>DDA</sub> /2)                                                                                                                        | Given for a 12-bit input code at V <sub>DDA</sub> = 3.6 V                                                                                                 |                               | -     | -   | ±12                     | LSB  |

| Gain error <sup>(3)</sup>        | Gain error                                                                                                                                          | Given for a 12-bit input code                                                                                                                             |                               | -     | -   | ±0.5                    | %    |

| t <sub>SETTLING</sub> (3)        | Settling time (full scale: for a 12-bit input code transition between the lowest and the highest input codes when DAC_OUT reaches final value ±1LSB |                                                                                                                                                           |                               | -     | 3   | 4                       | μs   |

| Update rate <sup>(3)</sup>       | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                           | C <sub>LOAD</sub> ≤50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                                                                     |                               | -     | -   | 1                       | MS/s |

## 6.3.20 Comparator characteristics

Table 76. Comparator characteristics<sup>(1)</sup>

| Symbol                   | Parameter                                                   | Conditions                                                        |                             |     | Тур | Max              | Unit |

|--------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|-----|-----|------------------|------|

| $V_{DDA}$                | Analog supply voltage                                       | -                                                                 |                             |     | -   | 3.6              |      |

| V <sub>IN</sub>          | Comparator input voltage range                              | -                                                                 |                             |     | -   | V <sub>DDA</sub> | V    |

| V <sub>BG</sub>          | Scaler input voltage                                        | -                                                                 |                             | -   | 1.2 | -                |      |

| V <sub>SC</sub>          | Scaler offset voltage                                       | -                                                                 |                             | -   | ±5  | ±10              | mV   |

| t <sub>S_SC</sub>        | V <sub>REFINT</sub> scaler startup<br>time from power down  | First V <sub>REFINT</sub> scaler activation after device power on |                             | ı   | -   | 1 <sup>(2)</sup> | s    |

| _                        | time nom power down                                         | Next activ                                                        | Next activations            |     |     | 0.2              | ms   |

| t <sub>START</sub>       | Comparator startup time                                     | Startup time to reach propagation delay specification             |                             |     | -   | 60               | μs   |

|                          |                                                             | Ultra-low-power mode                                              |                             | -   | 2   | 4.5              |      |

|                          | Propagation delay for 200 mV step with 100 mV overdrive     | Low-power mode                                                    |                             |     | 0.7 | 1.5              | μs   |

|                          |                                                             | Medium power mode                                                 | -                           | 0.3 | 0.6 | -                |      |

|                          |                                                             | High speed mode                                                   | V <sub>DDA</sub> ≥ 2.7 V    | -   | 50  | 100              | ns   |

|                          |                                                             |                                                                   | V <sub>DDA</sub> < 2.7 V    | -   | 100 | 240              | 1115 |

| t <sub>D</sub>           |                                                             | Ultra-low-power mode                                              |                             | -   | 2   | 7                | μs   |

|                          | Propagation delay for full range step with 100 mV overdrive | Low-power mode                                                    | -                           | 0.7 | 2.1 |                  |      |

|                          |                                                             | Medium power mode                                                 |                             |     | 0.3 | 1.2              |      |

|                          |                                                             | Lligh anged mode                                                  | $V_{DDA} \ge 2.7 \text{ V}$ | -   | 90  | 180              | ns - |

|                          |                                                             | High speed mode                                                   | V <sub>DDA</sub> < 2.7 V    | -   | 110 | 300              | 1115 |

| V <sub>offset</sub>      | Comparator offset error                                     | -                                                                 | -                           | ±4  | ±10 | mV               |      |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                        | -                                                                 | -                           | 18  | -   | μV/°<br>C        |      |

|                          |                                                             | Ultra-low-power mode                                              |                             | -   | 1.2 | 1.5              | μΑ   |

|                          | COMP current                                                | Low-power mode                                                    |                             | -   | 3   | 5                |      |

| I <sub>DD(COMP)</sub>    | consumption                                                 | Medium power mode                                                 | -                           | 10  | 15  |                  |      |

|                          |                                                             | High speed mode                                                   | -                           | 75  | 100 |                  |      |

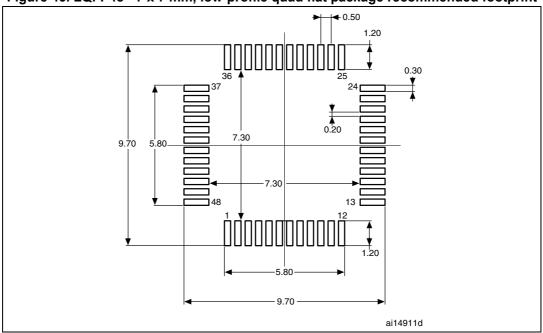

Table 83. LQFP48 – 7 x 7 mm, low-profile quad flat package mechanical data (continued)

|        |             |      | •    | ,                     |        |        |  |

|--------|-------------|------|------|-----------------------|--------|--------|--|