Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| betans                     |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 52                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 22x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303rbt7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | uction                                                                                          |

|---|-------|-------------------------------------------------------------------------------------------------|

| 2 | Desc  | ption                                                                                           |

| 3 | Func  | onal overview                                                                                   |

|   | 3.1   | ARM <sup>®</sup> Cortex <sup>®</sup> -M4 core with FPU with embedded Flash and SRAM $\ldots$ 13 |

|   | 3.2   | Memory protection unit (MPU) 13                                                                 |

|   | 3.3   | Embedded Flash memory 13                                                                        |

|   | 3.4   | Embedded SRAM                                                                                   |

|   | 3.5   | Boot modes                                                                                      |

|   | 3.6   | Cyclic redundancy check (CRC) 14                                                                |

|   | 3.7   | Power management                                                                                |

|   |       | 3.7.1 Power supply schemes                                                                      |

|   |       | 3.7.2   Power supply supervision   15                                                           |

|   |       | 3.7.3 Voltage regulator                                                                         |

|   |       | 3.7.4         Low-power modes         16                                                        |

|   | 3.8   | Interconnect matrix                                                                             |

|   | 3.9   | Clocks and startup                                                                              |

|   | 3.10  | General-purpose input/outputs (GPIOs)                                                           |

|   | 3.11  | Direct memory access (DMA) 19                                                                   |

|   | 3.12  | Interrupts and events                                                                           |

|   |       | 3.12.1 Nested vectored interrupt controller (NVIC)                                              |

|   | 3.13  | Fast analog-to-digital converter (ADC)                                                          |

|   |       | 3.13.1 Temperature sensor                                                                       |

|   |       | 3.13.2 Internal voltage reference (V <sub>REFINT</sub> )                                        |

|   |       | 3.13.3 V <sub>BAT</sub> battery voltage monitoring                                              |

|   |       | 3.13.4 OPAMP reference voltage (VREFOPAMP)                                                      |

|   | 3.14  | Digital-to-analog converter (DAC) 21                                                            |

|   | 3.15  | Operational amplifier (OPAMP) 21                                                                |

|   | 3.16  | Fast comparators (COMP)    22                                                                   |

|   | 3.17  | Timers and watchdogs 22                                                                         |

|   |       | 3.17.1 Advanced timers (TIM1, TIM8)                                                             |

DocID023353 Rev 13

### 3.7.4 Low-power modes

The STM32F303xB/STM32F303xC supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the USB wakeup, the RTC alarm, COMPx, I2Cx or U(S)ARTx.

Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and register contents are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin or an RTC alarm occurs.

*Note:* The RTC, the IWDG and the corresponding clock sources are not stopped by entering Stop or Standby mode.

## 3.8 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

| Interconnect source | Interconnect<br>destination                            | Interconnect action                |

|---------------------|--------------------------------------------------------|------------------------------------|

|                     | TIMx                                                   | Timers synchronization or chaining |

| TIMx                | ADCx<br>DAC1                                           | Conversion triggers                |

|                     | DMA                                                    | Memory to memory transfer trigger  |

|                     | Compx                                                  | Comparator output blanking         |

| COMPx               | COMPx TIMx Timer input: OCREF_CLR input, input capture |                                    |

| ADCx                | TIMx                                                   | Timer triggered by analog watchdog |

Table 4. STM32F303xB/STM32F303xC peripheral interconnect matrix

# 3.22 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I2S)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) supporting four different audio standards can operate as master or slave at half-duplex and full duplex communication modes. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by 8-bit programmable linear prescaler. When operating in master mode it can output a clock for an external audio component at 256 times the sampling frequency.

Refer to *Table 9* for the features available in SPI1, SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 |

|-----------------------------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    |

| I2S mode                    | -    | Х    | Х    |

| TI mode                     | Х    | Х    | Х    |

Table 9. STM32F303xB/STM32F303xC SPI/I2S implementation

1. X = supported.

## 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

## 3.24 Universal serial bus (USB)

The STM32F303xB/STM32F303xC devices embed an USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator). The USB has a dedicated 512-bytes SRAM memory for data transmission and reception.

|          | Pin nu  | umber  |        |                                          |          |               |       | Pin fun                                                                                                                              | ,                    |

|----------|---------|--------|--------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                  | Additional functions |

| B2       | 77      | 50     | 38     | PA15                                     | I/O      | FTf           | _     | I2C1_SCL, SPI1_NSS,<br>SPI3_NSS, I2S3_WS, JTDI,<br>USART2_RX, TIM1_BKIN,<br>TIM2_CH1_ETR, TIM8_CH1,<br>EVENTOUT                      | -                    |

| E4       | 78      | 51     | -      | PC10                                     | I/O      | FT            | (1)   | SPI3_SCK, I2S3_CK,<br>USART3_TX, UART4_TX,<br>TIM8_CH1N, EVENTOUT                                                                    | -                    |

| D3       | 79      | 52     | -      | PC11                                     | I/O      | FT            | (1)   | SPI3_MISO, I2S3ext_SD,<br>USART3_RX, UART4_RX,<br>TIM8_CH2N, EVENTOUT                                                                | -                    |

| A3       | 80      | 53     | -      | PC12                                     | I/O      | FT            | (1)   | SPI3_MOSI, I2S3_SD,<br>USART3_CK, UART5_TX,<br>TIM8_CH3N, EVENTOUT                                                                   | -                    |

| B3       | 81      | -      | -      | PD0                                      | I/O      | FT            | (1)   | CAN_RX, EVENTOUT                                                                                                                     | -                    |

| C3       | 82      | -      | -      | PD1                                      | I/O      | FT            | (1)   | CAN_TX, TIM8_CH4,<br>TIM8_BKIN2,EVENTOUT                                                                                             | -                    |

| A4       | 83      | 54     | -      | PD2                                      | I/O      | FT            | (1)   | UART5_RX, TIM3_ETR,<br>TIM8_BKIN, EVENTOUT                                                                                           | -                    |

| B4       | 84      | -      | -      | PD3                                      | I/O      | FT            | (1)   | USART2_CTS,<br>TIM2_CH1_ETR,<br>EVENTOUT                                                                                             | -                    |

| C4       | 85      | -      | -      | PD4                                      | I/O      | FT            | (1)   | TIM2_CH2, EVENTOUT                                                                                                                   | -                    |

| -        | 86      | -      | -      | PD5                                      | I/O      | FT            | (1)   | USART2_TX, EVENTOUT                                                                                                                  | -                    |

| -        | 87      | -      | -      | PD6                                      | I/O      | FT            | (1)   | USART2_RX, TIM2_CH4,<br>EVENTOUT                                                                                                     | -                    |

| D4       | 88      | -      | -      | PD7                                      | I/O      | FT            | (1)   | USART2_CK, TIM2_CH3,<br>EVENTOUT                                                                                                     | -                    |

| A5       | 89      | 55     | 39     | PB3                                      | I/O      | FT            | -     | SPI3_SCK, I2S3_CK,<br>SPI1_SCK, USART2_TX,<br>TIM2_CH2, TIM3_ETR,<br>TIM4_ETR, TIM8_CH1N,<br>TSC_G5_IO1, JTDO-<br>TRACESWO, EVENTOUT | -                    |

Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

48/148

|                       | Table 16. Alternate functions for port C |          |            |           |           |                       |           |     |     |  |

|-----------------------|------------------------------------------|----------|------------|-----------|-----------|-----------------------|-----------|-----|-----|--|

| Port &<br>Pin<br>Name | AF1 AF2 AF3                              |          | AF2 AF3    |           | 2 AF3 AF4 |                       | AF5       | AF6 | AF7 |  |

| PC0                   | EVENTOUT                                 | -        | -          | -         | -         | -                     | -         |     |     |  |

| PC1                   | EVENTOUT                                 | -        | -          | -         | -         | -                     | -         |     |     |  |

| PC2                   | EVENTOUT                                 | -        | COMP7_OUT  | -         | -         | -                     | -         |     |     |  |

| PC3                   | EVENTOUT                                 | -        | -          | -         | -         | TIM1_BKIN2            | -         |     |     |  |

| PC4                   | EVENTOUT                                 | -        | -          | -         | -         | -                     | USART1_TX |     |     |  |

| PC5                   | EVENTOUT                                 | -        | TSC_G3_IO1 | -         | -         | -                     | USART1_RX |     |     |  |

| PC6                   | EVENTOUT                                 | TIM3_CH1 | -          | TIM8_CH1  | -         | I2S2_MCK              | COMP6_OUT |     |     |  |

| PC7                   | EVENTOUT                                 | TIM3_CH2 | -          | TIM8_CH2  | -         | I2S3_MCK              | COMP5_OUT |     |     |  |

| PC8                   | EVENTOUT                                 | TIM3_CH3 | -          | TIM8_CH3  | -         | -                     | COMP3_OUT |     |     |  |

| PC9                   | EVENTOUT                                 | TIM3_CH4 | -          | TIM8_CH4  | I2S_CKIN  | TIM8_BKIN2            | -         |     |     |  |

| PC10                  | EVENTOUT                                 | -        | -          | TIM8_CH1N | UART4_TX  | SPI3_SCK, I2S3_CK     | USART3_TX |     |     |  |

| PC11                  | EVENTOUT                                 | -        | -          | TIM8_CH2N | UART4_RX  | SPI3_MISO, I2S3ext_SD | USART3_RX |     |     |  |

| PC12                  | EVENTOUT                                 | -        | -          | TIM8_CH3N | UART5_TX  | SPI3_MOSI, I2S3_SD    | USART3_CK |     |     |  |

| PC13                  | -                                        | -        | -          | TIM1_CH1N | -         | -                     | -         |     |     |  |

| PC14                  | -                                        | -        | -          | -         | -         | -                     | -         |     |     |  |

| PC15                  | -                                        | -        | -          | -         | -         | -                     | -         |     |     |  |

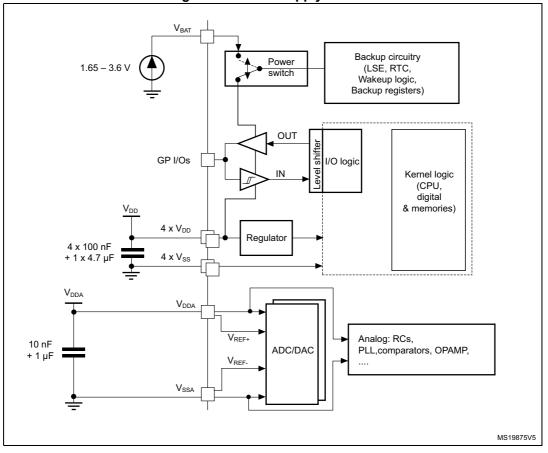

## 6.1.6 Power supply scheme

Figure 11. Power supply scheme

1. Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

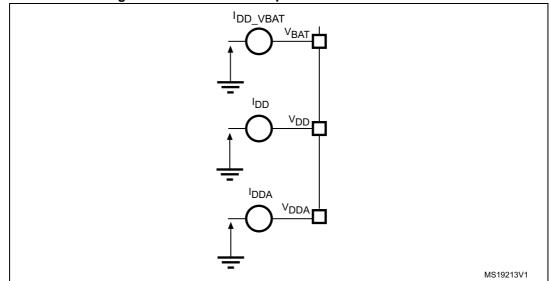

#### 6.1.7 **Current consumption measurement**

#### Figure 12. Current consumption measurement scheme

#### Absolute maximum ratings 6.2

Stresses above the absolute maximum ratings listed in Table 21: Voltage characteristics, Table 22: Current characteristics, and Table 23: Thermal characteristics may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                             | Ratings                                                                                | Min                                    | Мах                   | Unit |

|----------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                   | External main supply voltage (including $V_{DDA,}$ $V_{BAT}$ and $V_{DD})$             | -0.3                                   | 4.0                   |      |

| V <sub>DD</sub> -V <sub>DDA</sub>                  | Allowed voltage difference for $V_{DD} > V_{DDA}$                                      | -                                      | 0.4                   |      |

| V <sub>REF+</sub> -V <sub>DDA</sub> <sup>(2)</sup> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                                    | -                                      | 0.4                   |      |

|                                                    | Input voltage on FT and FTf pins                                                       | V <sub>SS</sub> –0.3                   | V <sub>DD</sub> + 4.0 | V    |

| V <sub>IN</sub> <sup>(3)</sup>                     | Input voltage on TTa pins                                                              | V <sub>SS</sub> –0.3                   | 4.0                   |      |

| VIN Y                                              | Input voltage on any other pin                                                         | V <sub>SS</sub> -0.3                   | 4.0                   |      |

|                                                    | Input voltage on Boot0 pin                                                             | 0                                      | 9                     |      |

| $ \Delta V_{DDx} $                                 | Variations between different V <sub>DD</sub> power pins                                | -                                      | 50                    | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub>                  | SX – V <sub>SS</sub>   Variations between all the different ground pins <sup>(4)</sup> |                                        | 50                    | 111V |

| V <sub>ESD(HBM)</sub>                              | Electrostatic discharge voltage (human body model)                                     | see Section 6.3.<br>sensitivity charac |                       | -    |

| Table 21 | . Voltage | characteristics <sup>(1)</sup> |

|----------|-----------|--------------------------------|

|----------|-----------|--------------------------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

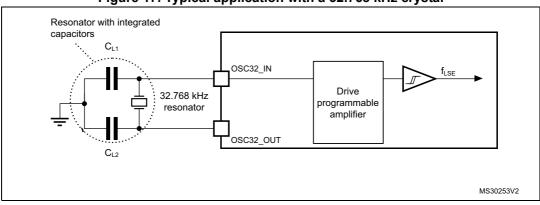

Figure 17. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.8 Internal clock source characteristics

The parameters given in *Table 44* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24*.

#### High-speed internal (HSI) RC oscillator

| Symbol                | Parameter                           | Conditions                       | Min                 | Тур | Мах                | Unit |  |  |

|-----------------------|-------------------------------------|----------------------------------|---------------------|-----|--------------------|------|--|--|

| f <sub>HSI</sub>      | Frequency                           | -                                | -                   | 8   | -                  | MHz  |  |  |

| TRIM                  | HSI user trimming step              | -                                | -                   | -   | 1 <sup>(2)</sup>   | %    |  |  |

| DuCy <sub>(HSI)</sub> | Duty cycle                          | -                                | 45 <sup>(2)</sup>   | -   | 55 <sup>(2)</sup>  | %    |  |  |

| ACC <sub>HSI</sub>    | Accuracy of the HSI oscillator      | T <sub>A</sub> = -40 to<br>105°C | -2.8 <sup>(3)</sup> | -   | 3.8 <sup>(3)</sup> |      |  |  |

|                       |                                     | T <sub>A</sub> = -10 to 85°C     | -1.9 <sup>(3)</sup> | -   | 2.3 <sup>(3)</sup> | %    |  |  |

|                       |                                     | T <sub>A</sub> = 0 to 85°C       | -1.9 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |  |  |

|                       |                                     | T <sub>A</sub> = 0 to 70°C       | -1.3 <sup>(3)</sup> | -   | 2 <sup>(3)</sup>   |      |  |  |

|                       |                                     | $T_A = 0$ to 55°C                | -1 <sup>(3)</sup>   | -   | 2 <sup>(3)</sup>   |      |  |  |

|                       |                                     | $T_{A} = 25^{\circ}C^{(4)}$      | -1                  | -   | 1                  |      |  |  |

| t <sub>su(HSI)</sub>  | HSI oscillator startup time         | -                                | 1 <sup>(2)</sup>    | -   | 2 <sup>(2)</sup>   | μs   |  |  |

| I <sub>DDA(HSI)</sub> | HSI oscillator power<br>consumption | -                                | -                   | 80  | 100 <sup>(2)</sup> | μA   |  |  |

Table 44. HSI oscillator characteristics<sup>(1)</sup>

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

|                  |                                                                                                                                                                                                                                                                                                                                         | Functional s       | usceptibility      |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                                                                                                                                                                                             | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0                                                                                                                                                                                                                                                                                                               | - 0                | NA                 |      |

| I <sub>INJ</sub> | Injected current on PC0, PC1, PC2, PC3, PF2, PA0, PA1, PA2, PA3, PF4, PA4, PA5, PA6, PA7, PC4, PC5, PB2 with induced leakage current on other pins from this group less than -50 $\mu$ A                                                                                                                                                | - 5                | -                  |      |

|                  | Injected current on PB0, PB1, PE7, PE8, PE9, PE10, PE11, PE12, PE13, PE14, PE15, PB12, PB13, PB14, PB15, PD8, PD9, PD10, PD11, PD12, PD13, PD14 with induced leakage current on other pins from this group less than -50 µA                                                                                                             | - 5                | -                  | mA   |

|                  | Injected current on PC0, PC1, PC2, PC3, PF2, PA0,<br>PA1, PA2, PA3, PF4, PA4, PA5, PA6, PA7, PC4, PC5,<br>PB2, PB0, PB1, PE7, PE8, PE9, PE10, PE11, PE12,<br>PE13, PE14, PE15, PB12, PB13, PB14, PB15, PD8,<br>PD9, PD10, PD11, PD12, PD13, PD14 with induced<br>leakage current on other pins from this group less than<br>400 $\mu$ A | -                  | +5                 |      |

|                  | Injected current on any other FT and FTf pins                                                                                                                                                                                                                                                                                           | - 5                | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                                                                                                                                                                                      | - 5                | +5                 |      |

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

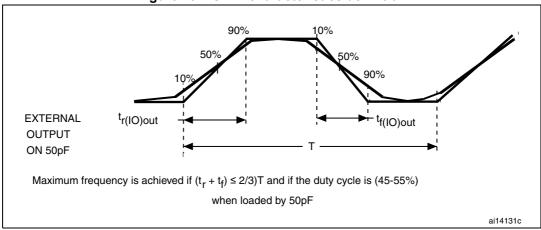

Figure 23. I/O AC characteristics definition

### 6.3.15 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 54*).

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                               | Parameter                                       | Conditions        | Min                                            | Тур | Мах                                         | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------------------------------------------------|-----|---------------------------------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -                                              | -   | 0.3V <sub>DD</sub> +<br>0.07 <sup>(1)</sup> | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 0.445V <sub>DD</sub> +<br>0.398 <sup>(1)</sup> | -   | -                                           | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage hysteresis         | -                 | -                                              | 200 | -                                           | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                             | 40  | 55                                          | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -                                              | -   | 100 <sup>(1)</sup>                          | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 500 <sup>(1)</sup>                             | -   | -                                           | ns   |

Table 57. NRST pin characteristics

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

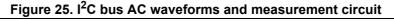

- 1. The I2C characteristics are the requirements from I2C bus specification rev03. They are guaranteed by design when I2Cx\_TIMING register is correctly programmed (Refer to the RM0316 reference manual).

- The maximum tHD;DAT could be 3.45 µs, 0.9 µs and 0.45 µs for standard mode, fast mode and fast mode plus, but must be less than the maximum of tVD;DAT or tVD;ACK by a transition time.

- 3. The minimum width of the spikes filtered by the analog filter is above  $t_{SP}(max)$ .

| Table 62. I2C analog filter characteristics <sup>(1)</sup> |                                                                   |     |     |      |  |

|------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|------|--|

| Symbol                                                     | Parameter                                                         | Min | Max | Unit |  |

| t <sub>AF</sub>                                            | Pulse width of spikes that are<br>suppressed by the analog filter | 50  | 260 | ns   |  |

1. Guaranteed by design.

<sup>1.</sup> Rs: Series protection resistors, Rp: Pull-up resistors, VDD\_I2C: I2C bus supply.

| Symbol                                    | Parameter                       | Conditions                     | Min | Тур | Мах | Unit |  |

|-------------------------------------------|---------------------------------|--------------------------------|-----|-----|-----|------|--|

| Driver characteristics                    |                                 |                                |     |     |     |      |  |

| t <sub>r</sub>                            | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |

| t <sub>f</sub>                            | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | -   | 20  | ns   |  |

| t <sub>rfm</sub>                          | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | -   | 110 | %    |  |

| V <sub>CRS</sub>                          | Output signal crossover voltage | -                              | 1.3 | -   | 2.0 | V    |  |

| Output driver<br>Impedance <sup>(3)</sup> | Z <sub>DRV</sub>                | driving high and low           | 28  | 40  | 44  | Ω    |  |

Table 67. USB: Full-speed electrical characteristics<sup>(1)</sup>

1. Guaranteed by design.

Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-), the matching impedance is already included in the embedded driver.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

## 6.3.19 DAC electrical specifications

| Symbol                              | Parameter                                                                                                                                                          | С                                                            | onditions                                                                           | Min | Тур | Max                     | Unit |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                                                                                                                                              |                                                              | -                                                                                   | 2.4 | -   | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup>    | Resistive load                                                                                                                                                     |                                                              | Connected to $V_{SSA}$                                                              | 5   | -   | -                       | kΩ   |

|                                     |                                                                                                                                                                    | buffer ON Connected to V <sub>DDA</sub>                      |                                                                                     | 25  | -   | -                       | K22  |

| $R_0^{(1)}$                         | Output impedance                                                                                                                                                   | DAC output                                                   | buffer OFF                                                                          | -   | -   | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup>    | Capacitive load                                                                                                                                                    | DAC output                                                   | buffer ON                                                                           | -   | -   | 50                      | pF   |

| V <sub>DAC_OUT</sub> <sup>(1)</sup> | Voltage on DAC_OUT<br>output                                                                                                                                       | code (0x0E)<br>V <sub>DDA</sub> = 3.6<br>and (0x155)         | s to 12-bit input<br>0) to (0xF1C) at<br>V<br>and (0xEAB) at<br>V DAC output buffer | 0.2 | -   | V <sub>DDA</sub> – 0.2  | V    |

|                                     |                                                                                                                                                                    | DAC output                                                   | buffer OFF                                                                          | -   | 0.5 | V <sub>DDA</sub> - 1LSB | mV   |

| I <sub>DDA</sub> <sup>(3)</sup>     | DAC DC current<br>consumption in quiescent                                                                                                                         | With no load<br>(0x800) on t                                 | d, middle code<br>he input.                                                         | -   | -   | 380                     | μA   |

| 'DDA'                               | mode (Standby mode) <sup>(2)</sup>                                                                                                                                 | With no load, worst code<br>(0xF1C) on the input.            |                                                                                     | -   | -   | 480                     | μA   |

| (3)                                 | Differential non linearity                                                                                                                                         | Given for a                                                  | 10-bit input code                                                                   | -   | -   | ±0.5                    | LSB  |

|                                     | Difference between two<br>consecutive code-1LSB)                                                                                                                   | Given for a 12-bit input code                                |                                                                                     | -   | -   | ±2                      | LSB  |

|                                     | Integral non linearity                                                                                                                                             | Given for a                                                  | 10-bit input code                                                                   | -   | -   | ±1                      | LSB  |

| INL <sup>(3)</sup>                  | INL <sup>(3)</sup> (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 4095)             |                                                              | 12-bit input code                                                                   | -   | -   | ±4                      | LSB  |

|                                     |                                                                                                                                                                    |                                                              | -                                                                                   | -   | -   | ±10                     | mV   |

| Offset <sup>(3)</sup>               | Offset error (difference<br>between measured value at<br>Code (0x800) and the ideal                                                                                | Given for a<br>V <sub>DDA</sub> = 3.6                        | 10-bit input code at<br>V                                                           | -   | -   | ±3                      | LSB  |

|                                     | value = $V_{DDA}/2$ )                                                                                                                                              | Given for a 12-bit input code at<br>V <sub>DDA</sub> = 3.6 V |                                                                                     | -   | -   | ±12                     | LSB  |

| Gain error <sup>(3)</sup>           | Gain error                                                                                                                                                         | Given for a                                                  | 12-bit input code                                                                   | -   | -   | ±0.5                    | %    |

|                                     | Settling time (full scale: for a<br>12-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | C <sub>LOAD</sub> ≤50 r<br>R <sub>LOAD</sub> ≥ 5             |                                                                                     | -   | 3   | 4                       | μs   |

| Update<br>rate <sup>(3)</sup>       | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | C <sub>LOAD</sub> ⊴50 p<br>R <sub>LOAD</sub> ≥ 5             |                                                                                     | -   | -   | 1                       | MS/s |

#### Table 75. DAC characteristics

#### **Electrical characteristics**

| Symbol           | Parameter             | Conditions                               |                       |    | Тур | Max | Unit |

|------------------|-----------------------|------------------------------------------|-----------------------|----|-----|-----|------|

|                  |                       | No hysteresis<br>(COMPxHYST[1:0]=00)     | -                     | -  | 0   | -   |      |

|                  |                       | Low hysteresis                           | High speed mode       | 3  |     | 13  |      |

|                  |                       | (COMPxHYST[1:0]=01)                      | All other power modes | 5  | 8   | 10  | mV   |

| V <sub>hys</sub> | Comparator hysteresis | Medium hysteresis<br>(COMPxHYST[1:0]=10) | High speed mode       | 7  |     | 26  |      |

|                  |                       |                                          | All other power modes | 9  | 15  | 19  |      |

|                  |                       | High hysteresis<br>(COMPxHYST[1:0]=11)   | High speed mode       | 18 |     | 49  |      |

|                  |                       |                                          | All other power modes | 19 | 31  | 40  |      |

| Table 76. Comparator characteristics <sup>(1)</sup> (co | ontinued) |

|---------------------------------------------------------|-----------|

|---------------------------------------------------------|-----------|

1. Data guaranteed by design.

2. For more details and conditions, see Figure 37 Maximum V\_{REFINT} scaler startup time from power down.

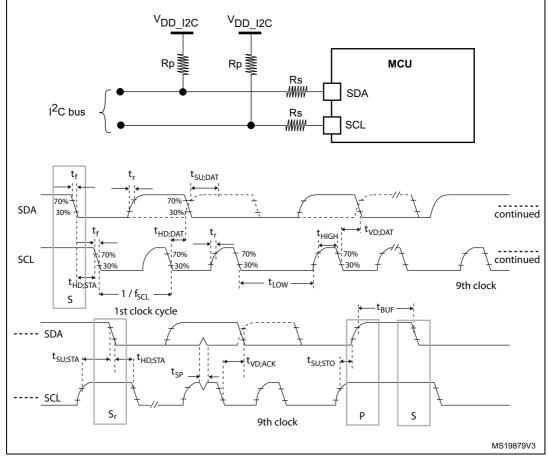

### Figure 37. Maximum $V_{REFINT}$ scaler startup time from power down

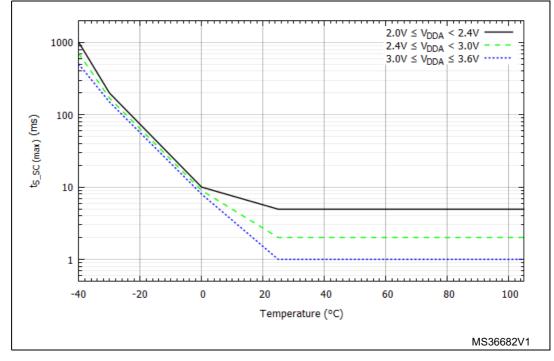

# 7.2 LQFP64 – 10 x 10 mm, low-profile quad flat package information

Figure 42. LQFP64 – 10 x 10 mm, low-profile quad flat package outline

1. Drawing is not to scale.

| Table 82. LQFP64 – 10 x 10 mm, low-profile quad flat package mechanical |

|-------------------------------------------------------------------------|

| data                                                                    |

|        | outu -      |       |      |                       |        |        |  |

|--------|-------------|-------|------|-----------------------|--------|--------|--|

| Symbol | millimeters |       |      | inches <sup>(1)</sup> |        |        |  |

| Symbol | Min         | Тур   | Max  | Min                   | Тур    | Мах    |  |

| А      | -           | -     | 1.60 | -                     | -      | 0.0630 |  |

| A1     | 0.05        | -     | 0.15 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.40  | 1.45 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.17        | 0.22  | 0.27 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.09        | -     | 0.20 | 0.0035                |        | 0.0079 |  |

| D      | -           | 12.00 | -    | -                     | 0.4724 | -      |  |

| D1     | -           | 10.00 | -    | -                     | 0.3937 | -      |  |

| D3     | -           | 7.50  | -    | -                     | 0.2953 | -      |  |

| E      | -           | 12.00 | -    | -                     | 0.4724 | -      |  |

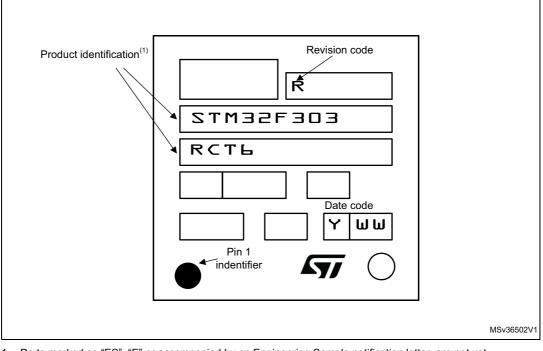

#### Device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 44. LQFP64 – 10 x 10 mm, low-profile quad flat package top view example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

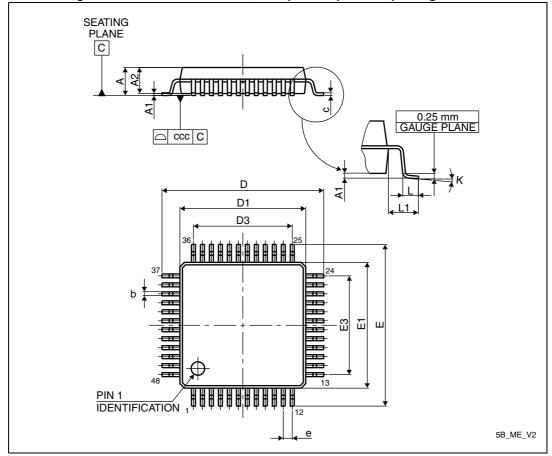

# 7.3 LQFP48 – 7 x 7 mm, low-profile quad flat package information

Figure 45. LQFP48 – 7 x 7 mm, low-profile quad flat package outline

1. Drawing is not to scale.

| Sympol | millimeters |      |      | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|------|------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур  | Мах  | Min                   | Тур    | Max    |  |

| А      | -           | -    | 1.60 | -                     | -      | 0.0630 |  |

| A1     | 0.05        | -    | 0.15 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.35        | 1.40 | 1.45 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.17        | 0.22 | 0.27 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.09        | -    | 0.20 | 0.0035                | -      | 0.0079 |  |

| D      | 8.80        | 9.00 | 9.20 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.80        | 7.00 | 7.20 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.50 | -    | -                     | 0.2165 | -      |  |

| E      | 8.80        | 9.00 | 9.20 | 0.3465                | 0.3543 | 0.3622 |  |

| Dete        |          | e 88. Document revision history (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 08-Jan-2013 | 5        | Updated V <sub>hys</sub> and I <sub>lkg</sub> in <i>Table 54: I/O static characteristics</i> .<br>Updated V <sub>IL(NRST)</sub> , V <sub>IH(NRST)</sub> , and V <sub>NF(NRST)</sub> in <i>Table 57: NRST pin characteristics</i> .<br>Updated <i>Table 70: ADC accuracy - limited test conditions, 100-pin packages</i> and <i>Table 64: ADC accuracy - limited test conditions 2</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24-Jun-2013 | 6        | Replaced Cortex-M4F with Cortex M4 with FPU<br>Updated Core, Memories and SPI bullet points in <i>Features</i><br>Removed 8KB CCM SRAM from STM32F302xx devices, updated<br><i>Figure 2:</i> STM32F303x <i>B</i> /STM32F303x <i>C</i> block diagram and Table 3:<br>STM32F303xx family device features and peripheral counts<br>Updated Section 3.4: Embedded SRAM<br>Added VREF+ in Section 3.14: Digital-to-analog converter (DAC)<br>Removed DMA support for UART5 in Table 11: USART features<br>Added 'reference clock detection' bullet in Section 3.18: Real-time clock<br>( <i>RTC</i> ) and backup registers<br>Added paragraph 'The touch sensing controller is fully' in Section 3.26:<br>Touch sensing controller (TSC)<br>Updated Comparison of I2C analog and digital filters<br>Updated Section 3.10: General-purpose input/outputs (GPIOs)<br>Added 'EVENTOUT' in Table 16: STM32F302xB/STM32F302xC pin<br>definitions and added note to 'VREF+' pin<br>Updated Σl <sub>VDD</sub> in Table 22: Current characteristics and Output driving<br>current<br>Updated Table 61: I2C timings specification (see I2C specification,<br>rev.03, June 2007) and Figure 25: I2C bus AC waveforms and<br>measurement circuit<br>Added VREF+ row to Table 68: ADC characteristics, replaced VDDA<br>with VREF+, updated t <sub>conv</sub> and added note to 'conversion voltage range<br>Added VREF+ row to Table 75: DAC characteristics and replaced VDDA<br>with VREF+ |

| 13-Nov-2013 | 7        | Removed STM32F302xB/STM32F302xC products (now in a separate datasheet).<br>Added I2S feature for SPI2 and SPI3<br>Added t <sub>SP</sub> to <i>Table 61: I2C timings specification (see I2C specification, rev.03, June 2007)</i> .<br>Renamed t <sub>SP</sub> to t <sub>AN</sub> in <i>Table 62: I2C analog filter characteristics</i> .<br>Added t <sub>STAB</sub> in <i>Table 68: ADC characteristics</i><br>Renamed V <sub>OPAMPx</sub> to <sub>VREFOPAMPx</sub><br>Updated <i>Table 71: ADC accuracy, 100-pin packages</i> .<br>Updated ADC channel names in <i>Section 3.13.1, Section 3.13.2</i> and<br><i>Section 3.13.3</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | Updated <i>Table 50: EMI characteristics</i> conditions :3.3v replaced by 3.6V.<br>Updated <i>Section 6.3.17: Communications interfaces</i> I <sup>2</sup> C interface.<br>Updated <i>Table 77: Operational amplifier characteristics</i> adding<br>TS_OPAMP_VOUT row.<br>Updated <i>Section 3.13: Fast analog-to-digital converter (ADC)</i> .<br>updated ARM and Cortex trademark.<br>Updated <i>Table 32: Typical and maximum VDD consumption in Stop and</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18-Apr-2014 | 8        | Standby modes with Max value at 85°C and 105°C.<br>Updated Table 70: ADC accuracy - limited test conditions, 100-pin<br>packages and Table 71: ADC accuracy, 100-pin packages for 100-pin<br>package.<br>Added Table 72: ADC accuracy - limited test conditions, 64-pin<br>packages and Table 73: ADC accuracy, 64-pin packagesfor 64-pin<br>package.<br>Added Table 74: ADC accuracy at 1MSPS for 1MSPS sampling<br>frequency.<br>Updated Table 63: SPI characteristics.<br>Updated Table 75: DAC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 09-Dec-2014 | 9        | Updated core description in cover page.<br>Updated HSI characteristics <i>Table 44: HSI oscillator characteristics</i> and<br><i>Figure 18: HSI oscillator accuracy characterization results for soldered</i><br><i>parts.</i><br>Updated <i>Table 58: TIMx characteristics.</i><br>Updated <i>Table 16: STM32F302xB/STM32F302xC pin definitions</i> adding<br>note for I/Os featuring an analog output function<br>(DAC_OUT,OPAMP_OUT).<br>Updated <i>Table 68: ADC characteristics</i> adding IDDA & IREF<br>consumptions.<br>Added <i>Figure 32: ADC typical current consumption on VDDA pin</i> and<br><i>Figure 33: ADC typical current consumption on VDDA pin</i> and<br><i>Figure 33: ADC typical current consumption on VREF+ pin.</i><br>Added Section 3.8: Interconnect matrix.<br>Updated <i>Figure 5: Clock tree.</i><br>Added note after <i>Table 32: Typical and maximum VDD consumption in</i><br><i>Stop and Standby modes.</i><br>Updated Section : In order to meet environmental requirements, ST<br>offers these devices in different grades of ECOPACK® packages,<br>depending on their level of environmental compliance. ECOPACK®<br>specifications, grade definitions and product status are available at:<br>www.st.com. ECOPACK® is an ST trademark. with new LQFP100,<br>LQFP64, LQFP48 package marking.<br>Updated <i>Table 16: STM32F302xB/STM32F302xC pin definitions</i> and<br>alternate functions tables replacing usart_rts by usart_rts_de. |

| 29-Jan-2015 | 10       | Updated Section 6.3.20: Comparator characteristics modifying ts_sc characteristics in Table 76 and adding Figure 37: Maximum VREFINT scaler startup time from power down.<br>Updated I <sub>DD</sub> data in Table 42: HSE oscillator characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 88. D | Ocument revision | history | (continued) |

|-------------|------------------|---------|-------------|

|-------------|------------------|---------|-------------|

| Table 66. Document revision history (continueu) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17-Apr-2015                                     | 11       | Updated Section 7: Package information: with new package information<br>structure adding 1 sub paragraph for each package.<br>Updated Figure 41: LQFP100 – 14 x 14 mm, low-profile quad flat<br>package top view example removing gate mark.<br>Added note for all packages about the device marking orientation: "the<br>following figure gives an example of topside marking orientation versus<br>pin 1 identifier location".<br>Updated Table 82: LQFP64 – 10 x 10 mm, low-profile quad flat package<br>mechanical data.                                                                                                                                                                                                                                                                                                                                         |

| 11-Dec-2015                                     | 12       | <ul> <li>Added WLCSP100:</li> <li>Updated cover page.</li> <li>Updated Table 2: STM32F303xB/STM32F303xC family device features and peripheral counts.</li> <li>Added Figure 7: STM32F303xB/STM32F303xC WLCSP100 pinout.</li> <li>Updated Table 13: STM32F303xB/STM32F303xC pin definitions.</li> <li>Updated Table 24: General operating conditions.</li> <li>Added Section 7.4: WLCSP100 - 0.4 mm pitch wafer level chip scale package information.</li> <li>Updated Table 86: Package thermal characteristics.</li> <li>Updated Table 87: Ordering information scheme.</li> <li>Updated Figure 4, Figure 5, Figure 6, Table 13 and Table 22 removing all VDD and VSS indexes.</li> <li>Updated Table 68: ADC characteristics adding V<sub>REF-</sub> negative voltage reference.</li> <li>Update Table 21: Voltage characteristics adding table note 4.</li> </ul> |

Table 88. Document revision history (continued)