# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 87                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 39x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303vbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | uction                                                                                          |

|---|-------|-------------------------------------------------------------------------------------------------|

| 2 | Desc  | ption                                                                                           |

| 3 | Func  | onal overview                                                                                   |

|   | 3.1   | ARM <sup>®</sup> Cortex <sup>®</sup> -M4 core with FPU with embedded Flash and SRAM $\ldots$ 13 |

|   | 3.2   | Memory protection unit (MPU) 13                                                                 |

|   | 3.3   | Embedded Flash memory 13                                                                        |

|   | 3.4   | Embedded SRAM                                                                                   |

|   | 3.5   | Boot modes                                                                                      |

|   | 3.6   | Cyclic redundancy check (CRC) 14                                                                |

|   | 3.7   | Power management                                                                                |

|   |       | 3.7.1 Power supply schemes                                                                      |

|   |       | 3.7.2   Power supply supervision   15                                                           |

|   |       | 3.7.3 Voltage regulator                                                                         |

|   |       | 3.7.4         Low-power modes         16                                                        |

|   | 3.8   | Interconnect matrix                                                                             |

|   | 3.9   | Clocks and startup                                                                              |

|   | 3.10  | General-purpose input/outputs (GPIOs)                                                           |

|   | 3.11  | Direct memory access (DMA) 19                                                                   |

|   | 3.12  | Interrupts and events                                                                           |

|   |       | 3.12.1 Nested vectored interrupt controller (NVIC)                                              |

|   | 3.13  | Fast analog-to-digital converter (ADC)                                                          |

|   |       | 3.13.1 Temperature sensor                                                                       |

|   |       | 3.13.2 Internal voltage reference (V <sub>REFINT</sub> )                                        |

|   |       | 3.13.3 V <sub>BAT</sub> battery voltage monitoring                                              |

|   |       | 3.13.4 OPAMP reference voltage (VREFOPAMP)                                                      |

|   | 3.14  | Digital-to-analog converter (DAC) 21                                                            |

|   | 3.15  | Operational amplifier (OPAMP) 21                                                                |

|   | 3.16  | Fast comparators (COMP)    22                                                                   |

|   | 3.17  | Timers and watchdogs 22                                                                         |

|   |       | 3.17.1 Advanced timers (TIM1, TIM8)                                                             |

# 3.7 **Power management**

# 3.7.1 **Power supply schemes**

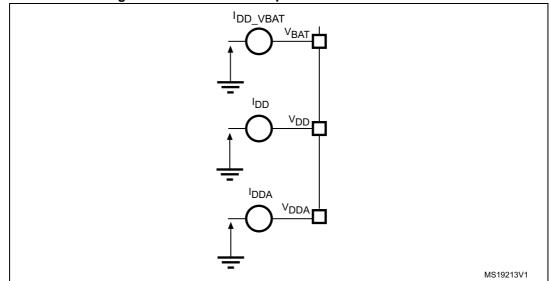

- $V_{SS}$ ,  $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. It is provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 2.0 to 3.6 V: external analog power supply for ADC, DACs, comparators operational amplifiers, reset blocks, RCs and PLL. The minimum voltage to be applied to V<sub>DDA</sub> differs from one analog peripheral to another. *Table 3* provides the summary of the V<sub>DDA</sub> ranges for analog peripherals. The V<sub>DDA</sub> voltage level must be always greater or equal to the V<sub>DD</sub> voltage level and must be provided first.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

|                   |                          | ••••                            |

|-------------------|--------------------------|---------------------------------|

| Analog peripheral | Minimum $V_{DDA}$ supply | Maximum V <sub>DDA</sub> supply |

| ADC / COMP        | 2.0 V                    | 3.6 V                           |

| DAC / OPAMP       | 2.4 V                    | 3.6V                            |

Table 3. External analog supply values for analog peripherals

# 3.7.2 Power supply supervision

The device has an integrated power-on reset (POR) and power-down reset (PDR) circuits. They are always active, and ensure proper operation above a threshold of 2 V. The device remains in reset mode when the monitored supply voltage is below a specified threshold, VPOR/PDR, without the need for an external reset circuit.

- The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.7.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR), and power-down.

- The MR mode is used in the nominal regulation mode (Run)

- The LPR mode is used in Stop mode.

- The power-down mode is used in Standby mode: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The voltage regulator is always enabled after reset. It is disabled in Standby mode.

# 3.13.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN17. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

# 3.13.4 OPAMP reference voltage (VREFOPAMP)

Every OPAMP reference voltage can be measured using a corresponding ADC internal channel: VREFOPAMP1 connected to ADC1 channel 15, VREFOPAMP2 connected to ADC2 channel 17, VREFOPAMP3 connected to ADC3 channel 17, VREFOPAMP4 connected to ADC4 channel 17.

# 3.14 Digital-to-analog converter (DAC)

Two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- Two DAC output channels

- 8-bit or 10-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability (for each channel)

- External triggers for conversion

# 3.15 Operational amplifier (OPAMP)

The STM32F303xB/STM32F303xC embeds four operational amplifiers with external or internal follower routing and PGA capability (or even amplifier and filter capability with external components). When an operational amplifier is selected, an external ADC channel is used to enable output measurement.

The operational amplifier features:

- 8.2 MHz bandwidth

- 0.5 mA output capability

- Rail-to-rail input/output

- In PGA mode, the gain can be programmed to be 2, 4, 8 or 16.

| Group | Capacitive sensing signal name | Pin<br>name | Group                                                  | Capacitive sensing signal name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin<br>name |

|-------|--------------------------------|-------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |                                                        | TSC_G5_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5                                                      | TSC_G5_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB4         |

| I     | TSC_G1_IO3                     | PA2         | 5                                                      | TSC_G5_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB6         |

|       | TSC_G1_IO4                     | PA3         |                                                        | TSC_G5_IO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB7         |

|       | TSC_G2_IO1                     | PA4         |                                                        | TSC_G6_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6                                                      | TSC_G6_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0                                                      | TSC_G6_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PB13        |

|       | TSC_G2_IO4                     | PA7         |                                                        | up         signal name         name           TSC_G5_I01         PB3           TSC_G5_I02         PB4           TSC_G5_I03         PB6           TSC_G5_I03         PB6           TSC_G5_I04         PB7           TSC_G6_I01         PB11           TSC_G6_I02         PB12           TSC_G6_I03         PB13           TSC_G6_I04         PB14           TSC_G6_I04         PB14           TSC_G6_I04         PB14           TSC_G7_I01         PE2           TSC_G7_I02         PE3           TSC_G7_I03         PE4           TSC_G7_I04         PE5           TSC_G8_I01         PD12           TSC_G8_I02         PD13           TSC_G8_I03         PD14 | PB14        |

|       | TSC_G3_IO1                     | PC5         |                                                        | TSC_G7_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PE2         |

| 3     | TSC_G3_IO2                     | PB0         | 7                                                      | TSC_G7_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PE3         |

| 5     | TSC_G3_IO3                     | PB1         | /                                                      | TSC_G7_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PE4         |

|       | TSC_G3_IO4                     | PB2         |                                                        | TSC_G7_IO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PE5         |

|       | TSC_G4_IO1                     | PA9         |                                                        | TSC_G8_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PD12        |

| 4     | TSC_G4_IO2                     | PA10        | R                                                      | TSC_G8_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PD13        |

| -     | TSC_G4_IO3                     | PA13        | 0                                                      | TSC_G8_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PD14        |

|       | TSC_G4_IO4                     | PA14        | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | PD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

# Table 10. Capacitive sensing GPIOs available on STM32F303xB/STM32F303xC devices

Table 11. No. of capacitive sensing channels available on STM32F303xB/STM32F303xC devices

|                                          | Number of capacitive sensing channels |             |             |  |  |  |  |  |  |  |  |

|------------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|--|--|--|

| Analog I/O group                         | STM32F303Vx                           | STM32F303Rx | STM32F303Cx |  |  |  |  |  |  |  |  |

| G1                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |  |

| G2                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |  |

| G3                                       | 3                                     | 3           | 2           |  |  |  |  |  |  |  |  |

| G4                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |  |

| G5                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |  |

| G6                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |  |

| G7                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |  |  |

| G8                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |  |  |

| Number of capacitive<br>sensing channels | 24                                    | 18          | 17          |  |  |  |  |  |  |  |  |

46/148

DocID023353 Rev 13

Pinouts and pin description

STM32F303xB STM32F303xC

|                    |          | Та           | able 17. Alterna | te functions fo | or port D |            |               |

|--------------------|----------|--------------|------------------|-----------------|-----------|------------|---------------|

| Port &<br>Pin Name | AF1      | AF2          | AF3              | AF4             | AF5       | AF6        | AF7           |

| PD0                | EVENTOUT | -            | -                | -               | -         | -          | CAN_RX        |

| PD1                | EVENTOUT | -            | -                | TIM8_CH4        | -         | TIM8_BKIN2 | CAN_TX        |

| PD2                | EVENTOUT | TIM3_ETR     | -                | TIM8_BKIN       | UART5_RX  | -          | -             |

| PD3                | EVENTOUT | TIM2_CH1_ETR | -                | -               | -         | -          | USART2_CTS    |

| PD4                | EVENTOUT | TIM2_CH2     | -                | -               | -         | -          | USART2_RTS_DE |

| PD5                | EVENTOUT | -            | -                | -               | -         | -          | USART2_TX     |

| PD6                | EVENTOUT | TIM2_CH4     | -                | -               | -         | -          | USART2_RX     |

| PD7                | EVENTOUT | TIM2_CH3     | -                | -               | -         | -          | USART2_CK     |

| PD8                | EVENTOUT | -            | -                | -               | -         | -          | USART3_TX     |

| PD9                | EVENTOUT | -            | -                | -               | -         | -          | USART3_RX     |

| PD10               | EVENTOUT | -            | -                | -               | -         | -          | USART3_CK     |

| PD11               | EVENTOUT | -            | -                | -               | -         | -          | USART3_CTS    |

| PD12               | EVENTOUT | TIM4_CH1     | TSC_G8_IO1       | -               | -         | -          | USART3_RTS_D  |

| PD13               | EVENTOUT | TIM4_CH2     | TSC_G8_IO2       | -               | -         | -          | -             |

| PD14               | EVENTOUT | TIM4_CH3     | TSC_G8_IO3       | -               | -         | -          | -             |

| PD15               | EVENTOUT | TIM4_CH4     | TSC_G8_IO4       | -               | -         | SPI2_NSS   | -             |

DocID023353 Rev 13

5

49/148

Pinouts and pin description

#### 6.1.7 **Current consumption measurement**

### Figure 12. Current consumption measurement scheme

#### Absolute maximum ratings 6.2

Stresses above the absolute maximum ratings listed in Table 21: Voltage characteristics, Table 22: Current characteristics, and Table 23: Thermal characteristics may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                             | Ratings                                                                    | Min                                    | Мах                                                    | Unit |

|----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                   | External main supply voltage (including $V_{DDA,}$ $V_{BAT}$ and $V_{DD})$ | -0.3                                   | 4.0                                                    |      |

| V <sub>DD</sub> -V <sub>DDA</sub>                  | Allowed voltage difference for $V_{DD} > V_{DDA}$                          | -                                      | 0.4                                                    |      |

| V <sub>REF+</sub> -V <sub>DDA</sub> <sup>(2)</sup> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                        | -                                      | 0.4                                                    |      |

|                                                    | Input voltage on FT and FTf pins                                           | V <sub>SS</sub> –0.3                   | V <sub>DD</sub> + 4.0                                  | V    |

| V <sub>IN</sub> <sup>(3)</sup>                     | Input voltage on TTa pins                                                  | V <sub>SS</sub> -0.3 4.0               |                                                        |      |

| VIN Y                                              | Input voltage on any other pin                                             | V <sub>SS</sub> -0.3                   | 4.0                                                    |      |

|                                                    | Input voltage on Boot0 pin                                                 | 0                                      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |      |

| $ \Delta V_{DDx} $                                 | Variations between different V <sub>DD</sub> power pins                    | -                                      | 50                                                     | m\/  |

| V <sub>SSX</sub> –V <sub>SS</sub>                  | Variations between all the different ground pins <sup>(4)</sup>            | -                                      | 50                                                     | 111V |

| V <sub>ESD(HBM)</sub>                              | Electrostatic discharge voltage (human body model)                         | see Section 6.3.<br>sensitivity charac |                                                        | -    |

| Table 21 | . Voltage | characteristics <sup>(1)</sup> |

|----------|-----------|--------------------------------|

|----------|-----------|--------------------------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

|        |                      |                                                  | Typ @V <sub>DD</sub> (V <sub>DD</sub> =V <sub>DDA</sub> ) |       |                    |                    |       |       |                           | Max <sup>(1)</sup>        |                            |         |  |

|--------|----------------------|--------------------------------------------------|-----------------------------------------------------------|-------|--------------------|--------------------|-------|-------|---------------------------|---------------------------|----------------------------|---------|--|

|        |                      |                                                  |                                                           | Тур ( | @v <sub>DD</sub> ( | v <sub>DD</sub> =v | DDA)  |       |                           | max"                      |                            |         |  |

| Symbol | Parameter            | Conditions                                       | 2.0 V                                                     | 2.4 V | 2.7 V              | 3.0 V              | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | Т <sub>А</sub> =<br>85 °С | T <sub>A</sub> =<br>105 °C | Unit    |  |

|        | Supply<br>current in | Regulator in run mode,<br>all oscillators OFF    | 20.05                                                     | 20.33 | 20.42              | 20.50              | 20.67 | 20.80 | 44.2 <sup>(2)</sup>       | 350                       | 735 <sup>(2)</sup>         |         |  |

|        | Stop mode            | Regulator in low-power mode, all oscillators OFF | 7.63                                                      | 7.77  | 7.90               | 8.07               | 8.17  | 8.33  | 30.6 <sup>(2)</sup>       | 335                       | 720 <sup>(2)</sup>         | )<br>µA |  |

|        | Supply               | LSI ON and IWDG ON                               | 0.80                                                      | 0.96  | 1.09               | 1.23               | 1.37  | 1.51  | -                         | -                         | -                          |         |  |

|        |                      | LSI OFF and IWDG OFF                             | 0.60                                                      | 0.74  | 0.83               | 0.93               | 1.02  | 1.11  | 5.0 <sup>(2)</sup>        | 7.8                       | 13.3 <sup>(2)</sup>        |         |  |

| Table 32. Typical and maximum V | consumption in Sto | p and Standby modes  |

|---------------------------------|--------------------|----------------------|

| Tuble of Typical and maximum v  |                    | p und oluniday modes |

1. Guaranteed by characterization results unless otherwise specified.

2. Data based on characterization results and tested in production.

|        |                                         |                       |                                                        |       | Тур @                                                  | )V <sub>DD</sub> ( | V <sub>DD</sub> = |       | Max <sup>(1)</sup> |                           |                           |                            |      |   |  |

|--------|-----------------------------------------|-----------------------|--------------------------------------------------------|-------|--------------------------------------------------------|--------------------|-------------------|-------|--------------------|---------------------------|---------------------------|----------------------------|------|---|--|

| Symbol | Parameter                               |                       | Conditions                                             | 2.0 V | 2.4 V                                                  | 2.7 V              | 3.0 V             | 3.3 V | 3.6 V              | T <sub>A</sub> =<br>25 °C | Т <sub>А</sub> =<br>85 °С | T <sub>A</sub> =<br>105 °C | Unit |   |  |

|        | Supply                                  | NO                    | Regulator in run mode, all oscillators OFF             | 1.81  | 1.95                                                   | 2.07               | 2.20              | 2.35  | 2.52               | 3.7                       | 5.5                       | 8.8                        |      |   |  |

|        | current in<br>Stop mode                 | oring                 | Regulator in low-power<br>mode, all oscillators<br>OFF | 1.81  | 1.95                                                   | 2.07               | 2.20              | 2.35  | 2.52               | 3.7                       | 5.5                       | 8.8                        |      |   |  |

|        | Supply<br>current in<br>Standby<br>mode | Juppiy                | LSI ON and IWDG ON                                     | 2.22  | 2.42                                                   | 2.59               | 2.78              | 3.0   | 3.24               | -                         | -                         | -                          |      |   |  |

|        |                                         |                       | LSI OFF and IWDG<br>OFF                                | 1.69  | 1.82                                                   | 1.94               | 2.08              | 2.23  | 2.40               | 3.5                       | 5.4                       | 9.2                        |      |   |  |

| IDDA   | Supply                                  | ЦЦ                    | Regulator in run mode,<br>all oscillators OFF          | 1.05  | 1.08                                                   | 1.10               | 1.15              | 1.22  | 1.29               | -                         | -                         | -                          | μA   |   |  |

|        | current in                              | current in            |                                                        | Drin  | Regulator in low-power<br>mode, all oscillators<br>OFF | 1.05               | 1.08              | 1.10  | 1.15               | 1.22                      | 1.29                      | -                          | -    | - |  |

|        | current in Standby                      | -                     | LSI ON and IWDG ON                                     | 1.44  | 1.52                                                   | 1.60               | 1.71              | 1.84  | 1.98               | -                         | -                         | -                          |      |   |  |

|        |                                         | current in<br>Standby | current in<br>Standby<br>mode                          | ~     | LSI OFF and IWDG<br>OFF                                | 0.93               | 0.95              | 0.98  | 1.02               | 1.08                      | 1.15                      | -                          | -    | - |  |

# Table 33. Typical and maximum $V_{\text{DDA}}$ consumption in Stop and Standby modes

1. Guaranteed by characterization results.

The total consumption is the sum of IDD and IDDA.

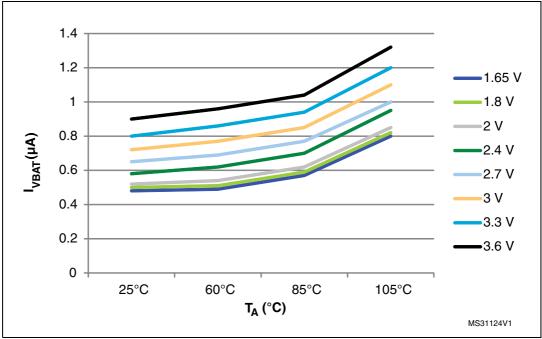

| Symbol   | Para              | (4)                                                                                           | Тур @V <sub>BAT</sub> |      |      |      |      |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |     |                           | Unit |

|----------|-------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|------|------|------|-------------------------------------------------|-----|---------------------------|------|

|          | meter             | (1)                                                                                           | 1.65V                 | 1.8V | 2V   | 2.4V | 2.7V | 3V   | 3.3V | 3.6V | T <sub>A</sub> =<br>25°C                        |     | T <sub>A</sub> =<br>105°C | onne |

|          | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48                  | 0.50 | 0.52 | 0.58 | 0.65 | 0.72 | 0.80 | 0.90 | 1.1                                             | 1.5 | 2.0                       |      |

| IDD_VBAT | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83                  | 0.86 | 0.90 | 0.98 | 1.03 | 1.10 | 1.20 | 1.30 | 1.5                                             | 2.2 | 2.9                       | μΑ   |

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Guaranteed by characterization results.

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

# Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V

- All I/O pins available on each package are in analog input configuration

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait states from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 MHz to 72 MHz), and Flash prefetch is ON

- When the peripherals are enabled,  $f_{APB1} = f_{AHB/2}$ ,  $f_{APB2} = f_{AHB}$

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8,16 and 64 is used for the frequencies 4 MHz, 2 MHz, 1 MHz, 500 kHz and 125 kHz respectively.

#### Table 35. Typical current consumption in Run mode, code with data processing running from Flash

|                                     |                                 | Conditions           |         | Ţ                      |                         |      |

|-------------------------------------|---------------------------------|----------------------|---------|------------------------|-------------------------|------|

| Symbol                              | Parameter                       |                      | fhclk   | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                                     |                                 |                      | 72 MHz  | 61.3                   | 28.0                    |      |

|                                     |                                 |                      | 64 MHz  | 54.8                   | 25.4                    |      |

|                                     |                                 |                      | 48 MHz  | 41.9                   | 19.3                    |      |

|                                     |                                 |                      | 32 MHz  | 28.5                   | 13.3                    |      |

|                                     |                                 |                      | 24 MHz  | 21.8                   | 10.4                    |      |

|                                     | Supply current in Run mode from |                      | 16 MHz  | 14.9                   | 7.2                     | mA   |

| I <sub>DD</sub>                     | V <sub>DD</sub> supply          |                      | 8 MHz   | 7.7                    | 3.9                     |      |

|                                     |                                 |                      | 4 MHz   | 4.5                    | 2.5                     | -    |

|                                     |                                 |                      | 2 MHz   | 2.8                    | 1.7                     |      |

|                                     |                                 |                      | 1 MHz   | 1.9                    | 1.3                     |      |

|                                     |                                 | Running from HSE     | 500 kHz | 1.4                    | 1.1                     |      |

|                                     |                                 | crystal clock 8 MHz, | 125 kHz | 1.1                    | 0.9                     |      |

|                                     |                                 | code executing from  | 72 MHz  | 240.3                  | 239.5                   |      |

|                                     |                                 | Flash                | 64 MHz  | 210.9                  | 210.3                   |      |

|                                     |                                 |                      | 48 MHz  | 155.8                  | 155.6                   |      |

|                                     |                                 |                      | 32 MHz  | 105.7                  | 105.6                   |      |

|                                     |                                 |                      | 24 MHz  | 82.1                   | 82.0                    |      |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Supply current in Run mode from |                      | 16 MHz  | 58.8                   | 58.8                    | μA   |

| 'DDA` / ` /                         | V <sub>DDA</sub> supply         |                      | 8 MHz   | 2.4                    | 2.4                     | μΑ   |

|                                     |                                 |                      | 4 MHz   | 2.4                    | 2.4                     | -    |

|                                     |                                 |                      | 2 MHz   | 2.4                    | 2.4                     |      |

|                                     |                                 |                      | 1 MHz   | 2.4                    | 2.4                     |      |

|                                     |                                 |                      | 500 kHz | 2.4                    | 2.4                     |      |

|                                     |                                 |                      | 125 kHz | 2.4                    | 2.4                     | ]    |

1. V<sub>DDA</sub> monitoring is ON.

2. When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

| Table 36. Peripheral current consumption (continued) |                                    |        |  |  |  |

|------------------------------------------------------|------------------------------------|--------|--|--|--|

| Peripheral                                           | Typical consumption <sup>(1)</sup> | Unit   |  |  |  |

| · ···p·····                                          | IDD                                |        |  |  |  |

| TIM6                                                 | 9.7                                |        |  |  |  |

| TIM7                                                 | 12.1                               |        |  |  |  |

| WWDG                                                 | 6.4                                |        |  |  |  |

| SPI2                                                 | 40.4                               |        |  |  |  |

| SPI3                                                 | 40.0                               |        |  |  |  |

| USART2                                               | 41.9                               |        |  |  |  |

| USART3                                               | 40.2                               |        |  |  |  |

| UART4                                                | 36.5                               | µA/MHz |  |  |  |

| UART5                                                | 30.8                               |        |  |  |  |

| I2C1                                                 | 10.5                               |        |  |  |  |

| I2C2                                                 | 10.4                               |        |  |  |  |

| USB                                                  | 26.2                               |        |  |  |  |

| CAN                                                  | 33.4                               |        |  |  |  |

| PWR                                                  | 5.7                                |        |  |  |  |

| DAC                                                  | 15.4                               |        |  |  |  |

Table 38. Peripheral current consumption (continued)

1. The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

2. BusMatrix is automatically active when at least one master is ON (CPU, DMA1 or DMA2).

3. The APBx bridge is automatically active when at least one peripheral is ON on the same bus.

# 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

# Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 49*. They are based on the EMS levels and classes defined in the application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25°C,<br>f <sub>HCLK</sub> = 72 MHz<br>conforms to IEC 61000-4-4 | 4A              |

### Table 49. EMS characteristics

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

## Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

## **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

# **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter              | Conditions                                        | Monitored               | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|--------|------------------------|---------------------------------------------------|-------------------------|------------------------------------------------|------|

| Symbol | Farameter              | contaitions                                       | frequency band 8/72 MHz |                                                | Unit |

|        |                        |                                                   | 0.1 to 30 MHz           | 7                                              |      |

| 6      | S Poak lovel LQFP100 p | $V_{DD} = 3.6 V, T_A = 25 °C,$<br>LQFP100 package | 30 to 130 MHz           | 20                                             | dBµV |

| SEMI   |                        | compliant with IEC                                | 130 MHz to 1GHz         | 27                                             |      |

|        |                        | 01907-2                                           | SAE EMI Level           | 4                                              | -    |

Table 50. EMI characteristics

# 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

# Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1 standard.

| Symbol                | Ratings                                                  | Conditions                                                  |                                | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = +25 \ ^{\circ}C$ , conforming to JESD22-A114         |                                | 2     | 2000                            |      |

|                       | Electrostatic                                            |                                                             | WLCSP100<br>package            | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | discharge voltage<br>(charge device model)               | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | Packages<br>except<br>WLCSP100 | 4     | 500                             |      |

Table 51. ESD absolute maximum ratings

1. Guaranteed by characterization results.

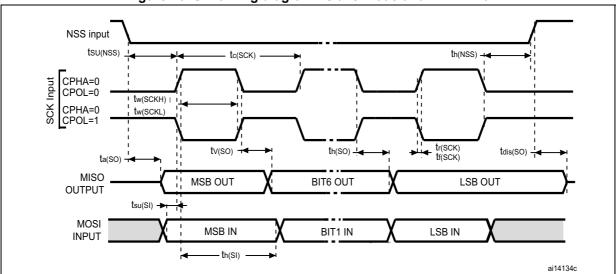

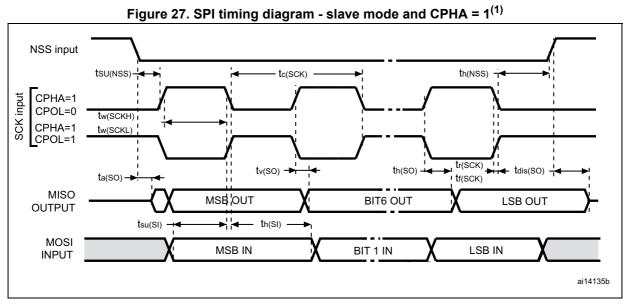

Figure 26. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

# 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 68* to *Table 70* are guaranteed by design, with conditions summarized in *Table 24*.

| Symbol            | Parameter                                                         | Conditions                     | Min | Тур   | Max              | Unit |  |

|-------------------|-------------------------------------------------------------------|--------------------------------|-----|-------|------------------|------|--|

| V <sub>DDA</sub>  | Analog supply voltage for ADC                                     | -                              | 2   | -     | 3.6              | V    |  |

|                   |                                                                   | Single-ended mode,<br>5 MSPS   | -   | 907   | 1033.0           |      |  |

|                   |                                                                   | Single-ended mode,<br>1 MSPS   | -   | 194   | 285.5            |      |  |

|                   | ADC current consumption on VDDA                                   | Single-ended mode,<br>200 KSPS | -   | 51.5  | 70               | μΑ   |  |

| I <sub>DDA</sub>  | (see <i>Figure 32</i> )                                           | Differential mode,<br>5 MSPS   | -   | 887.5 | 1009             | _ μΑ |  |

|                   |                                                                   | Differential mode,<br>1 MSPS   | -   | 212   | 285              |      |  |

|                   |                                                                   | Differential mode,<br>200 KSPS | -   | 51    | 69.5             |      |  |

| V <sub>REF+</sub> | Positive reference voltage                                        | -                              | 2   | -     | V <sub>DDA</sub> | V    |  |

| V <sub>REF-</sub> | Negative reference voltage                                        | -                              | -   | 0     | -                |      |  |

|                   |                                                                   | Single-ended mode,<br>5 MSPS   | -   | 104   | 139              | -    |  |

|                   | ADC current consumption on VREF+<br>pin<br>(see <i>Figure</i> 33) | Single-ended mode,<br>1 MSPS   | -   | 20.4  | 37               |      |  |

| I                 |                                                                   | Single-ended mode,<br>200 KSPS | -   | 3.3   | 11.3             |      |  |

| I <sub>REF</sub>  |                                                                   | Differential mode,<br>5 MSPS   | -   | 174   | 235              | - μΑ |  |

|                   |                                                                   | Differential mode,<br>1 MSPS   | -   | 34.6  | 52.6             | 1    |  |

|                   |                                                                   | Differential mode,<br>200 KSPS | -   | 6     | 13.6             |      |  |

# Table 68. ADC characteristics

103/148

| Symbol                                             | Parameter      | Conditions                                                     |                     |                     |     | Max<br>(4) | Unit |

|----------------------------------------------------|----------------|----------------------------------------------------------------|---------------------|---------------------|-----|------------|------|

|                                                    |                |                                                                | Single ended        | Fast channel 5.1 Ms | 64  | -          |      |

| SNR <sup>(5)</sup>                                 | Signal-to-     |                                                                | Single ended        | Slow channel 4.8 Ms | 64  | -          |      |

| SNR                                                | noise ratio    | ADC clock freq. $\leq$ 72 MHz,<br>Sampling freq $\leq$ 5 Msps, | Differential        | Fast channel 5.1 Ms | 67  | -          |      |

|                                                    |                |                                                                |                     | Slow channel 4.8 Ms | 67  | -          | dB   |

|                                                    |                | $2 V \le V_{DDA} \le 3.6 V$                                    | Single and d        | Fast channel 5.1 Ms | -   | -75        | иБ   |

| THD <sup>(5)</sup> Total<br>harmonic<br>distortion | 64-pin package | Single ended                                                   | Slow channel 4.8 Ms | -                   | -75 |            |      |

|                                                    |                |                                                                |                     | Fast channel 5.1 Ms | -   | -79        |      |

|                                                    |                |                                                                | Differential        | Slow channel 4.8 Ms | -   | -78        |      |

| Table 73. ADC accuracy, 64-pin | packages <sup>(1)(2)(3)</sup> (continued) |

|--------------------------------|-------------------------------------------|

|--------------------------------|-------------------------------------------|

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

- 3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. Guaranteed by characterization results.

- 5. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

| Symbol                      | Parameter                    | Test condition                                                                       | IS           | Тур  | Max <sup>(3)</sup> | Unit |

|-----------------------------|------------------------------|--------------------------------------------------------------------------------------|--------------|------|--------------------|------|

| ET                          | Total upadiustad arrar       |                                                                                      | Fast channel | ±2.5 | ±5                 |      |

|                             | Total unadjusted error       |                                                                                      | Slow channel | ±3.5 | ±5                 |      |

| EO                          | Offset error                 |                                                                                      | Fast channel | ±1   | ±2.5               |      |

| EO                          | EG Gain error                |                                                                                      | Slow channel | ±1.5 | ±2.5               |      |

| EC                          |                              | Sampling Freq ≤ 1MSPS                                                                | Fast channel | ±2   | ±3                 | LSB  |

| LG                          |                              | $2.4 \text{ V} \le \text{V}_{\text{DDA}} = \text{V}_{\text{REF+}} \le 3.6 \text{ V}$ | Slow channel | ±3   | ±4                 | LOD  |

| ED                          | Differential linearity error | Single-ended mode                                                                    | Fast channel | ±0.7 | ±2                 |      |

|                             | Differential linearity error |                                                                                      | Slow channel | ±0.7 | ±2                 |      |

| EL Integral linearity error | Integral linearity error     |                                                                                      | Fast channel | ±1   | ±3                 |      |

|                             |                              |                                                                                      | Slow channel | ±1.2 | ±3                 |      |

# Table 74. ADC accuracy at 1MSPS<sup>(1)(2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for IINJ(PIN) and ∑IINJ(PIN) in Section 6.3.14: I/O port characteristics does not affect the ADC accuracy.

3. Guaranteed by characterization results.

|          | (continuou) |             |      |        |                       |        |

|----------|-------------|-------------|------|--------|-----------------------|--------|

| 0h. a.l. |             | millimeters |      |        | inches <sup>(1)</sup> |        |

| Symbol   | Min         | Тур         | Мах  | Min    | Тур                   | Max    |

| E1       | 6.80        | 7.00        | 7.20 | 0.2677 | 0.2756                | 0.2835 |

| E3       | -           | 5.50        | -    | -      | 0.2165                | -      |

| е        | -           | 0.50        | -    | -      | 0.0197                | -      |

| L        | 0.45        | 0.60        | 0.75 | 0.0177 | 0.0236                | 0.0295 |

| L1       | -           | 1.00        | -    | -      | 0.0394                | -      |

| K        | 0°          | 3.5°        | 7°   | 0°     | 3.5°                  | 7°     |

| CCC      | -           | -           | 0.08 | -      | -                     | 0.0031 |

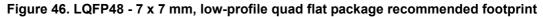

# Table 83. LQFP48 – 7 x 7 mm, low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

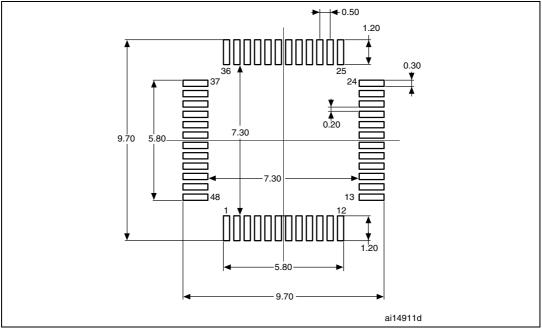

# Figure 49. WLCSP100 – 100L, 4.166 x 4.628 mm 0.4 mm pitch wafer level chip scale package recommended footprint

## Table 85. WLCSP100 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values |

|-------------------|--------------------|

| Pitch             | 0.4 mm             |

| Dpad              | 0.225 mm           |

| Dsm               | 0.290 mm           |

| Stencil thickness | 0.1 mm             |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06-May-2016 | 13       | <ul> <li>Updated Table 43: LSE oscillator characteristics (fLSE = 32.768 kHz)</li> <li>LSEDRV[1:0] bits.</li> <li>Updated Table 28: Embedded internal reference voltage V<sub>REFINT</sub> internal reference voltage (min and typ values).</li> <li>Updated Figure 5: STM32F303xB/STM32F303xC LQFP64 pinout replacing VSS by PF4.</li> <li>Updated Table 51: ESD absolute maximum ratings ESD CDM at class 3 and 4 including WLCSP100 package information.</li> <li>Updated Table 13: STM32F303xB/STM32F303xC pin definitions:</li> <li>Adding 'digital power supply' in the Pin function column at the line corresponding to K8/28/19 pins.</li> <li>Adding VSS digital ground line with WLCSP100 K9 and K10 pins connected.</li> <li>Replacing in VDD line for WLCSP100: 'A10, B10' by 'A9, A10, B10, B8'.</li> <li>Updated Table 77: Operational amplifier characteristics high saturation and low saturation voltages.</li> <li>Updated Table 13: STM32F303xB/STM32F303xC pin definitions adding note 'Fast ADC channel' for ADCx_IN15.</li> <li>Updated Table 68: ADC characteristics adding CMIR parameter and modifying tSTAB parameter characteristics.</li> </ul> |

| Table 88. | Document | revision  | history | (continued) | ١ |

|-----------|----------|-----------|---------|-------------|---|

|           | Document | 101101011 | motory  | loonunaca   |   |

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved