## STMicroelectronics - <u>STM32F303VCT6TR Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product StatusActiveCore ProcessorARM® Cortex®-M4Core Size32-Bit Single-CoreSpeed72MzConnectivityCANbus, PC, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, PS, OR, PWM, WDTNumber of I/O87Program Memory Size56KB (256K x 8)Program Memory TypeFLASHEERPOM Size-Nufsze40K x 8Voltage - Supply (Vcc/Vdd)2V - 3.6VDataConvertersAD 39x12b; D/A 2x12bOperating TypeInternalMounting TypeSurface MountProgram Grape10-LQFPSupplier Percease10-LQFP (14x14)Supplier Device Package10-LQFP (14x14) |                            |                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed72MHzConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O87Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPUsed Supple Cove Package100-LQFP (14x14)                              | Product Status             | Active                                                                  |

| Speed72MHzConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O87Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                         | Core Processor             | ARM® Cortex®-M4                                                         |

| ConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O87Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                   | Core Size                  | 32-Bit Single-Core                                                      |

| PeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O87Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                              | Speed                      | 72MHz                                                                   |

| Number of I/O87Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type500-LQFPSuppler Device Package100-LQFP (14x14)                                                                                                                                                                                             | Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSuppler Device Package100-LQFP (14x14)                                                                                                                                                                                 | Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Program Memory TypeFLASHEEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                                                                                  | Number of I/O              | 87                                                                      |

| EEPROM Size-RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFP (14x14)                                                                                                                                                                                                                                                                          | Program Memory Size        | 256КВ (256К х 8)                                                        |

| RAM Size40K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                       | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                      | EEPROM Size                | <u>.</u>                                                                |

| Data ConvertersA/D 39x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                                                         | RAM Size                   | 40K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14×14)                                                                                                                                                                                                                                                                                                                                             | Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                    | Data Converters            | A/D 39x12b; D/A 2x12b                                                   |

| Mounting TypeSurface MountPackage / Case100-LQFPSupplier Device Package100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                          | Oscillator Type            | Internal                                                                |

| Package / Case 100-LQFP   Supplier Device Package 100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                               | Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Supplier Device Package 100-LQFP (14x14)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Package / Case             | 100-LQFP                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303vct6tr                                                                                                                                                                                                                                                                                                                                                                                                             | Supplier Device Package    | 100-LQFP (14x14)                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303vct6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 6.3.4      | Embedded reference voltage62                                       |

|-------|------------|--------------------------------------------------------------------|

|       | 6.3.5      | Supply current characteristics62                                   |

|       | 6.3.6      | Wakeup time from low-power mode                                    |

|       | 6.3.7      | External clock source characteristics74                            |

|       | 6.3.8      | Internal clock source characteristics                              |

|       | 6.3.9      | PLL characteristics                                                |

|       | 6.3.10     | Memory characteristics81                                           |

|       | 6.3.11     | EMC characteristics                                                |

|       | 6.3.12     | Electrical sensitivity characteristics83                           |

|       | 6.3.13     | I/O current injection characteristics84                            |

|       | 6.3.14     | I/O port characteristics                                           |

|       | 6.3.15     | NRST pin characteristics91                                         |

|       | 6.3.16     | Timer characteristics                                              |

|       | 6.3.17     | Communications interfaces94                                        |

|       | 6.3.18     | ADC characteristics                                                |

|       | 6.3.19     | DAC electrical specifications 117                                  |

|       | 6.3.20     | Comparator characteristics 119                                     |

|       | 6.3.21     | Operational amplifier characteristics                              |

|       | 6.3.22     | Temperature sensor characteristics                                 |

|       | 6.3.23     | V <sub>BAT</sub> monitoring characteristics                        |

| Pack  | kage info  | ormation                                                           |

| 7.1   | LQFP1      | 00 – 14 x 14 mm, low-profile quad flat package                     |

|       | informa    | ation                                                              |

| 7.2   |            | 4 – 10 x 10 mm, low-profile quad flat package                      |

|       |            | ation                                                              |

| 7.3   |            | 8 – 7 x 7 mm, low-profile quad flat package                        |

|       |            | ation                                                              |

| 7.4   | WLCSI      | P100 - 0.4 mm pitch wafer level chip scale package information 134 |

| 7.5   | Therma     | al characteristics                                                 |

|       | 7.5.1      | Reference document                                                 |

|       | 7.5.2      | Selecting the product temperature range                            |

| Orde  | ering inf  | ormation                                                           |

| Davi  | oion hia   | 140 March 140                                                      |

| IZGAI | 21011 1112 | story                                                              |

8

9

7

# 3.22 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I2S)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) supporting four different audio standards can operate as master or slave at half-duplex and full duplex communication modes. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by 8-bit programmable linear prescaler. When operating in master mode it can output a clock for an external audio component at 256 times the sampling frequency.

Refer to *Table 9* for the features available in SPI1, SPI2 and SPI3.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 | SPI3 |

|-----------------------------|------|------|------|

| Hardware CRC calculation    | Х    | Х    | Х    |

| Rx/Tx FIFO                  | Х    | Х    | Х    |

| NSS pulse mode              | Х    | Х    | Х    |

| I2S mode                    | -    | Х    | Х    |

| TI mode                     | Х    | Х    | Х    |

Table 9. STM32F303xB/STM32F303xC SPI/I2S implementation

1. X = supported.

## 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

## 3.24 Universal serial bus (USB)

The STM32F303xB/STM32F303xC devices embed an USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator). The USB has a dedicated 512-bytes SRAM memory for data transmission and reception.

| Group | Capacitive sensing signal name | Pin<br>name | Group      | Capacitive sensing signal name                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin<br>name |

|-------|--------------------------------|-------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         | PA0        | TSC_G5_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5          | TSC_G5_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB4         |

| I     | TSC_G1_IO3                     | PA2         | 5          | TSC_G5_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB6         |

|       | TSC_G1_IO4                     | PA3         |            | TSC_G5_IO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB7         |

|       | TSC_G2_IO1                     | PA4         |            | TSC_G6_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6          | TSC_G6_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0          | TSC_G6_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PB13        |

|       | TSC_G2_IO4                     |             | TSC_G6_IO4 | PB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

|       | TSC_G3_IO1                     | PC5         |            | TSC_G7_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PE2         |

| 3     | TSC_G3_IO2                     | PB0         | 7          | TSC_G7_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PE3         |

| 5     | TSC_G3_IO3                     | PB1         | /          | TSC_G7_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PE4         |

|       | TSC_G3_IO4                     | PB2         |            | TSC_G5_IO1     PB3       TSC_G5_IO2     PB4       TSC_G5_IO3     PB6       TSC_G5_IO4     PB7       TSC_G6_IO1     PB12       TSC_G6_IO2     PB12       TSC_G6_IO3     PB14       TSC_G6_IO3     PB12       TSC_G6_IO3     PB14       TSC_G6_IO4     PB14       TSC_G6_IO4     PB14       TSC_G6_IO4     PB14       TSC_G7_IO1     PE2       TSC_G7_IO2     PE3       TSC_G7_IO3     PE4       TSC_G7_IO4     PE5       TSC_G8_IO1     PD12       TSC_G8_IO2     PD13       TSC_G8_IO3     PD14 | PE5         |

|       | TSC_G4_IO1                     | PA9         |            | TSC_G8_IO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD12        |

| 4     | TSC_G4_IO2                     | PA10        | 8          | TSC_G8_IO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD13        |

| -     | TSC_G4_IO3                     | PA13        | 0          | TSC_G8_IO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD14        |

|       | TSC_G4_IO4                     | PA14        |            | TSC_G8_IO4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD15        |

## Table 10. Capacitive sensing GPIOs available on STM32F303xB/STM32F303xC devices

Table 11. No. of capacitive sensing channels available on STM32F303xB/STM32F303xC devices

|                                          | Number of capacitive sensing channels |             |             |  |  |  |  |  |  |  |

|------------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|--|--|

| Analog I/O group                         | STM32F303Vx                           | STM32F303Rx | STM32F303Cx |  |  |  |  |  |  |  |

| G1                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |

| G2                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |

| G3                                       | 3                                     | 3           | 2           |  |  |  |  |  |  |  |

| G4                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |

| G5                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |

| G6                                       | 3                                     | 3           | 3           |  |  |  |  |  |  |  |

| G7                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |  |

| G8                                       | 3                                     | 0           | 0           |  |  |  |  |  |  |  |

| Number of capacitive<br>sensing channels | 24                                    | 18          | 17          |  |  |  |  |  |  |  |

## 3.27 Development support

#### 3.27.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 3.27.2 Embedded trace macrocell<sup>™</sup>

The ARM embedded trace macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F303xB/STM32F303xC through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using a high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

| Na               | me                   | Abbreviation                                     | Definition                                                                                            |  |  |  |

|------------------|----------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| Pin r            | name                 |                                                  | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |

|                  |                      | S                                                | Supply pin                                                                                            |  |  |  |

| Pin              | type                 | I                                                | Input only pin                                                                                        |  |  |  |

|                  |                      | I/O                                              | Input / output pin                                                                                    |  |  |  |

|                  |                      | FT                                               | 5 V tolerant I/O                                                                                      |  |  |  |

|                  |                      | FTf 5 V tolerant I/O, FM+ capable                |                                                                                                       |  |  |  |

| I/O etr          | ucture               | TTa 3.3 V tolerant I/O directly connected to ADC |                                                                                                       |  |  |  |

| i/O su           | uclure               | TC Standard 3.3V I/O                             |                                                                                                       |  |  |  |

|                  |                      | В                                                | Dedicated BOOT0 pin                                                                                   |  |  |  |

|                  |                      | RST                                              | Bidirectional reset pin with embedded weak pull-up resistor                                           |  |  |  |

| No               | tes                  | Unless otherwis                                  | e specified by a note, all I/Os are set as floating inputs during and after reset                     |  |  |  |

| D'               | Alternate functions  | Fu                                               | nctions selected through GPIOx_AFR registers                                                          |  |  |  |

| Pin<br>functions | Additional functions | Functions                                        | directly selected/enabled through peripheral registers                                                |  |  |  |

| Table 12. Legend/abbreviations used in the pinout table |  |

|---------------------------------------------------------|--|

| Table 12. Logena/abbreviatione acea in the phieut table |  |

#### Table 13. STM32F303xB/STM32F303xC pin definitions

|          | Pin nı  | umber  |        |                                          |          |                   |       | Pin fu                                     | nctions              |

|----------|---------|--------|--------|------------------------------------------|----------|-------------------|-------|--------------------------------------------|----------------------|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure     | Notes | Alternate functions                        | Additional functions |

| D6       | 1       | -      | -      | PE2                                      | I/O      | FT                | (1)   | TRACECK, TIM3_CH1,<br>TSC_G7_IO1, EVENTOUT | -                    |

| D7       | 2       | -      | -      | PE3                                      | I/O      | FT                | (1)   | TRACED0, TIM3_CH2,<br>TSC_G7_IO2, EVENTOUT | -                    |

| C8       | 3       | -      | -      | PE4                                      | I/O      | FT                | (1)   | TRACED1, TIM3_CH3,<br>TSC_G7_IO3, EVENTOUT | -                    |

| B9       | 4       | -      | -      | PE5                                      | I/O      | FT <sup>(1)</sup> |       | TRACED2, TIM3_CH4,<br>TSC_G7_IO4, EVENTOUT | -                    |

| E7       | 5       | -      | -      | PE6                                      | I/O      | FT                | (1)   | TRACED3, EVENTOUT                          | WKUP3, RTC_TAMP3     |

| D8       | 6       | 1      | 1      | V <sub>BAT</sub>                         | S        | -                 | -     | Backup po                                  | ower supply          |

|                           | Pin nı  | umber  |        |                                          |          |               |       | Pin functions                                                                                                                        |                      |  |  |  |  |

|---------------------------|---------|--------|--------|------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| WLCSP100                  | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                  | Additional functions |  |  |  |  |

| В5                        | 90      | 56     | 40     | PB4                                      | I/O      | FT            | -     | SPI3_MISO, I2S3ext_SD,<br>SPI1_MISO, USART2_RX,<br>TIM3_CH1, TIM16_CH1,<br>TIM17_BKIN, TIM8_CH2N,<br>TSC_G5_IO2, NJTRST,<br>EVENTOUT | -                    |  |  |  |  |

| A6                        | 91      | 57     | 41     | PB5                                      | I/O      | FT            | -     | SPI3_MOSI, SPI1_MOSI,<br>I2S3_SD, I2C1_SMBA,<br>USART2_CK, TIM16_BKIN,<br>TIM3_CH2, TIM8_CH3N,<br>TIM17_CH1, EVENTOUT                | -                    |  |  |  |  |

| В6                        | 92      | 58     | 42     | PB6                                      | I/O      | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N, TIM4_CH1,<br>TIM8_CH1,TSC_G5_IO3,<br>TIM8_ETR, TIM8_BKIN2,<br>EVENTOUT                           | -                    |  |  |  |  |

| C5                        | 93      | 59     | 43     | PB7                                      | I/O      | FTf           | -     | I2C1_SDA, USART1_RX,<br>TIM3_CH4, TIM4_CH2,<br>TIM17_CH1N, TIM8_BKIN,<br>TSC_G5_IO4, EVENTOUT                                        | -                    |  |  |  |  |

| A7                        | 94      | 60     | 44     | BOOT0                                    |          | В             | -     | Boot memo                                                                                                                            | ry selection         |  |  |  |  |

| D5                        | 95      | 61     | 45     | PB8                                      | I/O      | FTf           | -     | I2C1_SCL, CAN_RX,<br>TIM16_CH1, TIM4_CH3,<br>TIM8_CH2, TIM1_BKIN,<br>TSC_SYNC, COMP1_OUT,<br>EVENTOUT                                | -                    |  |  |  |  |

| C6                        | 96      | 62     | 46     | PB9                                      | I/O      | FTf           | -     | I2C1_SDA, CAN_TX,<br>TIM17_CH1, TIM4_CH4,<br>TIM8_CH3, IR_OUT,<br>COMP2_OUT, EVENTOUT                                                | -                    |  |  |  |  |

| B7                        | 97      | -      | -      | PE0                                      | I/O      | FT            | (1)   | USART1_TX, TIM4_ETR,<br>TIM16_CH1, EVENTOUT                                                                                          |                      |  |  |  |  |

| A8                        | 98      | -      | -      | PE1                                      | I/O      | FT            | (1)   | USART1_RX, TIM17_CH1,<br>EVENTOUT                                                                                                    | -                    |  |  |  |  |

| C7                        | 99      | 63     | 47     | VSS                                      | S        | -             | -     | Gro                                                                                                                                  | und                  |  |  |  |  |

| A9,<br>A10,<br>B10,<br>B8 | 100     | 64     | 48     | VDD                                      | S        | -             | -     | Digital pov                                                                                                                          | ver supply           |  |  |  |  |

#### Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

5

|                          | Table 14. Alternate functions for port A (continued) |                      |              |                |              |              |                      |                   |               |               |              |          |      |            |              |

|--------------------------|------------------------------------------------------|----------------------|--------------|----------------|--------------|--------------|----------------------|-------------------|---------------|---------------|--------------|----------|------|------------|--------------|

| Port<br>&<br>Pin<br>Name | AF0                                                  | AF1                  | AF2          | AF3            | AF4          | AF5          | AF6                  | AF7               | AF8           | AF9           | AF10         | AF11     | AF12 | AF14       | AF15         |

| PA12                     | -                                                    | TIM16_<br>CH1        | -            | -              | -            | -            | TIM1_CH2N            | USART1_<br>RTS_DE | COMP2<br>_OUT | CAN_TX        | TIM4_<br>CH2 | TIM1_ETR | -    | USB_<br>DP | EVENT<br>OUT |

| PA13                     | SWDIO<br>-JTMS                                       | TIM16_<br>CH1N       | -            | TSC_<br>G4_IO3 | -            | IR_<br>OUT   | -                    | USART3_<br>CTS    | -             | -             | TIM4_<br>CH3 | -        | -    | -          | EVENT<br>OUT |

| PA14                     | SWCLK<br>-JTCK                                       | -                    | -            | TSC_<br>G4_IO4 | I2C1_<br>SDA | TIM8_<br>CH2 | TIM1_BKIN            | USART2_<br>TX     | -             | -             | -            | -        | -    | -          | EVENT<br>OUT |

| PA15                     | JTDI                                                 | TIM2_<br>CH1_<br>ETR | TIM8_<br>CH1 | -              | I2C1_<br>SCL | SPI1_<br>NSS | SPI3_NSS,<br>I2S3_WS | USART2_<br>RX     | -             | TIM1_<br>BKIN | -            | -        | -    | -          | EVENT<br>OUT |

## 6.3 Operating conditions

#### 6.3.1 General operating conditions

| Table 24. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Symbol             | Parameter                                                           | Conditions                                  | Min  | Max                   | Unit |  |  |  |

|--------------------|---------------------------------------------------------------------|---------------------------------------------|------|-----------------------|------|--|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                        | -                                           | 0    | 72                    |      |  |  |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                       | -                                           | 0    | 36                    | MHz  |  |  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                       | -                                           | 0    | 72                    |      |  |  |  |

| V <sub>DD</sub>    | Standard operating voltage                                          | -                                           | 2    | 3.6                   | V    |  |  |  |

| M                  | Analog operating voltage<br>(OPAMP and DAC not used)                | Must have a potential                       | 2    | 3.6                   | V    |  |  |  |

| V <sub>DDA</sub>   | Analog operating voltage (OPAMP and DAC used)                       | equal to or higher than<br>V <sub>DD</sub>  | 2.4  | 3.6                   | V    |  |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                                            | -                                           | 1.65 | 3.6                   | V    |  |  |  |

|                    |                                                                     | TC I/O                                      | -0.3 | V <sub>DD</sub> +0.3  |      |  |  |  |

| V                  | I/O input voltage                                                   | TTa I/O                                     | -0.3 | V <sub>DDA</sub> +0.3 | V    |  |  |  |

| V <sub>IN</sub>    | I/O Input voltage                                                   | FT and FTf I/O <sup>(1)</sup>               | -0.3 | 5.5                   | v    |  |  |  |

|                    |                                                                     | BOOT0                                       | 0    | 5.5                   |      |  |  |  |

|                    |                                                                     | WLCSP100                                    | -    | 500                   |      |  |  |  |

| р                  | Power dissipation at $T_A =$                                        | LQFP100                                     | -    | 488                   |      |  |  |  |

| $P_{D}$            | 85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(2)</sup> | LQFP64                                      | -    | 444                   | — mW |  |  |  |

|                    |                                                                     | LQFP48                                      | -    | 364                   |      |  |  |  |

|                    | Ambient temperature for 6 suffix version                            | Maximum power<br>dissipation                | -40  | 85                    | 5 °C |  |  |  |

| Та                 |                                                                     | Low-power dissipation <sup>(3)</sup>        | -40  | 105                   |      |  |  |  |

| IA                 | Ambient temperature for 7 suffix version                            | Maximum power<br>dissipation                | -40  | 105                   | °C   |  |  |  |

|                    |                                                                     | Low-power dissipation <sup>(3)</sup> –40 12 |      |                       |      |  |  |  |

| т.                 | lunction tomporature reaso                                          | 6 suffix version                            | -40  | 105                   | °C   |  |  |  |

| TJ                 | Junction temperature range                                          | 7 suffix version                            | -40  | 125                   | U    |  |  |  |

1. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.5: Thermal characteristics).

| Symbol                  | Para                                  | Para Conditions<br>meter <sup>(1)</sup>                                                       |       | Тур @V <sub>BAT</sub> |      |      |      |      | Max<br>@V <sub>BAT</sub> = 3.6 V <sup>(2)</sup> |      |                          | Unit |                           |      |

|-------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------|-------|-----------------------|------|------|------|------|-------------------------------------------------|------|--------------------------|------|---------------------------|------|

|                         | meter                                 |                                                                                               | 1.65V | 1.8V                  | 2V   | 2.4V | 2.7V | 3V   | 3.3V                                            | 3.6V | T <sub>A</sub> =<br>25°C |      | T <sub>A</sub> =<br>105°C | onne |

| I <sub>DD_VBAT</sub> do | Backup<br>domain<br>supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode"<br>lower<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '00'  | 0.48  | 0.50                  | 0.52 | 0.58 | 0.65 | 0.72 | 0.80                                            | 0.90 | 1.1                      | 1.5  | 2.0                       |      |

|                         |                                       | LSE & RTC<br>ON; "Xtal<br>mode"<br>higher<br>driving<br>capability;<br>LSEDRV[1:<br>0] = '11' | 0.83  | 0.86                  | 0.90 | 0.98 | 1.03 | 1.10 | 1.20                                            | 1.30 | 1.5                      | 2.2  | 2.9                       | μΑ   |

Table 34. Typical and maximum current consumption from  $V_{\text{BAT}}$  supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Guaranteed by characterization results.

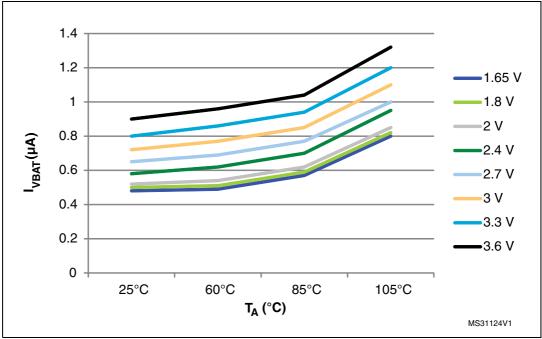

Figure 13. Typical V<sub>BAT</sub> current consumption (LSE and RTC ON/LSEDRV[1:0] = '00')

DocID023353 Rev 13

### 6.3.7 External clock source characteristics

#### High-speed external user clock generated from an external source

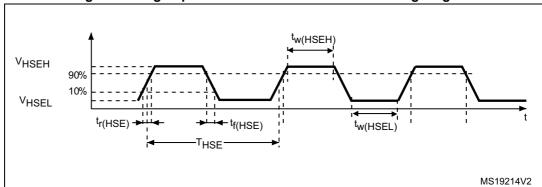

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 14*.

| Symbol                                       | Parameter                                           | Conditions | Min             | Тур | Max             | Unit |

|----------------------------------------------|-----------------------------------------------------|------------|-----------------|-----|-----------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency <sup>(1)</sup> |            | 1               | 8   | 32              | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage                 |            | $0.7V_{DD}$     | -   | V <sub>DD</sub> | v    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage                  | -          | V <sub>SS</sub> | -   | $0.3V_{DD}$     |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time <sup>(1)</sup>              |            | 15              | -   | -               | ne   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time <sup>(1)</sup>             |            | -               | -   | 20              | ns   |

1. Guaranteed by design.

#### Figure 14. High-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 42*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                          | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                  | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>                      | Feedback resistor           | -                                                  | -                  | 200 |                    | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                      | -                  | -   | 8.5                |      |

|                                     |                             | V <sub>DD</sub> =3.3 V, Rm= 30Ω<br>CL=10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                                     | HSE current consumption     | V <sub>DD</sub> =3.3 V, Rm= 45Ω<br>CL=10 pF@8 MHz  | -                  | 0.5 | -                  |      |

| I <sub>DD</sub>                     |                             | V <sub>DD</sub> =3.3 V, Rm= 30Ω<br>CL=5 pF@32 MHz  | -                  | 0.8 | -                  | mA   |

|                                     |                             | V <sub>DD</sub> =3.3 V, Rm= 30Ω<br>CL=10 pF@32 MHz | -                  | 1   | -                  |      |

|                                     |                             | V <sub>DD</sub> =3.3 V, Rm= 30Ω<br>CL=20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | Startup                                            | 10                 | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                      | -                  | 2   | -                  | ms   |

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design.

3. This consumption level occurs during the first 2/3 of the  $t_{SU(HSE)}$  startup time.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol Parameter |            | Conditions                                                                                                                  | Monitored       | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|------|

| Gymbol           | Farameter  | contaitions                                                                                                                 | frequency band  | 8/72 MHz                                       | Unit |

|                  |            | V 2 6 V T 25 °C                                                                                                             | 0.1 to 30 MHz   | 7                                              |      |

| 6                | Dook lovel | ak level $V_{DD} = 3.6 \text{ V}, \text{ T}_{A} = 25 ^{\circ}\text{C},$<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 30 to 130 MHz   | 20                                             | dBµV |

| S <sub>EMI</sub> | reak level |                                                                                                                             | 130 MHz to 1GHz | 27                                             |      |

|                  |            |                                                                                                                             | SAE EMI Level   | 4                                              | -    |

Table 50. EMI characteristics

#### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1 standard.

| Symbol                | Ratings                                                  | Conditions                                                  |                                | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model) | $T_A = +25 \ ^{\circ}C$ , conforming to JESD22-A114         |                                | 2     | 2000                            |      |

|                       | Electrostatic                                            |                                                             | WLCSP100<br>package            | 3     | 250                             | V    |

| V <sub>ESD(CDM)</sub> | discharge voltage<br>(charge device model)               | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | Packages<br>except<br>WLCSP100 | 4     | 500                             |      |

Table 51. ESD absolute maximum ratings

1. Guaranteed by characterization results.

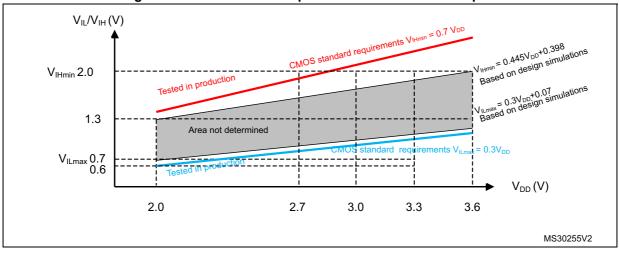

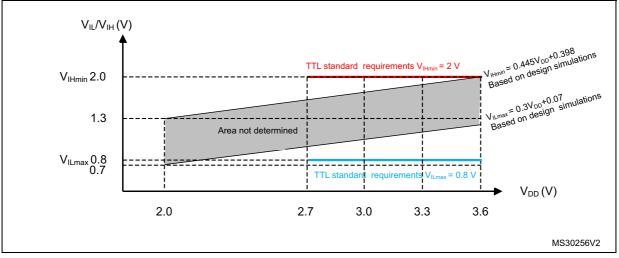

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 19* and *Figure 20* for standard I/Os.

Figure 19. TC and TTa I/O input characteristics - CMOS port

#### Figure 20. TC and TTa I/O input characteristics - TTL port

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 22*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 22*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*. All I/Os (FT, TTa and TC unless otherwise specified) are CMOS and TTL compliant.

| Symbol                               | Parameter                                               | Conditions                                                  | Min                  | Max | Unit |

|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(1)</sup>       | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>       | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup>    | Output high level voltage for an I/O pin                | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OLFM+</sub> <sup>(1)(4)</sup> | Output low level voltage for an FTf I/O pin in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 |      |

| Table 55. | Output voltage | e characteristics |

|-----------|----------------|-------------------|

|           | output voltage |                   |

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 22* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 22* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Data based on design simulation.

## 6.3.18 ADC characteristics

Unless otherwise specified, the parameters given in *Table 68* to *Table 70* are guaranteed by design, with conditions summarized in *Table 24*.

| Symbol            | Parameter                        | Conditions                     | Min   | Тур                          | Max              | Unit |     |  |

|-------------------|----------------------------------|--------------------------------|-------|------------------------------|------------------|------|-----|--|

| V <sub>DDA</sub>  | Analog supply voltage for ADC    | -                              | 2     | -                            | 3.6              | V    |     |  |

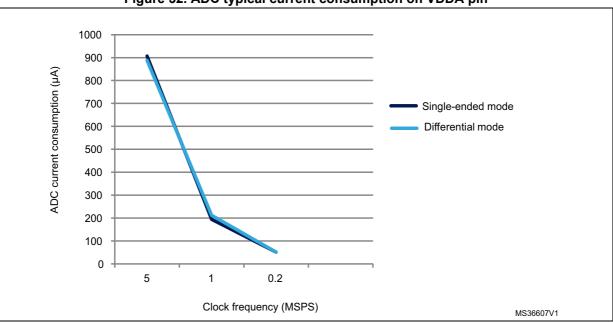

|                   |                                  | Single-ended mode,<br>5 MSPS   | -     | 907                          | 1033.0           |      |     |  |

|                   |                                  | Single-ended mode,<br>1 MSPS   | -     | 194                          | 285.5            |      |     |  |

|                   | ADC current consumption on VDDA  | Single-ended mode,<br>200 KSPS | -     | 51.5                         | 70               | μΑ   |     |  |

| I <sub>DDA</sub>  | (see <i>Figure 32</i> )          | Differential mode,<br>5 MSPS   | -     | 887.5                        | 1009             | _ μΑ |     |  |

|                   | -                                |                                | Dif   | Differential mode,<br>1 MSPS | -                | 212  | 285 |  |

|                   |                                  | Differential mode,<br>200 KSPS | -     | 51                           | 69.5             |      |     |  |

| V <sub>REF+</sub> | Positive reference voltage       | -                              | 2     | -                            | V <sub>DDA</sub> | V    |     |  |

| V <sub>REF-</sub> | Negative reference voltage       | -                              | -     | 0                            | -                | v    |     |  |

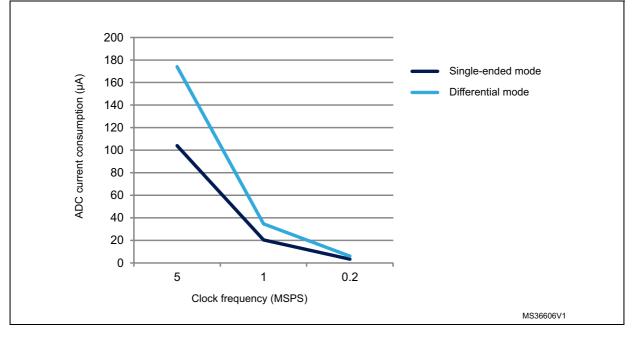

|                   |                                  | Single-ended mode,<br>5 MSPS   | -     | 104                          | 139              |      |     |  |

|                   |                                  | Single-ended mode,<br>1 MSPS   | -     | 20.4                         | 37               |      |     |  |

| I                 | ADC current consumption on VREF+ | Single-ended mode,<br>200 KSPS | - 3.3 |                              | 11.3             | μΑ   |     |  |

| I <sub>REF</sub>  | pin<br>(see <i>Figure 33</i> )   | Differential mode,<br>5 MSPS   | -     | 174                          | 235              |      |     |  |

|                   |                                  | Differential mode,<br>1 MSPS   | -     | 34.6                         | 52.6             |      |     |  |

|                   |                                  | Differential mode,<br>200 KSPS | -     | 6                            | 13.6             |      |     |  |

#### Table 68. ADC characteristics

103/148

DocID023353 Rev 13

Figure 32. ADC typical current consumption on VDDA pin

#### Figure 33. ADC typical current consumption on VREF+ pin

| Symbol | Parameter             | С                       | onditions                 |                     | Min <sup>(4)</sup>  | Max <sup>(4)</sup> | Unit |

|--------|-----------------------|-------------------------|---------------------------|---------------------|---------------------|--------------------|------|

|        |                       |                         | Single                    | Fast channel 5.1 Ms | -                   | ±6.5               |      |

|        | Total                 |                         | Ended                     | Slow channel 4.8 Ms | -                   | ±6.5               |      |

| ET     | unadjusted<br>error   |                         | Differential              | Fast channel 5.1 Ms | -                   | <u>+</u> 4         |      |

|        |                       |                         | Dillerential              | Slow channel 4.8 Ms | -                   | <u>+</u> 4         |      |

|        |                       |                         | Single                    | Fast channel 5.1 Ms | -                   | ±3                 |      |

| EO     | Offset error          |                         | Ended                     | Slow channel 4.8 Ms | -                   | ±3                 |      |

| LO     | Olisetenoi            |                         | Differential              | Fast channel 5.1 Ms | -                   | <u>+2</u>          |      |

|        |                       |                         | Dillerential              | Slow channel 4.8 Ms | -                   | <u>+2</u>          |      |

|        |                       |                         | Single                    | Fast channel 5.1 Ms | -                   | ±6                 |      |

| EG     | Gain error            |                         | Ended                     | Slow channel 4.8 Ms | -                   | ±6                 | LSB  |

| LG     |                       |                         | ADC clock freq. ≤ 72 MHz, | Differential        | Fast channel 5.1 Ms | -                  | ±3   |

|        |                       | Sampling freq. ≤ 5 Msps | Billereniadi              | Slow channel 4.8 Ms | -                   | ±3                 | -    |

|        |                       | inearity -              | Single                    | Fast channel 5.1 Ms | -                   | ±1.5               |      |

| ED     | Differential          |                         | Ended                     | Slow channel 4.8 Ms | -                   | ±1.5               |      |

|        | error                 |                         | Differential              | Fast channel 5.1 Ms | -                   | ±1.5               | 1    |

|        |                       |                         | Differential              | Slow channel 4.8 Ms | -                   | ±1.5               |      |

|        |                       |                         | Single                    | Fast channel 5.1 Ms | -                   | <u>+2</u>          | -    |

| EL     | Integral<br>linearity |                         | Ended                     | Slow channel 4.8 Ms | -                   | ±3                 |      |

|        | error                 |                         | Differential              | Fast channel 5.1 Ms | -                   | <u>+2</u>          |      |

|        |                       |                         | Dillerential              | Slow channel 4.8 Ms | -                   | <u>+2</u>          |      |

|        |                       |                         | Single                    | Fast channel 5.1 Ms | 10.4                | -                  |      |

| ENOB   | Effective number of   |                         | Ended                     | Slow channel 4.8 Ms | 10.2                | -                  | -:+- |

| (5)    | bits                  |                         | Differential              | Fast channel 5.1 Ms | 10.8                | -                  | bits |

|        |                       |                         | Differential              | Slow channel 4.8 Ms | 10.8                | -                  |      |

## Table 71. ADC accuracy, 100-pin packages<sup>(1)(2)(3)</sup>

| Symbol             | Parameter         | C                                                                                                    | Min<br>(3)   | Тур                 | Max<br>(3) | Unit |     |    |

|--------------------|-------------------|------------------------------------------------------------------------------------------------------|--------------|---------------------|------------|------|-----|----|

|                    |                   |                                                                                                      | Single ended | Fast channel 5.1 Ms | 66         | 67   | -   |    |

| SNR <sup>(4)</sup> | Signal-to-        |                                                                                                      | Single ended | Slow channel 4.8 Ms | 66         | 67   | -   |    |

| no                 | noise ratio       | hoise ratio ADC clock freq. $\leq$ 72 MHz<br>Sampling freq $\leq$ 5 Msps<br>V <sub>DDA</sub> = 3.3 V | Differential | Fast channel 5.1 Ms | 69         | 70   | -   |    |

|                    |                   |                                                                                                      |              | Slow channel 4.8 Ms | 69         | 70   | -   | dB |

|                    |                   | v <sub>DDA</sub> – 3.3 v<br>25°C                                                                     | Single ended | Fast channel 5.1 Ms | -          | -80  | -80 | uВ |

| THD <sup>(4)</sup> | Total<br>harmonic | 04-pill package                                                                                      |              | Slow channel 4.8 Ms | -          | -78  | -77 |    |

| י יעחו             | distortion        |                                                                                                      | Differential | Fast channel 5.1 Ms | -          | -83  | -82 |    |

|                    |                   |                                                                                                      | Differential | Slow channel 4.8 Ms | -          | -81  | -80 |    |

#### Table 72. ADC accuracy - limited test conditions, 64-pin packages<sup>(1)(2)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

4. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

## 6.3.20 Comparator characteristics

| Symbol                   | Parameter                                                         | Conditions                                                        |                          | Min | Тур | Мах              | Unit      |

|--------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|-----|-----|------------------|-----------|

| V <sub>DDA</sub>         | Analog supply voltage                                             | -                                                                 |                          | 2   | -   | 3.6              |           |

| V <sub>IN</sub>          | Comparator input voltage range                                    | -                                                                 |                          | 0   | -   | V <sub>DDA</sub> | V         |

| V <sub>BG</sub>          | Scaler input voltage                                              | -                                                                 |                          | -   | 1.2 | -                |           |

| V <sub>SC</sub>          | Scaler offset voltage                                             | -                                                                 |                          | -   | ±5  | ±10              | mV        |

| t <sub>S_SC</sub>        | V <sub>REFINT</sub> scaler startup<br>time from power down        | First V <sub>REFINT</sub> scaler activation after device power on |                          | -   | -   | 1 <sup>(2)</sup> | s         |

|                          |                                                                   | Next activations                                                  |                          | -   | -   | 0.2              | ms        |

| t <sub>START</sub>       | Comparator startup time                                           | Startup time to reach propagation delay specification             |                          | -   | -   | 60               | μs        |

| t <sub>D</sub>           | Propagation delay for<br>200 mV step with 100 mV<br>overdrive     | Ultra-low-power mode                                              |                          | -   | 2   | 4.5              | μs        |

|                          |                                                                   | Low-power mode                                                    |                          | -   | 0.7 | 1.5              |           |

|                          |                                                                   | Medium power mode                                                 |                          | -   | 0.3 | 0.6              |           |

|                          |                                                                   | High speed mode                                                   | $V_{DDA} \ge 2.7 V$      | -   | 50  | 100              | - ns      |

|                          |                                                                   |                                                                   | V <sub>DDA</sub> < 2.7 V | -   | 100 | 240              |           |

|                          | Propagation delay for full<br>range step with 100 mV<br>overdrive | Ultra-low-power mode                                              |                          | -   | 2   | 7                | μs        |