Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |

| Number of I/O              | 77                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 40K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 32x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA, WLCSP                                                        |

| Supplier Device Package    | 100-WLCSP (4.2x4.7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f303vcy6tr |

#### 3.17.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.17.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.17.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 3.18 Real-time clock (RTC) and backup registers

The RTC and the 16 backup registers are supplied through a switch that takes power from either the  $V_{DD}$  supply when present or the  $V_{BAT}$  pin. The backup registers are sixteen 32-bit registers used to store 64 bytes of user application data when  $V_{DD}$  power is not present.

They are not reset by a system or power reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Automatic correction for 28, 29 (leap year), 30 and 31 days of the month.

- Two programmable alarms with wake up from Stop and Standby mode capability.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stopand Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

# 3.22 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I2S)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) supporting four different audio standards can operate as master or slave at half-duplex and full duplex communication modes. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by 8-bit programmable linear prescaler. When operating in master mode it can output a clock for an external audio component at 256 times the sampling frequency.

Refer to *Table 9* for the features available in SPI1, SPI2 and SPI3.

SPI features<sup>(1)</sup> SPI1 SPI2 SPI3 Hardware CRC calculation Χ Х Х Rx/Tx FIFO Χ Χ Χ Χ NSS pulse mode Χ Х I2S mode Χ Χ TI mode Χ Х Х

Table 9. STM32F303xB/STM32F303xC SPI/I2S implementation

## 3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

## 3.24 Universal serial bus (USB)

The STM32F303xB/STM32F303xC devices embed an USB device peripheral compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator). The USB has a dedicated 512-bytes SRAM memory for data transmission and reception.

<sup>1.</sup> X = supported.

Table 10. Capacitive sensing GPIOs available on STM32F303xB/STM32F303xC devices

| Group | Capacitive sensing signal name | Pin<br>name | Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|-------------|-------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |       | TSC_G5_IO1                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5     | TSC_G5_IO2                     | PB4         |

| '     | TSC_G1_IO3                     | PA2         | 3     | TSC_G5_IO3                     | PB6         |

|       | TSC_G1_IO4                     | PA3         |       | TSC_G5_IO4                     | PB7         |

|       | TSC_G2_IO1                     | PA4         |       | TSC_G6_IO1                     | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6     | TSC_G6_IO2                     | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0     | TSC_G6_IO3                     | PB13        |

|       | TSC_G2_IO4                     | PA7         |       | TSC_G6_IO4                     | PB14        |

|       | TSC_G3_IO1                     | PC5         |       | TSC_G7_IO1                     | PE2         |

| 3     | TSC_G3_IO2                     | PB0         | 7     | TSC_G7_IO2                     | PE3         |

| 3     | TSC_G3_IO3                     | PB1         | /     | TSC_G7_IO3                     | PE4         |

|       | TSC_G3_IO4                     | PB2         |       | TSC_G7_IO4                     | PE5         |

|       | TSC_G4_IO1                     | PA9         |       | TSC_G8_IO1                     | PD12        |

| 4     | TSC_G4_IO2                     | PA10        | 8     | TSC_G8_IO2                     | PD13        |

| 7     | TSC_G4_IO3                     | PA13        |       | TSC_G8_IO3                     | PD14        |

|       | TSC_G4_IO4                     | PA14        |       | TSC_G8_IO4                     | PD15        |

Table 11. No. of capacitive sensing channels available on STM32F303xB/STM32F303xC devices

| Analog I/O group                      | Number      | of capacitive sensing c | hannels     |

|---------------------------------------|-------------|-------------------------|-------------|

| Analog I/O group                      | STM32F303Vx | STM32F303Rx             | STM32F303Cx |

| G1                                    | 3           | 3                       | 3           |

| G2                                    | 3           | 3                       | 3           |

| G3                                    | 3           | 3                       | 2           |

| G4                                    | 3           | 3                       | 3           |

| G5                                    | 3           | 3                       | 3           |

| G6                                    | 3           | 3                       | 3           |

| G7                                    | 3           | 0                       | 0           |

| G8                                    | 3           | 0                       | 0           |

| Number of capacitive sensing channels | 24          | 18                      | 17          |

## 3.27 Development support

### 3.27.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 3.27.2 Embedded trace macrocell™

The ARM embedded trace macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F303xB/STM32F303xC through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using a high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

Table 13. STM32F303xB/STM32F303xC pin definitions (continued)

|          | Pin nu  | umber  |        | 13. 3114132                                    |          |               |       | Pin functions                                                                         |                                                         |  |  |  |

|----------|---------|--------|--------|------------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| WLCSP100 | LQFP100 | LQFP64 | LQFP48 | Pin name<br>(function<br>after<br>reset)       | Pin type | I/O structure | Notes | Alternate functions                                                                   | Additional functions                                    |  |  |  |

| С9       | 7       | 2      | 2      | PC13 <sup>(2)</sup>                            | I/O      | TC            | -     | TIM1_CH1N                                                                             | WKUP2, RTC_TAMP1,<br>RTC_TS, RTC_OUT                    |  |  |  |

| C10      | 8       | 3      | 3      | PC14 <sup>(2)</sup><br>OSC32_IN<br>(PC14)      | I/O      | тс            | 1     | -                                                                                     | OSC32_IN                                                |  |  |  |

| D9       | 9       | 4      | 4      | PC15 <sup>(2)</sup><br>OSC32_<br>OUT<br>(PC15) | I/O      | тс            | -     | -                                                                                     | OSC32_OUT                                               |  |  |  |

| D10      | 10      | -      | -      | PF9                                            | I/O      | FT            | (1)   | TIM15_CH1, SPI2_SCK,<br>EVENTOUT                                                      | -                                                       |  |  |  |

| E10      | 11      | -      | -      | PF10                                           | I/O      | FT            | (1)   | TIM15_CH2, SPI2_SCK,<br>EVENTOUT                                                      | -                                                       |  |  |  |

| F10      | 12      | 5      | 5      | PF0-<br>OSC_IN<br>(PF0)                        | I/O      | FTf           | -     | TIM1_CH3N, I2C2_SDA,                                                                  | OSC_IN                                                  |  |  |  |

| F9       | 13      | 6      | 6      | PF1-<br>OSC_OUT<br>(PF1)                       | I/O      | FTf           | 1     | 12C2_SCL                                                                              | OSC_OUT                                                 |  |  |  |

| E9       | 14      | 7      | 7      | NRST                                           | I/O      | RS<br>T       |       | Device reset input / intern                                                           | al reset output (active low)                            |  |  |  |

| G10      | 15      | 8      | -      | PC0                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN6, COMP7_INM                                    |  |  |  |

| G9       | 16      | 9      | -      | PC1                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN7, COMP7_INP                                    |  |  |  |

| G8       | 17      | 10     | -      | PC2                                            | I/O      | TTa           | (1)   | COMP7_OUT, EVENTOUT                                                                   | ADC12_IN8                                               |  |  |  |

| H10      | 18      | 11     | -      | PC3                                            | I/O      | TTa           |       | TIM1_BKIN2, EVENTOUT                                                                  | ADC12_IN9                                               |  |  |  |

| E8       | 19      | -      | -      | PF2                                            | I/O      | TTa           | (1)   | EVENTOUT                                                                              | ADC12_IN10                                              |  |  |  |

| H8       | 20      | 12     | 8      | VSSA/<br>VREF-                                 | S        | -             | -     | Analog ground/Nega                                                                    | tive reference voltage                                  |  |  |  |

| J8       | 21      | -      | -      | VREF+ <sup>(3)</sup>                           | S        | -             | -     | Positive refe                                                                         | rence voltage                                           |  |  |  |

| J10      | 22      | -      | -      | VDDA                                           | S        | -             | -     | Analog po                                                                             | wer supply                                              |  |  |  |

| _        | -       | 13     | 9      | VDDA/<br>VREF+                                 | S        | -             | _     | Analog power supply/Positive reference voltage                                        |                                                         |  |  |  |

| H9       | 23      | 14     | 10     | PA0                                            | I/O      | TTa           | (4)   | USART2_CTS,<br>TIM2_CH1_ETR,TIM8_BKIN,<br>TIM8_ETR,TSC_G1_IO1,<br>COMP1_OUT, EVENTOUT | ADC1_IN1, COMP1_INM,<br>RTC_ TAMP2, WKUP1,<br>COMP7_INP |  |  |  |

- Function availability depends on the chosen device. When using the small packages (48 and 64 pin packages), the GPIO pins which are not present on these packages, must not be configured in analog mode.

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch sinks only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF

These GPIOs must not be used as current sources (e.g. to drive an LED).

After the first backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the Backup registers which is not reset by the main reset. For details on how to manage these GPIOs, refer to the Battery backup domain and BKP register description sections in the RM0316 reference manual.

- The VREF+ functionality is available only on the 100 pin package. On the 64-pin and 48-pin packages, the VREF+ is internally connected to VDDA.

- 5. These GPIOs offer a reduced touch sensing sensitivity. It is thus recommended to use them as sampling capacitor I/O.

Table 19. Alternate functions for port F

| Port &<br>Pin Name | AF1      | AF2       | AF3       | AF4      | AF5      | AF6       | AF7           |

|--------------------|----------|-----------|-----------|----------|----------|-----------|---------------|

| PF0                | -        | -         | -         | I2C2_SDA | -        | TIM1_CH3N | -             |

| PF1                | -        | -         | -         | I2C2_SCL | -        | -         | -             |

| PF2                | EVENTOUT | -         | -         | -        | -        | -         | -             |

| PF4                | EVENTOUT | COMP1_OUT | -         | -        | -        | -         | -             |

| PF6                | EVENTOUT | TIM4_CH4  | -         | I2C2_SCL | -        | -         | USART3_RTS_DE |

| PF9                | EVENTOUT | -         | TIM15_CH1 | -        | SPI2_SCK | -         | -             |

| PF10               | EVENTOUT | -         | TIM15_CH2 | -        | SPI2_SCK | -         | -             |

Table 20. STM32F303xB/STM32F303xC memory map, peripheral register boundary addresses (continued)

| Bus  | Boundary address          | Size<br>(bytes) | Peripheral         |

|------|---------------------------|-----------------|--------------------|

|      | 0x4000 8000 - 0x4000 FFFF | 32 K            | Reserved           |

|      | 0x4000 7800 - 0x4000 7FFF | 2 K             | Reserved           |

|      | 0x4000 7400 - 0x4000 77FF | 1 K             | DAC (dual)         |

|      | 0x4000 7000 - 0x4000 73FF | 1 K             | PWR                |

|      | 0x4000 6800 - 0x4000 6FFF | 2 K             | Reserved           |

|      | 0x4000 6400 - 0x4000 67FF | 1 K             | bxCAN              |

|      | 0x4000 6000 - 0x4000 63FF | 1 K             | USB SRAM 512 bytes |

|      | 0x4000 5C00 - 0x4000 5FFF | 1 K             | USB device FS      |

|      | 0x4000 5800 - 0x4000 5BFF | 1 K             | I2C2               |

|      | 0x4000 5400 - 0x4000 57FF | 1 K             | I2C1               |

|      | 0x4000 5000 - 0x4000 53FF | 1 K             | UART5              |

|      | 0x4000 4C00 - 0x4000 4FFF | 1 K             | UART4              |

|      | 0x4000 4800 - 0x4000 4BFF | 1 K             | USART3             |

|      | 0x4000 4400 - 0x4000 47FF | 1 K             | USART2             |

| APB1 | 0x4000 4000 - 0x4000 43FF | 1 K             | I2S3ext            |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | 1 K             | SPI3/I2S3          |

|      | 0x4000 3800 - 0x4000 3BFF | 1 K             | SPI2/I2S2          |

|      | 0x4000 3400 - 0x4000 37FF | 1 K             | I2S2ext            |

|      | 0x4000 3000 - 0x4000 33FF | 1 K             | IWDG               |

|      | 0x4000 2C00 - 0x4000 2FFF | 1 K             | WWDG               |

|      | 0x4000 2800 - 0x4000 2BFF | 1 K             | RTC                |

|      | 0x4000 1800 - 0x4000 27FF | 4 K             | Reserved           |

|      | 0x4000 1400 - 0x4000 17FF | 1 K             | TIM7               |

|      | 0x4000 1000 - 0x4000 13FF | 1 K             | TIM6               |

|      | 0x4000 0C00 - 0x4000 0FFF | 1 K             | Reserved           |

|      | 0x4000 0800 - 0x4000 0BFF | 1 K             | TIM4               |

|      | 0x4000 0400 - 0x4000 07FF | 1 K             | TIM3               |

|      | 0x4000 0000 - 0x4000 03FF | 1 K             | TIM2               |

#### 6.1.6 Power supply scheme

Backup circuitry Power (LSE, RTC, switch Wakeup logic, Backup registers) OUT GP I/Os I/O logic Kernel logic (CPU, digital & memories)  $4\;x\;V_{DD}$ Regulator 4 x 100 nF  $4 \times V_{SS}$ + 1 x 4.7 µF  $V_{\text{DDA}}$  $V_{DDA}$ V<sub>REF+</sub> Analog: RCs, 10 nF ADC/DAC PLL,comparators, OPAMP, + 1 µF  $V_{REF}$ MS19875V5

Figure 11. Power supply scheme

Dotted lines represent the internal connections on low pin count packages, joining the dedicated supply pins.

#### Caution:

Each power supply pair ( $V_{DD}/V_{SS}$ ,  $V_{DDA}/V_{SSA}$  etc..) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

577

#### 6.1.7 Current consumption measurement

JDD\_VBAT

VBAT

VDD

VDD

VDD

VDD

MS19213V1

Figure 12. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 21: Voltage characteristics*, *Table 22: Current characteristics*, and *Table 23: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Table 21. Voltage characterist | ics <sup>(1)</sup> |

|--------------------------------|--------------------|

| Datings                        |                    |

| Symbol                                             | Ratings                                                                                                        | Min                  | Max                   | Unit |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                   | External main supply voltage (including $V_{DDA,}$ $V_{BAT}$ and $V_{DD}$ )                                    | -0.3                 | 4.0                   |      |

| V <sub>DD</sub> –V <sub>DDA</sub>                  | Allowed voltage difference for V <sub>DD</sub> > V <sub>DDA</sub>                                              | -                    | 0.4                   |      |

| V <sub>REF+</sub> -V <sub>DDA</sub> <sup>(2)</sup> | Allowed voltage difference for V <sub>REF+</sub> > V <sub>DDA</sub>                                            | -                    | 0.4                   |      |

|                                                    | Input voltage on FT and FTf pins                                                                               | V <sub>SS</sub> -0.3 | V <sub>DD</sub> + 4.0 | V    |

| V <sub>IN</sub> <sup>(3)</sup>                     | Input voltage on TTa pins                                                                                      | V <sub>SS</sub> -0.3 | 4.0                   |      |

| VIN.                                               | Input voltage on any other pin                                                                                 | V <sub>SS</sub> -0.3 | 4.0                   |      |

|                                                    | Input voltage on Boot0 pin                                                                                     | 0                    | 9                     |      |

| $ \Delta V_{DDx} $                                 | Variations between different V <sub>DD</sub> power pins                                                        | -                    | 50                    | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub>                  | Variations between all the different ground pins <sup>(4)</sup>                                                | -                    | 50                    | IIIV |

| V <sub>ESD(HBM)</sub>                              | Electrostatic discharge voltage (human body model)  see Section 6.3.12: Electrical sensitivity characteristics |                      |                       |      |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range. The following relationship must be respected between V<sub>DDA</sub> and V<sub>DD</sub>: V<sub>DDA</sub> must power on before or at the same time as V<sub>DD</sub> in the power up sequence. V<sub>DDA</sub> must be greater than or equal to V<sub>DD</sub>.

The parameters given in *Table 30* to *Table 34* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24*.

Table 30. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6V

|                 |                      |                         |                   |        | periphe                             |       | abled               |      | periphe             |                                      |                     |      |  |

|-----------------|----------------------|-------------------------|-------------------|--------|-------------------------------------|-------|---------------------|------|---------------------|--------------------------------------|---------------------|------|--|

| Symbol          | Parameter            | Conditions              | f <sub>HCLK</sub> | T      | Max @ T <sub>A</sub> <sup>(1)</sup> |       |                     |      |                     | /lax @ T <sub>A</sub> <sup>(1)</sup> |                     | Unit |  |

|                 |                      |                         |                   | Тур    | 25 °C                               | 85 °C | 105 °C              | Тур  | 25 °C               | 85 °C                                | 105 °C              |      |  |

|                 |                      |                         | 72 MHz            | 61.2   | 65.8                                | 67.6  | 68.5                | 27.8 | 30.3                | 30.7                                 | 31.5                |      |  |

|                 |                      |                         | 64 MHz            | 54.7   | 59.1                                | 60.2  | 61.1                | 24.6 | 27.2                | 27.6                                 | 28.3                |      |  |

|                 |                      | External                | 48 MHz            | 41.7   | 45.1                                | 46.2  | 47.2                | 19.2 | 21.1                | 21.4                                 | 21.8                |      |  |

|                 |                      | clock (HSE              | 32 MHz            | 28.1   | 31.5                                | 32.5  | 32.7                | 12.9 | 14.6                | 14.8                                 | 15.3                |      |  |

|                 | Supply               | bypass)                 | 24 MHz            | 21.4   | 23.7                                | 24.4  | 25.2                | 10.0 | 11.4                | 11.4                                 | 12.1                |      |  |

|                 | current in Run mode, |                         | 8 MHz             | 7.4    | 8.4                                 | 8.6   | 9.4                 | 3.6  | 4.1                 | 4.4                                  | 5.0                 |      |  |

|                 | executing            |                         | 1 MHz             | 1.3    | 1.6                                 | 1.8   | 2.6                 | 0.8  | 1.0                 | 1.2                                  | 2.1                 |      |  |

|                 | from Flash           |                         | 64 MHz            | 49.7   | 54.4                                | 55.4  | 56.3                | 24.5 | 27.2                | 27.4                                 | 28.1                |      |  |

|                 |                      | Internal<br>clock (HSI) |                   | 48 MHz | 37.9                                | 42.2  | 43.0                | 43.5 | 18.9                | 21.4                                 | 21.5                | 21.6 |  |

|                 |                      |                         | 32 MHz            | 25.8   | 29.2                                | 29.2  | 30.0                | 12.7 | 14.2                | 14.6                                 | 15.2                |      |  |

|                 |                      |                         | 24 MHz            | 19.7   | 22.3                                | 22.6  | 23.2                | 6.7  | 7.7                 | 7.9                                  | 8.5                 |      |  |

|                 |                      |                         | 8 MHz             | 6.9    | 7.8                                 | 8.3   | 8.8                 | 3.5  | 4.0                 | 4.4                                  | 5.0                 | mA   |  |

| I <sub>DD</sub> |                      |                         | 72 MHz            | 60.8   | 66.2 <sup>(2)</sup>                 | 69.7  | 70.4 <sup>(2)</sup> | 27.4 | 31.7 <sup>(2)</sup> | 32.2                                 | 32.5 <sup>(2)</sup> | IIIA |  |

|                 |                      |                         | 64 MHz            | 54.3   | 59.1                                | 62.2  | 63.3                | 24.3 | 28.3                | 28.7                                 | 28.8                |      |  |

|                 |                      | External                | 48 MHz            | 41.0   | 45.6                                | 47.3  | 47.9                | 18.3 | 21.6                | 21.9                                 | 22.1                |      |  |

|                 |                      | clock (HSE              | 32 MHz            | 27.6   | 32.4                                | 32.4  | 32.9                | 12.3 | 15.0                | 15.2                                 | 15.4                |      |  |

|                 | Supply               | bypass)                 | 24 MHz            | 20.8   | 23.9                                | 24.3  | 25.0                | 9.3  | 11.3                | 11.4                                 | 12.0                |      |  |

|                 | current in Run mode, |                         | 8 MHz             | 6.9    | 7.8                                 | 8.7   | 9.0                 | 3.1  | 3.7                 | 4.2                                  | 4.9                 |      |  |

|                 | executing            |                         | 1 MHz             | 0.9    | 1.2                                 | 1.5   | 2.3                 | 0.4  | 0.6                 | 1.0                                  | 1.8                 |      |  |

|                 | from RAM             |                         | 64 MHz            | 49.2   | 53.9                                | 55.2  | 57.4                | 23.9 | 27.8                | 28.2                                 | 28.4                |      |  |

|                 |                      |                         | 48 MHz            | 37.3   | 40.8                                | 41.4  | 44.1                | 18.2 | 21.0                | 21.6                                 | 21.9                |      |  |

|                 |                      | Internal clock (HSI)    | 32 MHz            | 25.1   | 27.6                                | 29.1  | 30.1                | 12.0 | 14.0                | 14.5                                 | 15.1                |      |  |

|                 |                      |                         | 24 MHz            | 19.0   | 21.6                                | 22.1  | 22.9                | 6.3  | 7.2                 | 7.7                                  | 8.1                 |      |  |

|                 |                      |                         | 8 MHz             | 6.4    | 7.3                                 | 7.9   | 8.4                 | 3.0  | 3.5                 | 4.0                                  | 4.7                 |      |  |

Table 37. Switching output I/O current consumption

| Symbol          | Parameter               | Conditions <sup>(1)</sup>          | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit |

|-----------------|-------------------------|------------------------------------|----------------------------------------------|------|------|

|                 |                         |                                    | 2 MHz                                        | 0.90 |      |

|                 |                         |                                    | 4 MHz                                        | 0.93 |      |

|                 |                         | $V_{DD} = 3.3 V$ $C_{ext} = 0 pF$  | 8 MHz                                        | 1.16 |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$    | 18 MHz                                       | 1.60 |      |

|                 |                         |                                    | 36 MHz                                       | 2.51 |      |

|                 |                         |                                    | 48 MHz                                       | 2.97 |      |

|                 |                         | 2 MHz 0.93                         | 0.93                                         |      |      |

|                 |                         |                                    | 4 MHz                                        | 1.06 |      |

|                 |                         | $V_{DD}$ = 3.3 V $C_{ext}$ = 10 pF | 8 MHz                                        | 1.47 |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$    | 18 MHz                                       | 2.26 | mA   |

|                 |                         |                                    | 36 MHz                                       | 3.39 |      |

|                 |                         |                                    | 48 MHz                                       | 5.99 |      |

|                 |                         |                                    | 2 MHz                                        | 1.03 |      |

| I <sub>SW</sub> | I/O current consumption | V <sub>DD</sub> = 3.3 V            | 4 MHz                                        | 1.30 |      |

|                 | ·                       | $C_{ext}$ = 22 pF                  | 8 MHz                                        | 1.79 |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$    | 18 MHz                                       | 3.01 |      |

|                 |                         |                                    | 36 MHz                                       | 5.99 |      |

|                 |                         |                                    | 2 MHz                                        | 1.10 |      |

|                 |                         | V <sub>DD</sub> = 3.3 V            | 4 MHz                                        | 1.31 | 7    |

|                 |                         | C <sub>ext</sub> = 33 pF           | 8 MHz                                        | 2.06 |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$    | 18 MHz                                       | 3.47 |      |

|                 |                         |                                    | 36 MHz 8.35                                  |      |      |

|                 |                         |                                    | 2 MHz                                        | 1.20 |      |

|                 |                         | V <sub>DD</sub> = 3.3 V            | 4 MHz                                        | 1.54 |      |

|                 |                         | $C_{ext} = 47 pF$                  | 8 MHz                                        | 2.46 |      |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$    | 18 MHz                                       | 4.51 |      |

|                 |                         |                                    | 36 MHz                                       | 9.98 |      |

<sup>1.</sup> CS = 5 pF (estimated value).

#### On-chip peripheral current consumption

The MCU is placed under the following conditions:

- all I/O pins are in analog input configuration

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature at 25°C and V<sub>DD</sub> = V<sub>DDA</sub> = 3.3 V.

Table 38. Peripheral current consumption

|                 | Typical consumption <sup>(1)</sup> | l lmi4   |

|-----------------|------------------------------------|----------|

| Peripheral      | I <sub>DD</sub>                    | Unit     |

| BusMatrix (2)   | 12.6                               |          |

| DMA1            | 7.6                                |          |

| DMA2            | 6.1                                |          |

| CRC             | 2.1                                |          |

| GPIOA           | 10.0                               |          |

| GPIOB           | 10.3                               |          |

| GPIOC           | 2.2                                |          |

| GPIOD           | 8.8                                |          |

| GPIOE           | 3.3                                |          |

| GPIOF           | 3.0                                |          |

| TSC             | 5.5                                |          |

| ADC1&2          | 17.3                               |          |

| ADC3&4          | 18.8                               | μΑ/MHz   |

| APB2-Bridge (3) | 3.6                                | μΑνινιπΣ |

| SYSCFG          | 7.3                                |          |

| TIM1            | 40.0                               |          |

| SPI1            | 8.8                                |          |

| TIM8            | 36.4                               |          |

| USART1          | 23.3                               |          |

| TIM15           | 17.1                               |          |

| TIM16           | 10.1                               |          |

| TIM17           | 11.0                               |          |

| APB1-Bridge (3) | 6.1                                |          |

| TIM2            | 49.1                               |          |

| TIM3            | 38.8                               |          |

| TIM4            | 38.3                               |          |

## 6.3.6 Wakeup time from low-power mode

The wakeup times given in *Table 39* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep mode: the wakeup event is WFE.

- WKUP1 (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

Table 39. Low-power mode wakeup timings

| Symbol                     | Baramatar                   | Parameter Conditions        |       | Typ @VDD, V <sub>DD</sub> = V <sub>DDA</sub> |       |      |       |       | Max   | Unit                   |

|----------------------------|-----------------------------|-----------------------------|-------|----------------------------------------------|-------|------|-------|-------|-------|------------------------|

|                            | Parameter                   | ter Conditions              | 2.0 V | 2.4 V                                        | 2.7 V | 3 V  | 3.3 V | 3.6 V | IVIAX | Oill                   |

|                            | Wakeup from                 | Regulator in run mode       | 4.1   | 3.9                                          | 3.8   | 3.7  | 3.6   | 3.5   | 4.5   |                        |

| t <sub>WUSTOP</sub>        | Stop mode                   | Regulator in low-power mode | 7.9   | 6.7                                          | 6.1   | 5.7  | 5.4   | 5.2   | 9     | μs                     |

| t <sub>WUSTANDBY</sub> (1) | Wakeup from<br>Standby mode | LSI and<br>IWDG OFF         | 69.2  | 60.3                                         | 56.4  | 53.7 | 51.7  | 50    | 100   |                        |

| t <sub>WUSLEEP</sub>       | Wakeup from<br>Sleep mode   | -                           |       | 6                                            |       |      |       |       |       | CPU<br>clock<br>cycles |

<sup>1.</sup> Guaranteed by characterization results.

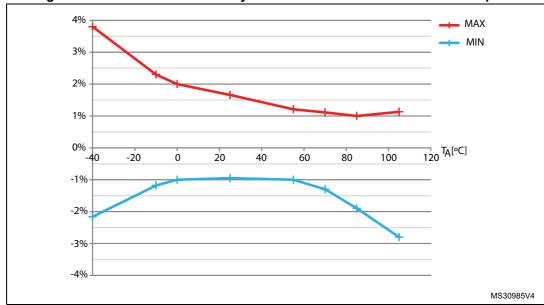

Figure 18. HSI oscillator accuracy characterization results for soldered parts

#### Low-speed internal (LSI) RC oscillator

Table 45. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup> | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

<sup>1.</sup>  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

5//

<sup>2.</sup> Guaranteed by design.

3. Channels available on PA2, PA6, PB1, PB12.

Table 70. ADC accuracy - limited test conditions, 100-pin packages (1)(2)

| Symbol                                       | Parameter              | Conditions                                                                                                         |                     |                     |      | Тур        | Max<br>(3) | Unit   |

|----------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|------------|------------|--------|

| Total<br>ET unadiusted                       |                        | Cinale anded                                                                                                       | Fast channel 5.1 Ms | -                   | ±3.5 | ±4.5       |            |        |

|                                              |                        | ed                                                                                                                 | Single ended        | Slow channel 4.8 Ms | -    | <u>±</u> 4 | ±4.5       | - LSB  |

| E1                                           | unadjusted<br>error    |                                                                                                                    | Differential        | Fast channel 5.1 Ms | -    | ±3         | ±3         |        |

|                                              |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | ±3         | ±3         |        |

|                                              |                        |                                                                                                                    | Oire alse and ad    | Fast channel 5.1 Ms | -    | ±1         | ±1.5       |        |

| EO                                           | Offset error           |                                                                                                                    | Single ended        | Slow channel 4.8 Ms | -    | ±1         | ±2.5       |        |

| EO                                           | Oliset elloi           |                                                                                                                    | Differential        | Fast channel 5.1 Ms | -    | ±1         | ±1.5       |        |

|                                              |                        |                                                                                                                    | Dillerential        | Slow channel 4.8 Ms | -    | ±1         | ±1.5       |        |

|                                              |                        | error                                                                                                              | Single anded        | Fast channel 5.1 Ms | -    | ±3         | ±4         |        |

| EG                                           | Gain error             |                                                                                                                    | Single ended        | Slow channel 4.8 Ms | -    | ±3.5       | <u>±4</u>  |        |

| EG                                           | Gairrenoi              |                                                                                                                    | Differential        | Fast channel 5.1 Ms | -    | ±1.5       | ±2.5       |        |

|                                              |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | <u>+2</u>  | ±2.5       |        |

|                                              |                        | ADC clock freq. ≤ 72 MHz Sampling freq. ≤ 5 Msps V <sub>DDA</sub> = V <sub>REF+</sub> = 3.3 V 25°C 100-pin package | Single ended        | Fast channel 5.1 Ms | -    | ±1         | ±1.5       |        |

| ED                                           | Differential linearity |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | ±1         | ±1.5       |        |

| ED                                           | error                  |                                                                                                                    | Differential        | Fast channel 5.1 Ms | -    | ±1         | ±1         |        |

|                                              |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | ±1         | ±1         |        |

|                                              |                        |                                                                                                                    | Single ended        | Fast channel 5.1 Ms | -    | ±1.5       | ±2         |        |

| EL                                           | Integral<br>linearity  |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | ±1.5       | ±3         |        |

| EL                                           | error                  |                                                                                                                    | Differential        | Fast channel 5.1 Ms | -    | ±1         | ±1.5       |        |

|                                              |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | -    | ±1         | ±1.5       |        |

|                                              |                        |                                                                                                                    | Single ended        | Fast channel 5.1 Ms | 10.7 | 10.8       | -          | - bits |

| ENOB <sup>(4)</sup> Effective number of bits |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | 10.7 | 10.8       | -          |        |

|                                              |                        | gnal-to-<br>sise and<br>stortion                                                                                   | Differential        | Fast channel 5.1 Ms | 11.2 | 11.3       | -          |        |

|                                              |                        |                                                                                                                    |                     | Slow channel 4.8 Ms | 11.1 | 11.3       | -          |        |

|                                              | Cianal to              |                                                                                                                    | Single ended        | Fast channel 5.1 Ms | 66   | 67         | -          | - dB   |

|                                              | noise and              |                                                                                                                    |                     | Slow channel 4.8 Ms | 66   | 67         | -          |        |

| SINAD                                        | distortion             |                                                                                                                    | Differential        | Fast channel 5.1 Ms | 69   | 70         | -          |        |

| rat                                          | ratio                  |                                                                                                                    |                     | Slow channel 4.8 Ms | 69   | 70         | -          |        |

Table 72. ADC accuracy - limited test conditions, 64-pin packages<sup>(1)(2)</sup> (continued)

| Symbol                                       | Parameter   | C                                               | Min<br>(3)                 | Тур                 | Max<br>(3) | Unit |     |      |

|----------------------------------------------|-------------|-------------------------------------------------|----------------------------|---------------------|------------|------|-----|------|

|                                              |             |                                                 | Single ended               | Fast channel 5.1 Ms | 66         | 67   | -   | - dB |

| SNR <sup>(4)</sup> Signal-to-<br>noise ratio | Signal-to-  |                                                 | Single ended               | Slow channel 4.8 Ms | 66         | 67   | -   |      |

|                                              | noise ratio | ADC clock freq. ≤ 72 MHz Sampling freq ≤ 5 Msps | Differential               | Fast channel 5.1 Ms | 69         | 70   | -   |      |

|                                              |             |                                                 |                            | Slow channel 4.8 Ms | 69         | 70   | -   |      |

|                                              |             | otal 64-pin package<br>armonic –                | Single ended  Differential | Fast channel 5.1 Ms | -          | -80  | -80 | uБ   |

| THD <sup>(4)</sup> Total harmon distortion   |             |                                                 |                            | Slow channel 4.8 Ms | -          | -78  | -77 |      |

|                                              | distortion  |                                                 |                            | Fast channel 5.1 Ms | -          | -83  | -82 |      |

|                                              |             |                                                 |                            | Slow channel 4.8 Ms | -          | -81  | -80 |      |

<sup>1.</sup> ADC DC accuracy values are measured after internal calibration.

<sup>2.</sup> ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

<sup>3.</sup> Guaranteed by characterization results.

<sup>4.</sup> Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

Table 84. WLCSP100 – 100L, 4.166 x 4.628 mm 0.4 mm pitch wafer level chip scale package mechanical data

| Cumbal             | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------------------|-------------|--------|-------|-----------------------|--------|--------|--|

| Symbol             | Min         | Тур    | Max   | Тур                   | Min    | Max    |  |

| Α                  | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |

| A1                 | -           | 0.17   | -     | -                     | 0.0067 | -      |  |

| A2                 | -           | 0.38   | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup>  | -           | 0.025  | -     | -                     | 0.0010 | -      |  |

| Ø b <sup>(3)</sup> | 0.22        | 0.25   | 0.28  | -                     | 0.0098 | 0.0110 |  |

| D                  | 4.166       | 4.201  | 4.236 | -                     | 0.1654 | 0.1668 |  |

| E                  | 4.628       | 4.663  | 4.698 | -                     | 0.1836 | 0.1850 |  |

| е                  | -           | 0.4    | -     | -                     | 0.0157 | -      |  |

| e1                 | -           | 3.6    | -     | -                     | 0.1417 | -      |  |

| e2                 | -           | 3.6    | -     | -                     | 0.1417 | -      |  |

| F                  | -           | 0.3005 | -     | -                     | 0.0118 | -      |  |

| G                  | -           | 0.5315 | -     | -                     | 0.0209 | -      |  |

| N                  | -           | 100    | -     | -                     | 3.9370 | -      |  |

| aaa                | -           | 0.1    | -     | -                     | 0.0039 | -      |  |

| bbb                | -           | 0.1    | -     | -                     | 0.0039 | -      |  |

| ccc                | -           | 0.1    | -     | -                     | 0.0039 | -      |  |

| ddd                | -           | 0.05   | -     | -                     | 0.0020 | -      |  |

| eee                | -           | 0.05   | -     | -                     | 0.0020 | -      |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

<sup>2.</sup> Back side coating.

<sup>3.</sup> Dimension is measured at the maximum bump diameter parallel to primary datum  ${\sf Z}$ .

## 9 Revision history

Table 88. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Jun-2012 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 07-Sep-2012 | 2        | Modified Features on cover page. Modified Table 2: STM32F301xx family device features and peripheral counts Added clock tree to Section 3.9: Clocks and startup Added Table 10: STM32F302xB/STM32F302xC I2C implementation Added Table 11: USART features Added Table 12: STM32F302xB/STM32F302xC SPI/I2S implementation Modified Table 13: Capacitive sensing GPIOs available on STM32F302xB/STM32F302xC devices Modified Figure 7, Figure 8 and Figure 9: STM32F302xB/STM32F302xC LQFP100 pinout Modified Table 16: STM32F302xB/STM32F302xC pin definitions Modified Table 16: STM32F302xB/STM32F302xC pin definitions Modified Table 21: Voltage characteristics Modified Table 22: Current characteristics Modified Table 25: Operating conditions at power-up / power-down Added footnote to Table 31: Typical and maximum current consumption from the VDDA supply Added footnote to Table 35 and Table 36: Typical current consumption in Sleep mode, code running from Flash or RAM Removed table "Switching output I/O current consumption" and table "Peripheral current consumption" Added note under Figure 17: Typical application with a 32.768 kHz crystal Updated Table 49: HSI oscillator characteristics Updated Wakeup time from low-power mode and Table 39: Low-power mode wakeup timings Updated Table 52: Electrical sensitivities Updated Table 53: I/O current injection susceptibility Updated Table 55: Output voltage characteristics Updated Table 55: Output voltage characteristics Updated Table 56: SPI characteristics Updated Table 64: I/S characteristics Corrected LQFP100 in Section 7.2.3: Selecting the product temperature range |

| 21-Sep-2012 | 3        | Updated Table 63: SPI characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 88. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 06-May-2016 | 13       | Updated <i>Table 43: LSE oscillator characteristics (fLSE</i> = 32.768 kHz) LSEDRV[1:0] bits. Updated <i>Table 28: Embedded internal reference voltage</i> V <sub>REFINT</sub> internal reference voltage (min and typ values). Updated <i>Figure 5: STM32F303xB/STM32F303xC LQFP64 pinout</i> replacing VSS by PF4. Updated <i>Table 51: ESD absolute maximum ratings</i> ESD CDM at class 3 and 4 including WLCSP100 package information. Updated <i>Table 13: STM32F303xB/STM32F303xC pin definitions:</i> – Adding 'digital power supply' in the Pin function column at the line corresponding to K8/28/19 pins.  – Adding VSS digital ground line with WLCSP100 K9 and K10 pins connected.  – Replacing in VDD line for WLCSP100: 'A10, B10' by 'A9, A10, B10, B8'. Updated <i>Figure 21: Five volt tolerant (FT and FTf) I/O input characteristics - CMOS port.</i> Updated <i>Table 77: Operational amplifier characteristics</i> high saturation and low saturation voltages. Updated <i>Table 13: STM32F303xB/STM32F303xC pin definitions</i> adding note 'Fast ADC channel' for ADCx_IN15. Updated <i>Table 68: ADC characteristics</i> resistive load. Updated <i>Table 68: ADC characteristics</i> adding CMIR parameter and modifying tSTAB parameter characteristics. |  |  |