Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite10f1m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 2. Hardware Register Map

| Address           | Block                            | Register Label              | Register Name                        | Reset Status      | Remarks           |

|-------------------|----------------------------------|-----------------------------|--------------------------------------|-------------------|-------------------|

| 0000h             | 5                                |                             | FFh <sup>1)</sup>                    | R/W               |                   |

| 0001h             | Port A                           | PADDR                       | Port A Data Direction Register       | 00h               | R/W               |

| 0002h             |                                  | PAOR                        | Port A Option Register               | 40h               | R/W               |

| 0003h             |                                  | PBDR                        | Port B Data Register                 | FFh <sup>1)</sup> | R/W               |

| 0004h             | Port B                           | PBDDR                       | Port B Data Direction Register       | 00h               | R/W               |

| 0005h             |                                  | PBOR                        | Port B Option Register               | 00h               | R/W <sup>2)</sup> |

| 0006h<br>0007h    |                                  | •                           | Reserved Area (2 bytes)              |                   |                   |

| 0008h             |                                  | LTCSR2                      | Lite Timer Control/Status Register 2 | 0Fh               | R/W               |

| 0009h             | LITE                             | LTARR                       | Lite Timer Auto-reload Register      | 00h               | R/W               |

| 000Ah             |                                  | LTCNTR                      | Lite Timer Counter Register          | 00h               | Read Only         |

| 000Bh             | TIMER 2                          | LTCSR1                      | Lite Timer Control/Status Register 1 | 0X00 0000h        | R/W               |

| 000Ch             |                                  | LTICR                       | Lite Timer Input Capture Register    | xxh               | Read Only         |

| 000Dh             |                                  | ATCSR                       | Timer Control/Status Register        | 0X00 0000h        | R/W               |

| 000Eh             |                                  | CNTRH                       | Counter Register High                | 00h               | Read Only         |

| 000Fh             |                                  | CNTRL                       | Counter Register Low                 | 00h               | Read Only         |

| 0010h             |                                  | ATRH                        | Auto-Reload Register High            | 00h               | R/W               |

| 0011h             |                                  | ATRL                        | Auto-Reload Register Low             | 00h               | R/W               |

| 0012h             |                                  | PWMCR                       | PWM Output Control Register          | 00h               | R/W               |

| 0013h             |                                  | PWM0CSR                     | PWM 0 Control/Status Register        | 00h               | R/W               |

| 0014h             |                                  | PWM1CSR                     | PWM 1 Control/Status Register        | 00h               | R/W               |

| 0015h             |                                  | PWM2CSR                     | PWM 2 Control/Status Register        | 00h               | R/W               |

| 0016h             | AUTO-                            | PWM3CSR                     | PWM 3 Control/Status Register        | 00h               | R/W               |

| 0017h             | RELOAD                           | DCR0H                       | PWM 0 Duty Cycle Register High       | 00h               | R/W               |

| 0018h             | TIMER 2                          | DCR0L                       | PWM 0 Duty Cycle Register Low        | 00h               | R/W               |

| 0019h             |                                  | DCR1H                       | PWM 1 Duty Cycle Register High       | 00h               | R/W               |

| 001911<br>001Ah   |                                  | DCR1L                       | PWM 1 Duty Cycle Register Low        | 00h               | R/W               |

|                   |                                  |                             |                                      |                   |                   |

| 001Bh             |                                  | DCR2H                       | PWM 2 Duty Cycle Register High       | 00h               | R/W               |

| 001Ch             |                                  | DCR2L                       | PWM 2 Duty Cycle Register Low        | 00h               | R/W               |

| 001Dh             |                                  | DCR3H                       | PWM 3 Duty Cycle Register High       | 00h               | R/W               |

| 001Eh             |                                  | DCR3L                       | PWM 3 Duty Cycle Register Low        | 00h               | R/W               |

| 001Fh             |                                  | ATICRH                      | Input Capture Register High          | 00h               | Read Only         |

| 0020h             |                                  | ATICRL                      | Input Capture Register Low           | 00h               | Read Only         |

| 0021h             |                                  | TRANCR                      | Transfer Control Register            | 01h               | R/W               |

| 0022h             |                                  | BREAKCR                     | Break Control Register               | 00h               | R/W               |

| 0023h to<br>002Dh |                                  |                             | Reserved area (11 bytes)             |                   |                   |

| 002Eh             | WDG                              | WDGCR                       | Watchdog Control Register            | 7Fh               | R/W               |

| 0002Fh            | FLASH                            | FCSR                        | Flash Control/Status Register        | 00h               | R/W               |

| 00030h            | EEPROM                           | EECSR                       | Data EEPROM Control/Status Register  | 00h               | R/W               |

| 0031h             | I31h SPIDR SPI Data I/O Register |                             | xxh                                  | R/W               |                   |

| 0032h             | SPI                              | SPICR                       | SPI Control Register                 | 0xh               | R/W               |

|                   |                                  | SPI Control Status Register | 00h                                  | R/W               |                   |

| 0034h             |                                  | ADCCSR                      | A/D Control Status Register          | 00h               | R/W               |

| 0035h             | ADC                              | ADCDRH                      | A/D Data Register High               | xxh               | Read Only         |

|                   |                                  |                             | 5 5                                  |                   |                   |

# DATA EEPROM (Cont'd)

#### **5.3 MEMORY ACCESS**

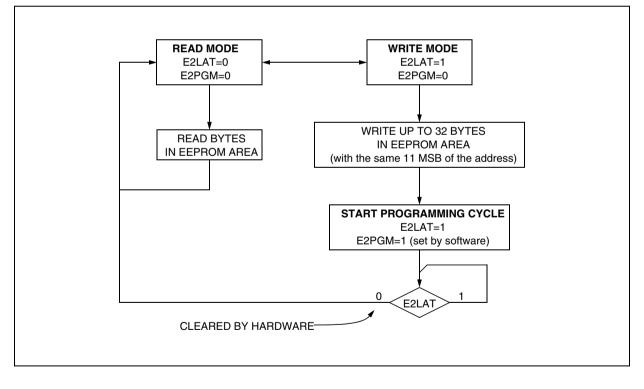

The Data EEPROM memory read/write access modes are controlled by the E2LAT bit of the EEP-ROM Control/Status register (EECSR). The flowchart in Figure 6 describes these different memory access modes.

#### Read Operation (E2LAT=0)

The EEPROM can be read as a normal ROM location when the E2LAT bit of the EECSR register is cleared. In a read cycle, the byte to be accessed is put on the data bus in less than 1 CPU clock cycle. This means that reading data from EEPROM takes the same time as reading data from EPROM, but this memory cannot be used to execute machine code.

#### Write Operation (E2LAT=1)

To access the write mode, the E2LAT bit has to be set by software (the E2PGM bit remains cleared). When a write access to the EEPROM area occurs,

#### Figure 6. Data EEPROM Programming Flowchart

the value is latched inside the 32 data latches according to its address.

When PGM bit is set by the software, all the previous bytes written in the data latches (up to 32) are programmed in the EEPROM cells. The effective high address (row) is determined by the last EEP-ROM write sequence. To avoid wrong programming, the user must take care that all the bytes written between two programming sequences have the same high address: only the five Least Significant Bits of the address can change.

At the end of the programming cycle, the PGM and LAT bits are cleared simultaneously.

**Note**: Care should be taken during the programming cycle. Writing to the same memory location will over-program the memory (logical AND between the two write access data result) because the data latches are only cleared at the end of the programming cycle and by the falling edge of the E2LAT bit.

57/

It is not possible to read the latched data. This note is ilustrated by the Figure 8.

# PHASE LOCKED LOOP (Cont'd)

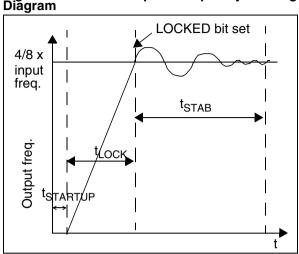

Figure 11. PLL Output Frequency Timing

When the PLL is started, after reset or wakeup from Halt mode or AWUFH mode, it outputs the clock after a delay of t<sub>STARTUP</sub>.

When the PLL output signal reaches the operating frequency, the LOCKED bit in the SICSCR register is set. Full PLL accuracy (ACC<sub>PLL</sub>) is reached after a stabilization time of  $t_{STAB}$  (see Figure 11 and 13.3.4 Internal RC Oscillator and PLL)

Refer to section 7.6.4 on page 33 for a description of the LOCKED bit in the SICSR register.

# 7.3 REGISTER DESCRIPTION

# MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |

Bits 7:2 = Reserved, must be kept cleared.

#### Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

- 0: MCO clock disabled, I/O port free for general purpose I/O.

- 1: MCO clock enabled.

#### Bit 0 = SMS Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ .

0: Normal mode (f<sub>CPU =</sub> f<sub>OSC</sub>

1: Slow mode ( $f_{CPU} = f_{OSC}/32$ )

#### **RC CONTROL REGISTER (RCCR)**

Read / Write

Reset Value: 1111 1111 (FFh)

| 7    |      |      |      |      |      |      | 0   |

|------|------|------|------|------|------|------|-----|

| CR70 | CR60 | CR50 | CR40 | CR30 | CR20 | CR10 | CR0 |

Bits 7:0 = **CR[7:0]** *RC* Oscillator Frequency Adjustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up.

00h = maximum available frequency

FFh = lowest available frequency

**Note:** To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

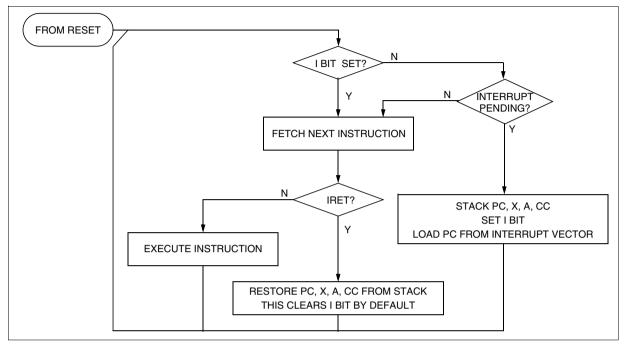

# INTERRUPTS (Cont'd)

#### Table 5. Interrupt Mapping

| N° | Source<br>Block | Description                                                     | Register<br>Label   | Priority<br>Order  | Exit<br>from<br>HALT or<br>AWUFH | Exit<br>from<br>ACTIVE<br>-HALT | Address<br>Vector |

|----|-----------------|-----------------------------------------------------------------|---------------------|--------------------|----------------------------------|---------------------------------|-------------------|

|    | RESET           | Reset                                                           | N/A                 | Highest            | yes                              | yes                             | FFFEh-FFFFh       |

|    | TRAP            | Software Interrupt                                              | N/A                 | Priority           | no                               |                                 | FFFCh-FFFDh       |

| 0  | AWU             | Auto Wake Up Interrupt                                          | AWUCSR              |                    | yes <sup>1)</sup>                |                                 | FFFAh-FFFBh       |

| 1  | ei0             | External Interrupt 0                                            |                     |                    |                                  |                                 | FFF8h-FFF9h       |

| 2  | ei1             | External Interrupt 1                                            | N/A                 |                    | yes                              | no                              | FFF6h-FFF7h       |

| 3  | ei2             | External Interrupt 2                                            |                     |                    |                                  |                                 | FFF4h-FFF5h       |

| 4  | ei3             | External Interrupt 3                                            |                     |                    |                                  |                                 | FFF2h-FFF3h       |

| 5  | LITE TIMER      | LITE TIMER RTC2 interrupt                                       | LTCSR2              |                    | no                               |                                 | FFF0h-FFF1h       |

| 6  |                 | Not used                                                        |                     |                    |                                  |                                 | FFEEh-FFEFh       |

| 7  | SI              | AVD interrupt                                                   | SICSR               |                    |                                  |                                 | FFECh-FFEDh       |

| 8  | AT TIMER        | AT TIMER Output Compare Interrupt<br>or Input Capture Interrupt | PWMxCSR<br>or ATCSR |                    |                                  | no                              | FFEAh-FFEBh       |

| 9  |                 | AT TIMER Overflow Interrupt                                     | ATCSR               |                    | no                               | yes                             | FFE8h-FFE9h       |

| 10 | LITE TIMER      | LITE TIMER Input Capture Interrupt                              | LTCSR               |                    |                                  | no                              | FFE6h-FFE7h       |

| 11 |                 | LITE TIMER RTC1 Interrupt                                       | LTCSR               | ▼                  |                                  | yes                             | FFE4h-FFE5h       |

| 12 | SPI             | SPI Peripheral Interrupts                                       | SPICSR              | Lowest<br>Priority | yes                              | no                              | FFE2h-FFE3h       |

| 13 |                 | Not usedNot used                                                |                     | Friority           |                                  |                                 | FFE0h-FFE1h       |

Note 1: This interrupt exits the MCU from "Auto Wake-up from Halt" mode only.

#### INTERRUPTS (Cont'd)

# EXTERNAL INTERRUPT CONTROL REGISTER (EICR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| •    |      |      |      |      |      |      | •    |

|------|------|------|------|------|------|------|------|

| IS31 | IS30 | IS21 | IS20 | IS11 | IS10 | IS01 | IS00 |

Bit 7:6 = IS3[1:0] ei3 sensitivity

These bits define the interrupt sensitivity for ei3 (Port B0) according to Table 6.

Bit 5:4 = IS2[1:0] ei2 sensitivity

These bits define the interrupt sensitivity for ei2 (Port B3) according to Table 6.

Bit 3:2 = **IS1[1:0]** *ei1 sensitivity*

These bits define the interrupt sensitivity for ei1 (Port A7) according to Table 6.

Bit 1:0 = ISO[1:0] ei0 sensitivity

These bits define the interrupt sensitivity for ei0 (Port A0) according to Table 6.

**Note:** These 8 bits can be written only when the I bit in the CC register is set.

#### **Table 6. Interrupt Sensitivity Bits**

| ISx1 | ISx0 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

# EXTERNAL INTERRUPT SELECTION REGISTER (EISR)

Read/Write

٥

Reset Value: 0000 1100 (0Ch)

| 7    |      |      |      |      |      |      | 0    |  |

|------|------|------|------|------|------|------|------|--|

| ei31 | ei30 | ei21 | ei20 | ei11 | ei10 | ei01 | ei00 |  |

Bit 7:6 = **ei3[1:0]** *ei3 pin selection*

These bits are written by software. They select the Port B I/O pin used for the ei3 external interrupt according to the table below.

#### External Interrupt I/O pin selection

| ei31 | ei30 | I/O Pin |

|------|------|---------|

| 0    | 0    | PB0 *   |

| 0    | 1    | PB1     |

| 1    | 0    | PB2     |

\* Reset State

Bit 5:4 = ei2[1:0] ei2 pin selection

These bits are written by software. They select the Port B I/O pin used for the ei2 external interrupt according to the table below.

#### External Interrupt I/O pin selection

| ei21 | ei20 | I/O Pin           |

|------|------|-------------------|

| 0    | 0    | PB3 *             |

| 0    | 1    | PB4 <sup>1)</sup> |

| 1    | 0    | PB5               |

| 1    | 1    | PB6               |

\* Reset State

1) Note that PB4 cannot be used as an external interrupt in HALT mode.

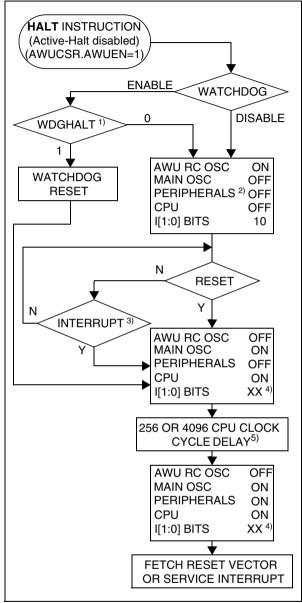

#### POWER SAVING MODES (Cont'd)

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only an AWUFH interrupt and some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 5, "Interrupt Mapping," on page 35 for more details.

**4.** Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

**5.** If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 11).

# 10 I/O PORTS

#### **10.1 INTRODUCTION**

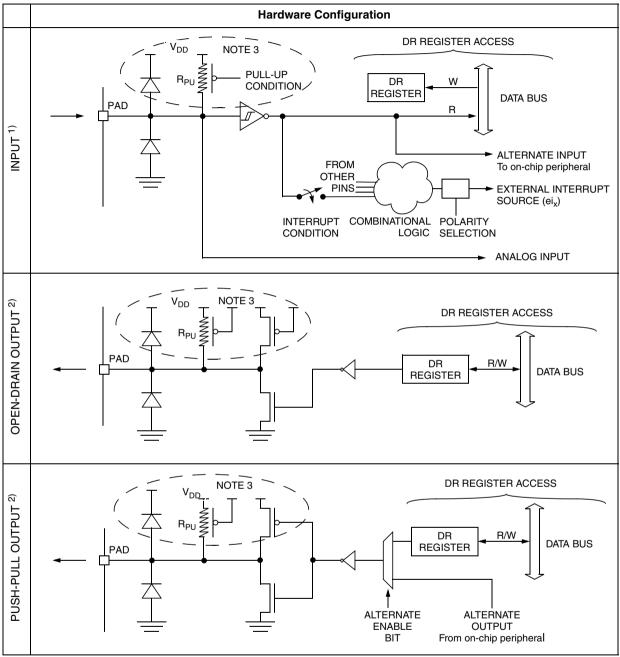

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

#### **10.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

Figure 30 shows the generic I/O block diagram.

#### 10.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

#### Notes:

1. Writing to the DR modifies the latch value but does not change the state of the input pin.

2. Do not use read/modify/write instructions (BSET/BRES) to modify the DR register.

#### **External Interrupt Function**

Depending on the device, setting the ORx bit while in input mode can configure an I/O as an input with interrupt. In this configuration, a signal edge or level input on the I/O generates an interrupt request via the corresponding interrupt vector (eix).

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) or the Miscellaneous Register controls this sensitivity, depending on the device. External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Modifying the sensitivity bits will clear any pending interrupts.

#### 10.2.2 Output Modes

Setting the DDRx bit selects output mode. Writing to the DR bits applies a digital value to the I/O through the latch. Reading the DR bits returns the previously stored value.

If an OR bit is available, different output modes can be selected by software: push-pull or opendrain. Refer to I/O Port Implementation section for configuration.

| DR Value ar | nd Output Pin Status | ; |

|-------------|----------------------|---|

|             |                      |   |

|   | DR | Push-Pull       | Open-Drain      |

|---|----|-----------------|-----------------|

| ſ | 0  | V <sub>OL</sub> | V <sub>OL</sub> |

|   | 1  | V <sub>OH</sub> | Floating        |

#### **10.2.3 Alternate Functions**

Many ST7s I/Os have one or more alternate functions. These may include output signals from, or input signals to, on-chip peripherals. The Device Pin Description table describes which peripheral signals can be input/output to which ports.

A signal coming from an on-chip peripheral can be output on an I/O. To do this, enable the on-chip peripheral as an output (enable bit in the peripheral's control register). The peripheral configures the I/O as an output and takes priority over standard I/ O programming. The I/O's state is readable by addressing the corresponding I/O data register.

Configuring an I/O as floating enables alternate function input. It is not recommended to configure an I/O as pull-up as this will increase current consumption. Before using an I/O as an alternate input, configure it without interrupt. Otherwise spurious interrupts can occur.

Configure an I/O as input floating for an on-chip peripheral signal which can be input and output.

#### Caution:

I/Os which can be configured as both an analog and digital alternate function need special attention. The user must control the peripherals so that the signals do not arrive at the same time on the same pin. If an external clock is used, only the clock alternate function should be employed on that I/O pin and not the other alternate function.

# I/O PORTS (Cont'd)

# Table 9. I/O Configurations

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

- 3. For true open drain, these elements are not implemented.

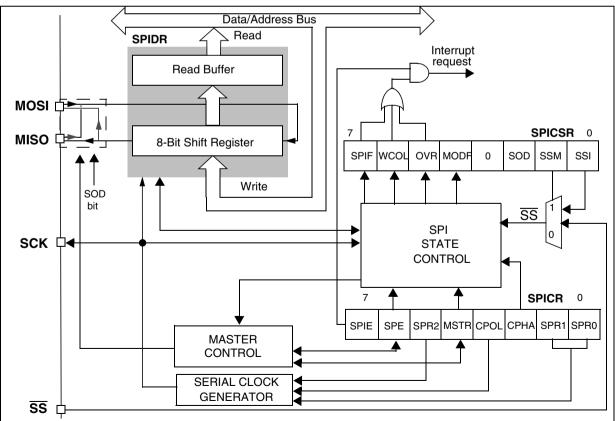

# **11.4 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 11.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **11.4.3 General Description**

Figure 41 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 3 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

# Figure 41. Serial Peripheral Interface Block Diagram

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### 11.5.6 Register Description

#### CONTROL/STATUS REGISTER (ADCCSR)

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7 |  |

|---|--|

|   |  |

5//

| 1   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

# Bit 7 = EOC End of Conversion

This bit is set by hardware. It is cleared by software reading the ADCDRH register.

- 0: Conversion is not complete

- 1: Conversion complete

#### Bit 6 = **SPEED** ADC clock selection

This bit is set and cleared by software. It is used together with the SLOW bit to configure the ADC clock speed. Refer to the table in the SLOW bit description.

#### Bit 5 = ADON A/D Converter on

This bit is set and cleared by software. 0: A/D converter and amplifier are switched off 1: A/D converter and amplifier are switched on

Bit 4:3 = **Reserved.** Must be kept cleared.

#### Bit 2:0 = CH[2:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|

| AINO         | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 1   |

| AIN2         | 0   | 1   | 0   |

| AIN3         | 0   | 1   | 1   |

| AIN4         | 1   | 0   | 0   |

| AIN5         | 1   | 0   | 1   |

| AIN6         | 1   | 1   | 0   |

\*The number of channels is device dependent. Refer to the device pinout description.

#### DATA REGISTER HIGH (ADCDRH)

Read Only

Reset Value: xxxx xxxx (xxh)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

Bit 7:0 = **D[9:2]** MSB of Analog Converted Value

#### AMP CONTROL/DATA REGISTER LOW (AD-CDRL)

Read/Write

Reset Value: 0000 00xx (0xh)

| 7 |   |   |            |      |             |    | 0  |

|---|---|---|------------|------|-------------|----|----|

| 0 | 0 | 0 | AMP<br>CAL | SLOW | AMP-<br>SEL | D1 | D0 |

Bit 7:5 = Reserved. Forced by hardware to 0.

#### Bit 4 = AMPCAL Amplifier Calibration Bit

This bit is set and cleared by software. User is suggested to use this bit to calibrate the ADC when amplifier is ON. Setting this bit internally connects amplifier input to 0v. Hence, corresponding ADC output can be used in software to eliminate amplifier-offset error.

0: Calibration off

1: Calibration on. (The input voltage of the amp is set to 0V)

Note: It is advised to use this bit to calibrate the ADC when the amplifier is ON. Setting this bit internally connects the amplifier input to 0v. Hence, the corresponding ADC output can be used in software to eliminate an amplifier-offset error.

#### Bit 3 = **SLOW** Slow mode

This bit is set and cleared by software. It is used together with the SPEED bit to configure the ADC clock speed as shown on the table below.

| f <sub>ADC</sub>    | SLOW | SPEED |

|---------------------|------|-------|

| f <sub>CPU</sub> /2 | 0    | 0     |

| f <sub>CPU</sub>    | 0    | 1     |

| f <sub>CPU</sub> /4 | 1    | х     |

# ST7 ADDRESSING MODES (Cont'd)

#### 12.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                            |

|----------------------------|-------------------------------------|

| NOP                        | No operation                        |

| TRAP                       | S/W Interrupt                       |

| WFI                        | Wait For Interrupt (Low Power Mode) |

| HALT                       | Halt Oscillator (Lowest Power Mode) |

| RET                        | Sub-routine Return                  |

| IRET                       | Interrupt Sub-routine Return        |

| SIM                        | Set Interrupt Mask                  |

| RIM                        | Reset Interrupt Mask                |

| SCF                        | Set Carry Flag                      |

| RCF                        | Reset Carry Flag                    |

| RSP                        | Reset Stack Pointer                 |

| LD                         | Load                                |

| CLR                        | Clear                               |

| PUSH/POP                   | Push/Pop to/from the stack          |

| INC/DEC                    | Increment/Decrement                 |

| TNZ                        | Test Negative or Zero               |

| CPL, NEG                   | 1 or 2 Complement                   |

| MUL                        | Byte Multiplication                 |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations         |

| SWAP                       | Swap Nibbles                        |

#### 12.1.2 Immediate

Immediate instructions have two bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

#### 12.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

#### **Direct (short)**

The address is a byte, thus requires only one byte after the opcode, but only allows 00 - FF addressing space.

#### Direct (long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

#### 12.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three sub-modes:

#### Indexed (No Offset)

There is no offset, (no extra byte after the opcode), and allows 00 - FF addressing space.

#### Indexed (Short)

The offset is a byte, thus requires only one byte after the opcode and allows 00 - 1FE addressing space.

#### Indexed (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

#### 12.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer).

The pointer address follows the opcode. The indirect addressing mode consists of two sub-modes:

#### Indirect (short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

#### Indirect (long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# ST7 ADDRESSING MODES (Cont'd)

# 12.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

#### **Indirect Indexed (Short)**

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table 20. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressingModesAddressingAddressingAddressing

| Long and Short<br>Instructions | Function                                        |

|--------------------------------|-------------------------------------------------|

| LD                             | Load                                            |

| CP                             | Compare                                         |

| AND, OR, XOR                   | Logical Operations                              |

| ADC, ADD, SUB, SBC             | Arithmetic Addition/subtrac-<br>tion operations |

| BCP                            | Bit Compare                                     |

| Short Instructions Only    | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP     | Swap Nibbles            |

|----------|-------------------------|

| CALL, JP | Call or Jump subroutine |

# 12.1.7 Relative Mode (Direct, Indirect)

This addressing mode is used to modify the PC register value by adding an 8-bit signed offset to it.

| Available Relative Direct/<br>Indirect Instructions | Function         |

|-----------------------------------------------------|------------------|

| JRxx                                                | Conditional Jump |

| CALLR                                               | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset follows the opcode.

#### **Relative (Indirect)**

The offset is defined in memory, of which the address follows the opcode.

# **13 ELECTRICAL CHARACTERISTICS**

# **13.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $\ensuremath{\mathsf{V}_{SS}}\xspace.$

#### 13.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 13.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^\circ\text{C},~V_{DD}=5\text{V}$  (for the  $4.5\text{V}{\leq}\text{V}_{DD}{\leq}5.5\text{V}$  voltage range) and  $V_{DD}=3.3\text{V}$  (for the  $3\text{V}{\leq}\text{V}_{DD}{\leq}4\text{V}$  voltage range). They are given only as design guidelines and are not tested.

#### 13.1.3 Typical curves

<u>/</u>حک

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

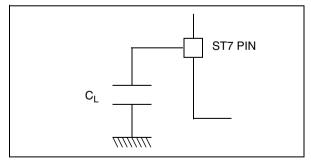

#### 13.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 49.

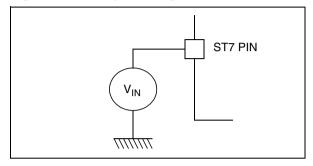

#### Figure 49. Pin loading conditions

#### 13.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 50.

#### Figure 50. Pin input voltage

# 13.3.2 Operating Conditions with Low Voltage Detector (LVD)

$T_A = -40$  to 85°C, unless otherwise specified

| Symbol                | Parameter                                         | Conditions                                        | Min                                                            | Тур                  | Max                                                            | Unit |  |

|-----------------------|---------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------------------------------------------------|------|--|

| V <sub>IT+(LVD)</sub> | Reset release threshold<br>(V <sub>DD</sub> rise) | High Threshold<br>Med. Threshold<br>Low Threshold | 4.00 <sup>1)</sup><br>3.40 <sup>1)</sup><br>2.65 <sup>1)</sup> | 4.25<br>3.60<br>2.90 | 4.50<br>3.80<br>3.15                                           | V    |  |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall) | High Threshold<br>Med. Threshold<br>Low Threshold | 3.80<br>3.20<br>2.40                                           | 4.05<br>3.40<br>2.70 | 4.30 <sup>1)</sup><br>3.65 <sup>1)</sup><br>2.90 <sup>1)</sup> | V    |  |

| V <sub>hys</sub>      | LVD voltage threshold hysteresis                  | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub>      |                                                                | 200                  |                                                                | mV   |  |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time rate <sup>2)</sup>      |                                                   | 20                                                             |                      | 20000                                                          | μs/V |  |

| t <sub>g(VDD)</sub>   | Filtered glitch delay on $V_{DD}$                 | Not detected by the LVD                           |                                                                |                      | 150                                                            | ns   |  |

| I <sub>DD(LVD</sub> ) | LVD/AVD current consumption                       |                                                   |                                                                | 220                  |                                                                | μA   |  |

#### Note:

1. Not tested in production.

2. Not tested in production. The  $V_{DD}$  rise time rate condition is needed to insure a correct device power-on and LVD reset. When the  $V_{DD}$  slope is outside these values, the LVD may not ensure a proper reset of the MCU.

# 13.3.3 Auxiliary Voltage Detector (AVD) Thresholds

$T_A = -40$  to 85°C, unless otherwise specified

| Symbol                  | Parameter                                                  | Conditions                                        | Min                                                            | Тур                  | Max                                                            | Unit |  |

|-------------------------|------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------------------------------------------------|------|--|

| V <sub>IT+(AVD)</sub>   | 1=>0 AVDF flag toggle threshold<br>(V <sub>DD</sub> rise)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.40 <sup>1)</sup><br>3.90 <sup>1)</sup><br>3.20 <sup>1)</sup> | 4.70<br>4.10<br>3.40 | 5.00<br>4.30<br>3.60                                           | V    |  |

| V <sub>IT-(AVD)</sub>   | 0=>1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.30<br>3.70<br>2.90                                           | 4.60<br>3.90<br>3.20 | 4.90 <sup>1)</sup><br>4.10 <sup>1)</sup><br>3.40 <sup>1)</sup> | V    |  |

| V <sub>hys</sub>        | AVD voltage threshold hysteresis                           | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub>      |                                                                | 150                  |                                                                | mV   |  |

| $\Delta V_{\text{IT-}}$ | Voltage drop between AVD flag set and LVD reset activation | V <sub>DD</sub> fall                              |                                                                | 0.45                 |                                                                | V    |  |

#### Note:

1. Not tested in production.

#### 13.3.4 Internal RC Oscillator and PLL

The ST7 internal clock can be supplied by an internal RC oscillator and PLL (selectable by option byte).

| Symbol                 | Parameter                                | Conditions | Min | Тур | Max | Unit                                                   |

|------------------------|------------------------------------------|------------|-----|-----|-----|--------------------------------------------------------|

| V <sub>DD(RC)</sub>    | Internal RC Oscillator operating voltage |            | 2.4 |     | 5.5 |                                                        |

| V <sub>DD(x4PLL)</sub> | x4 PLL operating voltage                 |            | 2.4 |     | 3.3 | V                                                      |

| V <sub>DD(x8PLL)</sub> | x8 PLL operating voltage                 |            | 3.3 |     | 5.5 |                                                        |

| t <sub>STARTUP</sub>   | PLL Startup time                         |            |     | 60  |     | PLL<br>input<br>clock<br>(f <sub>PLL</sub> )<br>cycles |

<u>ل</u>رک

# **13.5 CLOCK AND TIMING CHARACTERISTICS**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub>.

# 13.5.1 General Timings

| Symbol               | Parameter 1)                                                                   | Conditions             | Min  | <b>Typ</b> <sup>2)</sup> | Max  | Unit             |

|----------------------|--------------------------------------------------------------------------------|------------------------|------|--------------------------|------|------------------|

| t <sub>c(INST)</sub> | Instruction cycle time                                                         | f <sub>CPU</sub> =8MHz | 2    | 3                        | 12   | t <sub>CPU</sub> |

|                      |                                                                                |                        | 250  | 375                      | 1500 | ns               |

| +                    | Interrupt reaction time <sup>3)</sup><br>$t_{v(IT)} = \Delta t_{c(INST)} + 10$ | f <sub>CPU</sub> =8MHz | 10   |                          | 22   | t <sub>CPU</sub> |

| t <sub>v(IT)</sub>   |                                                                                |                        | 1.25 |                          | 2.75 | μs               |

#### Notes:

57

1. Guaranteed by Design. Not tested in production.

2. Data based on typical application software.

3. Time measured between interrupt event and interrupt vector fetch.  $Dt_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

# 13.5.2 Auto Wakeup from Halt Oscillator (AWU)

| Symbol             | Parameter                   | Conditions | Min | Тур | Max | Unit |

|--------------------|-----------------------------|------------|-----|-----|-----|------|

| f <sub>AWU</sub>   | AWU Oscillator Frequency    |            | 50  | 125 | 250 | kHz  |

| t <sub>RCSRT</sub> | AWU Oscillator startup time |            |     |     | 50  | μs   |

# **13.6 MEMORY CHARACTERISTICS**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ , unless otherwise specified

## 13.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Мах | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 13.6.2 FLASH Program Memory

| Symbol            | Parameter                                     | Conditions                                                                       | Min               | Тур  | Max               | Unit   |

|-------------------|-----------------------------------------------|----------------------------------------------------------------------------------|-------------------|------|-------------------|--------|

| V <sub>DD</sub>   | Operating voltage for Flash write/erase       |                                                                                  | 2.4               |      | 5.5               | V      |

| +                 | Programming time for 1~32 bytes <sup>2)</sup> | T <sub>A</sub> =-40 to +85°C                                                     |                   | 5    | 10                | ms     |

| t <sub>prog</sub> | Programming time for 1.5 kBytes               | T <sub>A</sub> =+25°C                                                            |                   | 0.24 | 0.48              | s      |

| t <sub>RET</sub>  | Data retention 4)                             | T <sub>A</sub> =+55°C <sup>3)</sup>                                              | 20                |      |                   | years  |

| N <sub>RW</sub>   | Write erase cycles                            | T <sub>A</sub> =+25°C                                                            | 10K <sup>7)</sup> |      |                   | cycles |

| I <sub>DD</sub>   | Supply current                                | Read / Write / Erase<br>modes<br>f <sub>CPU</sub> = 8MHz, V <sub>DD</sub> = 5.5V |                   |      | 2.6 <sup>6)</sup> | mA     |

| 30                |                                               | No Read/No Write Mode                                                            |                   |      | 100               | μΑ     |

|                   |                                               | Power down mode / HALT                                                           |                   | 0    | 0.1               | μΑ     |

#### 13.6.3 EEPROM Data Memory

| Symbol            | Parameter                                   | Conditions                          | Min                | Тур | Max | Unit   |

|-------------------|---------------------------------------------|-------------------------------------|--------------------|-----|-----|--------|

| $V_{DD}$          | Operating voltage for EEPROM<br>write/erase |                                     | 2.4                |     | 5.5 | V      |

| t <sub>prog</sub> | Programming time for 1~32 bytes             | T <sub>A</sub> =-40 to +85°C        |                    | 5   | 10  | ms     |

| t <sub>ret</sub>  | Data retention 4)                           | T <sub>A</sub> =+55°C <sup>3)</sup> | 20                 |     |     | years  |

| N <sub>RW</sub>   | Write erase cycles                          | T <sub>A</sub> =+25°C               | 300K <sup>7)</sup> |     |     | cycles |

#### Notes:

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Guaranteed by construction, not tested in production.

2. Up to 32 bytes can be programmed at a time.

- 3. The data retention time increases when the  $\mathrm{T}_{\mathrm{A}}$  decreases.

- 4. Data based on reliability test results and monitored in production.

- 5. Data based on characterization results, not tested in production.

- 6. Guaranteed by Design. Not tested in production.

- 7. Design target value pending full product characterization.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 13.8.2 Output Driving Current

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                          | Parameter                                                                                               |                       | Conditio               | ons                                                                                       | Min                                          | Max          | Unit |

|---------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|--------------|------|

|                                 | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time                    |                       | I <sub>IO</sub> =+5mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              | 1.0<br>1.2   |      |

| V <sub>OL</sub> <sup>1)</sup>   | (see Figure 70)                                                                                         |                       | I <sub>IO</sub> =+2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              | 0.4<br>0.5   |      |

| ♥OL                             | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                      | V <sub>DD</sub> =5V   | I <sub>IO</sub> =+20mA | , T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                            |                                              | 1.3<br>1.5   |      |

|                                 | (see Figure 72)                                                                                         | V <sub>DD</sub>       | I <sub>IO</sub> =+8mA  | T <sub>A</sub> ≥85°C                                                                      |                                              | 0.75<br>0.85 |      |

| V <sub>OH</sub> <sup>2)</sup>   | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 78)     |                       | I <sub>IO</sub> =-5mA, | T <sub>A</sub> ≥85°C                                                                      | V <sub>DD</sub> -1.6                         |              |      |

| ∙он                             |                                                                                                         |                       | I <sub>IO</sub> =-2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              |              |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 69) |                       | I <sub>IO</sub> =+2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              | 0.5<br>0.6   | v    |

|                                 | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                      | 3.3V                  | I <sub>IO</sub> =+8mA  | $\begin{array}{c} T_A \!\!\leq\!\! 85^\circ C \\ T_A \!\!\geq\!\! 85^\circ C \end{array}$ |                                              | 0.5<br>0.6   |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time                        | V <sub>DD</sub> =3.3V | I <sub>IO</sub> =-2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              |              |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 68) |                       | I <sub>IO</sub> =+2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              | 0.6<br>0.7   |      |

| UL                              | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                      | 22                    | I <sub>IO</sub> =+8mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              |                                              | 0.6<br>0.7   |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 75)     | V <sub>DD</sub> =2.7  | I <sub>IO</sub> =-2mA  | T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C                                              | V <sub>DD</sub> -0.9<br>V <sub>DD</sub> -1.0 |              |      |

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

3. Not tested in production, based on characterization results.

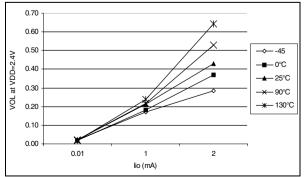

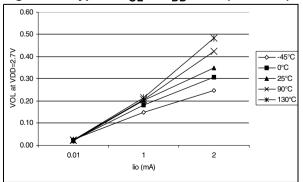

#### Figure 67. Typical V<sub>OL</sub> at V<sub>DD</sub>=2.4V (standard)

Figure 68. Typical V<sub>OL</sub> at V<sub>DD</sub>=2.7V (standard)

<u>ل</u>رک

# CONTROL PIN CHARACTERISTICS (Cont'd)

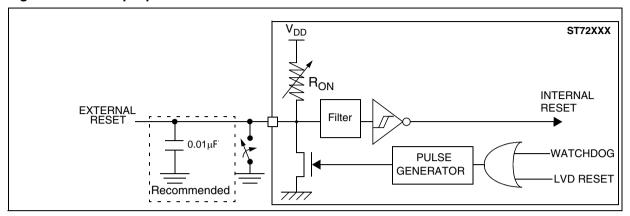

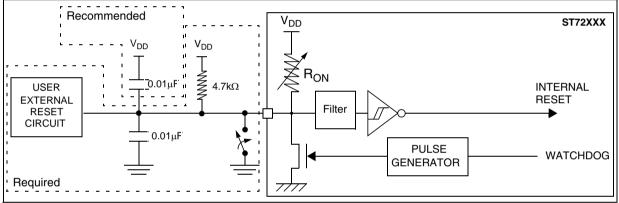

# Figure 82. RESET pin protection when LVD is enabled.<sup>1)2)3)4)5)</sup>

# Figure 83. RESET pin protection when LVD is disabled. $^{1/2)3)}$

1. The reset network protects the device against parasitic resets.

57

2. The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

3. Whatever the reset source is (internal or external), the user must ensure that the level on the  $\overrightarrow{\text{RESET}}$  pin can go below the V<sub>IL</sub> max. level specified in section 13.9.1 on page 110. Otherwise the reset will not be taken into account internally.

4. Because the reset circuit is <u>designed</u> to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin (by an external pull-up for example) is less than the absolute maximum value specified for  $I_{INJ(RESET)}$  in section 13.2.2 on page 92.

5. When the LVD is enabled, it is mandatory not to to connect a pull-up resistor and a capacitor to V<sub>DD</sub> on the RESET pin.

# **13.10 COMMUNICATION INTERFACE CHARACTERISTICS**

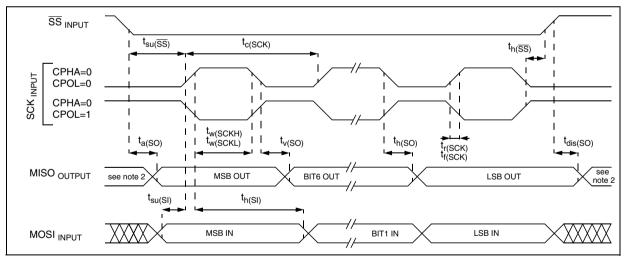

#### 13.10.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{OSC},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                    | Conditions                       | Min                               | Max                          | Unit             |  |

|----------------------------------------------|------------------------------|----------------------------------|-----------------------------------|------------------------------|------------------|--|

| f <sub>SCK =</sub>                           | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128 =<br>0.0625 | f <sub>CPU</sub> /4 =<br>2   | MHz              |  |

| 1/t <sub>c(SCK)</sub>                        | Si i clock irequency         | Slave<br>f <sub>CPU</sub> =8MHz  | 0                                 | f <sub>CPU</sub> /2<br>4     |                  |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time |                                  | see I/O p                         | see I/O port pin description |                  |  |

| t <sub>su(SS)</sub>                          | SS setup time                | Slave                            | 120                               |                              |                  |  |

| t <sub>h(SS)</sub>                           | SS hold time                 | Slave                            | 120                               |                              |                  |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time        | Master<br>Slave                  | 100<br>90                         |                              |                  |  |

| t <sub>su(MI)</sub><br>t <sub>su(SI)</sub>   | Data input setup time        | Master<br>Slave                  | 100<br>100                        |                              |                  |  |

| t <sub>h(MI)</sub><br>t <sub>h(SI)</sub>     | Data input hold time         | Master<br>Slave                  | 100<br>100                        |                              | ns               |  |

| t <sub>a(SO)</sub>                           | Data output access time      | Slave                            | 0                                 | 120                          |                  |  |

| t <sub>dis(SO)</sub>                         | Data output disable time     | Slave                            |                                   | 240                          |                  |  |

| t <sub>v(SO)</sub>                           | Data output valid time       | Slove (after enable adda)        |                                   | 120                          |                  |  |

| t <sub>h(SO)</sub>                           | Data output hold time        | Slave (after enable edge)        | 0                                 |                              | 1                |  |

| t <sub>v(MO)</sub>                           | Data output valid time       | Master (before capture edge)     | 0.25                              |                              | +                |  |

| t <sub>h(MO)</sub>                           | Data output hold time        | waster (before capture edge)     | 0.25                              |                              | t <sub>CPU</sub> |  |

#### Figure 84. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

- 1. Data based on design simulation and/or characterisation results, not tested in production.

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

- 3. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .