Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 15                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flite19f1m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

-

| 10    | ).1  | INTRODUCTION                                     |

|-------|------|--------------------------------------------------|

| 10    |      | FUNCTIONAL DESCRIPTION                           |

| 10    | ).3  | I/O PORT IMPLEMENTATION                          |

| 10    | ).4  | UNUSED I/O PINS                                  |

| 10    | ).5  | LOW POWER MODES                                  |

|       |      | INTERRUPTS                                       |

|       |      | DEVICE-SPECIFIC I/O PORT CONFIGURATION           |

| 11 OI | N-C  | HIP PERIPHERALS                                  |

| 11    | .1   | WATCHDOG TIMER (WDG)                             |

| 11    | .2   | 12-BIT AUTORELOAD TIMER 2 (AT2)                  |

| 11    | .3   | LITE TIMER 2 (LT2)                               |

| 11    | .4   | SERIAL PERIPHERAL INTERFACE (SPI)                |

| 11    | .5   | 10-BIT A/D CONVERTER (ADC)                       |

| 12 IN |      | RUCTION SET                                      |

| 12    | 2.1  | ST7 ADDRESSING MODES                             |

| 12    | 2.2  | INSTRUCTION GROUPS                               |

|       |      | TRICAL CHARACTERISTICS                           |

|       |      | PARAMETER CONDITIONS                             |

| 13    | 8.2  | ABSOLUTE MAXIMUM RATINGS                         |

| 13    | 3.3  | OPERATING CONDITIONS                             |

| 13    | 8.4  | SUPPLY CURRENT CHARACTERISTICS 100               |

| 13    | 8.5  | CLOCK AND TIMING CHARACTERISTICS 102             |

| 13    | 8.6  | MEMORY CHARACTERISTICS 103                       |

| 13    | 8.7  | EMC CHARACTERISTICS 104                          |

| 13    | 8.8  | I/O PORT PIN CHARACTERISTICS 106                 |

| 13    | 8.9  | CONTROL PIN CHARACTERISTICS                      |

| 13    | 8.10 | COMMUNICATION INTERFACE CHARACTERISTICS          |

| 13    | 3.11 | 10-BIT ADC CHARACTERISTICS                       |

| 14 PA | ACK  | AGE CHARACTERISTICS                              |

| 14    | .1   | PACKAGE MECHANICAL DATA 119                      |

| 14    | .2   | SOLDERING AND GLUEABILITY INFORMATION 12         |

| 15 DE | Ξνια | CE CONFIGURATION                                 |

| 15    | 5.1  | OPTION BYTES 122                                 |

| 15    | 5.2  | DEVICE ORDERING INFORMATION 124                  |

| 15    | 5.3  | DEVELOPMENT TOOLS 129                            |

| 15    | 5.4  | ST7 APPLICATION NOTES 120                        |

| -     | -    | RTANT NOTES                                      |

| 16    | 5.1  | EXECUTION OF BTJX INSTRUCTION 129                |

| 16    | 5.2  | ADC CONVERSION SPURIOUS RESULTS 129              |

| 16    | 5.3  | A/ D CONVERTER ACCURACY FOR FIRST CONVERSION 129 |

| 16    | 6.4  | NEGATIVE INJECTION IMPACT ON ADC ACCURACY 129    |

## Table 2. Hardware Register Map

| Address           | Block                              | Register Label | Reset Status                         | Remarks           |                   |

|-------------------|------------------------------------|----------------|--------------------------------------|-------------------|-------------------|

| 0000h             | Dh PADR Port A Data Register       |                | Port A Data Register                 | FFh <sup>1)</sup> | R/W               |

| 0001h             | Port A                             | PADDR          | Port A Data Direction Register       | 00h               | R/W               |

| 0002h             | PAOR                               |                | Port A Option Register               | 40h               | R/W               |

| 0003h             |                                    | PBDR           | Port B Data Register                 | FFh <sup>1)</sup> | R/W               |

| 0004h             | Port B                             | PBDDR          | Port B Data Direction Register       | 00h               | R/W               |

| 0005h             |                                    | PBOR           | Port B Option Register               | 00h               | R/W <sup>2)</sup> |

| 0006h<br>0007h    |                                    | •              | Reserved Area (2 bytes)              |                   |                   |

| 0008h             |                                    | LTCSR2         | Lite Timer Control/Status Register 2 | 0Fh               | R/W               |

| 0009h             | LITE                               | LTARR          | Lite Timer Auto-reload Register      | 00h               | R/W               |

| 000Ah             |                                    | LTCNTR         | Lite Timer Counter Register          | 00h               | Read Only         |

| 000Bh             | TIMER 2                            | LTCSR1         | Lite Timer Control/Status Register 1 | 0X00 0000h        | R/W               |

| 000Ch             |                                    | LTICR          | Lite Timer Input Capture Register    | xxh               | Read Only         |

| 000Dh             |                                    | ATCSR          | Timer Control/Status Register        | 0X00 0000h        | R/W               |

| 000Eh             |                                    | CNTRH          | Counter Register High                | 00h               | Read Only         |

| 000Fh             |                                    | CNTRL          | Counter Register Low                 | 00h               | Read Only         |

| 0010h             |                                    | ATRH           | Auto-Reload Register High            | 00h               | R/W               |

| 0011h             |                                    | ATRL           | Auto-Reload Register Low             | 00h               | R/W               |

| 0012h             |                                    | PWMCR          | PWM Output Control Register          | 00h               | R/W               |

| 0013h             |                                    | PWM0CSR        | PWM 0 Control/Status Register        | 00h               | R/W               |

| 0014h             |                                    | PWM1CSR        | PWM 1 Control/Status Register        | 00h               | R/W               |

| 0015h             |                                    | PWM2CSR        | PWM 2 Control/Status Register        | 00h               | R/W               |

| 0016h             | AUTO-                              | PWM3CSR        | PWM 3 Control/Status Register        | 00h               | R/W               |

| 0017h             | RELOAD                             | DCR0H          | PWM 0 Duty Cycle Register High       | 00h               | R/W               |

| 0018h             | TIMER 2                            | DCR0L          | PWM 0 Duty Cycle Register Low        | 00h               | R/W               |

| 0019h             |                                    | DCR1H          | PWM 1 Duty Cycle Register High       | 00h               | R/W               |

| 001911<br>001Ah   |                                    | DCR1L          | PWM 1 Duty Cycle Register Low        | 00h               | R/W               |

|                   |                                    |                |                                      |                   |                   |

| 001Bh             |                                    | DCR2H          | PWM 2 Duty Cycle Register High       | 00h               | R/W               |

| 001Ch             |                                    | DCR2L          | PWM 2 Duty Cycle Register Low        | 00h               | R/W               |

| 001Dh             |                                    | DCR3H          | PWM 3 Duty Cycle Register High       | 00h               | R/W               |

| 001Eh             |                                    | DCR3L          | PWM 3 Duty Cycle Register Low        | 00h               | R/W               |

| 001Fh             |                                    | ATICRH         | Input Capture Register High          | 00h               | Read Only         |

| 0020h             |                                    | ATICRL         | Input Capture Register Low           | 00h               | Read Only         |

| 0021h             |                                    | TRANCR         | Transfer Control Register            | 01h               | R/W               |

| 0022h             |                                    | BREAKCR        | Break Control Register               | 00h               | R/W               |

| 0023h to<br>002Dh |                                    |                | Reserved area (11 bytes)             |                   |                   |

| 002Eh             | WDG                                | WDGCR          | Watchdog Control Register            | 7Fh               | R/W               |

| 0002Fh            | FLASH                              | FCSR           | Flash Control/Status Register        | 00h               | R/W               |

| 00030h            | EEPROM                             | EECSR          | Data EEPROM Control/Status Register  | 00h               | R/W               |

| 0031h             |                                    | SPIDR          | SPI Data I/O Register                | xxh               | R/W               |

| 0032h             | SPI                                | SPICR          | SPI Control Register                 | 0xh               | R/W               |

| 0033h             | SPICSR SPI Control Status Register |                |                                      | 00h               | R/W               |

| 0034h             |                                    | ADCCSR         | A/D Control Status Register          | 00h               | R/W               |

| 0035h             | ADC                                | ADCDRH         | A/D Data Register High               | xxh               | Read Only         |

|                   |                                    |                | 5 5                                  |                   |                   |

# 7 SUPPLY, RESET AND CLOCK MANAGEMENT

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components.

#### Main features

- Clock Management

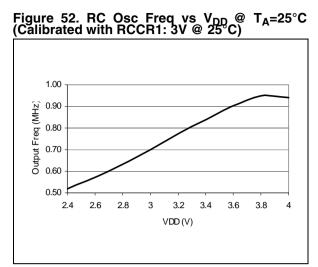

- 1 MHz internal RC oscillator (enabled by option byte, available on ST7LITE15 and ST7LITE19 devices only)

- 1 to 16 MHz or 32kHz External crystal/ceramic resonator (selected by option byte)

- External Clock Input (enabled by option byte)

- PLL for multiplying the frequency by 8 or 4 (enabled by option byte)

- For clock ART counter only: PLL32 for multiplying the 8 MHz frequency by 4 (enabled by option byte). The 8 MHz input frequency is mandatory and can be obtained in the following ways:

- –1 MHz RC + PLLx8

- –16 MHz external clock (internally divided by 2)

- –2 MHz. external clock (internally divided by 2) + PLLx8

- -Crystal oscillator with 16 MHz output frequency (internally divided by 2)

- Reset Sequence Manager (RSM)

- System Integrity Management (SI)

- Main supply Low voltage detection (LVD) with reset generation (enabled by option byte)

- Auxiliary Voltage detector (AVD) with interrupt capability for monitoring the main supply (enabled by option byte)

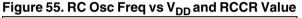

# 7.1 INTERNAL RC OSCILLATOR ADJUSTMENT

The device contains an internal RC oscillator with an accuracy of 1% for a given device, temperature and voltage range (4.5V-5.5V). It must be calibrated to obtain the frequency required in the application. This is done by software writing a calibration value in the RCCR (RC Control Register).

Whenever the microcontroller is reset, the RCCR returns to its default value (FFh), i.e. each time the device is reset, the calibration value must be loaded in the RCCR. Predefined calibration values are stored in EEPROM for 3 and 5V V<sub>DD</sub> supply voltages at 25°C, as shown in the following table.

| RCCR  | Conditions                                                             | ST7LITE19<br>Address | ST7LITE15<br>Address |

|-------|------------------------------------------------------------------------|----------------------|----------------------|

| RCCR0 | V <sub>DD</sub> =5V<br>T <sub>A</sub> =25°C<br>f <sub>RC</sub> =1MHz   | 1000h<br>and FFDEh   | FFDEh                |

| RCCR1 | V <sub>DD</sub> =3V<br>T <sub>A</sub> =25°C<br>f <sub>RC</sub> =700KHz | 1001h<br>and FFDFh   | FFDFh                |

#### Note:

- See "ELECTRICAL CHARACTERISTICS" on page 91. for more information on the frequency and accuracy of the RC oscillator.

- To improve clock stability, it is recommended to place a decoupling capacitor between the  $\rm V_{DD}$  and  $\rm V_{SS}$  pins.

- These two bytes are systematically programmed by ST, including on FASTROM devices. Consequently, customers intending to use FASTROM service must not use these two bytes.

- RCCR0 and RCCR1 calibration values will be erased if the read-out protection bit is reset after it has been set. See "Read out Protection" on page 14.

**Caution:** If the voltage or temperature conditions change in the application, the frequency may need to be recalibrated.

Refer to application note AN1324 for information on how to calibrate the RC frequency using an external reference signal.

# 7.2 PHASE LOCKED LOOP

The PLL can be used to multiply a 1MHz frequency from the RC oscillator or the external clock by 4 or 8 to obtain  $f_{OSC}$  of 4 or 8 MHz. The PLL is enabled and the multiplication factor of 4 or 8 is selected by 2 option bits.

- The x4 PLL is intended for operation with  $V_{DD}$  in the 2.4V to 3.3V range

- The x8 PLL is intended for operation with  $\rm V_{DD}$  in the 3.3V to 5.5V range

Refer to Section 15.1 for the option byte description.

If the PLL is disabled and the RC oscillator is enabled, then  $f_{OSC} = 1MHz$ .

If both the RC oscillator and the PLL are disabled,  $f_{OSC}$  is driven by the external clock.

57

## 7.5 RESET SEQUENCE MANAGER (RSM)

#### 7.5.1 Introduction

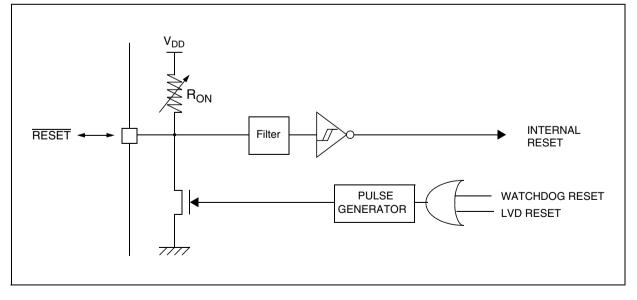

The reset sequence manager includes three RE-SET sources as shown in Figure 14:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

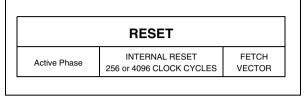

The basic RESET sequence consists of 3 phases as shown in Figure 13:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (see table below)

- RESET vector fetch

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay is automatically selected depending on the clock source chosen by option byte:

| Clock Source                                                         | CPU clock<br>cycle delay |

|----------------------------------------------------------------------|--------------------------|

| Internal RC Oscillator                                               | 256                      |

| External clock (connected to CLKIN pin)                              | 256                      |

| External Crystal/Ceramic Oscillator<br>(connected to OSC1/OSC2 pins) | 4096                     |

#### Figure 14. Reset Block Diagram

5//

The RESET vector fetch phase duration is 2 clock cycles.

If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 11).

#### Figure 13. RESET Sequence Phases

#### 7.5.2 Asynchronous External RESET pin

The  $\overline{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $R_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 15). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

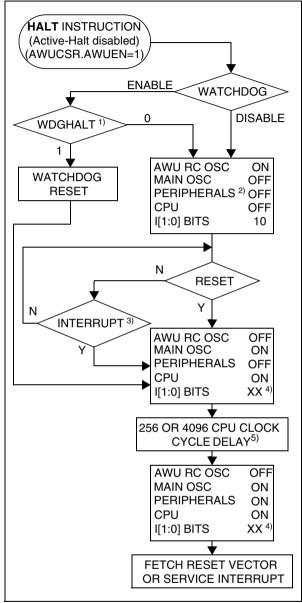

#### POWER SAVING MODES (Cont'd)

#### Similarities with Halt mode

The following AWUFH mode behaviour is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 9.4 HALT MODE).

- When entering AWUFH mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. None of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of Watchdog operation with AWUFH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET.

#### Figure 28. AWUF Halt Timing Diagram

57/

|                     |           | <b>←</b> <sup>†</sup> | t <sub>AWU</sub> | <b>▶</b>                     |             |

|---------------------|-----------|-----------------------|------------------|------------------------------|-------------|

|                     | RUN MODE  | HALT                  | MODE             | 256 OR 4096 t <sub>CPU</sub> | RUN MODE    |

| f <sub>CPU</sub>    |           |                       |                  |                              |             |

| f <sub>AWU_RC</sub> | 2         |                       |                  |                              | Clear       |

| AWUFH               | interrupt |                       |                  |                              | by software |

#### POWER SAVING MODES (Cont'd)

#### Notes:

**1.** WDGHALT is an option bit. See option byte section for more details.

**2.** Peripheral clocked with an external clock source can still be active.

**3.** Only an AWUFH interrupt and some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 5, "Interrupt Mapping," on page 35 for more details.

**4.** Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

**5.** If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 11).

# 10 I/O PORTS

#### **10.1 INTRODUCTION**

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

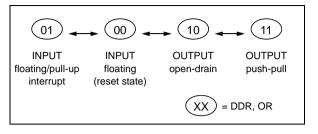

#### **10.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

Figure 30 shows the generic I/O block diagram.

#### 10.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

#### Notes:

1. Writing to the DR modifies the latch value but does not change the state of the input pin.

2. Do not use read/modify/write instructions (BSET/BRES) to modify the DR register.

#### **External Interrupt Function**

Depending on the device, setting the ORx bit while in input mode can configure an I/O as an input with interrupt. In this configuration, a signal edge or level input on the I/O generates an interrupt request via the corresponding interrupt vector (eix).

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) or the Miscellaneous Register controls this sensitivity, depending on the device. External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Modifying the sensitivity bits will clear any pending interrupts.

#### 10.2.2 Output Modes

Setting the DDRx bit selects output mode. Writing to the DR bits applies a digital value to the I/O through the latch. Reading the DR bits returns the previously stored value.

If an OR bit is available, different output modes can be selected by software: push-pull or opendrain. Refer to I/O Port Implementation section for configuration.

| DR Value ar | nd Output Pin Status | ; |

|-------------|----------------------|---|

|             |                      |   |

|   | DR | Push-Pull       | Open-Drain      |

|---|----|-----------------|-----------------|

| ſ | 0  | V <sub>OL</sub> | V <sub>OL</sub> |

|   | 1  | V <sub>OH</sub> | Floating        |

#### **10.2.3 Alternate Functions**

Many ST7s I/Os have one or more alternate functions. These may include output signals from, or input signals to, on-chip peripherals. The Device Pin Description table describes which peripheral signals can be input/output to which ports.

A signal coming from an on-chip peripheral can be output on an I/O. To do this, enable the on-chip peripheral as an output (enable bit in the peripheral's control register). The peripheral configures the I/O as an output and takes priority over standard I/ O programming. The I/O's state is readable by addressing the corresponding I/O data register.

Configuring an I/O as floating enables alternate function input. It is not recommended to configure an I/O as pull-up as this will increase current consumption. Before using an I/O as an alternate input, configure it without interrupt. Otherwise spurious interrupts can occur.

Configure an I/O as input floating for an on-chip peripheral signal which can be input and output.

#### Caution:

I/Os which can be configured as both an analog and digital alternate function need special attention. The user must control the peripherals so that the signals do not arrive at the same time on the same pin. If an external clock is used, only the clock alternate function should be employed on that I/O pin and not the other alternate function.

#### I/O PORTS (Cont'd)

#### Analog alternate function

Configure the I/O as floating input to use an ADC input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail, connected to the ADC input.

#### **Analog Recommendations**

Do not change the voltage level or loading on any I/O while conversion is in progress. Do not have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

#### **10.3 I/O PORT IMPLEMENTATION**

57/

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific I/O port features such as ADC input or open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 31. Other transitions are potentially risky and should be avoided, since they may present unwanted side-effects such as spurious interrupt generation.

#### Figure 31. Interrupt I/O Port State Transitions

#### **10.4 UNUSED I/O PINS**

Unused I/O pins must be connected to fixed voltage levels. Refer to Section 13.8.

#### **10.5 LOW POWER MODES**

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |

#### **10.6 INTERRUPTS**

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and if the I bit in the CC register is cleared (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit |     | Exit<br>from<br>Halt |  |

|-----------------------------------------------|---------------|--------------------------|-----|----------------------|--|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes | Yes                  |  |

# WATCHDOG TIMER (Cont'd)

#### 11.1.5 Interrupts

None.

# 11.1.6 Register Description CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled 1: Watchdog enabled

1. Watchuog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte. Bit 6:0 = **T[6:0]** 7-bit timer (MSB to LSB). These bits contain the decremented value. A reset is produced when it rolls over from 40h to 3Fh (T6

is produced when it rolls over from 40h to 3Fh (16 becomes cleared).

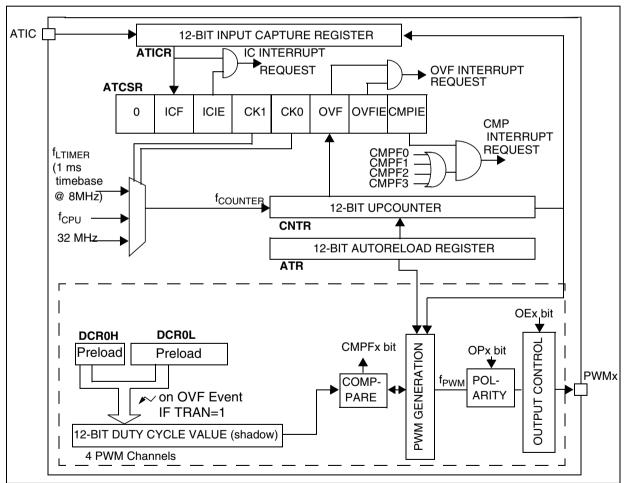

# 11.2 12-BIT AUTORELOAD TIMER 2 (AT2)

#### 11.2.1 Introduction

The 12-bit Autoreload Timer can be used for general-purpose timing functions. It is based on a freerunning 12-bit upcounter with an input capture register and four PWM output channels. There are 6 external pins:

- Four PWM outputs

- ATIC pin for the Input Capture function

- BREAK pin for forcing a break condition on the PWM outputs

#### 11.2.2 Main Features

57

12-bit upcounter with 12-bit autoreload register (ATR)

- Maskable overflow interrupt

- Generation of four independent PWMx signals

- Frequency 2KHz-4MHz (@ 8 MHz f<sub>CPU</sub>)

- Programmable duty-cycles

- Polarity control

- Programmable output modes

- Maskable Compare interrupt

- Input Capture

- 12-bit input capture register (ATICR)

- Triggered by rising and falling edges

- Maskable IC interrupt

#### Figure 33. Block Diagram

LITE TIMER (Cont'd)

# LITE TIMER COUNTER 2 (LTCNTR)

Read only Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| CNT7 | CNT7 | CNT7 | CNT7 | CNT3 | CNT2 | CNT1 | CNT0 |

Bits 7:0 = CNT[7:0] Counter 2 Reload Value. This register is read by software. The LTARR value is automatically loaded into Counter 2 (LTCN-TR) when an overflow occurs.

#### LITE TIMER CONTROL/STATUS REGISTER (LTCSR1)

Read / Write

Reset Value: 0x00 0000 (x0h)

| 7    |     |    |       |      |   |   | 0 |

|------|-----|----|-------|------|---|---|---|

| ICIE | ICF | ТВ | TB1IE | TB1F | - | - | - |

#### Bit 7 = ICIE Interrupt Enable.

This bit is set and cleared by software. 0: Input Capture (IC) interrupt disabled

1: Input Capture (IC) interrupt enabled

#### Bit 6 = **ICF** Input Capture Flag.

This bit is set by hardware and cleared by software by reading the LTICR register. Writing to this bit does not change the bit value.

0: No input capture

1: An input capture has occurred

Note: After an MCU reset, software must initialise the ICF bit by reading the LTICR register

#### Bit 5 = **TB** Timebase period selection.

This bit is set and cleared by software.

- 0: Timebase period =  $t_{OSC} * 8000 (1ms @ 8 MHz)$ 1: Timebase period =  $t_{OSC} * 16000 (2ms @ 8$

- MHz)

Bit 4 = **TB1IE** *Timebase Interrupt enable.* This bit is set and cleared by software. 0: Timebase (TB1) interrupt disabled

1: Timebase (TB1) interrupt enabled

#### Bit 3 = **TB1F** Timebase Interrupt Flag.

This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

0: No counter overflow

1: A counter overflow has occurred

#### Bits 2:0 = Reserved

# LITE TIMER INPUT CAPTURE REGISTER (LTICR)

Read only

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |  |

|------|------|------|------|------|------|------|------|--|

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |  |

#### Bits 7:0 = ICR[7:0] Input Capture Value

These bits are read by software and cleared by hardware after a reset. If the ICF bit in the LTCSR is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

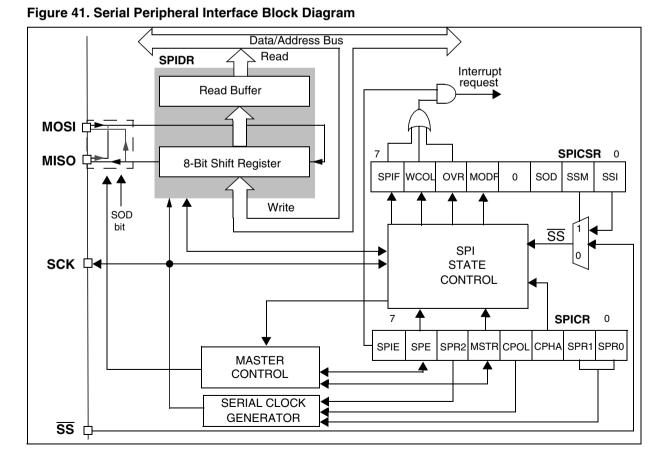

# **11.4 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 11.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### 11.4.3 General Description

Figure 41 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 3 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 11.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the Device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the Device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

# 11.4.6.1 Using the SPI to wake-up the Device from Halt mode

In slave configuration, the SPI is able to wake-up the Device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

**Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake-up the Device from Halt mode only if the Slave Select signal (external

57/

SS pin or the SSI bit in the SPICSR register) is low when the Device enters Halt mode. So if Slave selection is configured as external (see Section 11.4.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

#### 11.4.7 Interrupts

| Interrupt Event                | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Trans-<br>fer Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode<br>Fault Event     | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                  | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# INSTRUCTION GROUPS (Cont'd)

57

| Mnemo | Description                | Function/Example    | Dst    | Src | н | I | Ν | Z | С |

|-------|----------------------------|---------------------|--------|-----|---|---|---|---|---|

| ADC   | Add with Carry             | A = A + M + C       | А      | М   | Н |   | Ν | Z | С |

| ADD   | Addition                   | A = A + M           | А      | М   | Н |   | Ν | Z | С |

| AND   | Logical And                | A = A . M           | А      | М   |   |   | Ν | Z |   |

| BCP   | Bit compare A, Memory      | tst (A . M)         | А      | М   |   |   | Ν | Z |   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |   |   |   |   |   |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| CALL  | Call subroutine            |                     |        |     |   |   |   |   |   |

| CALLR | Call subroutine relative   |                     |        |     |   |   |   |   |   |

| CLR   | Clear                      |                     | reg, M |     |   |   | 0 | 1 |   |

| СР    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |   |   | Ν | Z | С |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |   |   | Ν | Z | 1 |

| DEC   | Decrement                  | dec Y               | reg, M |     |   |   | Ν | Z |   |

| HALT  | Halt                       |                     |        |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     | Н | Ι | Ν | Z | С |

| INC   | Increment                  | inc X               | reg, M |     |   |   | Ν | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |   |   |   |   |   |

| JRA   | Jump relative always       |                     |        |     |   |   |   |   |   |

| JRT   | Jump relative              |                     |        |     |   |   |   |   |   |

| JRF   | Never jump                 | jrf *               |        |     |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |   |   |   |   |   |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |   |   |   |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |   |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |   |   |   |   |   |

| JRNC  | Jump if C = 0              | C = 0 ?             |        |     |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |   |   |   |   |   |

| JRUGE | Jump if C = 0              | Jmp if unsigned >=  |        |     |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |   |   |   |   |   |

#### **13.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### **13.2.1 Voltage Characteristics**

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                            | Maximum value                  | Unit |

|-----------------------------------|----------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | Supply voltage                                     | 7.0                            | V    |

| V <sub>IN</sub>                   | Input voltage on any pin <sup>1) &amp; 2)</sup>    | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 | v    |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (Human Body Model) | see section 13.7.3 on page 104 | V    |

#### **13.2.2 Current Characteristics**

| Symbol                        | Ratings                                                                | Maximum value | Unit |

|-------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>              | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  | 100           |      |

| I <sub>VSS</sub>              | Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> | 100           |      |

|                               | Output current sunk by any standard I/O and control pin                | 25            |      |

| I <sub>IO</sub>               | Output current sunk by any high sink I/O pin                           | 50            |      |

|                               | Output current source by any I/Os and control pin                      | - 25          | mA   |

|                               | Injected current on RESET pin                                          | ± 5           | mA   |

| 2) & 4)                       | Injected current on OSC1 and OSC2 pins                                 | ± 5           |      |

| I <sub>INJ(PIN)</sub> 2) & 4) | Injected current on PB0 and PB1 pins 5)                                | +5            |      |

|                               | Injected current on any other pin 6)                                   | ± 5           |      |

| $\Sigma I_{INJ(PIN)}^{2)}$    | Total injected current (sum of all I/O and control pins) <sup>6)</sup> | ± 20          |      |

#### **13.2.3 Thermal Characteristics**

| Symbol           | Ratings Value                                                                       |             | Unit |  |  |

|------------------|-------------------------------------------------------------------------------------|-------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range                                                           | -65 to +150 | °C   |  |  |

| TJ               | Maximum junction temperature (see Table 21, "THERMAL CHARACTERISTICS," on page 119) |             |      |  |  |

#### Notes:

1. Directly connecting the I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 10k $\Omega$  for I/Os). Unused I/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the analog voltage is lower than the specified limits)

- Pure digital pins must have a negative injection less than 1.6mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

5. No negative current injection allowed on PB0 and PB1 pins.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

#### **OPERATING CONDITIONS** (Cont'd)

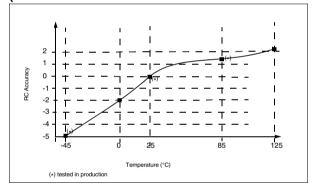

# Figure 54. Typical RC oscillator Accuracy vs temperature @ $V_{DD}$ =5V (Calibrated with RCCR0: 5V @ 25°C

57

Figure 53. RC Osc Freq vs V<sub>DD</sub> (Calibrated with RCCR0: 5V@ 25°C) 1.10 1.00 0.90 - -45° (THW) 0.70 **—**0° 0.70 0.60 0.50 0.40 0.30 - 25° . × 90° <del>ж</del> 105° •— 130° 0.20 0.10 0.00 2.5 3 3.5 4 4.5 5 5.5 6 Vdd (V)

#### EMC CHARACTERISTICS (Cont'd)

# 13.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### **Absolute Maximum Ratings**

#### 13.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard.

| Symbol                | Ratings                                                | Conditions            | Maximum value <sup>1)</sup> | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|-----------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 4000                        | V    |

#### Notes:

1. Data based on characterization results, not tested in production.

#### 13.7.3.2 Static and Dynamic Latch-Up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- DLU: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter              | Conditions                                                    | Class <sup>1)</sup> |

|--------|------------------------|---------------------------------------------------------------|---------------------|

| LU     | Static latch-up class  | T <sub>A</sub> =+25°C                                         | А                   |

| DLU    | Dynamic latch-up class | $V_{DD}$ =5.5V, f <sub>OSC</sub> =4MHz, T <sub>A</sub> =+25°C | А                   |

#### Notes:

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

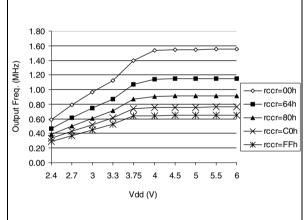

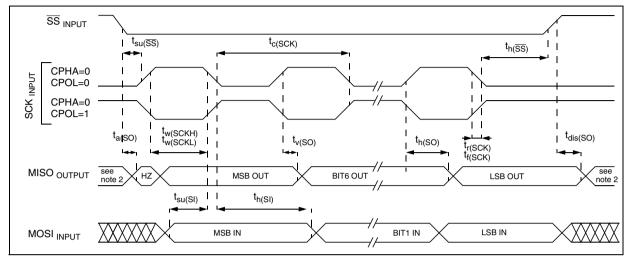

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

#### Figure 85. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

#### Figure 86. SPI Master Timing Diagram <sup>1)</sup>

#### Notes:

<u>/</u>ک

1. Measurement points are done at CMOS levels:  $0.3 x V_{DD}$  and  $0.7 x V_{DD}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

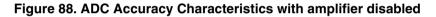

# ADC CHARACTERISTICS (Cont'd)

#### ADC Accuracy with V<sub>DD</sub>=5.0V

| Symbol         | Parameter                                  | Conditions                                                                              | Тур | Max | Unit |

|----------------|--------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|------|

| E <sub>T</sub> | Total unadjusted error <sup>2)</sup>       |                                                                                         | 3   | 6   |      |

| E <sub>O</sub> | Offset error <sup>2)</sup>                 |                                                                                         | 1.5 | 5   |      |

|                | Gain Error <sup>2)</sup>                   | f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz <sup>1)</sup> ,<br>V <sub>DD</sub> =5.0V | 2   | 4.5 | LSB  |

| E <sub>D</sub> | Differential linearity error <sup>2)</sup> | • DD-0.0 •                                                                              | 2.5 | 4.5 |      |

| E <sub>L</sub> | Integral linearity error <sup>2)</sup>     |                                                                                         | 2.5 | 4.5 |      |

#### Notes:

57

1) Data based on characterization results over the whole temperature range, monitored in production.

2) Injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input.

Analog pins can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 13.8 does not affect the ADC accuracy.

#### **15.3 DEVELOPMENT TOOLS**

STMicroelectronics offers a range of hardware and software development tools for the ST7 microcontroller family. Full details of tools available for the ST7 from third party manufacturers can be obtained from the STMicroelectronics Internet site: http://www.st.com.

Tools from these manufacturers include C compliers, evaluation tools, emulators and programmers.

#### Emulators

Two types of emulators are available from ST for the ST7LITE1 family:

- ST7 DVP3 entry-level emulator offers a flexible and modular debugging and programming solution. SO20 packages need a specific connection kit (refer to Table 25)

- ST7 EMU3 high-end emulator is delivered with everything (probes, TEB, adapters etc.) needed to start emulating the ST7LITE1. To configure it to emulate other ST7 subfamily devices, the active probe for the ST7EMU3 can be changed and the ST7EMU3 probe is designed for easy interchange of TEBs (Target Emulation Board). See Table 25.

#### In-circuit Debugging Kit

Two configurations are available from ST:

- ST7FLIT2-IND/USB: Low-cost In-Circuit Debugging kit from Softec Microsystems. Includes STX-InDART/USB board (USB port) (A promotion package of 15 STFLIT2-IND/USB can be ordered with the following order code: STFLIT2-IND/15)

- STxF-INDART/USB (A promotion package of 15 STxF-INDART/USB can be ordered with the following order code: STxF-INDART)

#### Flash Programming tools

- ST7-STICK ST7 In-circuit Communication Kit, a complete software/hardware package for programming ST7 Flash devices. It connects to a host PC parallel port and to the target board or socket board via ST7 ICC connector.

- ICC Socket Boards provide an easy to use and flexible means of programming ST7 Flash devices. They can be connected to any tool that supports the ST7 ICC interface, such as ST7 EMU3, ST7-DVP3, inDART, ST7-STICK, or many third-party development tools.

#### **Evaluation boards**

One evaluation tool is available from ST:

ST7FLIT2-COS/COM: STReal time starter kit from Cosmic software for ST7FLITE2 and ST7FLITE1

|                                        |                 | Programming         |               |                          |                           |

|----------------------------------------|-----------------|---------------------|---------------|--------------------------|---------------------------|

| Supported                              | ST7 DVP3 Series |                     | ST7 EMU       |                          |                           |

| Products                               | Emulator        | Connection kit      | Emulator      | Active Probe &<br>T.E.B. | ICC Socket Board          |

| ST7FLITE10<br>ST7FLITE15<br>ST7FLITE19 | ST7MDT10-DVP3   | ST7MDT10-20/<br>DVP | ST7MDT10-EMU3 | ST7MDT10-TEB             | ST7SB10/123 <sup>1)</sup> |

Table 25. STMicroelectronics Development Tools

Note 1: Add suffix /EU, /UK, /US for the power supply of your region.