# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 520                                                                       |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 49                                                                        |

| Number of Gates                | 20000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 68-VFQFN Exposed Pad                                                      |

| Supplier Device Package        | 68-QFN (8x8)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln020v2-qng68 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Timing Characteristics

### Applies to 1.5 V DC Core Voltage

Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | DOUT | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97 | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 4 mA           | STD         | 0.97 | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 6 mA           | STD         | 0.97 | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

| 8 mA           | STD         | 0.97 | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | DOUT | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97 | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 4 mA           | STD         | 0.97 | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 6 mA           | STD         | 0.97 | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

| 8 mA           | STD         | 0.97 | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Microsemi

IGLOO nano DC and Switching Characteristics

## Microsemi

IGLOO nano DC and Switching Characteristics

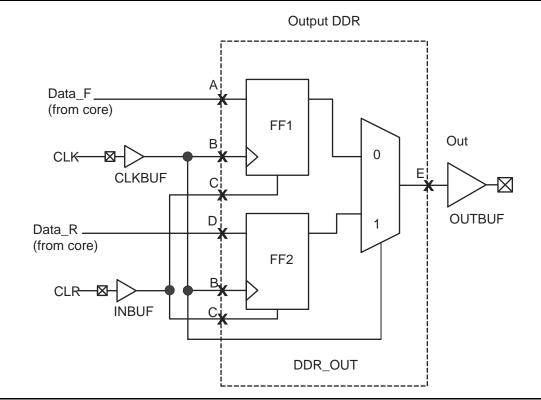

### Output DDR Module

| Table 2-81 • Pa | arameter Definitions |

|-----------------|----------------------|

|-----------------|----------------------|

| Parameter Name                          | Parameter Defini tion     | Measuring No des (from, to) |  |  |

|-----------------------------------------|---------------------------|-----------------------------|--|--|

| t <sub>DDROCLKQ</sub>                   | Clock-to-Out              | B, E                        |  |  |

| t <sub>DDROCLR2Q</sub>                  | Asynchronous Clear-to-Out | C, E                        |  |  |

| t <sub>DDROREMCLR</sub>                 | Clear Removal             | С, В                        |  |  |

| DDRORECCLR Clear Recovery               |                           | С, В                        |  |  |

| t <sub>DDROSUD1</sub>                   | Data Setup Data_F         | А, В                        |  |  |

| t <sub>DDROSUD2</sub> Data Setup Data_R |                           | D, B                        |  |  |

| tDDROHD1                                | Data Hold Data_F          | A, B                        |  |  |

| t <sub>DDROHD2</sub>                    | Data Hold Data_R          | D, B                        |  |  |

# VersaTile Characteristics

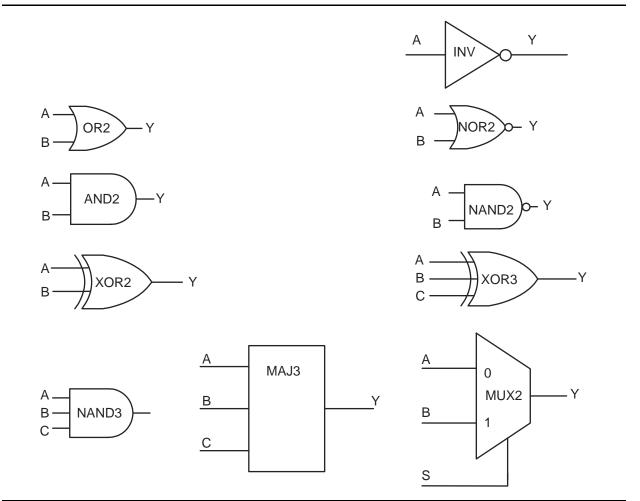

### VersaTile Specifications as a Combinatorial Module

The IGLOO nano library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide for Software v10.1.

Figure 2-21 • Sample of Combinatorial Cells

IGLOO nano DC and Switching Characteristics

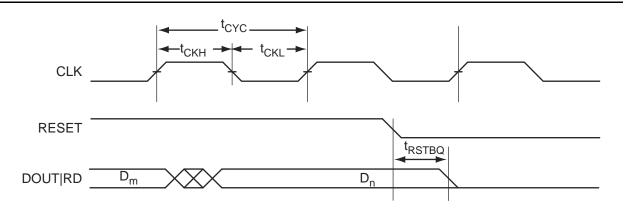

Figure 2-32 • RAM Reset. Applicable to Both RAM4K9 and RAM512x18.

# **Embedded FlashROM Characteristics**

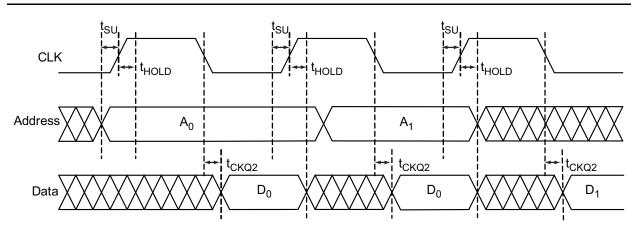

Figure 2-41 • Timing Diagram

### **Timing Characteristics**

1.5 V DC Core Voltage

### Table 2-108 • Embedded FlashROM Access Time Worst Commercial-Case Conditions: T $_{J} = 70^{\circ}$ C, VCC = 1.425 V

| Parameter         | Description             | Std.  | Units |

|-------------------|-------------------------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.57  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 20.90 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 15    | MHz   |

1.2 V DC Core Voltage

### Table 2-109 • Embedded FlashROM Access Time

Worst Commercial-Case Conditions: T  $_{J}$  = 70°C, VCC = 1.14 V

| Parameter         | Description             | Std.  | Units |

|-------------------|-------------------------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.59  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 35.74 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 10    | MHz   |

## Microsemi

Package Pin Assignments

|            | CS81              |                 | CS81              |

|------------|-------------------|-----------------|-------------------|

| Pin Number | AGLN060Z Function | Pin Number      | AGLN060Z Function |

| A1         | GAA0/IO02RSB0     | D8              | GCC1/IO35RSB0     |

| A2         | GAA1/IO03RSB0     | D9              | GCC0/IO36RSB0     |

| A3         | GAC0/IO06RSB0     | E1              | GFB0/IO83RSB1     |

| A4         | IO09RSB0          | E2              | GFB1/IO84RSB1     |

| A5         | IO13RSB0          | E3              | GFA1/IO81RSB1     |

| A6         | IO18RSB0          | E4              | VCCIB1            |

| A7         | GBB0/IO21RSB0     | E5              | VCC               |

| A8         | GBA1/IO24RSB0     | E6              | VCCIB0            |

| A9         | GBA2/IO25RSB0     | E7              | GCA1/IO39RSB0     |

| B1         | GAA2/IO95RSB1     | E8              | GCA0/IO40RSB0     |

| B2         | GAB0/IO04RSB0     | E9              | GCB2/IO42RSB0     |

| B3         | GAC1/IO07RSB0     | F1 <sup>1</sup> | VCCPLF            |

| B4         | IO08RSB0          | F2 <sup>1</sup> | VCOMPLF           |

| B5         | IO15RSB0          | F3              | GND               |

| B6         | GBC0/IO19RSB0     | F4              | GND               |

| B7         | GBB1/IO22RSB0     | F5              | VCCIB1            |

| B8         | IO26RSB0          | F6              | GND               |

| B9         | GBB2/IO27RSB0     | F7              | GDA1/IO49RSB0     |

| C1         | GAB2/IO93RSB1     | F8              | GDC1/IO45RSB0     |

| C2         | IO94RSB1          | F9              | GDC0/IO46RSB0     |

| C3         | GND               | G1              | GEA0/IO69RSB1     |

| C4         | IO10RSB0          | G2              | GEC1/IO74RSB1     |

| C5         | IO17RSB0          | G3              | GEB1/IO72RSB1     |

| C6         | GND               | G4              | IO63RSB1          |

| C7         | GBA0/IO23RSB0     | G5              | IO60RSB1          |

| C8         | GBC2/IO29RSB0     | G6              | IO54RSB1          |

| C9         | IO31RSB0          | G7              | GDB2/IO52RSB1     |

| D1         | GAC2/IO91RSB1     | G8              | VJTAG             |

| D2         | IO92RSB1          | G9              | TRST              |

| D3         | GFA2/IO80RSB1     | H1              | GEA1/IO70RSB1     |

| D4         | VCC               | H2              | FF/GEB2/IO67RSB1  |

| D5         | VCCIB0            | H3              | IO65RSB1          |

| D6         | GND               | H4              | IO62RSB1          |

| D7         | GCC2/IO43RSB0     | H5              | IO59RSB1          |

| CS81            |                   |  |  |  |

|-----------------|-------------------|--|--|--|

| Pin Number      | AGLN060Z Function |  |  |  |

| H6              | IO56RSB1          |  |  |  |

| H7 <sup>2</sup> | GDA2/IO51RSB1     |  |  |  |

| H8              | TDI               |  |  |  |

| H9              | TDO               |  |  |  |

| J1              | GEA2/IO68RSB1     |  |  |  |

| J2              | GEC2/IO66RSB1     |  |  |  |

| J3              | IO64RSB1          |  |  |  |

| J4              | IO61RSB1          |  |  |  |

| J5              | IO58RSB1          |  |  |  |

| J6              | IO55RSB1          |  |  |  |

| J7              | ТСК               |  |  |  |

| J8              | TMS               |  |  |  |

| J9              | VPUMP             |  |  |  |

### Notes:

1. Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN060Z-CS81.

2. The bus hold attribute (hold previous I/O state in Flash\*Freeze mode) is not supported for pin H7 in AGLN060Z-CS81.