Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

ĿXFI

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 1536                                                                       |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 60                                                                         |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 81-WFBGA, CSBGA                                                            |

| Supplier Device Package        | 81-CSP (5x5)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln060v2-csg81i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

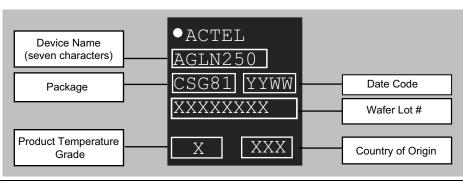

### **Device Marking**

Microsemi normally topside marks the full ordering part number on each device. There are some exceptions to this, such as some of the Z feature grade nano devices, the V2 designator for IGLOO devices, and packages where space is physically limited. Packages that have limited characters available are UC36, UC81, CS81, QN48, QN68, and QFN132. On these specific packages, a subset of the device marking will be used that includes the required legal information and as much of the part number as allowed by character limitation of the device. In this case, devices will have a truncated device marking and may exclude the applications markings, such as the I designator for Industrial Devices or the ES designator for Engineering Samples.

Figure 1 shows an example of device marking based on the AGLN250V2-CSG81. The actual mark will vary by the device/package combination ordered.

Figure 1 • Example of Device Marking for Small Form Factor Packages

# 2 – IGLOO nano DC and Switching Characteristics

### **General Specifications**

The Z feature grade does not support the enhanced nano features of Schmitt trigger input, Flash\*Freeze bus hold (hold previous I/O state in Flash\*Freeze mode), cold-sparing, and hot-swap I/O capability. Refer to "IGLOO nano Ordering Information" on page IV for more information.

### **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

| Symbol                        | Parameter                    | Limits          | Units |

|-------------------------------|------------------------------|-----------------|-------|

| VCC                           | DC core supply voltage       | -0.3 to 1.65    | V     |

| VJTAG                         | JTAG DC voltage              | -0.3 to 3.75    | V     |

| VPUMP                         | Programming voltage          | -0.3 to 3.75    | V     |

| VCCPLL                        | Analog power supply (PLL)    | -0.3 to 1.65    | V     |

| VCCI                          | DC I/O buffer supply voltage | -0.3 to 3.75    | V     |

| VI <sup>1</sup>               | I/O input voltage            | –0.3 V to 3.6 V | V     |

| T <sub>STG</sub> <sup>2</sup> | Storage temperature          | -65 to +150     | °C    |

| T <sub>J</sub> <sup>2</sup>   | Junction temperature         | +125            | °C    |

Table 2-1 •

Absolute Maximum Ratings

Notes:

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-4 on page 2-3.

<sup>2.</sup> For flash programming and retention maximum limits, refer to Table 2-3 on page 2-2, and for recommended operating limits, refer to Table 2-2 on page 2-2.

| VCCI          | Average VCCI–GND Overshoot or<br>Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                                 | 1.4 V                                         |

|               | 5%                                                                                                  | 1.49 V                                        |

| 3 V           | 10%                                                                                                 | 1.1 V                                         |

|               | 5%                                                                                                  | 1.19 V                                        |

| 3.3 V         | 10%                                                                                                 | 0.79 V                                        |

|               | 5%                                                                                                  | 0.88 V                                        |

| 3.6 V         | 10%                                                                                                 | 0.45 V                                        |

|               | 5%                                                                                                  | 0.54 V                                        |

#### Table 2-4 • Overshoot and Undershoot Limits <sup>1</sup>

Notes:

1. Based on reliability requirements at 85°C.

The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO nano device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4.

There are five regions to consider during power-up.

IGLOO nano I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### VCCI Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

### VCC Trip Point:

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.1 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.0 V Ramping up (V2 devices): 0.65 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.55 V < trip\_point\_down < 0.95 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

| Table 2-17 • | Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices |

|--------------|--------------------------------------------------------------------------------------|

|              | For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage                                 |

|           |                                                                   | [         | Device-Spe                 | cific Dyna   | mic Power   | r (µW/MHz) |         |

|-----------|-------------------------------------------------------------------|-----------|----------------------------|--------------|-------------|------------|---------|

| Parameter | Definition                                                        | AGLN250   | AGLN125                    | AGLN060      | AGLN020     | AGLN015    | AGLN010 |

| PAC1      | Clock contribution of a Global Rib                                | 2.829     | 2.875                      | 1.728        | 0           | 0          | 0       |

| PAC2      | Clock contribution of a Global Spine                              | 1.731     | 1.265                      | 1.268        | 2.562       | 2.562      | 1.685   |

| PAC3      | Clock contribution of a VersaTile row                             | 0.957     | 0.963                      | 0.967        | 0.862       | 0.862      | 0.858   |

| PAC4      | Clock contribution of a VersaTile used<br>as a sequential module  | 0.098     | 0.098                      | 0.098        | 0.094       | 0.094      | 0.091   |

| PAC5      | First contribution of a VersaTile used<br>as a sequential module  | 0.045     |                            |              |             |            |         |

| PAC6      | Second contribution of a VersaTile<br>used as a sequential module | 0.186     |                            |              |             |            |         |

| PAC7      | Contribution of a VersaTile used as a combinatorial module        |           |                            | 0.1          | 11          |            |         |

| PAC8      | Average contribution of a routing net                             |           |                            | 0.4          | 15          |            |         |

| PAC9      | Contribution of an I/O input pin (standard-dependent)             |           | See                        | e Table 2-13 | 3 on page 2 | 2-9        |         |

| PAC10     | Contribution of an I/O output pin<br>(standard-dependent)         |           | See Table 2-14 on page 2-9 |              |             |            |         |

| PAC11     | Average contribution of a RAM block<br>during a read operation    | 25.00 N/A |                            |              |             |            |         |

| PAC12     | Average contribution of a RAM block<br>during a write operation   | 30.00 N/A |                            |              |             |            |         |

| PAC13     | Dynamic contribution for PLL                                      |           | 2.10                       |              |             | N/A        |         |

# Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|                   |                                                       |                            | Device-Specific Static Power (mW) |         |         |         |         |

|-------------------|-------------------------------------------------------|----------------------------|-----------------------------------|---------|---------|---------|---------|

| Parameter         | Definition                                            | AGLN250                    | AGLN125                           | AGLN060 | AGLN020 | AGLN015 | AGLN010 |

| PDC1              | Array static power in Active mode                     |                            | See Table 2-12 on page 2-8        |         |         |         |         |

| PDC2              | Array static power in Static (Idle)<br>mode           |                            | See Table 2-12 on page 2-8        |         |         |         |         |

| PDC3              | Array static power in Flash*Freeze<br>mode            |                            | See Table 2-9 on page 2-7         |         |         |         |         |

| PDC4 <sup>1</sup> | Static PLL contribution                               | 0.90 N/A                   |                                   |         |         |         |         |

| PDC5              | Bank quiescent power<br>(VCCI-dependent) <sup>2</sup> | See Table 2-12 on page 2-8 |                                   |         |         |         |         |

Notes:

1. Minimum contribution of the PLL when running at lowest frequency.

2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

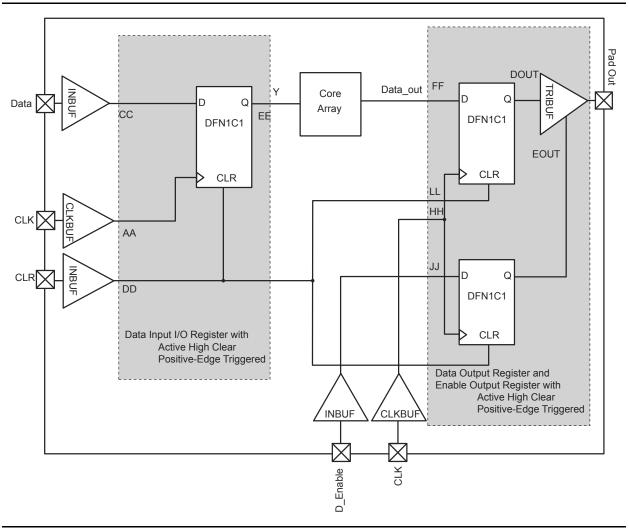

Fully Registered I/O Buffers with Asynchronous Clear

Figure 2-13 • Timing Model of the Registered I/O Buffers with Asynchronous Clear

### Microsemi

IGLOO nano DC and Switching Characteristics

#### 1.2 V DC Core Voltage

# Table 2-83 • Output DDR Propagation Delays<br/>Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V

| Parameter               | Description                                           | Std.   | Units |

|-------------------------|-------------------------------------------------------|--------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 1.60   | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 1.09   | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 1.16   | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00   | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00   | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 1.99   | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00   | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.24   | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.19   | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output DDR     | 0.31   | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output DDR      | 0.28   | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 160.00 | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### **VersaTile Characteristics**

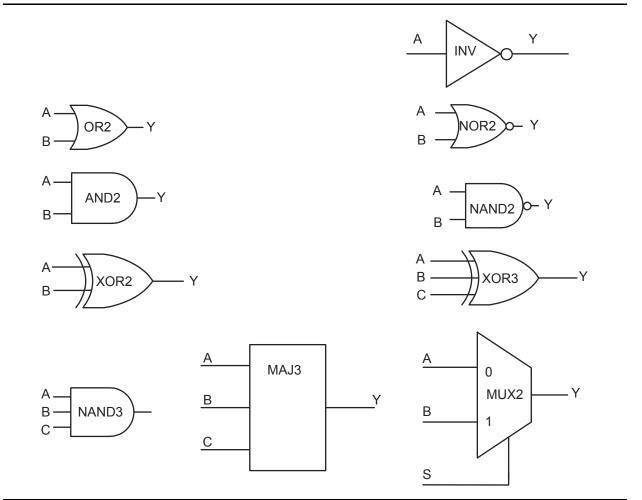

### VersaTile Specifications as a Combinatorial Module

The IGLOO nano library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide for Software v10.1*.

Figure 2-21 • Sample of Combinatorial Cells

# Table 2-90 •AGLN020 Global Resource<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.21              | 1.55              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.23              | 1.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.42              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-91 • AGLN060 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.32              | 1.62              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.34              | 1.71              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.38              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### *Microsemi*.

IGLOO nano DC and Switching Characteristics

# Table 2-92 •AGLN125 Global Resource<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.36              | 1.71              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.39              | 1.82              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-93 • AGLN250 Global Resource

| <b>Commercial-Case Conditio</b> | ons: T <sub>J</sub> = 70°C, VCC = 1.425 V |

|---------------------------------|-------------------------------------------|

|---------------------------------|-------------------------------------------|

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.39              | 1.73              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.41              | 1.84              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.43              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

# Table 2-94 •AGLN010 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | 5                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.71              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.78              | 2.31              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.53              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-95 • AGLN015 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

# Table 2-98 • AGLN125 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.08              | 2.54              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.15              | 2.77              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## Table 2-99 • AGLN250 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.11              | 2.57              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.19              | 2.81              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

| Table 2-101 • IGLOO nano CCC/PLL Specification          |  |

|---------------------------------------------------------|--|

| For IGLOO nano V2 Devices, 1.2 V DC Core Supply Voltage |  |

| Parameter                                                               |                 | Min.                       | Тур.                | Max.                          | Units               |

|-------------------------------------------------------------------------|-----------------|----------------------------|---------------------|-------------------------------|---------------------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC                    | 1.5             |                            | 160                 | MHz                           |                     |

| Clock Conditioning Circuitry Output Frequency fOUT_CC                   | 0.75            |                            | 160                 | MHz                           |                     |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>           |                 |                            | 580 <sup>3</sup>    |                               | ps                  |

| Number of Programmable Values in Each Programmab                        | le Delay Block  |                            |                     | 32                            |                     |

| Serial Clock (SCLK) for Dynamic PLL <sup>4,9</sup>                      |                 |                            |                     | 60                            |                     |

| Input Cycle-to-Cycle Jitter (peak magnitude)                            |                 |                            |                     | 0.25                          | ns                  |

| Acquisition Time                                                        |                 |                            |                     |                               |                     |

|                                                                         | LockControl = 0 |                            |                     | 300                           | μs                  |

|                                                                         | LockControl = 1 |                            |                     | 6.0                           | ms                  |

| Tracking Jitter <sup>5</sup>                                            |                 |                            |                     |                               |                     |

|                                                                         | LockControl = 0 |                            |                     | 4                             | ns                  |

|                                                                         | LockControl = 1 |                            |                     | 3                             | ns                  |

| Output Duty Cycle                                                       |                 | 48.5                       |                     | 51.5                          | %                   |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>              |                 | 2.3                        |                     | 20.86                         | ns                  |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2</sup>              |                 | 0.025                      |                     | 20.86                         | ns                  |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                       |                 |                            | 5.7                 |                               | ns                  |

| VCO Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> <sup>6</sup> |                 | Max Peak-to-Peak Period Ji |                     | <pre>     Period Jitte </pre> | er <sup>6,7,8</sup> |

| <del>-</del>                                                            | $SSO \le 2$     | $SSO \leq 4$               | $\text{SSO} \leq 8$ | $SSO \leq 16$                 |                     |

| 0.75 MHz to 50MHz                                                       | 0.50            | 1.20                       | 2.00                | 3.00                          | %                   |

| 50 MHz to 100 MHz                                                       | 2.50            | 5.00                       | 7.00                | 15.00                         | %                   |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for deratings.

2.  $T_J = 25^{\circ}C$ ,  $V_{CC} = 1.2 V$ .

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

- 4. Maximum value obtained for a STD speed grade device in Worst-Case Commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for derating values.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

- 6. VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the % jitter. The VCO jitter (in ps) applies to CCC\_OUT, regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps, no matter what the settings are for the output divider.

- 7. Measurements done with LVTTL 3.3 V 8 mA I/O drive strength and high slew rate. VCC/VCCPLL = 1.14 V, VCCI = 3.3 V, VQ/PQ/TQ type of packages, 20 pF load.

- SSOs are outputs that are synchronous to a single clock domain and have their clock-to-out times within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO nano FPGA Fabric User's Guide.

- 9. The AGLN010, AGLN015, and AGLN020 devices do not support PLLs.

IGLOO nano DC and Switching Characteristics

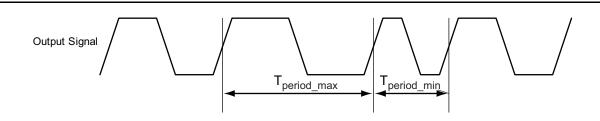

*Note:* Peak-to-peak jitter measurements are defined by  $T_{peak-to-peak} = T_{period_max} - T_{period_min}$ *Figure 2-26* • Peak-to-Peak Jitter Definition

IGLOO nano Low Power Flash FPGAs

Microsemi

AGLN020 Function IO38RSB1

IO37RSB1

IO33RSB1

IO30RSB1

IO27RSB1 IO23RSB1

TCK

TMS VPUMP

IGLOO nano Low Power Flash FPGAs

CS81

|            | CS81             |            | CS81             |            |

|------------|------------------|------------|------------------|------------|

| Pin Number | AGLN020 Function | Pin Number | AGLN020 Function | Pin Number |

| A1         | IO64RSB2         | E1         | GEC0/IO48RSB2    | J1         |

| A2         | IO54RSB2         | E2         | GEA0/IO47RSB2    | J2         |

| A3         | IO57RSB2         | E3         | NC               | J3         |

| A4         | IO36RSB1         | E4         | VCCIB1           | J4         |

| A5         | IO32RSB1         | E5         | VCC              | J5         |

| A6         | IO24RSB1         | E6         | VCCIB0           | J6         |

| A7         | IO20RSB1         | E7         | NC               | J7         |

| A8         | IO04RSB0         | E8         | GDA0/IO15RSB0    | J8         |

| A9         | IO08RSB0         | E9         | GDC0/IO14RSB0    | J9         |

| B1         | IO59RSB2         | F1         | IO46RSB2         |            |

| B2         | IO55RSB2         | F2         | IO45RSB2         |            |

| B3         | IO62RSB2         | F3         | NC               |            |

| B4         | IO34RSB1         | F4         | GND              |            |

| B5         | IO28RSB1         | F5         | VCCIB1           |            |

| B6         | IO22RSB1         | F6         | NC               |            |

| B7         | IO18RSB1         | F7         | NC               |            |

| B8         | IO00RSB0         | F8         | IO16RSB0         |            |

| B9         | IO03RSB0         | F9         | IO17RSB0         |            |

| C1         | IO51RSB2         | G1         | IO43RSB2         |            |

| C2         | IO50RSB2         | G2         | IO42RSB2         |            |

| C3         | NC               | G3         | IO41RSB2         |            |

| C4         | NC               | G4         | IO31RSB1         |            |

| C5         | NC               | G5         | NC               |            |

| C6         | NC               | G6         | IO21RSB1         |            |

| C7         | NC               | G7         | NC               |            |

| C8         | IO10RSB0         | G8         | VJTAG            |            |

| C9         | IO07RSB0         | G9         | TRST             |            |

| D1         | IO49RSB2         | H1         | IO40RSB2         |            |

| D2         | IO44RSB2         | H2         | FF/IO39RSB1      |            |

| D3         | NC               | H3         | IO35RSB1         |            |

| D4         | VCC              | H4         | IO29RSB1         |            |

| D5         | VCCIB2           | H5         | IO26RSB1         |            |

| D6         | GND              | H6         | IO25RSB1         |            |

| D7         | NC               | H7         | IO19RSB1         |            |

| D8         | IO13RSB0         | H8         | TDI              |            |

| D9         | IO12RSB0         | H9         | TDO              |            |

| QN48       |                              |  |  |  |  |  |

|------------|------------------------------|--|--|--|--|--|

| Pin Number | Pin Number AGLN030Z Function |  |  |  |  |  |

| 1          | IO82RSB1                     |  |  |  |  |  |

| 2          | GEC0/IO73RSB1                |  |  |  |  |  |

| 3          | GEA0/IO72RSB1                |  |  |  |  |  |

| 4          | GEB0/IO71RSB1                |  |  |  |  |  |

| 5          | GND                          |  |  |  |  |  |

| 6          | VCCIB1                       |  |  |  |  |  |

| 7          | IO68RSB1                     |  |  |  |  |  |

| 8          | IO67RSB1                     |  |  |  |  |  |

| 9          | IO66RSB1                     |  |  |  |  |  |

| 10         | IO65RSB1                     |  |  |  |  |  |

| 11         | IO64RSB1                     |  |  |  |  |  |

| 12         | IO62RSB1                     |  |  |  |  |  |

| 13         | IO61RSB1                     |  |  |  |  |  |

| 14         | FF/IO60RSB1                  |  |  |  |  |  |

| 15         | IO57RSB1                     |  |  |  |  |  |

| 16         | IO55RSB1                     |  |  |  |  |  |

| 17         | IO53RSB1                     |  |  |  |  |  |

| 18         | VCC                          |  |  |  |  |  |

| 19         | VCCIB1                       |  |  |  |  |  |

| 20         | IO46RSB1                     |  |  |  |  |  |

| 21         | IO42RSB1                     |  |  |  |  |  |

| 22         | TCK                          |  |  |  |  |  |

| 23         | TDI                          |  |  |  |  |  |

| 24         | TMS                          |  |  |  |  |  |

| 25         | VPUMP                        |  |  |  |  |  |

| 26         | TDO                          |  |  |  |  |  |

| 27         | TRST                         |  |  |  |  |  |

| 28         | VJTAG                        |  |  |  |  |  |

| 29         | IO38RSB0                     |  |  |  |  |  |

| 30         | GDB0/IO34RSB0                |  |  |  |  |  |

| 31         | GDA0/IO33RSB0                |  |  |  |  |  |

| 32         | GDC0/IO32RSB0                |  |  |  |  |  |

| 33         | VCCIB0                       |  |  |  |  |  |

| 34         | GND                          |  |  |  |  |  |

| 35         | VCC                          |  |  |  |  |  |

| 36         | IO25RSB0                     |  |  |  |  |  |

|            |                              |  |  |  |  |  |

|   |            | QN48              |  |  |

|---|------------|-------------------|--|--|

|   | Pin Number | AGLN030Z Function |  |  |

|   | 37         | IO24RSB0          |  |  |

|   | 38         | IO22RSB0          |  |  |

|   | 39         | IO20RSB0          |  |  |

|   | 40         | IO18RSB0          |  |  |

|   | 41         | IO16RSB0          |  |  |

|   | 42         | IO14RSB0          |  |  |

|   | 43         | IO10RSB0          |  |  |

|   | 44         | IO08RSB0          |  |  |

|   | 45         | IO06RSB0          |  |  |

|   | 46         | IO04RSB0          |  |  |

|   | 47         | IO02RSB0          |  |  |

|   | 48         | IO00RSB0          |  |  |

| 1 |            |                   |  |  |

Package Pin Assignments

|            | QN68                | QN68       |                     |

|------------|---------------------|------------|---------------------|

| Pin Number | AGLN020<br>Function | Pin Number | AGLN020<br>Function |

| 1          | IO60RSB2            | 36         | TDO                 |

| 2          | IO54RSB2            | 37         | TRST                |

| 3          | IO52RSB2            | 38         | VJTAG               |

| 4          | IO50RSB2            | 39         | IO17RSB0            |

| 5          | IO49RSB2            | 40         | IO16RSB0            |

| 6          | GEC0/IO48RSB2       | 41         | GDA0/IO15RSB0       |

| 7          | GEA0/IO47RSB2       | 42         | GDC0/IO14RSB0       |

| 8          | VCC                 | 43         | IO13RSB0            |

| 9          | GND                 | 44         | VCCIB0              |

| 10         | VCCIB2              | 45         | GND                 |

| 11         | IO46RSB2            | 46         | VCC                 |

| 12         | IO45RSB2            | 47         | IO12RSB0            |

| 13         | IO44RSB2            | 48         | IO11RSB0            |

| 14         | IO43RSB2            | 49         | IO09RSB0            |

| 15         | IO42RSB2            | 50         | IO05RSB0            |

| 16         | IO41RSB2            | 51         | IO00RSB0            |

| 17         | IO40RSB2            | 52         | IO07RSB0            |

| 18         | FF/IO39RSB1         | 53         | IO03RSB0            |

| 19         | IO37RSB1            | 54         | IO18RSB1            |

| 20         | IO35RSB1            | 55         | IO20RSB1            |

| 21         | IO33RSB1            | 56         | IO22RSB1            |

| 22         | IO31RSB1            | 57         | IO24RSB1            |

| 23         | IO30RSB1            | 58         | IO28RSB1            |

| 24         | VCC                 | 59         | NC                  |

| 25         | GND                 | 60         | GND                 |

| 26         | VCCIB1              | 61         | NC                  |

| 27         | IO27RSB1            | 62         | IO32RSB1            |

| 28         | IO25RSB1            | 63         | IO34RSB1            |

| 29         | IO23RSB1            | 64         | IO36RSB1            |

| 30         | IO21RSB1            | 65         | IO61RSB2            |

| 31         | IO19RSB1            | 66         | IO58RSB2            |

| 32         | ТСК                 | 67         | IO56RSB2            |

| 33         | TDI                 | 68         | IO63RSB2            |

| 34         | TMS                 | L          | •                   |

| 35         | VPUMP               |            |                     |

### Microsemi

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page        |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Revision 11               | The status of the AGLN060 device has changed from Advance to Production.                                                                                                                                                                                                                                                                                                                                                                          |             |

| (Jul 2010)                | The values for PAC1, PAC2, PAC3, and PAC4 were updated in Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices for 1.5 V core supply voltage (SAR 26404).                                                                                                                                                                                                                                            | 2-10        |

|                           | The values for PAC1, PAC2, PAC3, and PAC4 were updated in Table 2-17 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices for 1.2 V core supply voltage (SAR 26404).                                                                                                                                                                                                                                            | 2-11        |

| July 2010                 | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "IGLOO nano Device Status" table on page III indicates the status for each device in the device family.                                                                                                                                                                                  | N/A         |

| Revision 10<br>(Apr 2010) | References to differential inputs were removed from the datasheet, since IGLOO nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                                                                                                                                       | N/A         |

|                           | A parenthetical note, "hold previous I/O state in Flash*Freeze mode," was added to each occurrence of bus hold in the datasheet (SAR 24079).                                                                                                                                                                                                                                                                                                      | N/A         |

|                           | The "In-System Programming (ISP) and Security" section was revised to add 1.2 V programming.                                                                                                                                                                                                                                                                                                                                                      | I           |

|                           | The note connected with the "IGLOO nano Ordering Information" table was revised to<br>clarify features not available for Z feature grade devices.                                                                                                                                                                                                                                                                                                 | IV          |

|                           | The "IGLOO nano Device Status" table is new.                                                                                                                                                                                                                                                                                                                                                                                                      |             |

|                           | The definition of C in the "Temperature Grade Offerings" table was changed to "extended commercial temperature range".                                                                                                                                                                                                                                                                                                                            | VI          |

|                           | 1.2 V wide range was added to the list of voltage ranges in the "I/Os with Advanced I/O Standards" section.                                                                                                                                                                                                                                                                                                                                       | 1-8         |

|                           | A note was added to Table 2-2 • Recommended Operating Conditions <sup>1</sup> regarding switching from 1.2 V to 1.5 V core voltage for in-system programming. The VJTAG voltage was changed from "1.425 to 3.6" to "1.4 to 3.6" (SAR 24052). The note regarding voltage for programming V2 and V5 devices was revised (SAR 25213). The maximum value for VPUMP programming voltage (operation mode) was changed from 3.45 V to 3.6 V (SAR 25220). | 2-2         |

|                           | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}C$ , VCC = 1.14 V) were updated. Table 2-8 • Power Supply State per Mode is new.                                                                                                                              | 2-6,<br>2-7 |

|                           | The tables in the "Quiescent Supply Current" section were updated (SAR 24882 and SAR 24112).                                                                                                                                                                                                                                                                                                                                                      | 2-7         |

|                           | VJTAG was removed from Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode* (SARs 24112, 24882, and 79503).                                                                                                                                                                                                                                                                                                        | 2-8         |

|                           | The note stating what was included in I <sub>DD</sub> was removed from Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Shutdown Mode. The note, "per VCCI or VJTAG bank" was removed from Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash*Freeze Mode <sup>1</sup> . The note giving I <sub>DD</sub> was changed to "I <sub>DD</sub> = $N_{BANKS} * I_{CCI} + I_{CCA}$ ."                                | 2-8         |

|                           | The values in Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings and Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup> were updated. Wide range support information was added.                                                                                                                                                                         | 2-9         |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                         | Page                    |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Revision 10<br>(continued) | The following tables were updated with current available information. The equivalent software default drive strength option was added.                                                                                          | 2-19<br>through<br>2-40 |

|                            | Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels                                                                                                                                                          |                         |

|                            | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                    |                         |

|                            | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings                                                                                                                                                    |                         |

|                            | Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup>                                                                                                                                                                 |                         |

|                            | Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances                                                                                                                                                                             |                         |

|                            | Table 2-30 • I/O Short Currents IOSH/IOSL                                                                                                                                                                                       |                         |

|                            | Timing tables in the "Single-Ended I/O Characteristics" section, including new tables for 3.3 V and 1.2 V LVCMOS wide range.                                                                                                    |                         |

|                            | Table 2-40 $\mbox{ \bullet}$ Minimum and Maximum DC Input and Output Levels for LVCMOS 3.3 V Wide Range                                                                                                                         |                         |

|                            | Table 2-63 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                     |                         |

|                            | Table 2-67 • Minimum and Maximum DC Input and Output Levels (new)                                                                                                                                                               |                         |

|                            | The formulas in the notes to Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances were revised (SAR 21348).                                                                                                                      | 2-24                    |

|                            | The text introducing Table 2-31 • Duration of Short Circuit Event before Failure was revised to state six months at 100° instead of three months at 110° for reliability concerns. The row for 110° was removed from the table. |                         |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 24916): "It uses a 5-V tolerant input buffer and push-pull output buffer."                                                                              | 2-32                    |

|                            | The $F_{DDRIMAX}$ and $F_{DDOMAX}$ values were added to tables in the "DDR Module Specifications" section (SAR 23919). A note was added stating that DDR is not supported for AGLN010, AGLN015, and AGLN020.                    | 2-51                    |

|                            | Tables in the "Global Tree Timing Characteristics" section were updated with new information available.                                                                                                                         | 2-64                    |

|                            | Table 2-100 • IGLOO nano CCC/PLL Specification and Table 2-101 • IGLOO nano CCC/PLL Specification were revised (SAR 79390).                                                                                                     | 2-70,<br>2-71           |

|                            | Tables in the SRAM "Timing Characteristics" section and FIFO "Timing Characteristics" section were updated with new information available.                                                                                      | 2-77,<br>2-85           |

|                            | Table 3-3 • TRST and TCK Pull-Down Recommendations is new.                                                                                                                                                                      | 3-4                     |

|                            | A note was added to the "CS81" pin tables for AGLN060, AGLN060Z, AGLN125, AGLN125Z, AGLN250, and AGLN250Z indicating that pins F1 and F2 must be grounded (SAR 25007).                                                          | 4-9,<br>through<br>4-14 |

|                            | A note was added to the "CS81" and "VQ100" pin tables for AGLN060 and AGLN060Z stating that bus hold is not available for pin H7 or pin 45 (SAR 24079).                                                                         | 4-9,<br>4-24            |

|                            | The AGLN250 function for pin C8 in the "CS81" table was revised (SAR 22134).                                                                                                                                                    | 4-13                    |

Datasheet Information

| Revision / Version                                            | Changes                                                                                                                                                                                                                                                                                                              | Page       |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Revision 2 (Dec 2008)</b><br>Product Brief Advance<br>v0.4 | The second table note in "IGLOO nano Devices" table was revised to state, "AGLN060, AGLN125, and AGLN250 in the CS81 package do not support PLLs. AGLN030 and smaller devices do not support this feature."                                                                                                          | II         |

|                                                               | The I/Os per package for CS81 were revised to 60 for AGLN060, AGLN125, and AGLN250 in the "I/Os Per Package"table.                                                                                                                                                                                                   | II         |

| Packaging Advance<br>v0.3                                     | The "UC36" pin table is new.                                                                                                                                                                                                                                                                                         | 4-2        |

| <b>Revision 1 (Nov 2008)</b><br>Product Brief Advance<br>v0.3 | The "Advanced I/Os" section was updated to include wide power supply voltage support for 1.14 V to 1.575 V.                                                                                                                                                                                                          | Ι          |

|                                                               | The AGLN030 device was added to product tables and replaces AGL030 entries that were formerly in the tables.                                                                                                                                                                                                         | VI         |

|                                                               | The "I/Os Per Package"table was updated for the CS81 package to change the number of I/Os for AGLN060, AGLN125, and AGLN250 from 66 to 64.                                                                                                                                                                           | II         |

|                                                               | The "Wide Range I/O Support" section is new.                                                                                                                                                                                                                                                                         | 1-8        |

|                                                               | The table notes and references were revised in Table 2-2 • Recommended Operating Conditions <sup>1</sup> . VMV was included with VCCI and a table note was added stating, "VMV pins must be connected to the corresponding VCCI pins. See <i>Pin Descriptions</i> for further information." Please review carefully. | 2-2        |

|                                                               | VJTAG was added to the list in the table note for Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Flash*Freeze Mode*. Values were added for AGLN010, AGLN015, and AGLN030 for 1.5 V.                                                                                                          | 2-7        |

|                                                               | VCCI was removed from the list in the table note for Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode*.                                                                                                                                                                            | 2-8        |

|                                                               | Values for I <sub>CCA</sub> current were updated for AGLN010, AGLN015, and AGLN030 in Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash*Freeze Mode <sup>1</sup> .                                                                                                                                    | 2-8        |

|                                                               | Values for PAC1 and PAC2 were added to Table 2-15 • Different Components<br>Contributing to Dynamic Power Consumption in IGLOO nano Devices and Table<br>2-17 • Different Components Contributing to Dynamic Power Consumption in<br>IGLOO nano Devices.                                                             | 2-10, 2-11 |

|                                                               | Table notes regarding wide range support were added to Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels.                                                                                                                                                                                       | 2-19       |

|                                                               | 1.2 V LVCMOS wide range values were added to Table 2-22 • Summary of Maximum and Minimum DC Input Levels and Table 2-23 • Summary of AC Measuring Points.                                                                                                                                                            | 2-19, 2-20 |

|                                                               | The following table note was added to Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings and Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings: "All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range, as specified in the JESD8-B specification."  | 2-21       |

|                                                               | 3.3 V LVCMOS Wide Range and 1.2 V Wide Range were added to Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup> andTable 2-30 • I/O Short Currents IOSH/IOSL.                                                                                                                                             | 2-23, 2-24 |