Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 1536                                                                       |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 60                                                                         |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 81-WFBGA, CSBGA                                                            |

| Supplier Device Package        | 81-CSP (5x5)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln060v5-csg81i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 – IGLOO nano Device Overview

## **General Description**

The IGLOO family of flash FPGAs, based on a 130-nm flash process, offers the lowest power FPGA, a single-chip solution, small footprint packages, reprogrammability, and an abundance of advanced features.

The Flash\*Freeze technology used in IGLOO nano devices enables entering and exiting an ultra-low power mode that consumes nanoPower while retaining SRAM and register data. Flash\*Freeze technology simplifies power management through I/O and clock management with rapid recovery to operation mode.

The Low Power Active capability (static idle) allows for ultra-low power consumption while the IGLOO nano device is completely functional in the system. This allows the IGLOO nano device to control system power management based on external inputs (e.g., scanning for keyboard stimulus) while consuming minimal power.

Nonvolatile flash technology gives IGLOO nano devices the advantage of being a secure, low power, single-chip solution that is Instant On. The IGLOO nano device is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost.

These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

IGLOO nano devices offer 1 kbit of on-chip, reprogrammable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on an integrated phase-locked loop (PLL). The AGLN030 and smaller devices have no PLL or RAM support. IGLOO nano devices have up to 250 k system gates, supported with up to 36 kbits of true dual-port SRAM and up to 71 user I/Os.

IGLOO nano devices increase the breadth of the IGLOO product line by adding new features and packages for greater customer value in high volume consumer, portable, and battery-backed markets. Features such as smaller footprint packages designed with two-layer PCBs in mind, power consumption measured in nanoPower, Schmitt trigger, and bus hold (hold previous I/O state in Flash\*Freeze mode) functionality make these devices ideal for deployment in applications that require high levels of flexibility and low cost.

## Flash\*Freeze Technology

The IGLOO nano device offers unique Flash\*Freeze technology, allowing the device to enter and exit ultra-low power Flash\*Freeze mode. IGLOO nano devices do not need additional components to turn off I/Os or clocks while retaining the design information, SRAM content, and registers. Flash\*Freeze technology is combined with in-system programmability, which enables users to quickly and easily upgrade and update their designs in the final stages of manufacturing or in the field. The ability of IGLOO nano V2 devices to support a wide range of core voltage (1.2 V to 1.5 V) allows further reduction in power consumption, thus achieving the lowest total system power.

During Flash\*Freeze mode, each I/O can be set to the following configurations: hold previous state, tristate, HIGH, or LOW.

The availability of low power modes, combined with reprogrammability, a single-chip and single-voltage solution, and small-footprint packages make IGLOO nano devices the best fit for portable electronics.

IGLOO nano DC and Switching Characteristics

Table 2-2 • Recommended Operating Conditions 1

| Symbol              | P                       | arameter                                                | Extended<br>Commercial      | Industrial               | Units |  |  |  |

|---------------------|-------------------------|---------------------------------------------------------|-----------------------------|--------------------------|-------|--|--|--|

| TJ                  | Junction temperature    |                                                         | $-20 \text{ to} + 85^2$     | -40 to +100 <sup>2</sup> | °C    |  |  |  |

| VCC                 | 1.5 V DC core supply vo | oltage <sup>3</sup>                                     | 1.425 to 1.575              | 1.425 to 1.575           | V     |  |  |  |

|                     | 1.2 V–1.5 V wide range  | core voltage <sup>4,5</sup>                             | 1.14 to 1.575 1.14 to 1.575 |                          |       |  |  |  |

| VJTAG               | JTAG DC voltage         |                                                         | 1.4 to 3.6                  | 1.4 to 3.6               | V     |  |  |  |

| VPUMP <sup>6</sup>  | Programming voltage     | Programming mode                                        | 3.15 to 3.45                | 3.15 to 3.45             | V     |  |  |  |

|                     |                         | Operation                                               | ation 0 to 3.6 0 to 3.      |                          |       |  |  |  |

| VCCPLL <sup>7</sup> | Analog power supply     | 1.5 V DC core supply voltage <sup>3</sup>               | 1.425 to 1.575              | 1.425 to 1.575           | V     |  |  |  |

|                     | (PLL)                   | 1.2 V–1.5 V wide range core supply voltage <sup>4</sup> | 1.14 to 1.575               | 1.14 to 1.575            | V     |  |  |  |

| VCCI and            | 1.2 V DC supply voltage | , 4                                                     | 1.14 to 1.26                | 1.14 to 1.26             | V     |  |  |  |

| VMV <sup>8,9</sup>  | 1.2 V DC wide range su  | pply voltage <sup>4</sup>                               | 1.14 to 1.575               | 1.14 to 1.575            | V     |  |  |  |

|                     | 1.5 V DC supply voltage |                                                         | 1.425 to 1.575              | 1.425 to 1.575           | V     |  |  |  |

|                     | 1.8 V DC supply voltage | :                                                       | 1.7 to 1.9                  | 1.7 to 1.9               | V     |  |  |  |

|                     | 2.5 V DC supply voltage |                                                         | 2.3 to 2.7                  | 2.3 to 2.7               | V     |  |  |  |

|                     | 3.3 V DC supply voltage |                                                         | 3.0 to 3.6                  | 3.0 to 3.6               | V     |  |  |  |

|                     | 3.3 V DC wide range su  | pply voltage <sup>10</sup>                              | 2.7 to 3.6                  | 2.7 to 3.6               | V     |  |  |  |

#### Notes:

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. Default Junction Temperature Range in the Libero SoC software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information regarding custom settings, refer to the New Project Dialog Box in the Libero Online Help.

- 3. For IGLOO® nano V5 devices

- 4. For IGLOO nano V2 devices only, operating at VCCI ≥ VCC

- 5. IGLOO nano V5 devices can be programmed with the VCC core voltage at 1.5 V only. IGLOO nano V2 devices can be programmed with the VCC core voltage at 1.2 V (with FlashPro4 only) or 1.5 V. If you are using FlashPro3 and want to do in-system programming using 1.2 V, please contact the factory.

- 6.  $V_{PUMP}$  can be left floating during operation (not programming mode).

- 7. VCCPLL pins should be tied to VCC pins. See the "Pin Descriptions" chapter for further information.

- 8. VMV pins must be connected to the corresponding VCCI pins. See the Pin Descriptions chapter of the IGLOO nano FPGA Fabric User's Guide for further information.

- 9. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-21 on page 2-19. VCCI should be at the same voltage within a given I/O bank.

- 10. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

| Product<br>Grade |     | Program Retention (biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|------------------|-----|-------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|

| Commercial       | 500 | 20 years                            | 110                                                               | 100                                                                     |

| Industrial       | 500 | 20 years                            | 110                                                               | 100                                                                     |

#### Notes:

- 1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

- These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

2-2 Revision 19

Table 2-4 • Overshoot and Undershoot Limits 1

| vccı          | Average VCCI–GND Overshoot or<br>Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                                 | 1.4 V                                         |

|               | 5%                                                                                                  | 1.49 V                                        |

| 3 V           | 10%                                                                                                 | 1.1 V                                         |

|               | 5%                                                                                                  | 1.19 V                                        |

| 3.3 V         | 10%                                                                                                 | 0.79 V                                        |

|               | 5%                                                                                                  | 0.88 V                                        |

| 3.6 V         | 10%                                                                                                 | 0.45 V                                        |

|               | 5%                                                                                                  | 0.54 V                                        |

#### Notes:

- 1. Based on reliability requirements at 85°C.

- 2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO nano device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4.

There are five regions to consider during power-up.

IGLOO nano I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### **VCCI Trip Point:**

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

### VCC Trip Point:

Ramping up (V5 devices):  $0.6 \text{ V} < \text{trip\_point\_up} < 1.1 \text{ V}$ Ramping down (V5 devices):  $0.5 \text{ V} < \text{trip\_point\_down} < 1.0 \text{ V}$ Ramping up (V2 devices):  $0.65 \text{ V} < \text{trip\_point\_up} < 1.05 \text{ V}$ Ramping down (V2 devices):  $0.55 \text{ V} < \text{trip\_point\_down} < 0.95 \text{ V}$

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

## Power per I/O Pin

Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to IGLOO nano I/O Banks

|                                                        | VCCI (V) | Dynamic Power<br>PAC9 (μW/MHz) <sup>1</sup> |

|--------------------------------------------------------|----------|---------------------------------------------|

| Single-Ended                                           |          |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS                             | 3.3      | 16.38                                       |

| 3.3 V LVTTL / 3.3 V LVCMOS – Schmitt Trigger           | 3.3      | 18.89                                       |

| 3.3 V LVCMOS Wide Range <sup>2</sup>                   | 3.3      | 16.38                                       |

| 3.3 V LVCMOS Wide Range – Schmitt Trigger              | 3.3      | 18.89                                       |

| 2.5 V LVCMOS                                           | 2.5      | 4.71                                        |

| 2.5 V LVCMOS – Schmitt Trigger                         | 2.5      | 6.13                                        |

| 1.8 V LVCMOS                                           | 1.8      | 1.64                                        |

| 1.8 V LVCMOS – Schmitt Trigger                         | 1.8      | 1.79                                        |

| 1.5 V LVCMOS (JESD8-11)                                | 1.5      | 0.97                                        |

| 1.5 V LVCMOS (JESD8-11) – Schmitt Trigger              | 1.5      | 0.96                                        |

| 1.2 V LVCMOS <sup>3</sup>                              | 1.2      | 0.57                                        |

| 1.2 V LVCMOS – Schmitt Trigger <sup>3</sup>            | 1.2      | 0.52                                        |

| 1.2 V LVCMOS Wide Range <sup>3</sup>                   | 1.2      | 0.57                                        |

| 1.2 V LVCMOS Wide Range – Schmitt Trigger <sup>3</sup> | 1.2      | 0.52                                        |

#### Notes:

- 1. PAC9 is the total dynamic power measured on V<sub>CCI</sub>.

- 2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

- 3. Applicable to IGLOO nano V2 devices operating at VCCI ≥ VCC.

Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup>

Applicable to IGLOO nano I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Dynamic Power<br>PAC10 (μW/MHz) <sup>2</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------------|

| Single-Ended                         |                        |          |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 5                      | 3.3      | 107.98                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 5                      | 3.3      | 107.98                                       |

| 2.5 V LVCMOS                         | 5                      | 2.5      | 61.24                                        |

| 1.8 V LVCMOS                         | 5                      | 1.8      | 31.28                                        |

| 1.5 V LVCMOS (JESD8-11)              | 5                      | 1.5      | 21.50                                        |

| 1.2 V LVCMOS <sup>4</sup>            | 5                      | 1.2      | 15.22                                        |

#### Notes:

- 1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PAC10 is the total dynamic power measured on VCCI.

- 3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

- 4. Applicable for IGLOO nano V2 devices operating at VCCI ≥ VCC.

## **Power Consumption of Various Internal Resources**

Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|           |                                                                |           | Device Spe | ecific Dyna  | mic Power   | (µW/MHz) |         |  |  |

|-----------|----------------------------------------------------------------|-----------|------------|--------------|-------------|----------|---------|--|--|

| Parameter | Definition                                                     | AGLN250   | AGLN125    | AGLN060      | AGLN020     | AGLN015  | AGLN010 |  |  |

| PAC1      | Clock contribution of a Global Rib                             | 4.421     | 4.493      | 2.700        | 0           | 0        | 0       |  |  |

| PAC2      | Clock contribution of a Global Spine                           | 2.704     | 1.976      | 1.982        | 4.002       | 4.002    | 2.633   |  |  |

| PAC3      | Clock contribution of a VersaTile row                          | 1.496     | 1.504      | 1.511        | 1.346       | 1.346    | 1.340   |  |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.152     | 0.153      | 0.153        | 0.148       | 0.148    | 0.143   |  |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  |           |            | 0.0          | 57          |          |         |  |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.207     |            |              |             |          |         |  |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     |           |            | 0.           | 17          |          |         |  |  |

| PAC8      | Average contribution of a routing net                          |           |            | 0.           | .7          |          |         |  |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          |           | Se         | e Table 2-13 | 3 on page 2 | ?-9.     |         |  |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         |           |            | See Tab      | ole 2-14.   |          |         |  |  |

| PAC11     | Average contribution of a RAM block during a read operation    |           | 25.00      |              |             | N/A      |         |  |  |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00 N/A |            |              |             |          |         |  |  |

| PAC13     | Dynamic contribution for PLL                                   | 2.70 N/A  |            |              |             |          |         |  |  |

Table 2-16 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|                   |                                                    |                            | Device                     | -Specific   | Static Powe | er (mW) |         |  |  |  |  |

|-------------------|----------------------------------------------------|----------------------------|----------------------------|-------------|-------------|---------|---------|--|--|--|--|

| Parameter         | Definition                                         | AGLN250                    | AGLN125                    | AGLN060     | AGLN020     | AGLN015 | AGLN010 |  |  |  |  |

| PDC1              | Array static power in Active mode                  |                            | See Table 2-12 on page 2-8 |             |             |         |         |  |  |  |  |

|                   | Array static power in Static (Idle) mode           | See Table 2-12 on page 2-8 |                            |             |             |         |         |  |  |  |  |

|                   | Array static power in Flash*Freeze mode            |                            | S                          | ee Table 2- | 9 on page 2 | 2-7     |         |  |  |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                            |                            | 1.84                       |             | N/A         |         |         |  |  |  |  |

| PDC5              | Bank quiescent power (VCCI-dependent) <sup>2</sup> |                            | See Table 2-12 on page 2-8 |             |             |         |         |  |  |  |  |

#### Notes:

- 1. Minimum contribution of the PLL when running at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

2-10 Revision 19

IGLOO nano Low Power Flash FPGAs

#### **Timing Characteristics**

#### Applies to 1.5 V DC Core Voltage

Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 4 mA           | STD         | 0.97              | 3.52            | 0.19             | 0.86            | 1.16             | 0.66              | 3.59            | 3.42            | 1.75            | 1.90            | ns    |

| 6 mA           | STD         | 0.97              | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

| 8 mA           | STD         | 0.97              | 2.90            | 0.19             | 0.86            | 1.16             | 0.66              | 2.96            | 2.83            | 1.98            | 2.29            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 4 mA           | STD         | 0.97              | 2.16            | 0.19             | 0.86            | 1.16             | 0.66              | 2.20            | 1.80            | 1.75            | 1.99            | ns    |

| 6 mA           | STD         | 0.97              | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

| 8 mA           | STD         | 0.97              | 1.79            | 0.19             | 0.86            | 1.16             | 0.66              | 1.83            | 1.45            | 1.98            | 2.38            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

#### **Timing Characteristics**

Applies to 1.5 V DC Core Voltage

Table 2-41 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                          | STD            | 0.97              | 5.23            | 0.19             | 1.20            | 1.66             | 0.66              | 5.24            | 5.00            | 2.47            | 2.56            | ns    |

| 100 μΑ            | 4 mA                                                                          | STD            | 0.97              | 5.23            | 0.19             | 1.20            | 1.66             | 0.66              | 5.24            | 5.00            | 2.47            | 2.56            | ns    |

| 100 μΑ            | 6 mA                                                                          | STD            | 0.97              | 4.27            | 0.19             | 1.20            | 1.66             | 0.66              | 4.28            | 4.12            | 2.83            | 3.16            | ns    |

| 100 μΑ            | 8 mA                                                                          | STD            | 0.97              | 4.27            | 0.19             | 1.20            | 1.66             | 0.66              | 4.28            | 4.12            | 2.83            | 3.16            | ns    |

#### Notes:

Table 2-42 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                          | STD            | 0.97              | 3.11            | 0.19             | 1.20            | 1.66             | 0.66              | 3.13            | 2.55            | 2.47            | 2.70            | ns    |

| 100 μΑ            | 4 mA                                                                          | STD            | 0.97              | 3.11            | 0.19             | 1.20            | 1.66             | 0.66              | 3.13            | 2.55            | 2.47            | 2.70            | ns    |

| 100 μΑ            | 6 mA                                                                          | STD            | 0.97              | 2.56            | 0.19             | 1.20            | 1.66             | 0.66              | 2.57            | 2.02            | 2.82            | 3.31            | ns    |

| 100 μΑ            | 8 mA                                                                          | STD            | 0.97              | 2.56            | 0.19             | 1.20            | 1.66             | 0.66              | 2.57            | 2.02            | 2.82            | 3.31            | ns    |

#### Notes:

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 3. Software default selection highlighted in gray.

2-30 Revision 19

<sup>1.</sup> The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

<sup>1.</sup> The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

IGLOO nano DC and Switching Characteristics

#### 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general purpose 2.5 V applications.

Table 2-45 • Minimum and Maximum DC Input and Output Levels

| 2.5 V<br>LVCMOS   | ٧       | TL The state of th | ٧       | IH      | VOL     | VOH     | IOL | ЮН | IOSL                  | IOSH                  | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|-----|----|-----------------------|-----------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min., V | Max., V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min., V | Max., V | Max., V | Min., V | mA  | mA | Max., mA <sup>3</sup> | Max., mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3    | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.7     | 3.6     | 0.7     | 1.7     | 2   | 2  | 16                    | 18                    | 10                      | 10                      |

| 4 mA              | -0.3    | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.7     | 3.6     | 0.7     | 1.7     | 4   | 4  | 16                    | 18                    | 10                      | 10                      |

| 6 mA              | -0.3    | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.7     | 3.6     | 0.7     | 1.7     | 6   | 6  | 32                    | 37                    | 10                      | 10                      |

| 8 mA              | -0.3    | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.7     | 3.6     | 0.7     | 1.7     | 8   | 8  | 32                    | 37                    | 10                      | 10                      |

#### Notes:

- 1.  $I_{|L|}$  is the input leakage current per I/O pin over recommended operating conditions where -0.3 < VIN < VIL.

- 2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

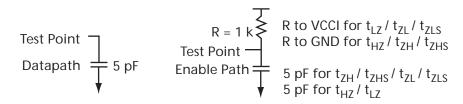

Figure 2-8 • AC Loading

Table 2-46 • 2.5 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |  |  |

|---------------|----------------|----------------------|------------------------|--|--|

| 0             | 2.5            | 1.2                  | 5                      |  |  |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

2-32 Revision 19

IGLOO nano Low Power Flash FPGAs

#### **Timing Characteristics**

#### Applies to 1.5 V DC Core Voltage

Table 2-47 • 2.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 4.13            | 0.19             | 1.10            | 1.24             | 0.66              | 4.01            | 4.13            | 1.73            | 1.74            | ns    |

| 4 mA           | STD         | 0.97              | 4.13            | 0.19             | 1.10            | 1.24             | 0.66              | 4.01            | 4.13            | 1.73            | 1.74            | ns    |

| 8 mA           | STD         | 0.97              | 3.39            | 0.19             | 1.10            | 1.24             | 0.66              | 3.31            | 3.39            | 1.98            | 2.19            | ns    |

| 8 mA           | STD         | 0.97              | 3.39            | 0.19             | 1.10            | 1.24             | 0.66              | 3.31            | 3.39            | 1.98            | 2.19            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-48 • 2.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.19            | 0.19             | 1.10            | 1.24             | 0.66              | 2.23            | 2.11            | 1.72            | 1.80            | ns    |

| 4 mA           | STD         | 0.97              | 2.19            | 0.19             | 1.10            | 1.24             | 0.66              | 2.23            | 2.11            | 1.72            | 1.80            | ns    |

| 6 mA           | STD         | 0.97              | 1.81            | 0.19             | 1.10            | 1.24             | 0.66              | 1.85            | 1.63            | 1.97            | 2.26            | ns    |

| 8 mA           | STD         | 0.97              | 1.81            | 0.19             | 1.10            | 1.24             | 0.66              | 1.85            | 1.63            | 1.97            | 2.26            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## **Output Register**

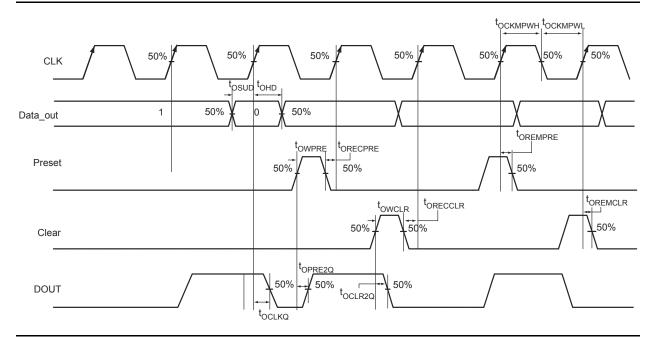

Figure 2-15 • Output Register Timing Diagram

#### Timing Characteristics

1.5 V DC Core Voltage

Table 2-74 • Output Data Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 1.00 | ns    |

| tosup                | Data Setup Time for the Output Data Register                         | 0.51 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 1.34 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 1.34 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.24 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.24 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.19 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.19 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Data Register          | 0.31 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

Table 2-94 • AGLN010 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           |   | Std.              |                   |       |

|----------------------|-------------------------------------------|---|-------------------|-------------------|-------|

| Parameter            | Description                               | • | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |   | 1.71              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |   | 1.78              | 2.31              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |   | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |   | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |   |                   | 0.53              | ns    |

#### Notes:

- Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-95 • AGLN015 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano Low Power Flash FPGAs

Table 2-98 • AGLN125 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | s                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.08              | 2.54              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.15              | 2.77              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

#### Notes:

- Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-99 • AGLN250 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           |   | Std.              |                   |       |

|----------------------|-------------------------------------------|---|-------------------|-------------------|-------|

| Parameter            | Description                               | 1 | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |   | 2.11              | 2.57              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |   | 2.19              | 2.81              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |   | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |   | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |   |                   | 0.62              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano DC and Switching Characteristics

## **Clock Conditioning Circuits**

#### **CCC Electrical Specifications**

**Timing Characteristics**

Table 2-100 • IGLOO nano CCC/PLL Specification For IGLOO nano V2 OR V5 Devices, 1.5 V DC Core Supply Voltage

| Parameter                                                               |                 | Min.        | Тур.                | Max.     | Units |

|-------------------------------------------------------------------------|-----------------|-------------|---------------------|----------|-------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>        |                 | 1.5         |                     | 250      | MHz   |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CC</sub>       | C               | 0.75        |                     | 250      | MHz   |

| Delay Increments in Programmable Delay Blocks 1, 2                      |                 |             | 360 <sup>3</sup>    |          | ps    |

| Number of Programmable Values in Each Programmable                      | e Delay Block   |             |                     | 32       |       |

| Serial Clock (SCLK) for Dynamic PLL <sup>4,9</sup>                      |                 |             |                     | 100      | MHz   |

| Input Cycle-to-Cycle Jitter (peak magnitude)                            |                 |             |                     | 1        | ns    |

| Acquisition Time                                                        |                 |             |                     |          |       |

|                                                                         | LockControl = 0 |             |                     | 300      | μs    |

|                                                                         | LockControl = 1 |             |                     | 6.0      | ms    |

| Tracking Jitter <sup>5</sup>                                            |                 |             |                     |          |       |

|                                                                         | LockControl = 0 |             |                     | 2.5      | ns    |

|                                                                         | LockControl = 1 |             |                     | 1.5      | ns    |

| Output Duty Cycle                                                       |                 | 48.5        |                     | 51.5     | %     |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>              |                 | 1.25        |                     | 15.65    | ns    |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2,</sup>             |                 | 0.025       |                     | 15.65    | ns    |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                       |                 |             | 3.5                 |          | ns    |

| VCO Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> <sup>6</sup> | Max Peak-to-Pea | k Jitter Da | ta <sup>6,7,8</sup> |          |       |

|                                                                         | $SSO \leq 2$    | SSO ≤ 4     | SSO ≤ 8             | SSO ≤ 16 |       |

| 0.75 MHz to 50 MHz                                                      | 0.50            | 0.60        | 0.80                | 1.20     | %     |

| 50 MHz to 250 MHz                                                       | 2.50            | 4.00        | 6.00                | 12.00    | %     |

#### Notes:

- 1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for deratings.

- 2.  $T_{.I} = 25^{\circ}C$ , VCC = 1.5 V

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

- 4. Maximum value obtained for a STD speed grade device in Worst-Case Commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for derating values.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

- 6. VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the % jitter. The VCO jitter (in ps) applies to CCC\_OUT, regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps, no matter what the settings are for the output divider.

- 7. Measurements done with LVTTL 3.3 V 8 mA I/O drive strength and high slew rate. VCC/VCCPLL = 1.425 V, VCCI = 3.3 V, VQ/PQ/TQ type of packages, 20 pF load.

- 8. SSOs are outputs that are synchronous to a single clock domain and have their clock-to-out times within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO nano FPGA Fabric User's Guide.

- 9. The AGLN010, AGLN015, and AGLN020 devices do not support PLLs.

2-70 Revision 19

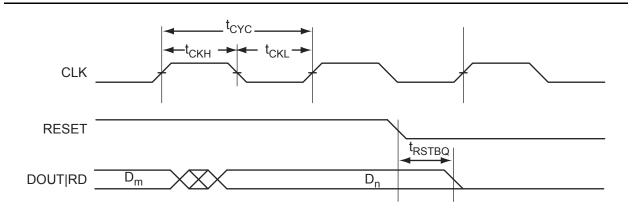

Figure 2-32 • RAM Reset. Applicable to Both RAM4K9 and RAM512x18.

2-76 Revision 19

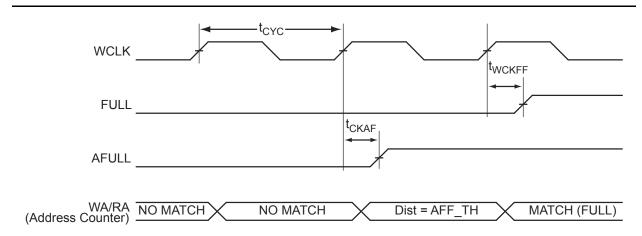

Figure 2-38 • FIFO FULL Flag and AFULL Flag Assertion

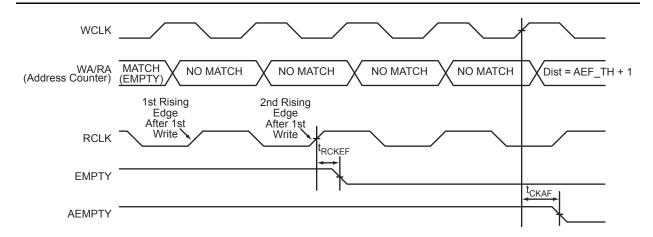

Figure 2-39 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

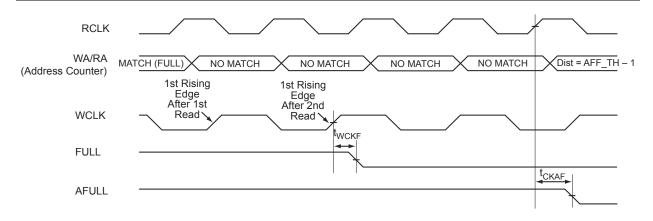

Figure 2-40 • FIFO FULL Flag and AFULL Flag Deassertion

2-84 Revision 19

## **Embedded FlashROM Characteristics**

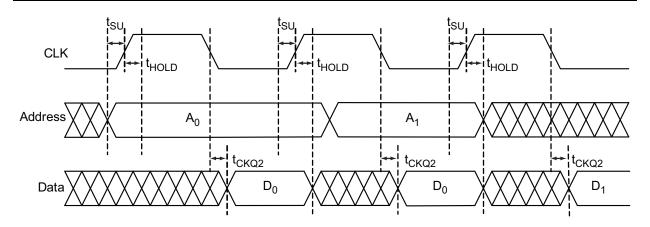

Figure 2-41 • Timing Diagram

## **Timing Characteristics**

1.5 V DC Core Voltage

Table 2-108 • Embedded FlashROM Access Time

Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

| Parameter         | Description             | Std.  | Units |

|-------------------|-------------------------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.57  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 20.90 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 15    | MHz   |

#### 1.2 V DC Core Voltage

Table 2-109 • Embedded FlashROM Access Time Worst Commercial-Case Conditions:  $T_J$  = 70°C, VCC = 1.14 V

| Parameter         | Description             | Std.  | Units |

|-------------------|-------------------------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.59  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 35.74 | ns    |

| F <sub>MAX</sub>  | Maximum Clock Frequency | 10    | MHz   |

## Package Pin Assignments

|            | 20140               |

|------------|---------------------|

| (          | QN48                |

| Pin Number | AGLN010<br>Function |

| 1          | GEC0/IO37RSB1       |

| 2          | IO36RSB1            |

| 3          | GEA0/IO34RSB1       |

| 4          | IO22RSB1            |

| 5          | GND                 |

| 6          | VCCIB1              |

| 7          | IO24RSB1            |

| 8          | IO33RSB1            |

| 9          | IO26RSB1            |

| 10         | IO32RSB1            |

| 11         | IO27RSB1            |

| 12         | IO29RSB1            |

| 13         | IO30RSB1            |

| 14         | FF/IO31RSB1         |

| 15         | IO28RSB1            |

| 16         | IO25RSB1            |

| 17         | IO23RSB1            |

| 18         | VCC                 |

| 19         | VCCIB1              |

| 20         | IO17RSB1            |

| 21         | IO14RSB1            |

| 22         | TCK                 |

| 23         | TDI                 |

| 24         | TMS                 |

| 25         | VPUMP               |

| 26         | TDO                 |

| 27         | TRST                |

| 28         | VJTAG               |

| 29         | IO11RSB0            |

| 30         | IO10RSB0            |

| 31         | IO09RSB0            |

| 32         | IO08RSB0            |

| 33         | VCCIB0              |

| 34         | GND                 |

| 35         | VCC                 |

| QN48       |                     |  |

|------------|---------------------|--|

| Pin Number | AGLN010<br>Function |  |

| 36         | IO07RSB0            |  |

| 37         | IO06RSB0            |  |

| 38         | GDA0/IO05RSB0       |  |

| 39         | IO03RSB0            |  |

| 40         | GDC0/IO01RSB0       |  |

| 41         | IO12RSB1            |  |

| 42         | IO13RSB1            |  |

| 43         | IO15RSB1            |  |

| 44         | IO16RSB1            |  |

| 45         | IO18RSB1            |  |

| 46         | IO19RSB1            |  |

| 47         | IO20RSB1            |  |

| 48         | IO21RSB1            |  |

4-16 Revision 19

Package Pin Assignments

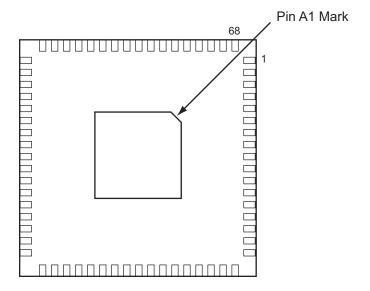

## **QN68**

#### Notes:

- 1. This is the bottom view of the package.

- 2. The die attach paddle of the package is tied to ground (GND).

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

4-18 Revision 19

## 5 - Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in each version of the IGLOO nano datasheet.

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Revision 19<br>(October 2015)   | Modified the note to include device/package obsoletion information in "Features and Benefits" section (SAR 69724).                                                                                                                                                                                                                                                                                                                                                                                    | 1-I                   |

|                                 | Added a note under Security Feature "Y" in "IGLOO nano Ordering Information" section (SAR 70553).                                                                                                                                                                                                                                                                                                                                                                                                     | 1-IV                  |

|                                 | Modified AGLN250 pin assignment table to match with I/O Attribute Editor tool from Libero in "CS81" Package (SAR 59049).                                                                                                                                                                                                                                                                                                                                                                              | 4-6                   |

|                                 | Modified the nominal area to 25 for CS81 Package in Table 1 (SAR 71127).                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-II                  |

|                                 | Modified the title of AGLN125Z pin assignment table for "CS81" Package (SAR 71127).                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6                   |

| Revision 18<br>(November 2013)  | Modified the "Device Marking" section and updated Figure 1 • Example of Device Marking for Small Form Factor Packages to reflect updates suggested per CN1004 published on 5/10/2010 (SAR 52036).                                                                                                                                                                                                                                                                                                     | V                     |

| Revision 17<br>(May 2013)       | Deleted details related to Ambient temperature from "Enhanced Commercial Temperature Range", "IGLOO nano Ordering Information", "Temperature Grade Offerings", and Table 2-2 • Recommended Operating Conditions <sup>1</sup> to remove ambiguities arising due to the same, and modified Note 2 (SAR 47063).                                                                                                                                                                                          | I, IV, VI,<br>and 2-2 |

| Revision 16<br>(December 2012)  | The "IGLOO nano Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43174).                                                                                                                                                                                                                                                                    | IV                    |

|                                 | The note in Table 2-100 • IGLOO nano CCC/PLL Specification and Table 2-101 • IGLOO nano CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42565).                                                                                                                                                                                                                                                                  | 2-70,<br>2-71         |

|                                 | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                                          | NA                    |

|                                 | The status of the AGLN125 device has been modified from 'Advance' to 'Production' in the "IGLOO nano Device Status" section (SAR 41416).                                                                                                                                                                                                                                                                                                                                                              | III                   |

|                                 | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 40274).                                                                                                                                                                                                                                                                                                                                                                            | NA                    |

| Revision 14<br>(September 2012) | The "Security" section was modified to clarify that Microsemi does not support read-back of programmed data.                                                                                                                                                                                                                                                                                                                                                                                          | 1-2                   |