# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2000                           |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 3072                                                                       |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 71                                                                         |

| Number of Gates                | 125000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln125v2-vqg100 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, flash-based IGLOO nano devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic.

Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The IGLOO nano device architecture mitigates the need for ASIC migration at higher user volumes. This makes IGLOO nano devices cost-effective ASIC replacement solutions, especially for applications in the consumer, networking/communications, computing, and avionics markets.

With a variety of devices under \$1, IGLOO nano FPGAs enable cost-effective implementation of programmable logic and quick time to market.

#### Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO nano flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO nano FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Advanced Flash Technology

The IGLOO nano device offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO nano FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

#### Advanced Architecture

The proprietary IGLOO nano architecture provides granularity comparable to standard-cell ASICs. The IGLOO nano device consists of five distinct and programmable architectural features (Figure 1-3 on page 1-5 to Figure 1-4 on page 1-5):

- Flash\*Freeze technology

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO nano core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC<sup>®</sup> family of third-generation-architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

<sup>†</sup> The AGLN030 and smaller devices do not support PLL or SRAM.

The inputs of the six CCC blocks are accessible from the FPGA core or from dedicated connections to the CCC block, which are located near the CCC.

The CCC block has these key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis (for PLL only)

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration (for PLL only).

- Output duty cycle = 50% ± 1.5% or better (for PLL only)

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used (for PLL only)

- Maximum acquisition time is 300 µs (for PLL only)

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns (for PLL only)

- Four precise phases; maximum misalignment between adjacent phases of 40 ps  $\times$  250 MHz /  $f_{OUT\_CCC}$  (for PLL only)

#### **Global Clocking**

IGLOO nano devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

#### I/Os with Advanced I/O Standards

IGLOO nano FPGAs feature a flexible I/O structure, supporting a range of voltages (1.2 V, 1.2 V wide range, 1.5 V, 1.8 V, 2.5 V, 3.0 V wide range, and 3.3 V).

The I/Os are organized into banks with two, three, or four banks per device. The configuration of these banks determines the I/O standards supported.

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of various single-data-rate applications for all versions of nano devices and double-data-rate applications for the AGLN060, AGLN125, and AGLN250 devices.

IGLOO nano devices support LVTTL and LVCMOS I/O standards, are hot-swappable, and support cold-sparing and Schmitt trigger.

Hot-swap (also called hot-plug, or hot-insertion) is the operation of hot-insertion or hot-removal of a card in a powered-up system.

Cold-sparing (also called cold-swap) refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

### Wide Range I/O Support

IGLOO nano devices support JEDEC-defined wide range I/O operation. IGLOO nano devices support both the JESD8-B specification, covering both 3 V and 3.3 V supplies, for an effective operating range of 2.7 V to 3.6 V, and JESD8-12 with its 1.2 V nominal, supporting an effective operating range of 1.14 V to 1.575 V.

Wider I/O range means designers can eliminate power supplies or power conditioning components from the board or move to less costly components with greater tolerances. Wide range eases I/O bank management and provides enhanced protection from system voltage spikes, while providing the flexibility to easily run custom voltage applications.

IGLOO nano Device Overview

- 6. Click **OK** to return to the FlashPoint Programming File Generator window.

- Note: I/O States During programming are saved to the ADB and resulting programming files after completing programming file generation.

## Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to T<sub>J</sub> = 70°C, VCC = 1.14 V)

| Array Voltage | Junction Temperature (°C) |       |       |       |       |       |       |  |  |  |

|---------------|---------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| VCC (V)       | -40°C                     | –20°C | 0°C   | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |

| 1.14          | 0.968                     | 0.974 | 0.979 | 0.991 | 1.000 | 1.006 | 1.009 |  |  |  |

| 1.2           | 0.863                     | 0.868 | 0.873 | 0.884 | 0.892 | 0.898 | 0.901 |  |  |  |

| 1.26          | 0.792                     | 0.797 | 0.801 | 0.811 | 0.819 | 0.824 | 0.827 |  |  |  |

For IGLOO nano V2, 1.2 V DC Core Supply Voltage

## **Calculating Power Dissipation**

### **Quiescent Supply Current**

Quiescent supply current (IDD) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power mode usage. Microsemi recommends using the Power Calculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

| Table 2-8 • | Power Supply State per Mode  |

|-------------|------------------------------|

|             | · oner euppig etate per meae |

|                      | Power Supply Configurations |        |      |       |                 |  |  |  |

|----------------------|-----------------------------|--------|------|-------|-----------------|--|--|--|

| Modes/Power Supplies | VCC                         | VCCPLL | VCCI | VJTAG | VPUMP           |  |  |  |

| Flash*Freeze         | On                          | On     | On   | On    | On/off/floating |  |  |  |

| Sleep                | Off                         | Off    | On   | Off   | Off             |  |  |  |

| Shutdown             | Off                         | Off    | Off  | Off   | Off             |  |  |  |

| No Flash*Freeze      | On                          | On     | On   | On    | On/off/floating |  |  |  |

Note: Off: Power Supply level = 0 V

Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Flash\*Freeze Mode\*

|                | Core<br>Voltage | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|----------------|-----------------|---------|---------|---------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V           | 1.9     | 3.3     | 3.3     | 8       | 13      | 20      | μA    |

|                | 1.5 V           | 5.8     | 6       | 6       | 10      | 18      | 34      | μA    |

Note: \*IDD includes VCC, VPUMP, VCCI, VCCPLL, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-9 through Table 2-14 on page 2-9 and Table 2-15 on page 2-10 through Table 2-18 on page 2-11 (PDC6 and PDC7).

IGLOO nano DC and Switching Characteristics

|                                           | Core<br>Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------------------------------|------------------|---------|---------|---------|---------|---------|---------|-------|

| VCCI= 1.2 V (per bank)<br>Typical (25°C)  | 1.2 V            | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μA    |

| VCCI = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μA    |

| VCCI = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μA    |

| VCCI = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μA    |

| VCCI = 3.3 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μA    |

#### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode\*

Note: \*I<sub>DD</sub> = N<sub>BANKS</sub> \* I<sub>CCI</sub>.

#### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Shutdown Mode

|                   | Core Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------|---------------|---------|---------|---------|---------|---------|---------|-------|

| Typical<br>(25°C) | 1.2 V / 1.5 V | 0       | 0       | 0       | 0       | 0       | 0       | μA    |

#### Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash\*Freeze Mode<sup>1</sup>

|                                                   | Core<br>Voltage | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|---------------------------------------------------|-----------------|---------|---------|---------|---------|---------|---------|-------|

| ICCA Current <sup>2</sup>                         |                 | •       |         |         |         |         |         |       |

| Typical (25°C)                                    | 1.2 V           | 3.7     | 5       | 5       | 10      | 13      | 18      | μA    |

|                                                   | 1.5 V           | 8       | 14      | 14      | 20      | 28      | 44      | μA    |

| ICCI or IJTAG Current                             |                 | -       |         |         |         |         |         |       |

| VCCI / VJTAG = 1.2 V (per<br>bank) Typical (25°C) | 1.2 V           | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μA    |

| VCCI / VJTAG = 1.5 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μA    |

| VCCI / VJTAG = 1.8 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μA    |

| VCCI / VJTAG = 2.5 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μA    |

| VCCI / VJTAG = 3.3 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μA    |

Notes:

IDD = N<sub>BANKS</sub> \* ICCI + ICCA. JTAG counts as one bank when powered.

Includes VCC, VCCPLL, and VPUMP currents.

| Table 2-17 • | Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices |

|--------------|--------------------------------------------------------------------------------------|

|              | For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage                                 |

|           |                                                                   | [                              | Device-Spe | cific Dyna   | mic Power   | r (µW/MHz) |         |

|-----------|-------------------------------------------------------------------|--------------------------------|------------|--------------|-------------|------------|---------|

| Parameter | Definition                                                        | AGLN250                        | AGLN125    | AGLN060      | AGLN020     | AGLN015    | AGLN010 |

| PAC1      | Clock contribution of a Global Rib                                | 2.829                          | 2.875      | 1.728        | 0           | 0          | 0       |

| PAC2      | Clock contribution of a Global Spine                              | 1.731                          | 1.265      | 1.268        | 2.562       | 2.562      | 1.685   |

| PAC3      | Clock contribution of a VersaTile row                             | 0.957                          | 0.963      | 0.967        | 0.862       | 0.862      | 0.858   |

| PAC4      | Clock contribution of a VersaTile used<br>as a sequential module  | 0.098                          | 0.098      | 0.098        | 0.094       | 0.094      | 0.091   |

| PAC5      | First contribution of a VersaTile used<br>as a sequential module  |                                |            | 0.0          | 45          |            |         |

| PAC6      | Second contribution of a VersaTile<br>used as a sequential module | rsaTile 0.186                  |            |              |             |            |         |

| PAC7      | Contribution of a VersaTile used as a combinatorial module        |                                |            | 0.1          | 11          |            |         |

| PAC8      | Average contribution of a routing net                             |                                | 0.45       |              |             |            |         |

| PAC9      | Contribution of an I/O input pin (standard-dependent)             |                                | See        | e Table 2-13 | 3 on page 2 | 2-9        |         |

| PAC10     | Contribution of an I/O output pin<br>(standard-dependent)         | pin See Table 2-14 on page 2-9 |            |              |             |            |         |

| PAC11     | Average contribution of a RAM block<br>during a read operation    | k 25.00 N/A                    |            |              |             |            |         |

| PAC12     | Average contribution of a RAM block<br>during a write operation   | k 30.00 N/A                    |            |              |             |            |         |

| PAC13     | Dynamic contribution for PLL                                      |                                | 2.10       |              |             | N/A        |         |

## Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 Devices, 1.2 V Core Supply Voltage

|                   |                                                       |                                               | Device                     | -Specific S  | Static Powe | er (mW) |  |  |

|-------------------|-------------------------------------------------------|-----------------------------------------------|----------------------------|--------------|-------------|---------|--|--|

| Parameter         | Definition                                            | AGLN250 AGLN125 AGLN060 AGLN020 AGLN015 AGLN0 |                            |              |             |         |  |  |

| PDC1              | Array static power in Active mode                     |                                               | Se                         | e Table 2-1  | 2 on page 2 | 2-8     |  |  |

| PDC2              | Array static power in Static (Idle)<br>mode           |                                               | See Table 2-12 on page 2-8 |              |             |         |  |  |

| PDC3              | Array static power in Flash*Freeze<br>mode            |                                               | S                          | ee Table 2-9 | 9 on page 2 | 2-7     |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                               | 0.90 N/A                                      |                            |              |             |         |  |  |

| PDC5              | Bank quiescent power<br>(VCCI-dependent) <sup>2</sup> | See Table 2-12 on page 2-8                    |                            |              |             |         |  |  |

Notes:

1. Minimum contribution of the PLL when running at lowest frequency.

2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

IGLOO nano DC and Switching Characteristics

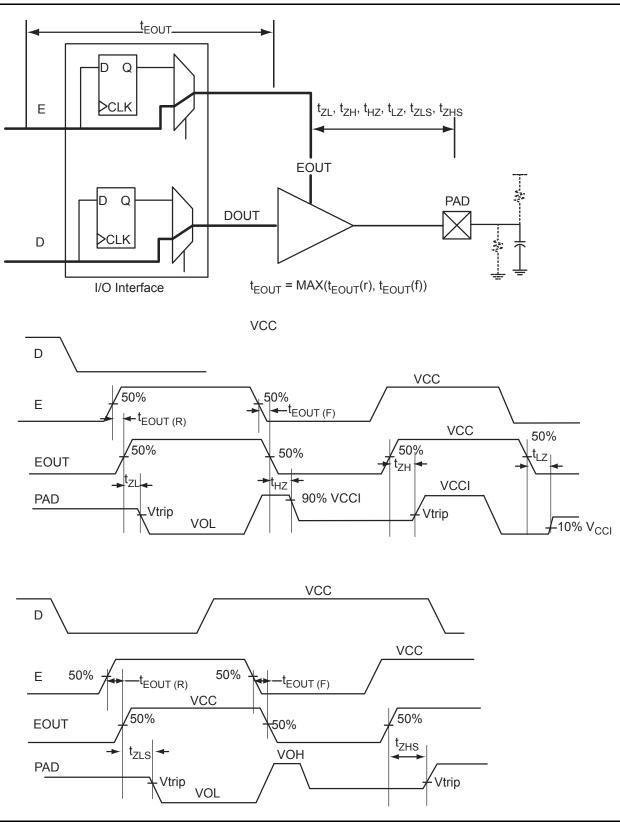

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

IGLOO nano DC and Switching Characteristics

#### Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|                         | R <sub>(WEAK PL</sub> | JLL-UP) <sup>1</sup> (Ω) | $R_{(WEAK PULL-DOWN)}^2(\Omega)$ |       |  |

|-------------------------|-----------------------|--------------------------|----------------------------------|-------|--|

| VCCI                    | Min.                  | Max.                     | Min.                             | Max.  |  |

| 3.3 V                   | 10 K                  | 45 K                     | 10 K                             | 45 K  |  |

| 3.3 V (wide range I/Os) | 10 K                  | 45 K                     | 10 K                             | 45 K  |  |

| 2.5 V                   | 11 K                  | 55 K                     | 12 K                             | 74 K  |  |

| 1.8 V                   | 18 K                  | 70 K                     | 17 K                             | 110 K |  |

| 1.5 V                   | 19 K                  | 90 K                     | 19 K                             | 140 K |  |

| 1.2 V                   | 25 K                  | 110 K                    | 25 K                             | 150 K |  |

| 1.2 V (wide range I/Os) | 19 K                  | 110 K                    | 19 K                             | 150 K |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

#### Table 2-30 • I/O Short Currents IOSH/IOSL

|                            | Drive Strength | IOSL (mA)*           | IOSH (mA)*            |

|----------------------------|----------------|----------------------|-----------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA           | 25                   | 27                    |

| _                          | 4 mA           | 25                   | 27                    |

| Γ                          | 6 mA           | 51                   | 54                    |

| Γ                          | 8 mA           | 51                   | 54                    |

| 3.3 V LVCMOS Wide Range    | 100 µA         | Same as equivalent s | oftware default drive |

| 2.5 V LVCMOS               | 2 mA           | 16                   | 18                    |

| Γ                          | 4 mA           | 16                   | 18                    |

|                            | 6 mA           | 32                   | 37                    |

| Γ                          | 8 mA           | 32                   | 37                    |

| 1.8 V LVCMOS               | 2 mA           | 9                    | 11                    |

| Γ                          | 4 mA           | 17                   | 22                    |

| 1.5 V LVCMOS               | 2 mA           | 13                   | 16                    |

| 1.2 V LVCMOS               | 1 mA           | 10                   | 13                    |

| 1.2 V LVCMOS Wide Range    | 100 µA         | 10                   | 13                    |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

IGLOO nano DC and Switching Characteristics

### Single-Ended I/O Characteristics

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | ΊL        | v         | н         | VOL       | VOH       | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 25                      | 27                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 25                      | 27                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 51                      | 54                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 51                      | 54                      | 10               | 10               |

Table 2-34 • Minimum and Maximum DC Input and Output Levels

Notes:

1.  $I_{IL}$  is the input leakage current per I/O pin over recommended operating conditions where -0.3 < VIN < VIL.

2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

Test Point

$$rac{1}{5}$$

pF  $R = 1 k$

Datapath  $rac{1}{5}$  pF  $R = 1 k$

Enable Path  $rac{1}{5}$  pF for  $t_{LZ} / t_{ZL} / t_{ZLS}$

$rac{1}{5}$  pF for  $t_{ZH} / t_{ZHS} / t_{ZL} / t_{ZLS}$

#### Figure 2-7 • AC Loading

#### Table 2-35 • 3.3 V LVTTL/LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

IGLOO nano DC and Switching Characteristics

#### Timing Characteristics

#### Applies to 1.5 V DC Core Voltage

#### Table 2-53 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 5.44            | 0.19             | 1.03            | 1.44             | 0.66              | 5.25            | 5.44            | 1.69            | 1.35            | ns    |

| 4 mA           | STD         | 0.97              | 4.44            | 0.19             | 1.03            | 1.44             | 0.66              | 4.37            | 4.44            | 1.99            | 2.11            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-54 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.64            | 0.19             | 1.03            | 1.44             | 0.66              | 2.59            | 2.64            | 1.69            | 1.40            | ns    |

| 4 mA           | STD         | 0.97              | 2.08            | 0.19             | 1.03            | 1.44             | 0.66              | 2.12            | 1.95            | 1.99            | 2.19            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Applies to 1.2 V DC Core Voltage

#### Table 2-55 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 5.92            | 0.26             | 1.13            | 1.59             | 1.10              | 5.72            | 5.92            | 2.11            | 1.95            | ns    |

| 4 mA           | STD         | 1.55              | 4.91            | 0.26             | 1.13            | 1.59             | 1.10              | 4.82            | 4.91            | 2.42            | 2.73            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Table 2-56 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 3.05            | 0.26             | 1.13            | 1.59             | 1.10              | 3.01            | 3.05            | 2.10            | 2.00            | ns    |

| 4 mA           | STD         | 1.55              | 2.49            | 0.26             | 1.13            | 1.59             | 1.10              | 2.53            | 2.34            | 2.42            | 2.81            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

#### Timing Characteristics

#### Applies to 1.5 V DC Core Voltage

#### Table 2-59 • 1.5 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 5.39            | 0.19             | 1.19            | 1.62             | 0.66              | 5.48            | 5.39            | 2.02            | 2.06            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-60 • 1.5 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V

|                |             |                   | J               | ,                |                 |                  |                   | ,               |                 |                 |                 |       |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

| 2 mA           | STD         | 0.97              | 2.39            | 0.19             | 1.19            | 1.62             | 0.66              | 2.44            | 2.24            | 2.02            | 2.15            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Applies to 1.2 V DC Core Voltage

## Table 2-61 • 1.5 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.4 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 5.87            | 0.26             | 1.27            | 1.77             | 1.10              | 5.92            | 5.87            | 2.45            | 2.65            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-62 • 1.5 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage Commercial Case Conditional T = 70°C Worst Case VCC = 1.14 V

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.4 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 2.78            | 0.26             | 1.27            | 1.77             | 1.10              | 2.82            | 2.62            | 2.44            | 2.74            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

#### Table 2-71 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-13 on page 2-43 for more information.

IGLOO nano DC and Switching Characteristics

#### 1.2 V DC Core Voltage

## Table 2-77 • Output Enable Register Propagation Delays Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                            | Std. | Units |  |

|-----------------------|------------------------------------------------------------------------|------|-------|--|

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                               | 1.10 | ns    |  |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 1.15 | ns    |  |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |  |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.65 | ns    |  |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.65 | ns    |  |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |  |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |  |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |  |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |  |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |  |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |  |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Enable Register          | 0.31 | ns    |  |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Enable Register           | 0.28 | ns    |  |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## **VersaTile Characteristics**

### VersaTile Specifications as a Combinatorial Module

The IGLOO nano library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide for Software v10.1*.

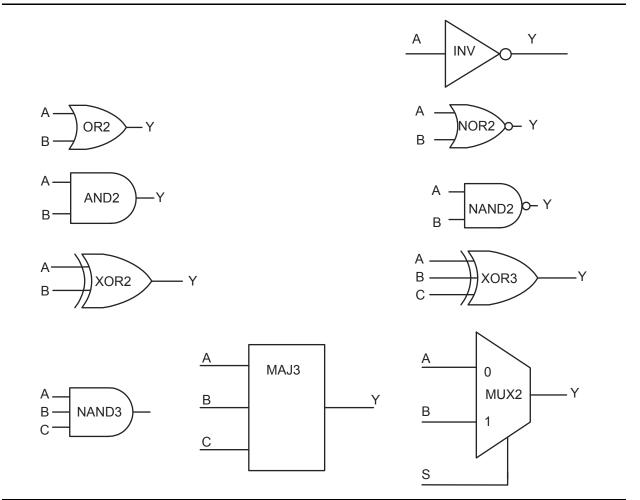

Figure 2-21 • Sample of Combinatorial Cells

IGLOO nano DC and Switching Characteristics

## Table 2-96 • AGLN020 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-97 • AGLN060 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |  |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|--|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |  |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.02              | 2.42              | ns    |  |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.09              | 2.65              | ns    |  |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |  |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |  |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.56              | ns    |  |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano DC and Switching Characteristics

### Timing Waveforms

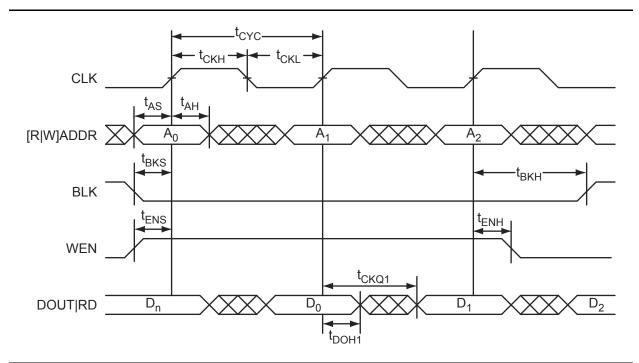

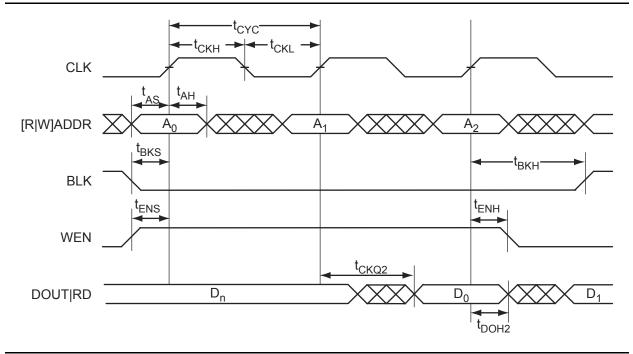

Figure 2-29 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

### **Timing Characteristics**

1.5 V DC Core Voltage

#### Table 2-102 • RAM4K9

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.69 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.13 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.68 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 1.37 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.13 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.59 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.30 | ns    |

| t <sub>CKQ1</sub>     | Clock HIGH to new data valid on DOUT (output retained, WMODE = 0)                                                   | 2.94 | ns    |

|                       | Clock HIGH to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.55 | ns    |

| t <sub>CKQ2</sub>     | Clock HIGH to new data valid on DOUT (pipelined)                                                                    | 1.51 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address; applicable C to closing edge     |      | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge | 0.35 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge | 0.41 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                    | 1.72 | ns    |

|                       | RESET Low to data out Low on DOUT (pipelined)                                                                       | 1.72 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.51 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 2.68 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.68 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 6.24 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 160  | MHz   |

Notes:

1. For more information, refer to the application note AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based FPGAs and SoC FPGAs App Note.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-15 for more details.

#### **Timing Characteristics**

1.5 V DC Core Voltage

#### Table 2-110 • JTAG 1532

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | Std.  | Units |

|----------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 1.00  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 2.00  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 1.00  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 2.00  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 25.00 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 15    | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.58  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

#### *Table 2-111* • JTAG 1532

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter                                    | Description                 | Std.  | Units |

|----------------------------------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub> Test Data Input Setup Time |                             | 1.50  | ns    |

| t <sub>DIHD</sub>                            | Test Data Input Hold Time   | 3.00  | ns    |

| t <sub>TMSSU</sub>                           | Test Mode Select Setup Time | 1.50  | ns    |

| t <sub>TMDHD</sub>                           | Test Mode Select Hold Time  | 3.00  | ns    |

| t <sub>TCK2Q</sub>                           | Clock to Q (data out)       | 11.00 | ns    |

| t <sub>RSTB2Q</sub>                          | Reset to Q (data out)       | 30.00 | ns    |

| F <sub>TCKMAX</sub>                          | TCK Maximum Frequency       | 9.00  | MHz   |

| t <sub>TRSTREM</sub>                         | ResetB Removal Time         | 1.18  | ns    |

| t <sub>TRSTREC</sub>                         | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub>                         | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano Low Power Flash FPGAs

|            | UC81                 | ] [        | UC81                 |  |

|------------|----------------------|------------|----------------------|--|

| Pin Number | AGLN030Z<br>Function | Pin Number | AGLN030Z<br>Function |  |

| A1         | IO00RSB0             | D9         | IO30RSB0             |  |

| A2         | IO02RSB0             | E1         | GEB0/IO71RSB1        |  |

| A3         | IO06RSB0             | E2         | GEA0/IO72RSB1        |  |

| A4         | IO11RSB0             | E3         | GEC0/IO73RSB1        |  |

| A5         | IO16RSB0             | E4         | VCCIB1               |  |

| A6         | IO19RSB0             | E5         | VCC                  |  |

| A7         | IO22RSB0             | E6         | VCCIB0               |  |

| A8         | IO24RSB0             | E7         | GDC0/IO32RSB0        |  |

| A9         | IO26RSB0             | E8         | GDA0/IO33RSB0        |  |

| B1         | IO81RSB1             | E9         | GDB0/IO34RSB0        |  |

| B2         | IO04RSB0             | F1         | IO68RSB1             |  |

| B3         | IO10RSB0             | F2         | IO67RSB1             |  |

| B4         | IO13RSB0             | F3         | IO64RSB1             |  |

| B5         | IO15RSB0             | F4         | GND                  |  |

| B6         | IO20RSB0             | F5         | VCCIB1               |  |

| B7         | IO21RSB0             | F6         | IO47RSB1             |  |

| B8         | IO28RSB0             | F7         | IO36RSB0             |  |

| B9         | IO25RSB0             | F8         | IO38RSB0             |  |

| C1         | IO79RSB1             | F9         | IO40RSB0             |  |

| C2         | IO80RSB1             | G1         | IO65RSB1             |  |

| C3         | IO08RSB0             | G2         | IO66RSB1             |  |

| C4         | IO12RSB0             | G3         | IO57RSB1             |  |

| C5         | IO17RSB0             | G4         | IO53RSB1             |  |

| C6         | IO14RSB0             | G5         | IO49RSB1             |  |

| C7         | IO18RSB0             | G6         | IO45RSB1             |  |

| C8         | IO29RSB0             | G7         | IO46RSB1             |  |

| C9         | IO27RSB0             | G8         | VJTAG                |  |

| D1         | IO74RSB1             | G9         | TRST                 |  |

| D2         | IO76RSB1             | H1         | IO62RSB1             |  |

| D3         | IO77RSB1             | H2         | FF/IO60RSB1          |  |

| D4         | VCC                  | H3         | IO58RSB1             |  |

| D5         | VCCIB0               | H4         | IO54RSB1             |  |

| D6         | GND                  | H5         | IO48RSB1             |  |

| D7         | IO23RSB0             | H6         | IO43RSB1             |  |

| D8         | IO31RSB0             | H7         | IO42RSB1             |  |

| UC81       |                      |  |  |  |

|------------|----------------------|--|--|--|

| Pin Number | AGLN030Z<br>Function |  |  |  |

| H8         | TDI                  |  |  |  |

| H9         | TDO                  |  |  |  |

| J1         | IO63RSB1             |  |  |  |

| J2         | IO61RSB1             |  |  |  |

| J3         | IO59RSB1             |  |  |  |

| J4         | IO56RSB1             |  |  |  |

| J5         | IO52RSB1             |  |  |  |

| J6         | IO44RSB1             |  |  |  |

| J7         | ТСК                  |  |  |  |

| J8         | TMS                  |  |  |  |

| J9         | VPUMP                |  |  |  |

IGLOO nano Low Power Flash FPGAs

| VQ100      |                      |            | VQ100                |            | VQ100                |  |

|------------|----------------------|------------|----------------------|------------|----------------------|--|

| Pin Number | AGLN030Z<br>Function | Pin Number | AGLN030Z<br>Function | Pin Number | AGLN030Z<br>Function |  |

| 1          | GND                  | 36         | IO51RSB1             | 71         | IO29RSB0             |  |

| 2          | IO82RSB1             | 37         | VCC                  | 72         | IO28RSB0             |  |

| 3          | IO81RSB1             | 38         | GND                  | 73         | IO27RSB0             |  |

| 4          | IO80RSB1             | 39         | VCCIB1               | 74         | IO26RSB0             |  |

| 5          | IO79RSB1             | 40         | IO49RSB1             | 75         | IO25RSB0             |  |

| 6          | IO78RSB1             | 41         | IO47RSB1             | 76         | IO24RSB0             |  |

| 7          | IO77RSB1             | 42         | IO46RSB1             | 77         | IO23RSB0             |  |

| 8          | IO76RSB1             | 43         | IO45RSB1             | 78         | IO22RSB0             |  |

| 9          | GND                  | 44         | IO44RSB1             | 79         | IO21RSB0             |  |

| 10         | IO75RSB1             | 45         | IO43RSB1             | 80         | IO20RSB0             |  |

| 11         | IO74RSB1             | 46         | IO42RSB1             | 81         | IO19RSB0             |  |

| 12         | GEC0/IO73RSB1        | 47         | ТСК                  | 82         | IO18RSB0             |  |

| 13         | GEA0/IO72RSB1        | 48         | TDI                  | 83         | IO17RSB0             |  |

| 14         | GEB0/IO71RSB1        | 49         | TMS                  | 84         | IO16RSB0             |  |

| 15         | IO70RSB1             | 50         | NC                   | 85         | IO15RSB0             |  |

| 16         | IO69RSB1             | 51         | GND                  | 86         | IO14RSB0             |  |

| 17         | VCC                  | 52         | VPUMP                | 87         | VCCIB0               |  |

| 18         | VCCIB1               | 53         | NC                   | 88         | GND                  |  |

| 19         | IO68RSB1             | 54         | TDO                  | 89         | VCC                  |  |

| 20         | IO67RSB1             | 55         | TRST                 | 90         | IO12RSB0             |  |

| 21         | IO66RSB1             | 56         | VJTAG                | 91         | IO10RSB0             |  |

| 22         | IO65RSB1             | 57         | IO41RSB0             | 92         | IO08RSB0             |  |

| 23         | IO64RSB1             | 58         | IO40RSB0             | 93         | IO07RSB0             |  |

| 24         | IO63RSB1             | 59         | IO39RSB0             | 94         | IO06RSB0             |  |

| 25         | IO62RSB1             | 60         | IO38RSB0             | 95         | IO05RSB0             |  |

| 26         | IO61RSB1             | 61         | IO37RSB0             | 96         | IO04RSB0             |  |

| 27         | FF/IO60RSB1          | 62         | IO36RSB0             | 97         | IO03RSB0             |  |

| 28         | IO59RSB1             | 63         | GDB0/IO34RSB0        | 98         | IO02RSB0             |  |

| 29         | IO58RSB1             | 64         | GDA0/IO33RSB0        | 99         | IO01RSB0             |  |

| 30         | IO57RSB1             | 65         | GDC0/IO32RSB0        | 100        | IO00RSB0             |  |

| 31         | IO56RSB1             | 66         | VCCIB0               |            |                      |  |

| 32         | IO55RSB1             | 67         | GND                  |            |                      |  |

| 33         | IO54RSB1             | 68         | VCC                  |            |                      |  |

| 34         | IO53RSB1             | 69         | IO31RSB0             |            |                      |  |

| 35         | IO52RSB1             | 70         | IO30RSB0             |            |                      |  |