Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 3072                                                                        |

| Total RAM Bits                 | 36864                                                                       |

| Number of I/O                  | 71                                                                          |

| Number of Gates                | 125000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 100-TQFP                                                                    |

| Supplier Device Package        | 100-VQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln125v5-zvqg100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

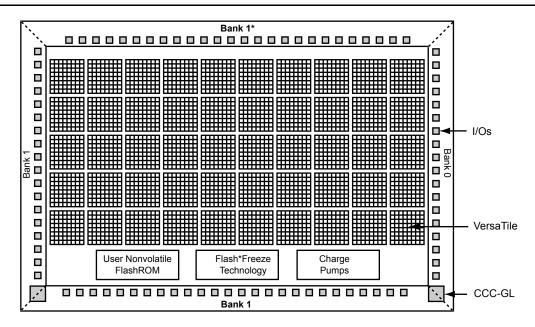

Note: \*Bank 0 for the AGLN030 device

Figure 1-1 • IGLOO Device Architecture Overview with Two I/O Banks and No RAM (AGLN010 and AGLN030)

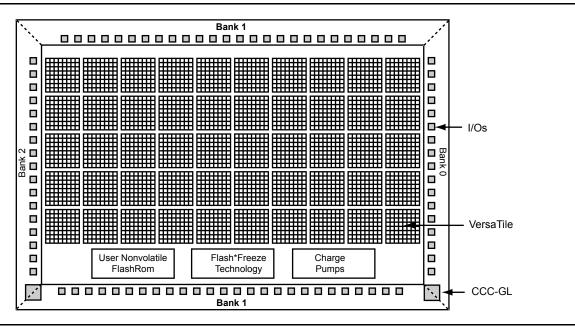

Figure 1-2 • IGLOO Device Architecture Overview with Three I/O Banks and No RAM (AGLN015 and AGLN020)

1-4 Revision 19

## Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

- Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-7 on page 1-9).

- 5. Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

Figure 1-7 • I/O States During Programming Window

## PLL Behavior at Brownout Condition

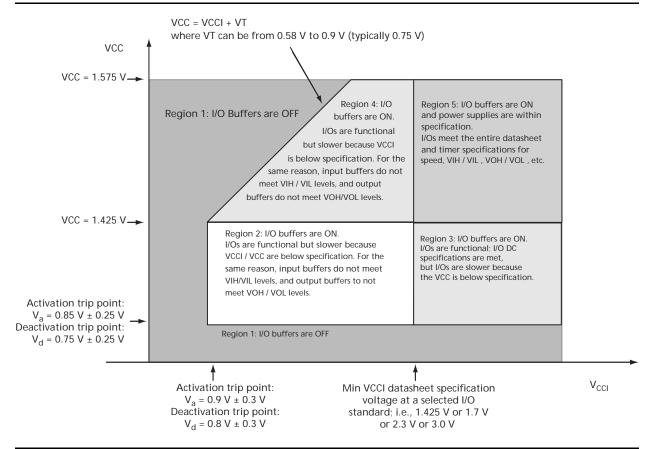

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper powerup behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels (see Figure 2-1 and Figure 2-2 on page 2-5 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels (0.75 V  $\pm$  0.25 V for V5 devices, and 0.75 V  $\pm$  0.2 V for V2 devices), the PLL output lock signal goes LOW and/or the output clock is lost. Refer to the "Brownout Voltage" section in the "Power-Up/-Down Behavior of Low Power Flash Devices" chapter of the *IGLOO nano FPGA Fabric User's Guide* for information on clock and lock recovery.

## Internal Power-Up Activation Sequence

- Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

To make sure the transition from input buffers to output buffers is clean, ensure that there is no path longer than 100 ns from input buffer to output buffer in your design.

Figure 2-1 • V5 Devices – I/O State as a Function of VCCI and VCC Voltage Levels

2-4 Revision 19

# **Power Consumption of Various Internal Resources**

Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|           |                                                                |         | Device Sp | ecific Dyna  | mic Power   | (µW/MHz) |         |  |

|-----------|----------------------------------------------------------------|---------|-----------|--------------|-------------|----------|---------|--|

| Parameter | Definition                                                     | AGLN250 | AGLN125   | AGLN060      | AGLN020     | AGLN015  | AGLN010 |  |

| PAC1      | Clock contribution of a Global Rib                             | 4.421   | 4.493     | 2.700        | 0           | 0        | 0       |  |

| PAC2      | Clock contribution of a Global Spine                           | 2.704   | 1.976     | 1.982        | 4.002       | 4.002    | 2.633   |  |

| PAC3      | Clock contribution of a VersaTile row                          | 1.496   | 1.504     | 1.511        | 1.346       | 1.346    | 1.340   |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.152   | 0.153     | 0.153        | 0.148       | 0.148    | 0.143   |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  | 0.057   |           |              |             |          |         |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.207   |           |              |             |          |         |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     |         |           | 0.           | 17          |          |         |  |

| PAC8      | Average contribution of a routing net                          |         |           | 0.           | .7          |          |         |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          |         | Se        | e Table 2-13 | 3 on page 2 | ?-9.     |         |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         |         |           | See Tab      | le 2-14.    |          |         |  |

| PAC11     | Average contribution of a RAM block during a read operation    |         | 25.00     |              | N/A         |          |         |  |

| PAC12     | Average contribution of a RAM block during a write operation   |         | 30.00     |              | N/A         |          |         |  |

| PAC13     | Dynamic contribution for PLL 2.70                              |         |           |              | _           | N/A      |         |  |

Table 2-16 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|                   |                                                       |                            | Device                     | -Specific   | Static Powe | er (mW) |         |  |  |

|-------------------|-------------------------------------------------------|----------------------------|----------------------------|-------------|-------------|---------|---------|--|--|

| Parameter         | Definition                                            | AGLN250                    | AGLN125                    | AGLN060     | AGLN020     | AGLN015 | AGLN010 |  |  |

| PDC1              | Array static power in Active mode                     | See Table 2-12 on page 2-8 |                            |             |             |         |         |  |  |

|                   | Array static power in Static (Idle) mode              |                            | See Table 2-12 on page 2-8 |             |             |         |         |  |  |

|                   | Array static power in Flash*Freeze mode               |                            | S                          | ee Table 2- | 9 on page 2 | 2-7     |         |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                               | 1.84 N/A                   |                            |             |             |         |         |  |  |

| PDC5              | Bank quiescent power<br>(VCCI-dependent) <sup>2</sup> | See Table 2-12 on page 2-8 |                            |             |             |         |         |  |  |

#### Notes:

- 1. Minimum contribution of the PLL when running at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

2-10 Revision 19

IGLOO nano Low Power Flash FPGAs

## Applies to IGLOO nano at 1.5 V Core Operating Conditions

Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings STD Speed Grade, Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| I/O Standard                            | Drive Strength (mA) | Equivalent Software Default<br>t Drive Strength Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) | tвоит | top  | <sup>‡</sup> DIN | tрү  | tpys | t <sub>EOUT</sub> | <sup>t</sup> zı. | tz <del>1</del> | t <sub>LZ</sub> | t <sub>НZ</sub> | Units |

|-----------------------------------------|---------------------|---------------------------------------------------------------------|-----------|----------------------|-------|------|------------------|------|------|-------------------|------------------|-----------------|-----------------|-----------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS           | 8 mA                | 8 mA                                                                | High      | 5 pF                 | 0.97  | 1.79 | 0.19             | 0.86 | 1.16 | 0.66              | 1.83             | 1.45            | 1.98            | 2.38            | ns    |

| 3.3 V LVCMOS<br>Wide Range <sup>2</sup> | 100 μΑ              | 8 mA                                                                | High      | 5 pF                 | 0.97  | 2.56 | 0.19             | 1.20 | 1.66 | 0.66              | 2.57             | 2.02            | 2.82            | 3.31            | ns    |

| 2.5 V LVCMOS                            | 8 mA                | 8 mA                                                                | High      | 5 pF                 | 0.97  | 1.81 | 0.19             | 1.10 | 1.24 | 0.66              | 1.85             | 1.63            | 1.97            | 2.26            | ns    |

| 1.8 V LVCMOS                            | 4 mA                | 4 mA                                                                | High      | 5 pF                 | 0.97  | 2.08 | 0.19             | 1.03 | 1.44 | 0.66              | 2.12             | 1.95            | 1.99            | 2.19            | ns    |

| 1.5 V LVCMOS                            | 2 mA                | 2 mA                                                                | High      | 5 pF                 | 0.97  | 2.39 | 0.19             | 1.19 | 1.52 | 0.66              | 2.44             | 2.24            | 2.02            | 2.15            | ns    |

#### Notes:

- The minimum drive strength for any LVCMOS 1.2 V or LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range, as specified in the JESD8-B specification.

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## Applies to 1.2 V DC Core Voltage

Table 2-43 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                          | STD            | 1.55              | 6.01            | 0.26             | 1.31            | 1.91             | 1.10              | 6.01            | 5.66            | 3.02            | 3.49            | ns    |

| 100 μΑ            | 4 mA                                                                          | STD            | 1.55              | 6.01            | 0.26             | 1.31            | 1.91             | 1.10              | 6.01            | 5.66            | 3.02            | 3.49            | ns    |

| 100 μΑ            | 6 mA                                                                          | STD            | 1.55              | 5.02            | 0.26             | 1.31            | 1.91             | 1.10              | 5.02            | 4.76            | 3.38            | 4.10            | ns    |

| 100 μΑ            | 8 mA                                                                          | STD            | 1.55              | 5.02            | 0.26             | 1.31            | 1.91             | 1.10              | 5.02            | 4.76            | 3.38            | 4.10            | ns    |

#### Notes:

Table 2-44 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                          | STD            | 1.55              | 3.82            | 0.26             | 1.31            | 1.91             | 1.10              | 3.82            | 3.15            | 3.01            | 3.65            | ns    |

| 100 μΑ            | 4 mA                                                                          | STD            | 1.55              | 3.82            | 0.26             | 1.31            | 1.91             | 1.10              | 3.82            | 3.15            | 3.01            | 3.65            | ns    |

| 100 μΑ            | 6 mA                                                                          | STD            | 1.55              | 3.25            | 0.26             | 1.31            | 1.91             | 1.10              | 3.25            | 2.61            | 3.38            | 4.27            | ns    |

| 100 μΑ            | 8 mA                                                                          | STD            | 1.55              | 3.25            | 0.26             | 1.31            | 1.91             | 1.10              | 3.25            | 2.61            | 3.38            | 4.27            | ns    |

#### Notes:

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 3. Software default selection highlighted in gray.

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

<sup>1.</sup> The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

## 1.2 V LVCMOS (JESD8-12A)

Low-Voltage CMOS for 1.2 V complies with the LVCMOS standard JESD8-12A for general purpose 1.2 V applications. It uses a 1.2 V input buffer and a push-pull output buffer.

Table 2-63 • Minimum and Maximum DC Input and Output Levels

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         | VIH       |             | VOL VOH     |    | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 1 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 1  | 1  | 10                      | 13                      | 10                      | 10                      |

#### Notes:

- 1. I<sub>IL</sub> is the input leakage current per I/O pin over recommended operating conditions where –0.3 < VIN < VIL.

- 2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

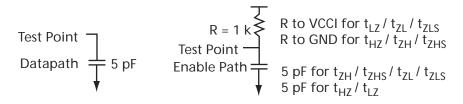

Figure 2-11 • AC Loading

Table 2-64 • 1.2 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.2            | 0.6                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

## **Timing Characteristics**

Applies to 1.2 V DC Core Voltage

Table 2-65 • 1.2 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| <b>Drive Strength</b> | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-----------------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 1 mA                  | STD         | 1.55              | 8.30            | 0.26             | 1.56            | 2.27             | 1.10              | 7.97            | 7.54            | 2.56            | 2.55            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-66 • 1.2 V LVCMOS High Slew

Commercial-Case Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 1 mA           | STD         | 1.55              | 3.50            | 0.26             | 1.56            | 2.27             | 1.10              | 3.37            | 3.10            | 2.55            | 2.66            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-71 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| t <sub>OSUD</sub>     | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| toerecclr             | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

Note: \*See Figure 2-13 on page 2-43 for more information.

2-44 Revision 19

# **Output Register**

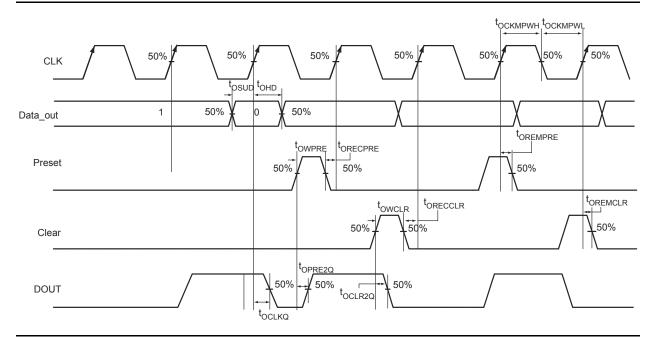

Figure 2-15 • Output Register Timing Diagram

Timing Characteristics

1.5 V DC Core Voltage

Table 2-74 • Output Data Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 1.00 | ns    |

| tosup                | Data Setup Time for the Output Data Register                         | 0.51 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 1.34 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 1.34 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.24 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.24 | ns    |

| towclr               | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.19 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.19 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Data Register          | 0.31 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# **Output Enable Register**

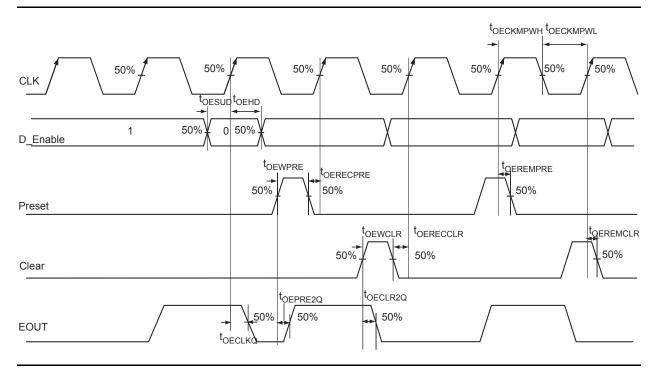

Figure 2-16 • Output Enable Register Timing Diagram

**Timing Characteristics**

1.5 V DC Core Voltage

Table 2-76 • Output Enable Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.75 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         |      | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.13 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.13 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        |      | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Enable Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-70. Table 2-88 to Table 2-96 on page 2-68 present minimum and maximum global clock delays within each device. Minimum and maximum delays are measured with minimum and maximum loading.

## **Timing Characteristics**

1.5 V DC Core Voltage

Table 2-88 • AGLN010 Global Resource

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                           | S                                            | Std.              |       |

|----------------------|-------------------------------------------|----------------------------------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup>                            | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.13                                         | 1.42              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.15                                         | 1.50              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock | nimum Pulse Width HIGH for Global Clock 1.40 |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock  | 1.65                                         |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                                              | 0.35              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-89 • AGLN015 Global Resource Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                               | S                                           | td.               |       |

|----------------------|-----------------------------------------------|---------------------------------------------|-------------------|-------|

| Parameter            | Description                                   | Min. <sup>1</sup>                           | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock              | 1.21                                        | 1.55              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock             | 1.23                                        | 1.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width HIGH for Global Clock     | imum Pulse Width HIGH for Global Clock 1.40 |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock 1.65 |                                             |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock                 |                                             | 0.42              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-64 Revision 19

IGLOO nano Low Power Flash FPGAs

Table 2-90 • AGLN020 Global Resource Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , VCC = 1.425 V

|                      |                                           |                                              | S                 | td.               |       |

|----------------------|-------------------------------------------|----------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               |                                              | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |                                              | 1.21              | 1.55              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |                                              | 1.23              | 1.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | nimum Pulse Width High for Global Clock 1.40 |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                                              | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                                              |                   | 0.42              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-91 • AGLN060 Global Resource Commercial-Case Conditions: T<sub>.I</sub> = 70°C, VCC = 1.425 V

|                      |                                                |  | St                | td.               |       |

|----------------------|------------------------------------------------|--|-------------------|-------------------|-------|

| Parameter            | Description                                    |  | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock               |  | 1.32              | 1.62              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock              |  | 1.34              | 1.71              | ns    |

| t <sub>RCKMPWH</sub> | Ninimum Pulse Width HIGH for Global Clock 1.40 |  |                   | ns                |       |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width LOW for Global Clock 1.65  |  |                   | ns                |       |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock                  |  |                   | 0.38              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-96 • AGLN020 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                                |                                 | S                 | td.               |       |

|----------------------|------------------------------------------------|---------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                                    |                                 | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock               | nput Low Delay for Global Clock |                   | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock 1.9          |                                 | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock 1.40 |                                 |                   | ns                |       |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock 1.65  |                                 |                   | ns                |       |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock                  |                                 |                   | 0.61              | ns    |

#### Notes:

- Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-97 • AGLN060 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.                                        |                   | td.               |       |

|----------------------|-------------------------------------------|---------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               |                                             | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |                                             | 2.02              | 2.42              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |                                             | 2.09              | 2.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | imum Pulse Width High for Global Clock 1.40 |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                                             | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                                             |                   | 0.56              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-68 Revision 19

# **Clock Conditioning Circuits**

## **CCC Electrical Specifications**

**Timing Characteristics**

Table 2-100 • IGLOO nano CCC/PLL Specification For IGLOO nano V2 OR V5 Devices, 1.5 V DC Core Supply Voltage

| Parameter                                                               |                 | Min.        | Тур.                | Max.     | Units |

|-------------------------------------------------------------------------|-----------------|-------------|---------------------|----------|-------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>        |                 | 1.5         |                     | 250      | MHz   |

| Clock Conditioning Circuitry Output Frequency fout_co                   | CC              | 0.75        |                     | 250      | MHz   |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>           |                 |             | 360 <sup>3</sup>    |          | ps    |

| Number of Programmable Values in Each Programmal                        | ole Delay Block |             |                     | 32       |       |

| Serial Clock (SCLK) for Dynamic PLL <sup>4,9</sup>                      |                 |             |                     | 100      | MHz   |

| Input Cycle-to-Cycle Jitter (peak magnitude)                            |                 |             |                     | 1        | ns    |

| Acquisition Time                                                        |                 |             |                     |          |       |

|                                                                         | LockControl = 0 |             |                     | 300      | μs    |

|                                                                         | LockControl = 1 |             |                     | 6.0      | ms    |

| Tracking Jitter <sup>5</sup>                                            |                 |             |                     |          |       |

|                                                                         | LockControl = 0 |             |                     | 2.5      | ns    |

|                                                                         | LockControl = 1 |             |                     | 1.5      | ns    |

| Output Duty Cycle                                                       | •               | 48.5        |                     | 51.5     | %     |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>              |                 | 1.25        |                     | 15.65    | ns    |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2,</sup>             |                 | 0.025       |                     | 15.65    | ns    |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                       |                 |             | 3.5                 |          | ns    |

| VCO Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> <sup>6</sup> | Max Peak-to-Pea | k Jitter Da | ta <sup>6,7,8</sup> |          |       |

|                                                                         | SSO ≤ 2         | SSO ≤ 4     | SSO ≤ 8             | SSO ≤ 16 |       |

| 0.75 MHz to 50 MHz                                                      | 0.50            | 0.60        | 0.80                | 1.20     | %     |

| 50 MHz to 250 MHz                                                       | 2.50            | 4.00        | 6.00                | 12.00    | %     |

#### Notes:

- 1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for deratings.

- 2.  $T_{.1} = 25$ °C, VCC = 1.5 V

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

- 4. Maximum value obtained for a STD speed grade device in Worst-Case Commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 and Table 2-7 on page 2-7 for derating values.

- 5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

- 6. VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the % jitter. The VCO jitter (in ps) applies to CCC\_OUT, regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps, no matter what the settings are for the output divider.

- 7. Measurements done with LVTTL 3.3 V 8 mA I/O drive strength and high slew rate. VCC/VCCPLL = 1.425 V, VCCI = 3.3 V, VQ/PQ/TQ type of packages, 20 pF load.

- 8. SSOs are outputs that are synchronous to a single clock domain and have their clock-to-out times within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO nano FPGA Fabric User's Guide.

- 9. The AGLN010, AGLN015, and AGLN020 devices do not support PLLs.

2-70 Revision 19

IGLOO nano Low Power Flash FPGAs

# **Timing Characteristics**

1.5 V DC Core Voltage

Table 2-102 • RAM4K9

Commercial-Case Conditions:  $T_J = 70^{\circ}C$ , Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.69 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.13 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.68 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 1.37 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.13 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.59 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.30 | ns    |

| t <sub>CKQ1</sub>     | Clock HIGH to new data valid on DOUT (output retained, WMODE = 0)                                                   | 2.94 | ns    |

|                       | Clock HIGH to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.55 | ns    |

| t <sub>CKQ2</sub>     | Clock HIGH to new data valid on DOUT (pipelined)                                                                    | 1.51 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address; applicable to closing edge       | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge | 0.35 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge | 0.41 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                    | 1.72 | ns    |

|                       | RESET Low to data out Low on DOUT (pipelined)                                                                       | 1.72 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.51 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 2.68 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.68 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 6.24 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 160  | MHz   |

### Notes:

<sup>1.</sup> For more information, refer to the application note AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based FPGAs and SoC FPGAs App Note.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

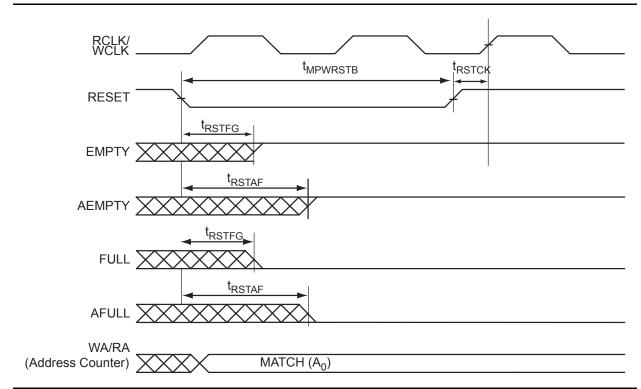

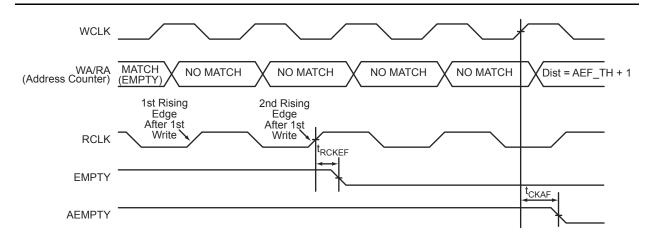

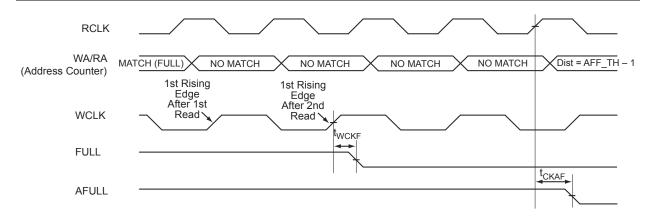

Figure 2-36 • FIFO Reset

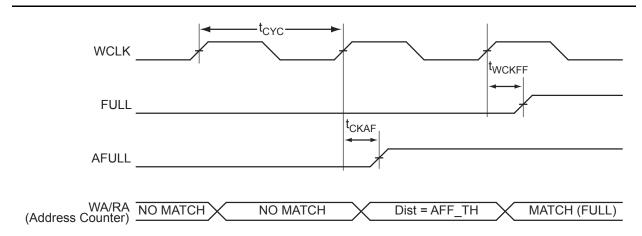

Figure 2-37 • FIFO EMPTY Flag and AEMPTY Flag Assertion

Figure 2-38 • FIFO FULL Flag and AFULL Flag Assertion

Figure 2-39 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

Figure 2-40 • FIFO FULL Flag and AFULL Flag Deassertion

2-84 Revision 19

IGLOO nano Low Power Flash FPGAs

# Timing Characteristics

1.5 V DC Core Voltage

Table 2-106 • FIFO

Worst Commercial-Case Conditions:  $T_J = 70$ °C, VCC = 1.425 V

| Parameter            | Description                                       | Std.    | Units |

|----------------------|---------------------------------------------------|---------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.66    | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.13    | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.30    | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00    | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        |         | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.20    | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.77    | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    |         | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     |         | ns    |

| t <sub>WCKFF</sub>   | F WCLK High to Full Flag Valid 2                  |         | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 10.71   | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 2.90    | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 10.60   | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out LOW on RD (flow-through)    | 1.68    | ns    |

|                      | RESET Low to Data Out LOW on RD (pipelined)       | 1.68    | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.51    | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery 2.                                 |         | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.68 ns |       |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 6.24    | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 160     | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

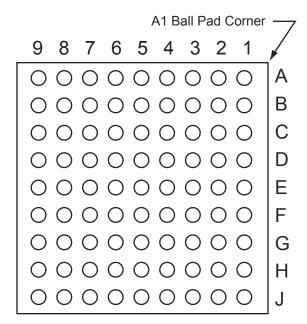

Package Pin Assignments

## **CS81**

Note: This is the bottom view of the package.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

4-6 Revision 19

Package Pin Assignments

|            | VQ100            |

|------------|------------------|

| Pin Number | AGLN250 Function |

| 1          | GND              |

| 2          | GAA2/IO67RSB3    |

| 3          | IO66RSB3         |

| 4          | GAB2/IO65RSB3    |

| 5          | IO64RSB3         |

| 6          | GAC2/IO63RSB3    |

| 7          | IO62RSB3         |

| 8          | IO61RSB3         |

| 9          | GND              |

| 10         | GFB1/IO60RSB3    |

| 11         | GFB0/IO59RSB3    |

| 12         | VCOMPLF          |

| 13         | GFA0/IO57RSB3    |

| 14         | VCCPLF           |

| 15         | GFA1/IO58RSB3    |

| 16         | GFA2/IO56RSB3    |

| 17         | VCC              |

| 18         | VCCIB3           |

| 19         | GFC2/IO55RSB3    |

| 20         | GEC1/IO54RSB3    |

| 21         | GEC0/IO53RSB3    |

| 22         | GEA1/IO52RSB3    |

| 23         | GEA0/IO51RSB3    |

| 24         | VMV3             |

| 25         | GNDQ             |

| 26         | GEA2/IO50RSB2    |

| 27         | FF/GEB2/IO49RSB2 |

| 28         | GEC2/IO48RSB2    |

| 29         | IO47RSB2         |

| 30         | IO46RSB2         |

| 31         | IO45RSB2         |

| 32         | IO44RSB2         |

| 33         | IO43RSB2         |

| 34         | IO42RSB2         |

| 35         | IO41RSB2         |

| 36         | IO40RSB2         |

| VQ100      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AGLN250 Function |  |  |

| 37         | VCC              |  |  |

| 38         | GND              |  |  |

| 39         | VCCIB2           |  |  |

| 40         | IO39RSB2         |  |  |

| 41         | IO38RSB2         |  |  |

| 42         | IO37RSB2         |  |  |

| 43         | GDC2/IO36RSB2    |  |  |

| 44         | GDB2/IO35RSB2    |  |  |

| 45         | GDA2/IO34RSB2    |  |  |

| 46         | GNDQ             |  |  |

| 47         | TCK              |  |  |

| 48         | TDI              |  |  |

| 49         | TMS              |  |  |

| 50         | VMV2             |  |  |

| 51         | GND              |  |  |

| 52         | VPUMP            |  |  |

| 53         | NC               |  |  |

| 54         | TDO              |  |  |

| 55         | TRST             |  |  |

| 56         | VJTAG            |  |  |

| 57         | GDA1/IO33RSB1    |  |  |

| 58         | GDC0/IO32RSB1    |  |  |

| 59         | GDC1/IO31RSB1    |  |  |

| 60         | IO30RSB1         |  |  |

| 61         | GCB2/IO29RSB1    |  |  |

| 62         | GCA1/IO27RSB1    |  |  |

| 63         | GCA0/IO28RSB1    |  |  |

| 64         | GCC0/IO26RSB1    |  |  |

| 65         | GCC1/IO25RSB1    |  |  |

| 66         | VCCIB1           |  |  |

| 67         | GND              |  |  |

| 68         | VCC              |  |  |

| 69         | IO24RSB1         |  |  |

| 70         | GBC2/IO23RSB1    |  |  |

| 71         | GBB2/IO22RSB1    |  |  |

| 72         | IO21RSB1         |  |  |

| VQ100      |                  |

|------------|------------------|

| Pin Number | AGLN250 Function |

| 73         | GBA2/IO20RSB1    |

| 74         | VMV1             |

| 75         | GNDQ             |

| 76         | GBA1/IO19RSB0    |

| 77         | GBA0/IO18RSB0    |

| 78         | GBB1/IO17RSB0    |

| 79         | GBB0/IO16RSB0    |

| 80         | GBC1/IO15RSB0    |

| 81         | GBC0/IO14RSB0    |

| 82         | IO13RSB0         |

| 83         | IO12RSB0         |

| 84         | IO11RSB0         |

| 85         | IO10RSB0         |

| 86         | IO09RSB0         |

| 87         | VCCIB0           |

| 88         | GND              |

| 89         | VCC              |

| 90         | IO08RSB0         |

| 91         | IO07RSB0         |

| 92         | IO06RSB0         |

| 93         | GAC1/IO05RSB0    |

| 94         | GAC0/IO04RSB0    |

| 95         | GAB1/IO03RSB0    |

| 96         | GAB0/IO02RSB0    |

| 97         | GAA1/IO01RSB0    |

| 98         | GAA0/IO00RSB0    |

| 99         | GNDQ             |

| 100        | VMV0             |

4-28 Revision 19