# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2014.10                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 6144                                                                       |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 68                                                                         |

| Number of Gates                | 250000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                   |

| Supplier Device Package        | 100-VQFP (14x14)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln250v2-vqg100 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Marking**

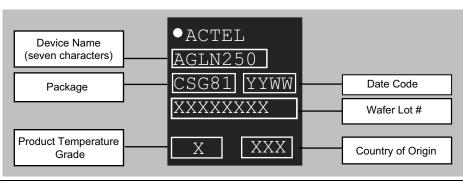

Microsemi normally topside marks the full ordering part number on each device. There are some exceptions to this, such as some of the Z feature grade nano devices, the V2 designator for IGLOO devices, and packages where space is physically limited. Packages that have limited characters available are UC36, UC81, CS81, QN48, QN68, and QFN132. On these specific packages, a subset of the device marking will be used that includes the required legal information and as much of the part number as allowed by character limitation of the device. In this case, devices will have a truncated device marking and may exclude the applications markings, such as the I designator for Industrial Devices or the ES designator for Engineering Samples.

Figure 1 shows an example of device marking based on the AGLN250V2-CSG81. The actual mark will vary by the device/package combination ordered.

Figure 1 • Example of Device Marking for Small Form Factor Packages

## IGLOO nano Products Available in the Z Feature Grade

| IGLOO nano-Z Devices | AGLN030Z* | AGLN060Z* | AGLN125Z* | AGLN250Z* |

|----------------------|-----------|-----------|-----------|-----------|

|                      | QN48      | -         | -         | -         |

|                      | QN68      | -         | -         | -         |

|                      | UC81      | -         | -         | -         |

|                      | CS81      | CS81      | CS81      | CS81      |

| Packages             | VQ100     | VQ100     | VQ100     | VQ100     |

Note: \*Not recommended for new designs.

## **Temperature Grade Offerings**

|         | AGLN010 | AGLN015 <sup>*</sup> | AGLN020 |                       | AGLN060               | AGLN125               | AGLN250               |

|---------|---------|----------------------|---------|-----------------------|-----------------------|-----------------------|-----------------------|

| Package |         |                      |         | AGLN030Z <sup>*</sup> | AGLN060Z <sup>*</sup> | AGLN125Z <sup>*</sup> | AGLN250Z <sup>*</sup> |

| UC36    | C, I    | -                    | -       | -                     | -                     | -                     | -                     |

| QN48    | C, I    | -                    | -       | C, I                  | -                     | -                     | -                     |

| QN68    | -       | C, I                 | C, I    | C, I                  | -                     | -                     | -                     |

| UC81    | -       | -                    | C, I    | C, I                  | -                     | -                     | -                     |

| CS81    | -       | -                    | C, I    | C, I                  | C, I                  | C, I                  | C, I                  |

| VQ100   | -       | -                    | -       | C, I                  | C, I                  | C, I                  | C, I                  |

Note: \* Not recommended for new designs.

C = Enhanced Commercial temperature range: -20°C to +85°C junction temperature

*I* = Industrial temperature range: -40°C to +100°C junction temperature

Contact your local Microsemi representative for device availability: http://www.microsemi.com/soc/contact/default.aspx.

IGLOO nano DC and Switching Characteristics

### **Thermal Characteristics**

### Introduction

The temperature variable in the Microsemi Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because dynamic and static power consumption cause the chip junction temperature to be higher than the ambient temperature.

EQ 1 can be used to calculate junction temperature.

$T_J$  = Junction Temperature =  $\Delta T + T_A$

where:

T<sub>A</sub> = Ambient temperature

$\Delta T$  = Temperature gradient between junction (silicon) and ambient  $\Delta T$  =  $\theta_{ia}$  \* P

$\theta_{ja}$  = Junction-to-ambient of the package.  $\theta_{ja}$  numbers are located in Figure 2-5.

P = Power dissipation

### Package Thermal Characteristics

The device junction-to-case thermal resistivity is  $\theta_{jc}$  and the junction-to-ambient air thermal resistivity is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown for two air flow rates. The maximum operating junction temperature is 100°C. EQ 2 shows a sample calculation of the maximum operating power dissipation allowed for a 484-pin FBGA package at commercial temperature and in still air.

Maximum Power Allowed =

$$\frac{\text{Max. junction temp. (°C) - Max. ambient temp. (°C)}}{\theta_{ja}(°C/W)} = \frac{100°C - 70°C}{20.5°C/W} = 1.46 \text{ W}$$

| EQ | 2 |

|----|---|

|----|---|

EQ 1

|                                 |              |                 | $\theta_{ja}$ |                  |                  |       |

|---------------------------------|--------------|-----------------|---------------|------------------|------------------|-------|

| Package Type                    | Pin<br>Count | θ <sub>jc</sub> | Still Air     | 200 ft./<br>min. | 500 ft./<br>min. | Units |

| Chip Scale Package (CSP)        | 36           | TBD             | TBD           | TBD              | TBD              | C/W   |

|                                 | 81           | TBD             | TBD           | TBD              | TBD              | C/W   |

| Quad Flat No Lead (QFN)         | 48           | TBD             | TBD           | TBD              | TBD              | C/W   |

|                                 | 68           | TBD             | TBD           | TBD              | TBD              | C/W   |

|                                 | 100          | TBD             | TBD           | TBD              | TBD              | C/W   |

| Very Thin Quad Flat Pack (VQFP) | 100          | 10.0            | 35.3          | 29.4             | 27.1             | C/W   |

### Table 2-5 • Package Thermal Resistivities

### Temperature and Voltage Derating Factors

# Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $T_J$ = 70°C, VCC = 1.425 V)

For IGLOO nano V2 or V5 Devices, 1.5 V DC Core Supply Voltage

| Array Voltage | Junction Temperature (°C) |       |       |       |       |       |       |  |  |  |

|---------------|---------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| VCC (V)       | –40°C                     | –20°C | 0°C   | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |

| 1.425         | 0.947                     | 0.956 | 0.965 | 0.978 | 1.000 | 1.009 | 1.013 |  |  |  |

| 1.5           | 0.875                     | 0.883 | 0.892 | 0.904 | 0.925 | 0.932 | 0.937 |  |  |  |

| 1.575         | 0.821                     | 0.829 | 0.837 | 0.848 | 0.868 | 0.875 | 0.879 |  |  |  |

IGLOO nano DC and Switching Characteristics

|                                           | Core<br>Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------------------------------|------------------|---------|---------|---------|---------|---------|---------|-------|

| VCCI= 1.2 V (per bank)<br>Typical (25°C)  | 1.2 V            | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μA    |

| VCCI = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μA    |

| VCCI = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μA    |

| VCCI = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μA    |

| VCCI = 3.3 V (per bank)<br>Typical (25°C) | 1.2 V /<br>1.5 V | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μA    |

### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Sleep Mode\*

Note: \*I<sub>DD</sub> = N<sub>BANKS</sub> \* I<sub>CCI</sub>.

### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO nano Shutdown Mode

|                   | Core Voltage  | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|-------------------|---------------|---------|---------|---------|---------|---------|---------|-------|

| Typical<br>(25°C) | 1.2 V / 1.5 V | 0       | 0       | 0       | 0       | 0       | 0       | μA    |

### Table 2-12 • Quiescent Supply Current (IDD), No IGLOO nano Flash\*Freeze Mode<sup>1</sup>

|                                                   | Core<br>Voltage | AGLN010 | AGLN015 | AGLN020 | AGLN060 | AGLN125 | AGLN250 | Units |

|---------------------------------------------------|-----------------|---------|---------|---------|---------|---------|---------|-------|

| ICCA Current <sup>2</sup>                         |                 | •       |         |         |         |         |         |       |

| Typical (25°C)                                    | 1.2 V           | 3.7     | 5       | 5       | 10      | 13      | 18      | μA    |

|                                                   | 1.5 V           | 8       | 14      | 14      | 20      | 28      | 44      | μA    |

| ICCI or IJTAG Current                             |                 | -       |         |         |         |         |         |       |

| VCCI / VJTAG = 1.2 V (per<br>bank) Typical (25°C) | 1.2 V           | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | 1.7     | μA    |

| VCCI / VJTAG = 1.5 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | 1.8     | μA    |

| VCCI / VJTAG = 1.8 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | 1.9     | μA    |

| VCCI / VJTAG = 2.5 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | 2.2     | μA    |

| VCCI / VJTAG = 3.3 V (per<br>bank) Typical (25°C) | 1.2 V / 1.5 V   | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | 2.5     | μA    |

Notes:

IDD = N<sub>BANKS</sub> \* ICCI + ICCA. JTAG counts as one bank when powered.

Includes VCC, VCCPLL, and VPUMP currents.

IGLOO nano DC and Switching Characteristics

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>oclr2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| toesud                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

### Table 2-71 • Parameter Definition and Measuring Nodes

Note: \*See Figure 2-13 on page 2-43 for more information.

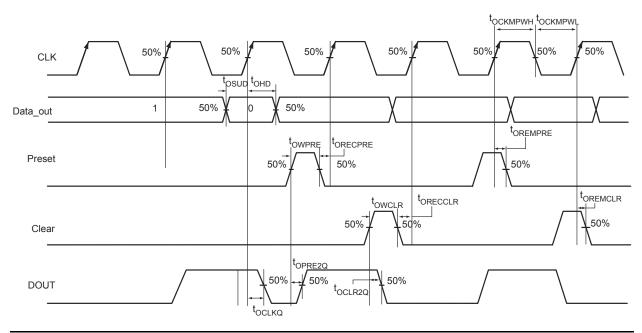

### **Output Register**

### Figure 2-15 • Output Register Timing Diagram

**Timing Characteristics**

1.5 V DC Core Voltage

# Table 2-74 • Output Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 1.00 | ns    |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                         | 0.51 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 1.34 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 1.34 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.24 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.24 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.19 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.19 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Data Register          | 0.31 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

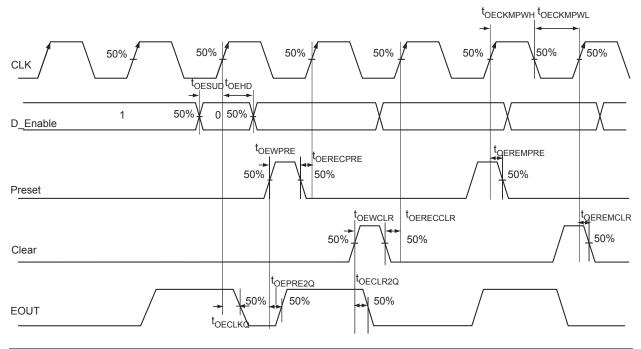

### Output Enable Register

### Figure 2-16 • Output Enable Register Timing Diagram

### **Timing Characteristics**

### 1.5 V DC Core Voltage

# Table 2-76 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.75 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.51 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 1.13 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 1.13 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width LOW for the Output Enable Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

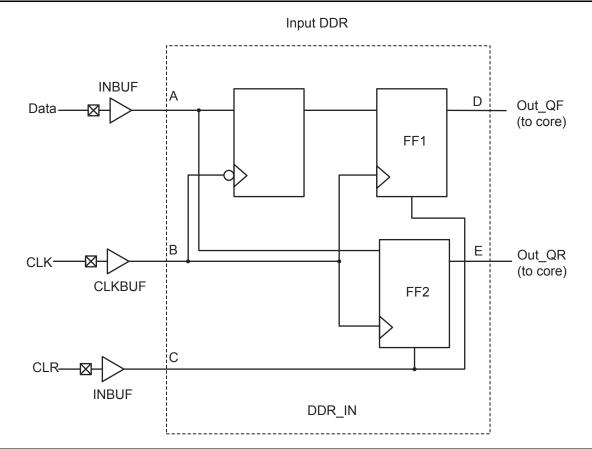

### **DDR Module Specifications**

Note: DDR is not supported for AGLN010, AGLN015, and AGLN020 devices.

### Input DDR Module

| Figure | 2-17• | Input | DDR | Timing | Model |

|--------|-------|-------|-----|--------|-------|

|        |       |       |     |        |       |

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF          | B, E                       |

| t <sub>DDRISUD</sub>    | Data Setup Time of DDR input | A, B                       |

|                         | Data Hold Time of DDR input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | С, В                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | С, В                       |

IGLOO nano DC and Switching Characteristics

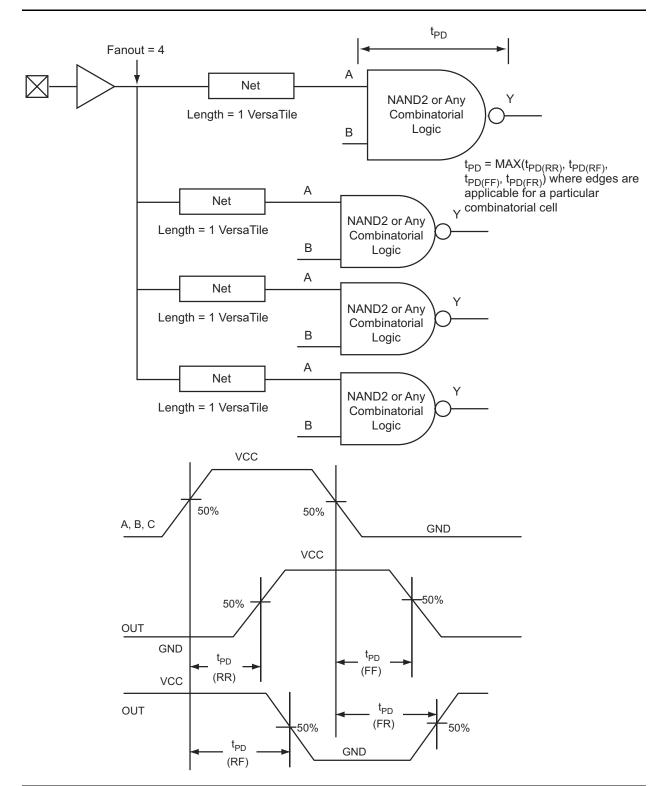

Figure 2-22 • Timing Model and Waveforms

### Timing Characteristics

1.5 V DC Core Voltage

# Table 2-84 • Combinatorial Cell Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.76 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.87 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.91 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.90 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.94 | ns    |

| XOR2               | Y = A 🕀 B                 | t <sub>PD</sub> | 1.39 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 1.44 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 1.60 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 1.17 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 1.18 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### 1.2 V DC Core Voltage

# Table 2-85 •Combinatorial Cell Propagation Delays<br/>Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Combinatorial Cell | Equation                  | Parameter       | Std. | Units |

|--------------------|---------------------------|-----------------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 1.33 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 1.48 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 1.58 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 1.53 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 1.63 | ns    |

| XOR2               | Y = A 🕀 B                 | t <sub>PD</sub> | 2.34 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 2.59 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 2.74 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 2.03 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 2.11 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

#### 1.2 V DC Core Voltage

# Table 2-94 •AGLN010 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | 5                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.71              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.78              | 2.31              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.53              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## Table 2-95 • AGLN015 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano DC and Switching Characteristics

# Table 2-96 • AGLN020 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-97 • AGLN060 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.02              | 2.42              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.09              | 2.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.56              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano DC and Switching Characteristics

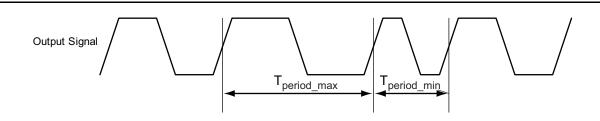

*Note:* Peak-to-peak jitter measurements are defined by  $T_{peak-to-peak} = T_{period_max} - T_{period_min}$ *Figure 2-26* • Peak-to-Peak Jitter Definition

### **Timing Characteristics**

1.5 V DC Core Voltage

### Table 2-102 • RAM4K9

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.69 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.13 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.68 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 1.37 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.13 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.59 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.30 | ns    |

| t <sub>CKQ1</sub>     | Clock HIGH to new data valid on DOUT (output retained, WMODE = 0)                                                   | 2.94 | ns    |

|                       | Clock HIGH to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.55 | ns    |

| t <sub>CKQ2</sub>     | Clock HIGH to new data valid on DOUT (pipelined)                                                                    | 1.51 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address; applicable to closing edge       | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge | 0.35 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge | 0.41 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DOUT (flow-through)                                                                    | 1.72 | ns    |

|                       | RESET Low to data out Low on DOUT (pipelined)                                                                       | 1.72 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.51 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 2.68 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.68 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 6.24 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 160  | MHz   |

Notes:

1. For more information, refer to the application note AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based FPGAs and SoC FPGAs App Note.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

### 1.2 V DC Core Voltage

### Table 2-107 • FIFO

Worst Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 3.44  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.26  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.30  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (DI) Setup Time                        | 1.30  | ns    |

| t <sub>DH</sub>      | Input Data (DI) Hold Time                         | 0.41  | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 5.67  | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 3.02  | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 6.02  | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 5.71  | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 22.17 | ns    |

| t <sub>RSTFG</sub>   | RESET LOW to Empty/Full Flag Valid                | 5.93  | ns    |

| t <sub>RSTAF</sub>   | RESET LOW to Almost Empty/Full Flag Valid         | 21.94 | ns    |

| t <sub>RSTBQ</sub>   | RESET LOW to Data Out Low on RD (flow-through)    | 3.41  | ns    |

|                      | RESET LOW to Data Out Low on RD (pipelined)       | 4.09  | 3.41  |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.02  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 5.48  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 92    | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

IGLOO nano DC and Switching Characteristics

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-15 for more details.

### **Timing Characteristics**

1.5 V DC Core Voltage

### Table 2-110 • JTAG 1532

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | Std.  | Units |

|----------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 1.00  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 2.00  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 1.00  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 2.00  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 25.00 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 15    | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.58  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### 1.2 V DC Core Voltage

### *Table 2-111* • JTAG 1532

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                 | Std.  | Units |

|----------------------|-----------------------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 1.50  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 3.00  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 1.50  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 3.00  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 11.00 | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 30.00 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 9.00  | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 1.18  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.00  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

TDI

#### Table 3-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

Note: Equivalent parallel resistance if more than one device is on the JTAG chain

### Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

### TMS Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

### TRST Boundary Scan Reset Pin

The TRST pin functions as an active-low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 3-2 and must satisfy the parallel resistance value requirement. The values in Table 3-2 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

### **Special Function Pins**

### NC

### No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

### DC

### Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

### Packaging

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

IGLOO nano Low Power Flash FPGAs

| CS81       |                  |            | CS81             |  |  |

|------------|------------------|------------|------------------|--|--|

| Pin Number | AGLN250 Function | Pin Number | AGLN250 Function |  |  |

| A1         | GAA0/IO00RSB0    | E1         | GFB0/IO59RSB3    |  |  |

| A2         | GAA1/IO01RSB0    | E2         | GFB1/IO60RSB3    |  |  |

| A3         | GAC0/IO04RSB0    | E3         | GFA1/IO58RSB3    |  |  |

| A4         | IO07RSB0         | E4         | VCCIB3           |  |  |

| A5         | IO09RSB0         | E5         | VCC              |  |  |

| A6         | IO12RSB0         | E6         | VCCIB1           |  |  |

| A7         | GBB0/IO16RSB0    | E7         | GCA0/IO28RSB1    |  |  |

| A8         | GBA1/IO19RSB0    | E8         | GCA1/IO27RSB1    |  |  |

| A9         | GBA2/IO20RSB1    | E9         | GCB2/IO29RSB1    |  |  |

| B1         | GAA2/IO67RSB3    | F1         | VCCPLF           |  |  |

| B2         | GAB0/IO02RSB0    | F2         | VCOMPLF          |  |  |

| B3         | GAC1/IO05RSB0    | F3         | GND              |  |  |

| B4         | IO06RSB0         | F4         | GND              |  |  |

| B5         | IO10RSB0         | F5         | VCCIB2           |  |  |

| B6         | GBC0/IO14RSB0    | F6         | GND              |  |  |

| B7         | GBB1/IO17RSB0    | F7         | GDA1/IO33RSB1    |  |  |

| B8         | IO21RSB1         | F8         | GDC1/IO31RSB1    |  |  |

| B9         | GBB2/IO22RSB1    | F9         | GDC0/IO32RSB1    |  |  |

| C1         | GAB2/IO65RSB3    | G1         | GEA0/IO51RSB3    |  |  |

| C2         | IO66RSB3         | G2         | GEC1/IO54RSB3    |  |  |

| C3         | GND              | G3         | GEC0/IO53RSB3    |  |  |

| C4         | IO08RSB0         | G4         | IO45RSB2         |  |  |

| C5         | IO11RSB0         | G5         | IO42RSB2         |  |  |

| C6         | GND              | G6         | IO37RSB2         |  |  |

| C7         | GBA0/IO18RSB0    | G7         | GDB2/IO35RSB2    |  |  |

| C8         | GBC2/IO23RSB1    | G8         | VJTAG            |  |  |

| C9         | IO24RSB1         | G9         | TRST             |  |  |

| D1         | GAC2/IO63RSB3    | H1         | GEA1/IO52RSB3    |  |  |

| D2         | IO64RSB3         | H2         | FF/GEB2/IO49RSB2 |  |  |

| D3         | GFA2/IO56RSB3    | H3         | IO47RSB2         |  |  |

| D4         | VCC              | H4         | IO44RSB2         |  |  |

| D5         | VCCIB0           | H5         | IO41RSB2         |  |  |

| D6         | GND              | H6         | IO39RSB2         |  |  |

| D7         | IO30RSB1         | H7         | GDA2/IO34RSB2    |  |  |

| D8         | GCC1/IO25RSB1    | H8         | TDI              |  |  |

| D9         | GCC0/IO26RSB1    | H9         | TDO              |  |  |

| CS81       |                  |  |

|------------|------------------|--|

| Pin Number | AGLN250 Function |  |

| J1         | GEA2/IO50RSB2    |  |

| J2         | GEC2/IO48RSB2    |  |

| J3         | IO46RSB2         |  |

| J4         | IO43RSB2         |  |

| J5         | IO40RSB2         |  |

| J6         | IO38RSB2         |  |

| J7         | ТСК              |  |

| J8         | TMS              |  |

| J9         | VPUMP            |  |

Note: \* Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN250-CS81.

Package Pin Assignments

|            | VQ100            | VQ100      |                  |

|------------|------------------|------------|------------------|

| Pin Number | AGLN250 Function | Pin Number | AGLN250 Function |

| 1          | GND              | 37         | VCC              |

| 2          | GAA2/IO67RSB3    | 38         | GND              |

| 3          | IO66RSB3         | 39         | VCCIB2           |

| 4          | GAB2/IO65RSB3    | 40         | IO39RSB2         |

| 5          | IO64RSB3         | 41         | IO38RSB2         |

| 6          | GAC2/IO63RSB3    | 42         | IO37RSB2         |

| 7          | IO62RSB3         | 43         | GDC2/IO36RSB2    |

| 8          | IO61RSB3         | 44         | GDB2/IO35RSB2    |

| 9          | GND              | 45         | GDA2/IO34RSB2    |

| 10         | GFB1/IO60RSB3    | 46         | GNDQ             |

| 11         | GFB0/IO59RSB3    | 47         | TCK              |

| 12         | VCOMPLF          | 48         | TDI              |

| 13         | GFA0/IO57RSB3    | 49         | TMS              |

| 14         | VCCPLF           | 50         | VMV2             |

| 15         | GFA1/IO58RSB3    | 51         | GND              |

| 16         | GFA2/IO56RSB3    | 52         | VPUMP            |

| 17         | VCC              | 53         | NC               |

| 18         | VCCIB3           | 54         | TDO              |

| 19         | GFC2/IO55RSB3    | 55         | TRST             |

| 20         | GEC1/IO54RSB3    | 56         | VJTAG            |

| 21         | GEC0/IO53RSB3    | 57         | GDA1/IO33RSB1    |

| 22         | GEA1/IO52RSB3    | 58         | GDC0/IO32RSB1    |

| 23         | GEA0/IO51RSB3    | 59         | GDC1/IO31RSB1    |

| 24         | VMV3             | 60         | IO30RSB1         |

| 25         | GNDQ             | 61         | GCB2/IO29RSB1    |

| 26         | GEA2/IO50RSB2    | 62         | GCA1/IO27RSB1    |

| 27         | FF/GEB2/IO49RSB2 | 63         | GCA0/IO28RSB1    |

| 28         | GEC2/IO48RSB2    | 64         | GCC0/IO26RSB1    |

| 29         | IO47RSB2         | 65         | GCC1/IO25RSB1    |

| 30         | IO46RSB2         | 66         | VCCIB1           |

| 31         | IO45RSB2         | 67         | GND              |

| 32         | IO44RSB2         | 68         | VCC              |

| 33         | IO43RSB2         | 69         | IO24RSB1         |

| 34         | IO42RSB2         | 70         | GBC2/IO23RSB1    |

| 35         | IO41RSB2         | 71         | GBB2/IO22RSB1    |

| 36         | IO40RSB2         | 72         | IO21RSB1         |

| VQ100      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AGLN250 Function |  |  |

| 73         | GBA2/IO20RSB1    |  |  |

| 74         | VMV1             |  |  |

| 75         | GNDQ             |  |  |

| 76         | GBA1/IO19RSB0    |  |  |

| 77         | GBA0/IO18RSB0    |  |  |

| 78         | GBB1/IO17RSB0    |  |  |

| 79         | GBB0/IO16RSB0    |  |  |

| 80         | GBC1/IO15RSB0    |  |  |

| 81         | GBC0/IO14RSB0    |  |  |

| 82         | IO13RSB0         |  |  |

| 83         | IO12RSB0         |  |  |

| 84         | IO11RSB0         |  |  |

| 85         | IO10RSB0         |  |  |

| 86         | IO09RSB0         |  |  |

| 87         | VCCIB0           |  |  |

| 88         | GND              |  |  |

| 89         | VCC              |  |  |

| 90         | IO08RSB0         |  |  |

| 91         | IO07RSB0         |  |  |

| 92         | IO06RSB0         |  |  |

| 93         | GAC1/IO05RSB0    |  |  |

| 94         | GAC0/IO04RSB0    |  |  |

| 95         | GAB1/IO03RSB0    |  |  |

| 96         | GAB0/IO02RSB0    |  |  |

| 97         | GAA1/IO01RSB0    |  |  |

| 98         | GAA0/IO00RSB0    |  |  |

| 99         | GNDQ             |  |  |

| 100        | VMV0             |  |  |

IGLOO nano Low Power Flash FPGAs

| Revision / Version                                     | Changes                                                                                                                                                                                                                                                                                                                                 | Page                  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Revision 1 (cont'd)                                    | The "QN48" pin diagram was revised.                                                                                                                                                                                                                                                                                                     | 4-16                  |

| Packaging Advance<br>v0.2                              | Note 2 for the "QN48", "QN68", and "100-Pin QFN" pin diagrams was changed to "The die attach paddle of the package is tied to ground (GND)."                                                                                                                                                                                            |                       |

|                                                        | The "VQ100" pin diagram was revised to move the pin IDs to the upper left corner instead of the upper right corner.                                                                                                                                                                                                                     | 4-23                  |

| Revision 0 (Oct 2008)<br>Product Brief Advance<br>v0.2 | The following tables and sections were updated to add the UC81 and CS81<br>packages for AGL030:<br>"IGLOO nano Devices"<br>"I/Os Per Package"<br>"IGLOO nano Products Available in the Z Feature Grade"<br>"Temperature Grade Offerings"                                                                                                | N/A                   |

|                                                        | The "I/Os Per Package" table was updated to add the following information to table note 4: "For nano devices, the VQ100 package is offered in both leaded and RoHS-compliant versions. All other packages are RoHS-compliant only."                                                                                                     | II                    |

|                                                        | The "IGLOO nano Products Available in the Z Feature Grade" section was updated to remove QN100 for AGLN250.                                                                                                                                                                                                                             | VI                    |

|                                                        | The device architecture figures, Figure 1-3 • IGLOO Device Architecture Overview with Two I/O Banks (AGLN060, AGLN125) through Figure 1-4 • IGLOO Device Architecture Overview with Four I/O Banks (AGLN250), were revised. Figure 1-1 • IGLOO Device Architecture Overview with Two I/O Banks and No RAM (AGLN010 and AGLN030) is new. | 1-4<br>through<br>1-5 |

|                                                        | The "PLL and CCC" section was revised to include information about CCC-GLs in AGLN020 and smaller devices.                                                                                                                                                                                                                              | 1-7                   |

|                                                        | The "I/Os with Advanced I/O Standards" section was revised to add information about IGLOO nano devices supporting double-data-rate applications.                                                                                                                                                                                        | 1-8                   |