Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 6144                                                                       |

| Total RAM Bits                 | 36864                                                                      |

| Number of I/O                  | 60                                                                         |

| Number of Gates                | 250000                                                                     |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 81-WFBGA, CSBGA                                                            |

| Supplier Device Package        | 81-CSP (5x5)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/agln250v2-zcsg81 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

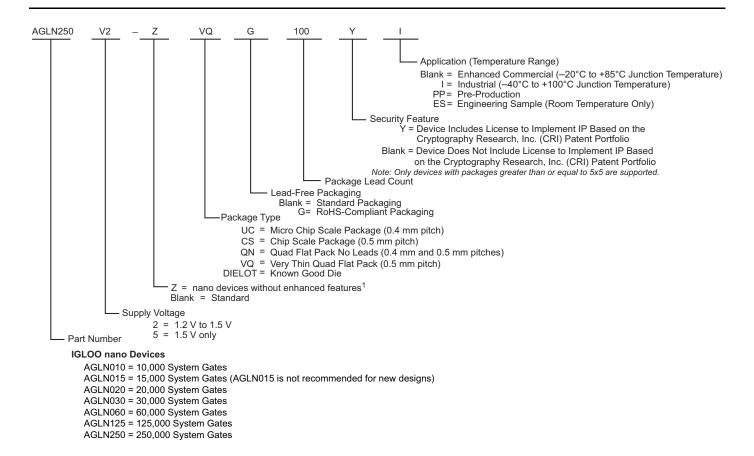

# **IGLOO** nano Ordering Information

#### Notes:

- Z-feature grade devices AGLN060Z, AGLN125Z, and AGLN250Z do not support the enhanced nano features of Schmitt Trigger input, bus hold (hold previous I/O state in Flash\*Freeze mode), cold-sparing, hot-swap I/O capability and 1.2 V programming. The AGLN030 Z feature grade does not support Schmitt trigger input, bus hold and 1.2 V programming. For the VQ100, CS81, UC81, QN68, and QN48 packages, the Z feature grade and the N part number are not marked on the device. Z feature grade devices are not recommended for new designs.

- AGLN030 is available in the Z feature grade only.

- 3. Marking Information: IGLOO nano V2 devices do not have a V2 marking, but IGLOO nano V5 devices are marked with a V5 designator.

# **Devices Not Recommended For New Designs**

AGLN015, AGLN030Z, AGLN060Z, AGLN125Z, and AGLN250Z are not recommended for new designs. For more information on obsoleted devices/packages, refer to the *PDN1503 - IGLOO nano Z and ProASIC3 nano Z Families*.

IV Revision 19

# **Table of Contents**

| IGLOO nano Device Overview                                              |      |

|-------------------------------------------------------------------------|------|

| General Description                                                     |      |

| IGLOO nano DC and Switching Characteristics                             |      |

| General Specifications                                                  |      |

| Calculating Power Dissipation                                           |      |

| User I/O Characteristics                                                | 2-15 |

| VersaTile Characteristics                                               | 2-57 |

| Global Resource Characteristics                                         | 2-63 |

| Clock Conditioning Circuits                                             |      |

| Embedded SRAM and FIFO Characteristics                                  | 2-73 |

| Embedded FlashROM Characteristics                                       | 2-87 |

| JTAG 1532 Characteristics                                               | 2-88 |

| Pin Descriptions                                                        |      |

| Supply Pins                                                             |      |

| User Pins                                                               |      |

| JTAG Pins                                                               |      |

| Special Function Pins                                                   |      |

| Packaging                                                               |      |

| Related Documents                                                       |      |

| Package Pin Assignments                                                 |      |

| UC36                                                                    | 4-1  |

| UC81                                                                    | 4-3  |

| CS81                                                                    | 4-6  |

| QN48                                                                    | 4-15 |

| QN68                                                                    | 4-18 |

| VQ100                                                                   | 4-22 |

| Datasheet Information                                                   |      |

| List of Changes                                                         |      |

| Datasheet Categories                                                    | 5-8  |

| Safety Critical, Life Support, and High-Reliability Applications Policy | 5-8  |

## Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, flash-based IGLOO nano devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic.

Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The IGLOO nano device architecture mitigates the need for ASIC migration at higher user volumes. This makes IGLOO nano devices cost-effective ASIC replacement solutions, especially for applications in the consumer, networking/communications, computing, and avionics markets.

With a variety of devices under \$1, IGLOO nano FPGAs enable cost-effective implementation of programmable logic and quick time to market.

# Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO nano flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO nano FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

## Advanced Flash Technology

The IGLOO nano device offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO nano FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

#### Advanced Architecture

The proprietary IGLOO nano architecture provides granularity comparable to standard-cell ASICs. The IGLOO nano device consists of five distinct and programmable architectural features (Figure 1-3 on page 1-5 to Figure 1-4 on page 1-5):

- Flash\*Freeze technology

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO nano core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC<sup>®</sup> family of third-generation-architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

<sup>†</sup> The AGLN030 and smaller devices do not support PLL or SRAM.

# **Power Consumption of Various Internal Resources**

Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|           |                                                                |                 | Device Spe | ecific Dyna  | mic Power   | (µW/MHz) |         |  |  |  |  |

|-----------|----------------------------------------------------------------|-----------------|------------|--------------|-------------|----------|---------|--|--|--|--|

| Parameter | Definition                                                     | AGLN250         | AGLN125    | AGLN060      | AGLN020     | AGLN015  | AGLN010 |  |  |  |  |

| PAC1      | Clock contribution of a Global Rib                             | 4.421           | 4.493      | 2.700        | 0           | 0        | 0       |  |  |  |  |

| PAC2      | Clock contribution of a Global Spine                           | 2.704           | 1.976      | 1.982        | 4.002       | 4.002    | 2.633   |  |  |  |  |

| PAC3      | Clock contribution of a VersaTile row                          | 1.496           | 1.504      | 1.511        | 1.346       | 1.346    | 1.340   |  |  |  |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.152           | 0.153      | 0.153        | 0.148       | 0.148    | 0.143   |  |  |  |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  |                 |            | 0.0          | 57          |          |         |  |  |  |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module |                 | 0.207      |              |             |          |         |  |  |  |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     |                 | 0.17       |              |             |          |         |  |  |  |  |

| PAC8      | Average contribution of a routing net                          |                 | 0.7        |              |             |          |         |  |  |  |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          |                 | Se         | e Table 2-13 | 3 on page 2 | ?-9.     |         |  |  |  |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         | See Table 2-14. |            |              |             |          |         |  |  |  |  |

| PAC11     | Average contribution of a RAM block during a read operation    | k 25.00         |            |              |             | N/A      |         |  |  |  |  |

| PAC12     | Average contribution of a RAM block during a write operation   |                 | 30.00      |              |             | N/A      |         |  |  |  |  |

| PAC13     | Dynamic contribution for PLL                                   |                 | 2.70       |              |             | N/A      |         |  |  |  |  |

Table 2-16 • Different Components Contributing to the Static Power Consumption in IGLOO nano Devices For IGLOO nano V2 or V5 Devices, 1.5 V Core Supply Voltage

|                   |                                                    | Device -Specific Static Power (mW)                   |                            |             |             |     |  |  |

|-------------------|----------------------------------------------------|------------------------------------------------------|----------------------------|-------------|-------------|-----|--|--|

| Parameter         | Definition                                         | Definition AGLN250 AGLN125 AGLN060 AGLN020 AGLN015 A |                            |             | AGLN010     |     |  |  |

| PDC1              | Array static power in Active mode                  |                                                      | See Table 2-12 on page 2-8 |             |             |     |  |  |

|                   | Array static power in Static (Idle) mode           | See Table 2-12 on page 2-8                           |                            |             |             |     |  |  |

|                   | Array static power in Flash*Freeze mode            |                                                      | S                          | ee Table 2- | 9 on page 2 | 2-7 |  |  |

| PDC4 <sup>1</sup> | Static PLL contribution                            | 1.84 N/A                                             |                            |             |             |     |  |  |

| PDC5              | Bank quiescent power (VCCI-dependent) <sup>2</sup> | See Table 2-12 on page 2-8                           |                            |             |             |     |  |  |

#### Notes:

- 1. Minimum contribution of the PLL when running at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC.

2-10 Revision 19

#### Combinatorial Cells Contribution—P<sub>C-CELL</sub>

$P_{C-CELL} = N_{C-CELL} * \alpha_1 / 2 * PAC7 * F_{CLK}$

N<sub>C-CFLL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_{\text{1}}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

# Routing Net Contribution—P<sub>NET</sub>

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * \alpha_1 / 2 * PAC8 * F_{CLK}$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

N<sub>C-CFLL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

## I/O Input Buffer Contribution—PINPUTS

$P_{INPUTS} = N_{INPUTS} * \alpha_2 / 2 * PAC9 * F_{CLK}$

N<sub>INPLITS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

## I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * PAC10 * F_{CLK}$

$N_{\mbox{OUTPUTS}}$  is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-14.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-20 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

#### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{PAC11} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ\text{-}CLOCK}} * \beta_2 + \mathsf{PAC12} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE\text{-}CLOCK}} * \beta_3$

N<sub>BLOCKS</sub> is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-20 on page 2-14.

#### PLL Contribution—P<sub>PLL</sub>

P<sub>PLL</sub> = PDC4 + PAC13 \*F<sub>CLKOUT</sub>

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (PAC13\* FCLKOUT product) to the total PLL contribution.

# **Detailed I/O DC Characteristics**

Table 2-27 • Input Capacitance

| Symbol             | Definition                         | Conditions           | Min. | Max. | Units |

|--------------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub>    | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| C <sub>INCLK</sub> | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

# Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup>

| Standard                             | Drive Strength | $R_{PULL-DOWN} \ (\Omega)^2$ | $R_{PULL\text{-}UP} \ (\Omega)^3$ |

|--------------------------------------|----------------|------------------------------|-----------------------------------|

| 3.3 V LVTTL / 3.3V LVCMOS            | 2 mA           | 100                          | 300                               |

|                                      | 4 mA           | 100                          | 300                               |

|                                      | 6 mA           | 50                           | 150                               |

|                                      | 8 mA           | 50                           | 150                               |

| 3.3 V LVCMOS Wide Range              | 100 μΑ         | Same as equivalent s         | software default drive            |

| 2.5 V LVCMOS                         | 2 mA           | 100                          | 200                               |

|                                      | 4 mA           | 100                          | 200                               |

|                                      | 6 mA           | 50                           | 100                               |

|                                      | 8 mA           | 50                           | 100                               |

| 1.8 V LVCMOS                         | 2 mA           | 200                          | 225                               |

|                                      | 4 mA           | 100                          | 112                               |

| 1.5 V LVCMOS                         | 2 mA           | 200                          | 224                               |

| 1.2 V LVCMOS <sup>4</sup>            | 1 mA           | 315                          | 315                               |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 100 μΑ         | 315                          | 315                               |

#### Notes:

<sup>1.</sup> These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models posted at http://www.microsemi.com/soc/download/ibis/default.aspx.

<sup>2.</sup>  $R_{(PULL\text{-}DOWN\text{-}MAX)} = (VOLspec) / IOLspec$

<sup>3.</sup>  $R_{(PULL-UP-MAX)} = (VCCImax - VOHspec) / I_{OHspec}$

<sup>4.</sup> Applicable to IGLOO nano V2 devices operating at VCCI ≥ VCC.

IGLOO nano DC and Switching Characteristics

#### **Timing Characteristics**

### Applies to 1.5 V DC Core Voltage

Table 2-53 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | $t_{LZ}$ | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|----------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 5.44            | 0.19             | 1.03            | 1.44             | 0.66              | 5.25            | 5.44            | 1.69     | 1.35            | ns    |

| 4 mA           | STD         | 0.97              | 4.44            | 0.19             | 1.03            | 1.44             | 0.66              | 4.37            | 4.44            | 1.99     | 2.11            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-54 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| <b>Drive Strength</b> | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-----------------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA                  | STD         | 0.97              | 2.64            | 0.19             | 1.03            | 1.44             | 0.66              | 2.59            | 2.64            | 1.69            | 1.40            | ns    |

| 4 mA                  | STD         | 0.97              | 2.08            | 0.19             | 1.03            | 1.44             | 0.66              | 2.12            | 1.95            | 1.99            | 2.19            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Applies to 1.2 V DC Core Voltage

Table 2-55 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 5.92            | 0.26             | 1.13            | 1.59             | 1.10              | 5.72            | 5.92            | 2.11            | 1.95            | ns    |

| 4 mA           | STD         | 1.55              | 4.91            | 0.26             | 1.13            | 1.59             | 1.10              | 4.82            | 4.91            | 2.42            | 2.73            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-56 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 1.55              | 3.05            | 0.26             | 1.13            | 1.59             | 1.10              | 3.01            | 3.05            | 2.10            | 2.00            | ns    |

| 4 mA           | STD         | 1.55              | 2.49            | 0.26             | 1.13            | 1.59             | 1.10              | 2.53            | 2.34            | 2.42            | 2.81            | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-36 Revision 19

## 1.2 V LVCMOS (JESD8-12A)

Low-Voltage CMOS for 1.2 V complies with the LVCMOS standard JESD8-12A for general purpose 1.2 V applications. It uses a 1.2 V input buffer and a push-pull output buffer.

Table 2-63 • Minimum and Maximum DC Input and Output Levels

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 1 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 1   | 1  | 10                      | 13                      | 10                      | 10                      |

#### Notes:

- 1. I<sub>IL</sub> is the input leakage current per I/O pin over recommended operating conditions where –0.3 < VIN < VIL.

- 2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions where VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

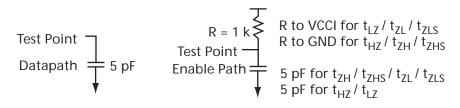

Figure 2-11 • AC Loading

Table 2-64 • 1.2 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input LOW (V) | Input HIGH (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.2            | 0.6                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

#### **Timing Characteristics**

#### Applies to 1.2 V DC Core Voltage

Table 2-65 • 1.2 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 1 mA           | STD         | 1.55              | 8.30            | 0.26             | 1.56            | 2.27             | 1.10              | 7.97            | 7.54            | 2.56            | 2.55            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-66 • 1.2 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 1 mA           | STD         | 1.55              | 3.50            | 0.26             | 1.56            | 2.27             | 1.10              | 3.37            | 3.10            | 2.55            | 2.66            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO nano DC and Switching Characteristics

Table 2-70 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| toclka                | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosup                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              |                                |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

Note: \*See Figure 2-12 on page 2-41 for more information.

2-42 Revision 19

IGLOO nano DC and Switching Characteristics

### 1.2 V DC Core Voltage

Table 2-73 • Input Data Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                                                         | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.68 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.97 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 1.19 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 1.19 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.24 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.24 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.19 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.19 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Input Data Register          | 0.31 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width LOW for the Input Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-46 Revision 19

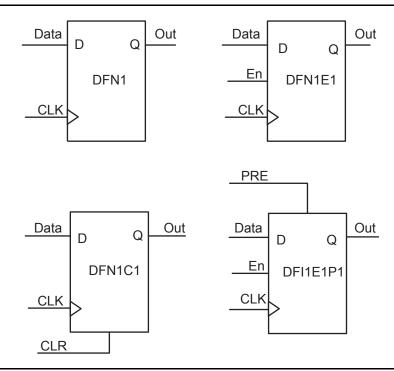

# VersaTile Specifications as a Sequential Module

The IGLOO nano library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide for Software v10.1.

Figure 2-23 • Sample of Sequential Cells

2-60 Revision 19

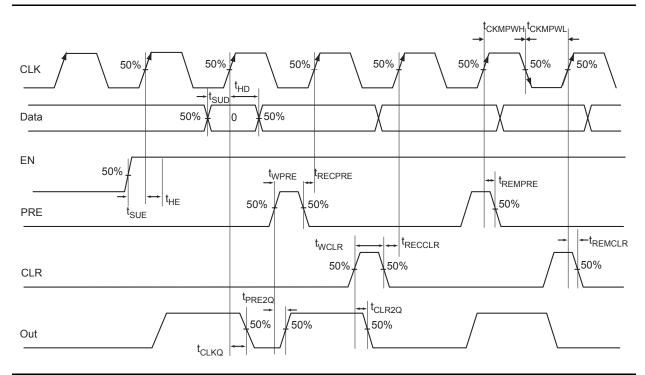

Figure 2-24 • Timing Model and Waveforms

# Timing Characteristics 1.5 V DC Core Voltage

Table 2-86 • Register Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.89 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.81 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.73 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.60 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.62 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width HIGH for the Core Register          | 0.56 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width LOW for the Core Register           | 0.56 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

Table 2-94 • AGLN010 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           |   | S                 | td.               |       |

|----------------------|-------------------------------------------|---|-------------------|-------------------|-------|

| Parameter            | Description                               | • | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |   | 1.71              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |   | 1.78              | 2.31              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |   | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |   | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |   |                   | 0.53              | ns    |

#### Notes:

- Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-95 • AGLN015 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.81              | 2.26              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.90              | 2.51              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.61              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

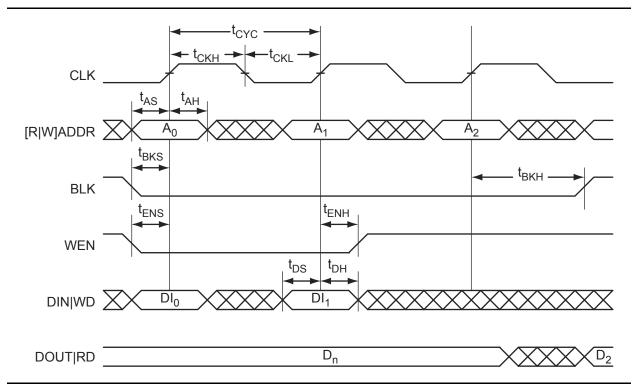

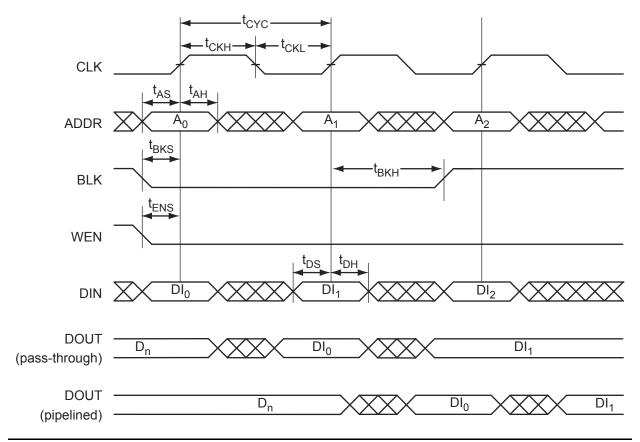

Figure 2-30 • RAM Write, Output Retained (WMODE = 0). Applicable to Both RAM4K9 and RAM512x18.

Figure 2-31 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

# 1.2 V DC Core Voltage

Table 2-104 • RAM4K9

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                                                                         | Std.  | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 1.28  | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.25  | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 1.25  | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.25  | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 2.54  | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.25  | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 1.10  | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.55  | ns    |

| t <sub>CKQ1</sub>     | Clock HIGH to new data valid on DOUT (output retained, WMODE = 0)                                                   | 5.51  | ns    |

|                       | Clock HIGH to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 4.77  | ns    |

| t <sub>CKQ2</sub>     | Clock HIGH to new data valid on DOUT (pipelined)                                                                    | 2.82  | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address; applicable to closing edge       | 0.30  | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address; applicable to opening edge | 0.89  | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address; applicable to opening edge | 1.01  | ns    |

| t <sub>RSTBQ</sub>    | RESET LOW to data out LOW on DOUT (flow-through)                                                                    | 3.21  | ns    |

|                       | RESET LOW to data out LOW on DO (pipelined)                                                                         | 3.21  | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.93  | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 4.94  | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 1.18  | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 10.90 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 92    | MHz   |

#### Notes:

<sup>1.</sup> For more information, refer to the application note AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based FPGAs and SoC FPGAs App Note.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

# Package Pin Assignments

|            | CS81     |

|------------|----------|

|            | AGLN030Z |

| Pin Number | Function |

| A1         | IO00RSB0 |

| A2         | IO02RSB0 |

| A3         | IO06RSB0 |

| A4         | IO11RSB0 |

| A5         | IO16RSB0 |

| A6         | IO19RSB0 |

| A7         | IO22RSB0 |

| A8         | IO24RSB0 |

| A9         | IO26RSB0 |

| B1         | IO81RSB1 |

| B2         | IO04RSB0 |

| В3         | IO10RSB0 |

| B4         | IO13RSB0 |

| B5         | IO15RSB0 |

| В6         | IO20RSB0 |

| В7         | IO21RSB0 |

| В8         | IO28RSB0 |

| В9         | IO25RSB0 |

| C1         | IO79RSB1 |

| C2         | IO80RSB1 |

| C3         | IO08RSB0 |

| C4         | IO12RSB0 |

| C5         | IO17RSB0 |

| C6         | IO14RSB0 |

| C7         | IO18RSB0 |

| C8         | IO29RSB0 |

| C9         | IO27RSB0 |

| D1         | IO74RSB1 |

| D2         | IO76RSB1 |

| D3         | IO77RSB1 |

| D4         | VCC      |

| D5         | VCCIB0   |

| D6         | GND      |

| D7         | IO23RSB0 |

| D8         | IO31RSB0 |

|            |          |

|            | CS81          |

|------------|---------------|

|            | AGLN030Z      |

| Pin Number | Function      |

| D9         | IO30RSB0      |

| E1         | GEB0/IO71RSB1 |

| E2         | GEA0/IO72RSB1 |

| E3         | GEC0/IO73RSB1 |

| E4         | VCCIB1        |

| E5         | VCC           |

| E6         | VCCIB0        |

| E7         | GDC0/IO32RSB0 |

| E8         | GDA0/IO33RSB0 |

| E9         | GDB0/IO34RSB0 |

| F1         | IO68RSB1      |

| F2         | IO67RSB1      |

| F3         | IO64RSB1      |

| F4         | GND           |

| F5         | VCCIB1        |

| F6         | IO47RSB1      |

| F7         | IO36RSB0      |

| F8         | IO38RSB0      |

| F9         | IO40RSB0      |

| G1         | IO65RSB1      |

| G2         | IO66RSB1      |

| G3         | IO57RSB1      |

| G4         | IO53RSB1      |

| G5         | IO49RSB1      |

| G6         | IO44RSB1      |

| G7         | IO46RSB1      |

| G8         | VJTAG         |

| G9         | TRST          |

| H1         | IO62RSB1      |

| H2         | FF/IO60RSB1   |

| H3         | IO58RSB1      |

| H4         | IO54RSB1      |

| H5         | IO48RSB1      |

| H6         | IO43RSB1      |

| H7         | IO42RSB1      |

|            | CS81                 |  |  |  |

|------------|----------------------|--|--|--|

| Pin Number | AGLN030Z<br>Function |  |  |  |

| H8         | TDI                  |  |  |  |

| H9         | TDO                  |  |  |  |

| J1         | IO63RSB1             |  |  |  |

| J2         | IO61RSB1             |  |  |  |

| J3         | IO59RSB1             |  |  |  |

| J4         | IO56RSB1             |  |  |  |

| J5         | IO52RSB1             |  |  |  |

| J6         | IO45RSB1             |  |  |  |

| J7         | TCK                  |  |  |  |

| J8         | TMS                  |  |  |  |

| J9         | VPUMP                |  |  |  |

4-8 Revision 19

|            | CS81             |

|------------|------------------|

| Pin Number | AGLN060 Function |

| A1         | GAA0/IO02RSB0    |

| A2         | GAA1/IO03RSB0    |

| A3         | GAC0/IO06RSB0    |

| A4         | IO09RSB0         |

| A5         | IO13RSB0         |

| A6         | IO18RSB0         |

| A7         | GBB0/IO21RSB0    |

| A8         | GBA1/IO24RSB0    |

| A9         | GBA2/IO25RSB0    |

| B1         | GAA2/IO95RSB1    |

| B2         | GAB0/IO04RSB0    |

| В3         | GAC1/IO07RSB0    |

| B4         | IO08RSB0         |

| B5         | IO15RSB0         |

| B6         | GBC0/IO19RSB0    |

| B7         | GBB1/IO22RSB0    |

| B8         | IO26RSB0         |

| В9         | GBB2/IO27RSB0    |

| C1         | GAB2/IO93RSB1    |

| C2         | IO94RSB1         |

| C3         | GND              |

| C4         | IO10RSB0         |

| C5         | IO17RSB0         |

| C6         | GND              |

| C7         | GBA0/IO23RSB0    |

| C8         | GBC2/IO29RSB0    |

| C9         | IO31RSB0         |

| D1         | GAC2/IO91RSB1    |

| D2         | IO92RSB1         |

| D3         | GFA2/IO80RSB1    |

| D4         | VCC              |

| D5         | VCCIB0           |

| D6         | GND              |

| D7         | GCC2/IO43RSB0    |

|            | -                |

| CS81            |                  |

|-----------------|------------------|

| Pin Number      | AGLN060 Function |

| D8              | GCC1/IO35RSB0    |

| D9              | GCC0/IO36RSB0    |

| E1              | GFB0/IO83RSB1    |

| E2              | GFB1/IO84RSB1    |

| E3              | GFA1/IO81RSB1    |

| E4              | VCCIB1           |

| E5              | VCC              |

| E6              | VCCIB0           |

| E7              | GCA1/IO39RSB0    |

| E8              | GCA0/IO40RSB0    |

| E9              | GCB2/IO42RSB0    |

| F1 <sup>1</sup> | VCCPLF           |

| F2 <sup>1</sup> | VCOMPLF          |

| F3              | GND              |

| F4              | GND              |

| F5              | VCCIB1           |

| F6              | GND              |

| F7              | GDA1/IO49RSB0    |

| F8              | GDC1/IO45RSB0    |

| F9              | GDC0/IO46RSB0    |

| G1              | GEA0/IO69RSB1    |

| G2              | GEC1/IO74RSB1    |

| G3              | GEB1/IO72RSB1    |

| G4              | IO63RSB1         |

| G5              | IO60RSB1         |

| G6              | IO54RSB1         |

| G7              | GDB2/IO52RSB1    |

| G8              | VJTAG            |

| G9              | TRST             |

| H1              | GEA1/IO70RSB1    |

| H2              | FF/GEB2/IO67RSB1 |

| НЗ              | IO65RSB1         |

| H4              | IO62RSB1         |

| H5              | IO59RSB1         |

| CS81            |                  |

|-----------------|------------------|

| Pin Number      | AGLN060 Function |

| H6              | IO56RSB1         |

| H7 <sup>2</sup> | GDA2/IO51RSB1    |

| H8              | TDI              |

| H9              | TDO              |

| J1              | GEA2/IO68RSB1    |

| J2              | GEC2/IO66RSB1    |

| J3              | IO64RSB1         |

| J4              | IO61RSB1         |

| J5              | IO58RSB1         |

| J6              | IO55RSB1         |

| J7              | TCK              |

| J8              | TMS              |

| J9              | VPUMP            |

#### Notes:

- 1. Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN060-CS81.

- 2. The bus hold attribute (hold previous I/O state in Flash\*Freeze mode) is not supported for pin H7 in AGLN060-CS81.

Package Pin Assignments

| Pin Number<br>A1 | AGLN125Z Function |

|------------------|-------------------|

| A1               | 0440/100000000    |

|                  | GAA0/IO00RSB0     |

| A2               | GAA1/IO01RSB0     |

| A3               | GAC0/IO04RSB0     |

| A4               | IO13RSB0          |

| A5               | IO22RSB0          |

| A6               | IO32RSB0          |

| A7               | GBB0/IO37RSB0     |

| A8               | GBA1/IO40RSB0     |

| A9               | GBA2/IO41RSB0     |

| B1               | GAA2/IO132RSB1    |

| B2               | GAB0/IO02RSB0     |

| В3               | GAC1/IO05RSB0     |

| B4               | IO11RSB0          |

| B5               | IO25RSB0          |

| В6               | GBC0/IO35RSB0     |

| В7               | GBB1/IO38RSB0     |

| B8               | IO42RSB0          |

| В9               | GBB2/IO43RSB0     |

| C1               | GAB2/IO130RSB1    |

| C2               | IO131RSB1         |

| C3               | GND               |

| C4               | IO15RSB0          |

| C5               | IO28RSB0          |

| C6               | GND               |

| C7               | GBA0/IO39RSB0     |

| C8               | GBC2/IO45RSB0     |

| C9               | IO47RSB0          |

| D1               | GAC2/IO128RSB1    |

| D2               | IO129RSB1         |

| D3               | GFA2/IO117RSB1    |

| D4               | VCC               |

| D5               | VCCIB0            |

| D6               | GND               |

| D7               | GCC2/IO59RSB0     |

| D8               | GCC1/IO51RSB0     |

| D9               | GCC0/IO52RSB0     |

| CS81       |                   |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| E1         | GFB0/IO120RSB1    |

| E2         | GFB1/IO121RSB1    |

| E3         | GFA1/IO118RSB1    |

| E4         | VCCIB1            |

| E5         | VCC               |

| E6         | VCCIB0            |

| E7         | GCA0/IO56RSB0     |

| E8         | GCA1/IO55RSB0     |

| E9         | GCB2/IO58RSB0     |

| F1*        | VCCPLF            |

| F2*        | VCOMPLF           |

| F3         | GND               |

| F4         | GND               |

| F5         | VCCIB1            |

| F6         | GND               |

| F7         | GDA1/IO65RSB0     |

| F8         | GDC1/IO61RSB0     |

| F9         | GDC0/IO62RSB0     |

| G1         | GEA0/IO104RSB1    |

| G2         | GEC0/IO108RSB1    |

| G3         | GEB1/IO107RSB1    |

| G4         | IO96RSB1          |

| G5         | IO92RSB1          |

| G6         | IO72RSB1          |

| G7         | GDB2/IO68RSB1     |

| G8         | VJTAG             |

| G9         | TRST              |

| H1         | GEA1/IO105RSB1    |

| H2         | FF/GEB2/IO102RSB1 |

| НЗ         | IO99RSB1          |

| H4         | IO94RSB1          |

| H5         | IO91RSB1          |

| H6         | IO81RSB1          |

| H7         | GDA2/IO67RSB1     |

| H8         | TDI               |

| H9         | TDO               |

| CS81       |                   |

|------------|-------------------|

| Pin Number | AGLN125Z Function |

| J1         | GEA2/IO103RSB1    |

| J2         | GEC2/IO101RSB1    |

| J3         | IO97RSB1          |

| J4         | IO93RSB1          |

| J5         | IO90RSB1          |

| J6         | IO78RSB1          |

| J7         | TCK               |

| J8         | TMS               |

| J9         | VPUMP             |

Note: \* Pin numbers F1 and F2 must be connected to ground because a PLL is not supported for AGLN125Z-CS81.

4-12 Revision 19

| VQ100      |                   |

|------------|-------------------|

| Pin Number | AGLN250Z Function |

| 1          | GND               |

| 2          | GAA2/IO67RSB3     |

| 3          | IO66RSB3          |

| 4          | GAB2/IO65RSB3     |

| 5          | IO64RSB3          |

| 6          | GAC2/IO63RSB3     |

| 7          | IO62RSB3          |

| 8          | IO61RSB3          |

| 9          | GND               |

| 10         | GFB1/IO60RSB3     |

| 11         | GFB0/IO59RSB3     |

| 12         | VCOMPLF           |

| 13         | GFA0/IO57RSB3     |

| 14         | VCCPLF            |

| 15         | GFA1/IO58RSB3     |

| 16         | GFA2/IO56RSB3     |

| 17         | VCC               |

| 18         | VCCIB3            |

| 19         | GFC2/IO55RSB3     |

| 20         | GEC1/IO54RSB3     |

| 21         | GEC0/IO53RSB3     |

| 22         | GEA1/IO52RSB3     |

| 23         | GEA0/IO51RSB3     |

| 24         | VMV3              |

| 25         | GNDQ              |

| 26         | GEA2/IO50RSB2     |

| 27         | FF/GEB2/IO49RSB2  |

| 28         | GEC2/IO48RSB2     |

| 29         | IO47RSB2          |

| 30         | IO46RSB2          |

| 31         | IO45RSB2          |

| 32         | IO44RSB2          |

| 33         | IO43RSB2          |

| 34         | IO42RSB2          |

| 35         | IO41RSB2          |

| 36         | IO40RSB2          |

| VQ100      |                   |

|------------|-------------------|

| Pin Number | AGLN250Z Function |

| 37         | VCC               |

| 38         | GND               |

| 39         | VCCIB2            |

| 40         | IO39RSB2          |

| 41         | IO38RSB2          |

| 42         | IO37RSB2          |

| 43         | GDC2/IO36RSB2     |

| 44         | GDB2/IO35RSB2     |

| 45         | GDA2/IO34RSB2     |

| 46         | GNDQ              |

| 47         | TCK               |

| 48         | TDI               |

| 49         | TMS               |

| 50         | VMV2              |

| 51         | GND               |

| 52         | VPUMP             |

| 53         | NC                |

| 54         | TDO               |

| 55         | TRST              |

| 56         | VJTAG             |

| 57         | GDA1/IO33RSB1     |

| 58         | GDC0/IO32RSB1     |

| 59         | GDC1/IO31RSB1     |

| 60         | IO30RSB1          |

| 61         | GCB2/IO29RSB1     |

| 62         | GCA1/IO27RSB1     |

| 63         | GCA0/IO28RSB1     |

| 64         | GCC0/IO26RSB1     |

| 65         | GCC1/IO25RSB1     |

| 66         | VCCIB1            |

| 67         | GND               |

| 68         | VCC               |

| 69         | IO24RSB1          |

| 70         | GBC2/IO23RSB1     |

| 71         | GBB2/IO22RSB1     |

| 72         | IO21RSB1          |

| VQ100      |                   |

|------------|-------------------|

| Pin Number | AGLN250Z Function |

| 73         | GBA2/IO20RSB1     |

| 74         | VMV1              |

| 75         | GNDQ              |

| 76         | GBA1/IO19RSB0     |

| 77         | GBA0/IO18RSB0     |

| 78         | GBB1/IO17RSB0     |

| 79         | GBB0/IO16RSB0     |

| 80         | GBC1/IO15RSB0     |

| 81         | GBC0/IO14RSB0     |

| 82         | IO13RSB0          |

| 83         | IO12RSB0          |

| 84         | IO11RSB0          |

| 85         | IO10RSB0          |

| 86         | IO09RSB0          |

| 87         | VCCIB0            |

| 88         | GND               |

| 89         | VCC               |

| 90         | IO08RSB0          |

| 91         | IO07RSB0          |

| 92         | IO06RSB0          |

| 93         | GAC1/IO05RSB0     |

| 94         | GAC0/IO04RSB0     |

| 95         | GAB1/IO03RSB0     |

| 96         | GAB0/IO02RSB0     |

| 97         | GAA1/IO01RSB0     |

| 98         | GAA0/IO00RSB0     |

| 99         | GNDQ              |

| 100        | VMV0              |

**Microsemi Corporate Headquarters** One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail:

sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.