Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                         |

| Core Size                  | 16/32-Bit                                                                     |

| Speed                      | 96MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 80                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 64K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                    |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-LFBGA                                                                     |

| Supplier Device Package    | -                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str910faz32h6         |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49. | ADC conversion time (silicon Rev H and higher)                          | 91 |

|-----------|-------------------------------------------------------------------------|----|

| Table 50. | LQFP80 12 x12 mm low-profile quad flat package                          |    |

|           | mechanical data                                                         | 96 |

| Table 51. | LQFP128 - 128-pin, 14 x 14 mm low-profile quad flat package             |    |

|           | mechanical data                                                         | 99 |

| Table 52. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |    |

|           | 0.8 mm pitch, package mechanical data 1                                 | 02 |

| Table 53. | Thermal characteristics                                                 | 04 |

| Table 54. | Ordering information scheme                                             | 05 |

| Table 55. | Document revision history 1                                             | 06 |

# List of figures

| Figure 1.  | STR91xFA block diagram                                                  | 14  |

|------------|-------------------------------------------------------------------------|-----|

| Figure 2.  | Clock control                                                           | 21  |

| Figure 3.  | JTAG chaining inside the STR91xFA                                       | 28  |

| Figure 4.  | EMI 16-bit multiplexed connection example                               | 40  |

| Figure 5.  | EMI 8-bit multiplexed connection example                                | 40  |

| Figure 6.  | EMI 8-bit non-multiplexed connection example                            | 41  |

| Figure 7.  | STR91xFAM 80-pin package pinout                                         | 43  |

| Figure 8.  | STR91xFAW 128-pin package pinout                                        | 44  |

| Figure 9.  | STR91xFA memory map                                                     | 57  |

| Figure 10. | Pin loading conditions                                                  | 58  |

| Figure 11. | Pin input voltage                                                       | 59  |

| Figure 12. | LVD reset delay case 1                                                  | 63  |

| Figure 13. | LVD reset delay case 2                                                  | 63  |

| Figure 14. | LVD reset delay case 3                                                  | 63  |

| Figure 15. | Sleep mode current vs temperature with LVD on                           | 65  |

| Figure 16. | Typical application with an external clock source                       | 68  |

| Figure 17. | Typical application with a 32.768 kHz crystal                           | 69  |

| Figure 18. | Non-mux write timings                                                   | 76  |

| Figure 19. | Non-mux bus read timings                                                | 77  |

| Figure 20. | Mux write diagram                                                       | 78  |

| Figure 21. | Mux read diagram                                                        | 79  |

| Figure 22. | Page mode read diagram                                                  | 80  |

| Figure 23. | Sync burst write diagram                                                |     |

| Figure 24. | Sync burst read diagram.                                                | 83  |

| Figure 25. | MIL_RX_CLK and MIL_TX_CLK timing diagram                                | 84  |

| Figure 26. | MDC timing diagram                                                      |     |

| Figure 27. | Ethernet MII management timing diagram                                  | 85  |

| Figure 28. | Ethernet MII transmit timing diagram                                    |     |

| Figure 29. | Ethernet MII receive timing diagram                                     |     |

| Figure 30. | SPI slave timing diagram with CPHA = 0                                  | 88  |

| Figure 31. | SPI slave timing diagram with CPHA = 1                                  | 89  |

| Figure 32. | SPI master timing diagram                                               | 89  |

| Figure 33. | ADC conversion characteristics                                          | 92  |

| Figure 34. | Device marking for revision G LQFP80 and LQFP128 packages.              | 93  |

| Figure 35. | Device marking for revision G LFBGA144 packages                         | 93  |

| Figure 36. | Device marking for revision H LQFP80 and LQFP128 packages.              | 93  |

| Figure 37. | Device marking for revision H LFBGA144 packages                         | 93  |

| Figure 38. | Device marking for revision A LQFP80 and LQFP128 packages               |     |

| Figure 39. | Device marking for revision A LFBGA144 packages                         | 94  |

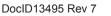

| Figure 40. | LQFP80 12 x 12 mm 80 pin low-profile quad flat package outline          | 95  |

| Figure 41. | LQFP80 - 80 pin, 12 x 12 mm low-profile quad flat package footprint     | 96  |

| Figure 42. | LQFP80 package top view                                                 |     |

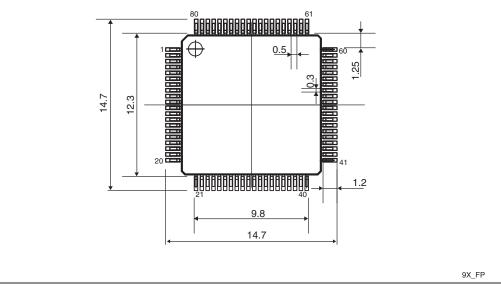

| Figure 43. | LQFP128 14 x 14 mm 128 pin low-profile quad flat package outline        | 98  |

| Figure 44. | LQFP128 package top view                                                |     |

| Figure 45. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |     |

| -          | 0.8 mm pitch, package outline                                           | 101 |

| Figure 46. | LFBGA144 package top view                                               |     |

| Figure 47. | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                   | 103 |

# 1 Description

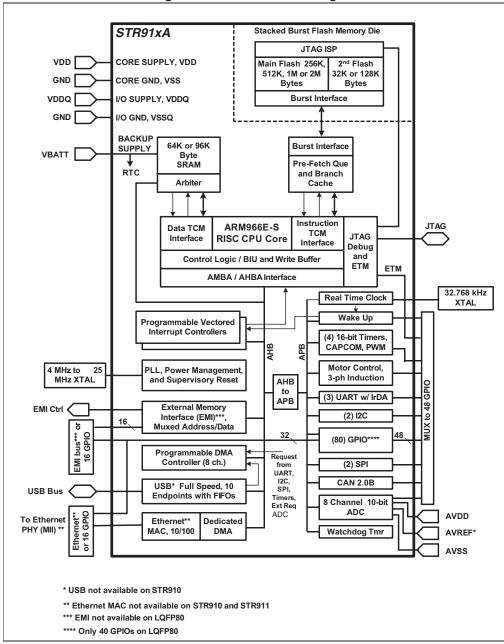

STR91xFA is a series of ARM<sup>®</sup>-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

Figure 1. STR91xFA block diagram

## 3.7 Non-volatile memories

There are two independent 32-bit wide burst Flash memories enabling true read-while-write operation. The Flash memories are single-voltage erase/program with 20 year minimum data retention and 100K minimum erase cycles. The primary Flash memory is much larger than the secondary Flash.

Both Flash memories are blank when devices are shipped from ST. The CPU can boot only from Flash memory (configurable selection of which Flash bank).

Flash memories are programmed half-word (16 bits) at a time, but are erased by sector or by full array.

## 3.7.1 Primary Flash memory

Using the STR91xFA device configuration software tool and 3rd party Integrated Developer Environments, it is possible to specify that the primary Flash memory is the default memory from which the CPU boots at reset, or otherwise specify that the secondary Flash memory is the default boot memory. This choice of boot memory is non-volatile and stored in a location that can be programmed and changed only by JTAG In-System Programming. See *Section 6: Memory mapping*, for more detail.

The primary Flash memory has equal length 64K byte sectors. See *Table 3* for number of sectors per device type.

|                       | 5 1        |            | - ,     |          |

|-----------------------|------------|------------|---------|----------|

| Size of primary Flash | 256 Kbytes | 512 Kbytes | 1 Mbyte | 2 Mbytes |

| Number of sectors     | 4          | 8          | 16      | 32       |

| Size of each sector   | 64 K       | bytes      | 64 K    | bytes    |

Table 3. Sectoring of primary Flash memory

## 3.7.2 Secondary Flash memory

The smaller of the two Flash memories can be used to implement a bootloader, capable of storing code to perform robust In-Application Programming (IAP) of the primary Flash memory. The CPU executes code from the secondary Flash, while updating code in the primary Flash memory. New code for the primary Flash memory can be downloaded over any of the interfaces on the STR91xFA (USB, Ethernet, CAN, UART, etc.)

Additionally, the secondary Flash memory may also be used to store small data sets by emulating EEPROM through firmware, eliminating the need for external EEPROM memories. This raises the data security level because passcodes and other sensitive information can be securely locked inside the STR91xFA device.

The secondary Flash memory is sectored as shown in *Table 4* according to device type.

Both the primary Flash memory and the secondary Flash memory can be programmed with code and/or data using the JTAG In-System Programming (ISP) channel, totally independent of the CPU. This is excellent for iterative code development and for manufacturing.

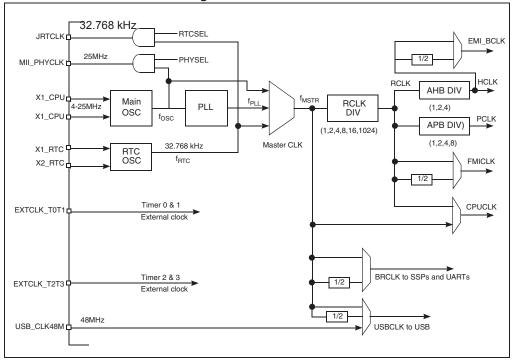

As an option, there are a number of peripherals that do not have to receive a clock sourced from the CCU. The USB interface can receive an external clock on pin P2.7, TIM timers TIM0/ TIM1 can receive an external clock on pin P2.4, and timers TIM2/TIM3 on pin P2.5.

Figure 2. Clock control

## 3.10.2 Reference clock (RCLK)

The main clock ( $f_{MSTR}$ ) can be divided to operate at a slower frequency reference clock (RCLK) for the ARM core and all the peripherals. The RCLK provides the divided clock for the ARM core, and feeds the dividers for the AHB, APB, External Memory Interface, and FMI units.

#### 3.10.3 AHB clock (HCLK)

The RCLK can be divided by 1, 2 or 4 to generate the AHB clock. The AHB clock is the bus clock for the AHB bus and all bus transfers are synchronized to this clock. The maximum HCLK frequency is 96 MHz.

#### 3.10.4 APB clock (PCLK)

The RCLK can be divided by 1, 2, 4 or 8 to generate the APB clock. The APB clock is the bus clock for the APB bus and all bus transfers are synchronized to this clock. Many of the peripherals that are connected to the AHB bus also use the PCLK as the source for external bus data transfers. The maximum PCLK frequency is 48 MHz.

#### 3.10.11 Operation example

As an example of CCU operation, a 25 MHz crystal can be connected to the main oscillator input on pins X1\_CPU and X2\_CPU, a 32.768 kHz crystal connected to pins X1\_RTC and X2\_RTC, and the clock input of an external Ethernet PHY device is connected to STR91xFA output pin P5.2. In this case, the CCU can run the CPU at 96 MHz from PLL, the USB interface at 48 MHz, and the Ethernet interface at 25 MHz. The RTC is always running in the background at 32.768 kHz, and the CPU can go to very low power mode dynamically by running from 32.768 kHz and shutting off peripheral clocks and the PLL as needed.

## 3.11 Flexible power management

The STR91xFA offers configurable and flexible power management control that allows the user to choose the best power option to fit the application. Power consumption can be dynamically managed by firmware and hardware to match the system's requirements. Power management is provided via clock control to the CPU and individual peripherals.

Clocks to the CPU and peripherals can be individually divided and gated off as needed. In addition to individual clock divisors, the CCU master clock source going to the CPU, AHB, APB, EMI, and FMI can be divided dynamically by as much as 1024 for low power operation. Additionally, the CCU may switch its input to the 32.768 kHz RTC clock at any time for low power.

The STR91xFA supports the following three global power control modes:

- Run Mode: All clocks are on with option to gate individual clocks off via clock mask registers.

- Idle Mode: CPU and FMI clocks are off until an interrupt, reset, or wake-up occurs. Pre-configured clock mask registers selectively allow individual peripheral clocks to continue run during Idle Mode.

- Sleep Mode: All clocks off except RTC clock. Wake up unit remains powered, PLL is forced off.

A special mode is used when JTAG debug is active which never gates off any clocks even if the CPU enters Idle or Sleep mode.

## 3.11.1 Run mode

This is the default mode after any reset occurs. Firmware can gate off or scale any individual clock. Also available is a special Interrupt Mode which allows the CPU to automatically run full speed during an interrupt service and return back to the selected CPU clock divisor rate when the interrupt has been serviced. The advantage here is that the CPU can run at a very low frequency to conserve power until a periodic wake-up event or an asynchronous interrupt occurs at which time the CPU runs full speed immediately.

#### 3.12.2 Battery supply

An optional stand-by voltage from a battery or other source may be connected to pin VBATT to retain the contents of SRAM in the event of a loss of the main digital supplies ( $V_{DD}$  and  $V_{DDQ}$ ). The SRAM will automatically switch its supply from the internal  $V_{DD}$  source to the VBATT pin when the voltage of  $V_{DD}$  drops below the LVD threshold. In order to use the battery supply, the LVD must be enabled.

The VBATT pin also supplies power to the RTC unit, allowing the RTC to function even when the main digital supplies ( $V_{DD}$  and  $V_{DDQ}$ ) are switched off. By configuring the RTC register, it is possible to select whether or not to power from VBATT only the RTC unit, or power the RTC unit and the SRAM when the STR91xFA device is powered off.

## 3.13 System supervisor

The STR91xFA monitors several system and environmental inputs and will generate a global reset, a system reset, or an interrupt based on the nature of the input and configurable settings. A global reset clears all functions on the STR91xFA, a system reset will clear all but the Clock Control Unit (CCU) settings and the system status register. At any time, firmware may reset individual on-chip peripherals. System supervisor inputs include:

- GR: CPU voltage supply (V<sub>DD</sub>) drop out or brown out

- GR: I/O voltage supply (V<sub>DDQ</sub>) drop out or brown out

- GR: Power-Up condition

- SR: Watchdog timer timeout

- SR: External reset pin (RESET\_INn)

- SR: JTAG debug reset command

Note: GR: means the input causes Global Reset, SR: means the input causes System Reset

The CPU may read a status register after a reset event to determine if the reset was caused by a watchdog timer timeout or a voltage supply drop out. This status register is cleared only by a power up reset.

#### 3.13.1 Supply voltage brownout

Each operating voltage source ( $V_{DD}$  and  $V_{DDQ}$ ) is monitored separately by the Low Voltage Detect (LVD) circuitry. The LVD will generate an early warning interrupt to the CPU when voltage sags on either  $V_{DD}$  or  $V_{DDQ}$  voltage inputs. This is an advantage for battery powered applications because the system can perform an orderly shutdown before the batteries become too weak. The voltage trip point to cause a brown out interrupt is typically 0.25V above the LVD dropout thresholds that cause a reset.

CPU firmware may prevent all brown-out interrupts by writing to interrupt mask registers at run-time.

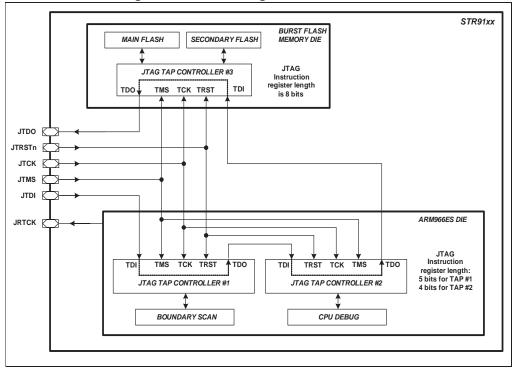

three TAPs are daisy-chained, only one TAP will converse on the JTAG bus at any given time while the other two TAPs are in BYPASS mode. The TAP positioning order within this JTAG chain is the boundary scan TAP first, followed by the ARM debug TAP, followed by the Flash TAP. All three TAP controllers are reset simultaneously by one of two methods:

- A chip-level global reset, caused only by a Power-On-Reset (POR) or a Low Voltage Detect (LVD).

- A reset command issued by the external JTAG test equipment. This can be the assertion of the JTAG JTRSTn input pin on the STR91xFA or a JTAG reset command shifted into the STR91xFA serially.

This means that chip-level system resets from watchdog time-out or the assertion of RESET\_INn pin do not affect the operation of any JTAG TAP controller. Only global resets effect the TAPs.

Figure 3. JTAG chaining inside the STR91xFA

#### 3.15.1 In-system-programming

The JTAG interface is used to program or erase all memory areas of the STR91xFA device. The pin RESET\_INn must be asserted during ISP to prevent the CPU from fetching invalid instructions while the Flash memories are being programmed.

Note that the 32 bytes of OTP memory locations cannot be erased by any means once programmed by JTAG ISP or the CPU.

#### 3.15.2 Boundary scan

Standard JTAG boundary scan testing compliant with IEEE-1149.1 is available on the majority of pins of the STR91xFA for circuit board test during manufacture of the end product. STR91xFA pins that are not serviced by boundary scan are the following:

- JTAG pins JTCK, JTMS, JTDI, JTDO, JTRSTn, JRTCK

- Oscillator input pins X1\_CPU, X2\_CPU, X1\_RTC, X2\_RTC

- Tamper detect input pin TAMPER\_IN (128-pin and 144-pin packages only)

## 3.15.3 CPU debug

The ARM966E-S CPU core has standard ARM EmbeddedICE-RT logic, allowing the STR91xFA to be debugged through the JTAG interface. This provides advanced debugging features making it easier to develop application firmware, operating systems, and the hardware itself. Debugging requires that an external host computer, running debug software, is connected to the STR91xFA target system via hardware which converts the stream of debug data and commands from the host system's protocol (USB, Ethernet, etc.) to the JTAG EmbeddedICE-RT protocol on the STR91xFA. These protocol converters are commercially available and operate with debugging software tools.

The CPU may be forced into a Debug State by a breakpoint (code fetch), a watchpoint (data access), or an external debug request over the JTAG channel, at which time the CPU core and memory system are effectively stopped and isolated from the rest of the system. This is known as Halt Mode and allows the internal state of the CPU core, memory, and peripherals to be examined and manipulated. Typical debug functions are supported such as run, halt, and single-step. The EmbeddedICE-RT logic supports two hardware compare units. Each can be configured to be either a watchpoint or a breakpoint. Breakpoints can also be data-dependent.

Debugging (with some limitations) may also occur through the JTAG interface while the CPU is running full speed, known as Monitor Mode. In this case, a breakpoint or watchpoint will not force a Debug State and halt the CPU, but instead will cause an exception which can be tracked by the external host computer running monitor software. Data can be sent and received over the JTAG channel without affecting normal instruction execution. Time critical code, such as Interrupt Service Routines may be debugged real-time using Monitor Mode.

#### 3.15.4 JTAG security bit

This is a non-volatile bit (Flash memory based), which when set will not allow the JTAG debugger or JTAG programmer to read the Flash memory contents.

Using JTAG ISP, this bit is typically programmed during manufacture of the end product to prevent unwanted future access to firmware intellectual property. The JTAG Security Bit can be cleared only by a JTAG "Full Chip Erase" command, making the STR91xFA device blank (except for programmed OTP bytes), and ready for programming again. The CPU can read the status of the JTAG Security Bit, but it may not change the bit value.

#### 3.18.1 Packet buffer interface (PBI)

The PBI manages a set of buffers inside the 2 Kbyte Packet Buffer, both for transmission and reception. The PBI will choose the proper buffer according to requests coming from the USB Serial Interface Engine (SIE) and locate it in the Packet SRAM according to addresses pointed by endpoint registers. The PBI will also auto-increment the address after each exchanged byte until the end of packet, keeping track of the number of exchanged bytes and preventing buffer overrun. Special support is provided by the PBI for isochronous and bulk transfers, implementing double-buffer usage which ensures there is always an available buffer for a USB packet while the CPU uses a different buffer.

#### 3.18.2 DMA

A programmable DMA channel may be assigned by CPU firmware to service the USB interface for fast and direct transfers between the USB bus and SRAM with little CPU involvement. This DMA channel includes the following features:

- Direct USB Packet Buffer SRAM to system SRAM transfers of receive packets, by descriptor chain for bulk or isochronous endpoints.

- Direct system SRAM to USB Packet Buffer SRAM transfers of transmit packets, by descriptor chain for bulk or isochronous endpoints.

- Linked-list descriptor chain support for multiple USB packets

#### 3.18.3 Suspend mode

CPU firmware may place the USB interface in a low-power suspend mode when required, and the USB interface will automatically wake up asynchronously upon detecting activity on the USB pins.

## 3.19 CAN 2.0B interface

The STR91xFA provides a CAN interface complying with CAN protocol version 2.0 parts A and B. An external CAN transceiver device connected to pins CAN\_RX and CAN\_TX is required for connection to the physical CAN bus.

The CAN interface manages up to 32 Message Objects and Identifier Masks using a Message SRAM and a Message Handler. The Message Handler takes care of low-level CAN bus activity such as acceptance filtering, transfer of messages between the CAN bus and the Message SRAM, handling of transmission requests, and interrupt generation. The CPU has access to the Message SRAM via the Message Handler using a set of 38 control registers.

The follow features are supported by the CAN interface:

- Bit rates up to 1 Mbps

- Disable Automatic Retransmission mode for Time Triggered CAN applications

- 32 Message Objects

- Each Message Object has its own Identifier Mask

- Programmable FIFO mode

- Programmable loopback mode for self-test operation

The CAN interface is not supported by DMA.

## 3.20 UART interfaces with DMA

The STR91xFA supports three independent UART serial interfaces, designated UART0, UART1, and UART2. Each interface is very similar to the industry-standard 16C550 UART device. All three UART channels support IrDA encoding/decoding, requiring only an external LED transceiver to pins UARTx\_RX and UARTx\_Tx for communication. One UART channel (UART0) supports full modem control signals.

UART interfaces include the following features:

- Maximum baud rate of 1.5 Mbps

- Separate FIFOs for transmit and receive, each 16 deep, each FIFO can be disabled by firmware if desired

- Programmable FIFO trigger levels between 1/8 and 7/8

- Programmable baud rate generator based on CCU master clock, or CCU master clock divided by two

- Programmable serial data lengths of 5, 6, 7, or 8 bits with start bit and 1 or 2 stop bits

- Programmable selection of even, odd, or no-parity bit generation and detection

- False start-bit detection

- Line break generation and detection

- Support of IrDA SIR ENDEC functions for data rates of up to 115.2K bps

- IrDA bit duration selection of 3/16 or low-power (1.14 to 2.23 µsec)

- Channel UART0 supports modem control functions CTS, DCD, DSR, RTS, DTR, and RI

For your reference, only two standard 16550 UART features are not supported, 1.5 stop bits and independent receive clock.

#### 3.20.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service channels UART0 and UART1 for fast and direct transfers between the UART bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that UART FIFOs are enabled.

# 3.21 I<sup>2</sup>C interfaces

The STR91xFA supports two independent I2C serial interfaces, designated I2C0, and I2C1. Each interface allows direct connection to an I2C bus as either a bus master or bus slave device (firmware configurable). I2C is a two-wire communication channel, having a bidirectional data signal and a single-directional clock signal based on open-drain line drivers, requiring external pull-up resistors.

Byte-wide data is transferred between a Master device and a Slave device on two wires. More than one bus Master is allowed, but only one Master may control the bus at any given time. Data is not lost when another Master requests the use of a busy bus because I2C supports collision detection and arbitration. More than one Slave device may be present on the bus, each having a unique address. The bus Master initiates all data movement and generates the clock that permits the transfer. Once a transfer is initiated by the Master, any device that is addressed is considered a Slave. Automatic clock synchronization allows I2C devices with different bit rates to communicate on the same physical bus.

|        |         |          |             |             | Та                         | ble 8. Device                  | pin descript                    | ion                    |                               |                                   |

|--------|---------|----------|-------------|-------------|----------------------------|--------------------------------|---------------------------------|------------------------|-------------------------------|-----------------------------------|

| F      | Pack    | age      |             | e           |                            |                                |                                 | Alternate              | functions                     |                                   |

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name | Signal type | Default pin function       | Default<br>input<br>function   | Alternate<br>input 1            | Alternate<br>output 1  | Alternate<br>output 2         | Alternate<br>output 3             |

| -      | 67      | L11      | P0.0        | I/O         | GPIO_0.0,<br>GP Input, HiZ | MII_TX_CLK,<br>PHY Xmit clock  | I2C0_CLKIN,<br>I2C clock in     | GPIO_0.0,<br>GP Output | I2C0_CLKOUT,<br>I2C clock out | ETM_PCK0,<br>ETM Packet           |

| -      | 69      | K10      | P0.1        | I/O         | GPIO_0.1,<br>GP Input, HiZ | -                              | I2C0_DIN,<br>I2C data in        | GPIO_0.1,<br>GP Output | I2C0_DOUT,<br>I2C data out    | ETM_PCK1,<br>ETM Packet           |

| -      | 71      | J11      | P0.2        | I/O         | GPIO_0.2,<br>GP Input, HiZ | MII_RXD0,<br>PHY Rx data0      | I2C1_CLKIN,<br>I2C clock in     | GPIO_0.2,<br>GP Output | I2C1_CLKOUT,<br>I2C clock out | ETM_PCK2,<br>ETM Packet           |

| -      | 76      | H12      | P0.3        | I/O         | GPIO_0.3,<br>GP Input, HiZ | MII_RXD1,<br>PHY Rx data       | I2C1_DIN,<br>I2C data in        | GPIO_0.3,<br>GP Output | I2C1_DOUT,<br>I2C data out    | ETM_PCK3,<br>ETM Packet           |

| -      | 78      | H10      | P0.4        | I/O         | GPIO_0.4,<br>GP Input, HiZ | MII_RXD2,<br>PHY Rx data       | TIM0_ICAP1,<br>Input Capture    | GPIO_0.4,<br>GP Output | EMI_CS0n,<br>EMI Chip Select  | ETM_PSTAT0,<br>ETM pipe status    |

| -      | 85      | F11      | P0.5        | I/O         | GPIO_0.5,<br>GP Input, HiZ | MII_RXD3,<br>PHY Rx data       | TIM0_ICAP2,<br>Input Capture    | GPIO_0.5,<br>GP Output | EMI_CS1n,<br>EMI Chip Select  | ETM_PSTAT1,<br>ETM pipe status    |

| -      | 88      | E11      | P0.6        | I/O         | GPIO_0.6,<br>GP Input, HiZ | MII_RX_CLK,<br>PHY Rx clock    | TIM2_ICAP1,<br>Input Capture    | GPIO_0.6,<br>GP Output | EMI_CS2n,<br>EMI Chip Select  | ETM_PSTAT2,<br>ETM pipe status    |

| -      | 90      | B12      | P0.7        | I/O         | GPIO_0.7,<br>GP Input, HiZ | MII_RX_DV,<br>PHY data valid   | TIM2_ICAP2,<br>Input Capture    | GPIO_0.7,<br>GP Output | EMI_CS3n,<br>EMI Chip Select  | ETM_TRSYNC,<br>ETM trace sync     |

| -      | 98      | B10      | P1.0        | I/O         | GPIO_1.0,<br>GP Input, HiZ | MII_RX_ER,<br>PHY rcv error    | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_1.0,<br>GP Output | UART1_TX,<br>UART xmit data   | SSP1_SCLK,<br>SSP mstr clk<br>out |

| -      | 99      | C10      | P1.1        | I/O         | GPIO_1.1,<br>GP Input, HiZ | -                              | UART1_RX,<br>UART rcv data      | GPIO_1.1,<br>GP Output | MII_TXD0,<br>MAC Tx data      | SSP1_MOSI,<br>SSP mstr dat<br>out |

| -      | 101     | B9       | P1.2        | I/O         | GPIO_1.2,<br>GP Input, HiZ | -                              | SSP1_MISO,<br>SSP mstr data in  | GPIO_1.2,<br>GP Output | MII_TXD1,<br>MAC Tx data      | UART0_TX,<br>UART xmit data       |

| -      | 106     | C8       | P1.3        | I/O         | GPIO_1.3,<br>GP Input, HiZ | -                              | UART2_RX,<br>UART rcv data      | GPIO_1.3,<br>GP Output | MII_TXD2,<br>MAC Tx data      | SSP1_NSS,<br>SSP mstr sel<br>out  |

| -      | 109     | B7       | P1.4        | I/O         | GPIO_1.4,<br>GP Input, HiZ | -                              | I2C0_CLKIN,<br>I2C clock in     | GPIO_1.4,<br>GP Output | MII_TXD3,<br>MAC Tx data      | I2C0_CLKOUT,<br>I2C clock out     |

| -      | 110     | A7       | P1.5        | I/O         | GPIO_1.5,<br>GP Input, HiZ | MII_COL,<br>PHY collision      | CAN_RX,<br>CAN rcv data         | GPIO_1.5,<br>GP Output | UART2_TX,<br>UART xmit data   | ETM_TRCLK,<br>ETM trace clock     |

| -      | 114     | F7       | P1.6        | I/O         | GPIO_1.6,<br>GP Input, HiZ | MII_CRS,<br>PHY carrier sns    | I2C0_DIN,<br>I2C data in        | GPIO_1.6,<br>GP Output | CAN_TX,<br>CAN Tx data        | I2C0_DOUT,<br>I2C data out        |

| -      | 116     | D6       | P1.7        | I/O         | GPIO_1.7,<br>GP Input, HiZ | -                              | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_1.7,<br>GP Output | MII_MDC,<br>MAC mgt dat ck    | ETM_TRCLK,<br>ETM trace clock     |

| 7      | 10      | E2       | P2.0        | I/O         | GPIO_2.0,                  | UART0_CTS,                     | I2C0_CLKIN,                     | GPIO_2.0,              | I2C0_CLKOUT,                  | ETM_PCK0,                         |

| 8      | 10      | E3       | P2.1        | 1/0         | GP Input, HiZ<br>GPIO_2.1, | Clear To Send<br>UART0_DSR,    | I2C clock in<br>I2C0_DIN,       | GP Output<br>GPIO_2.1, | I2C clock out<br>I2C0_DOUT,   | ETM Packet<br>ETM_PCK1,           |

| 21     | 33      | M1       | P2.2        | 1/0         | GP Input, HiZ<br>GPIO_2.2, | Data Set Ready<br>UART0_DCD,   | I2C data in<br>I2C1_CLKIN,      | GP Output<br>GPIO_2.2, | I2C data out                  | ETM Packet<br>ETM_PCK2,           |

| 22     | 35      | K3       | P2.3        | 1/0         | GP Input, HiZ<br>GPIO_2.3, | Dat Carrier Det                | I2C clock in<br>I2C1_DIN,       | GP Output<br>GPIO_2.3, | I2C clock out                 | ETM Packet<br>ETM_PCK3,           |

| 22     | 37      | L4       | P2.4        | 1/0         | GP Input, HiZ<br>GPIO_2.4, | Ring Indicator<br>EXTCLK_T0T1E | I2C data in<br>SSP0_SCLK,       | GP Output<br>GPIO_2.4, | I2C data out<br>SSP0_SCLK,    | ETM Packet<br>ETM_PSTAT0,         |

| 20     | 51      | L4       | 1 2.4       | "0          | GP Input, HiZ              | xt clk timer0/1                | SSP slv clk in                  | GP Output              | SSP mstr clk out              | ETM pipe status                   |

Table 8. Device pin description

| <b>_</b> | Dect    |          |                | 1           |                                                                                      | Device pin description (continued) |                      |                       |                       |                       |  |  |  |  |

|----------|---------|----------|----------------|-------------|--------------------------------------------------------------------------------------|------------------------------------|----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

|          | Packa   | age      |                | ЭС          |                                                                                      |                                    | Alternate functions  |                       |                       |                       |  |  |  |  |

| LQFP80   | LQFP128 | LFBGA144 | Pin<br>name    | Signal type | Default pin<br>function                                                              | Default<br>input<br>function       | Alternate<br>input 1 | Alternate<br>output 1 | Alternate<br>output 2 | Alternate<br>output 3 |  |  |  |  |

| 27       | 42      | M5       | X1_RTC         | I           | RTC oscillator<br>or crystal input<br>(32.768 kHz)                                   |                                    | N/A                  |                       |                       |                       |  |  |  |  |

| 26       | 41      | M4       | X2_RTC         | 0           | RTC crystal connection                                                               |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 61       | 97      | B11      | JRTCK          | 0           | JTAG return<br>clock or RTC<br>clock                                                 |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 67       | 107     | D8       | JTRSTn         | I           | JTAG TAP<br>controller reset                                                         |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 68       | 108     | E8       | JTCK           | I           | JTAG clock                                                                           |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 69       | 111     | A6       | JTMS           | I           | JTAG mode<br>select                                                                  |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 72       | 115     | C6       | JTDI           | I           | JTAG data in                                                                         |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 73       | 117     | B6       | JTDO           | 0           | JTAG data out                                                                        |                                    |                      | N/A                   |                       |                       |  |  |  |  |

|          |         |          |                |             |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| -        | 122     | A3       | AVDD           | v           | ADC analog<br>voltage source,<br>2.7 V - 3.6 V                                       |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| -        | 4       | C3       | AVSS           | G           | ADC analog<br>ground                                                                 |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 5        | -       | -        | AVSS_<br>VSSQ  | G           | Common<br>ground point<br>for digital I/O &<br>analog ADC                            |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| -        | 123     | A2       | AVREF          | v           | ADC reference voltage input                                                          |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 76       | -       | -        | AVREF_<br>AVDD | v           | Combined<br>ADC ref<br>voltage and<br>ADC analog<br>voltage source,<br>2.7 V - 3.6 V |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 24       | 39      | M3       | VBATT          | v           | Standby<br>voltage input<br>for RTC and<br>SRAM backup                               |                                    |                      | N/A                   |                       |                       |  |  |  |  |

| 6        | 9       | E1       | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| 15       | 23      | J1       | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| 36       | 57      | -        | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| 46       | 73      | K12      | VDDQ           | V           | V Source for                                                                         |                                    |                      |                       |                       |                       |  |  |  |  |

| 54       | 86      | B5       | VDDQ           | V           | I/O and USB.<br>2.7 V to 3.6 V                                                       |                                    | N/A                  |                       |                       |                       |  |  |  |  |

| 28       | 43      | L5       | VDDQ           | V           | 2.7 V (0 0.0 V                                                                       |                                    |                      |                       |                       |                       |  |  |  |  |

| 63       | 102     | H7       | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| 74       | 120     | D9       | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

| -        | -       | F9       | VDDQ           | V           |                                                                                      |                                    |                      |                       |                       |                       |  |  |  |  |

Table 8. Device pin description (continued)

|        | Pack    | ane      |             |             |                                     |                              | Alternate functions  |                       |                       |                       |  |  |  |  |

|--------|---------|----------|-------------|-------------|-------------------------------------|------------------------------|----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

|        | acro    | aye      |             | be          |                                     |                              |                      | Allemale              | Turictions            |                       |  |  |  |  |

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name | Signal type | Default pin<br>function             | Default<br>input<br>function | Alternate<br>input 1 | Alternate<br>output 1 | Alternate<br>output 2 | Alternate<br>output 3 |  |  |  |  |

| -      | 8       | L2       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 16     | 24      | K4       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 35     | 56      | C5       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| -      | -       | D4       | VSSQ        | G           | Digital Ground                      |                              | N/A                  |                       |                       |                       |  |  |  |  |

| 45     | 72      | G5       | VSSQ        | G           | for                                 |                              |                      |                       |                       |                       |  |  |  |  |

| 55     | 87      | J7       | VSSQ        | G           | !/O and USB                         |                              |                      |                       |                       |                       |  |  |  |  |

| 25     | 40      | A8       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 66     | 105     | F8       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 75     | 121     | L12      | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 11     | 17      | F4       | VDD         | V           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 31     | 49      | D7       | VDD         | V           | V Source for                        |                              |                      |                       |                       |                       |  |  |  |  |

| 50     | 81      | L6       | VDD         | V           | CPU.<br>1.65 V - 2.0 V              |                              |                      | N/A                   |                       |                       |  |  |  |  |

| 70     | 112     | G11      | VDD         | V           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 10     | 16      | F3       | VSS         | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| 30     | 48      | H5       | VSS         | G           | Digital Ground                      |                              |                      |                       |                       |                       |  |  |  |  |

| 51     | 82      | G10      | VSS         | G           | for CPU                             |                              |                      | N/A                   |                       |                       |  |  |  |  |

| 71     | 113     | E7       | VSS         | G           |                                     |                              |                      |                       |                       |                       |  |  |  |  |

| -      | -       | C9       | PLLV<br>DDQ | v           | V Source for<br>PLL<br>2.7 to 3.6 V | N/A                          |                      |                       |                       |                       |  |  |  |  |

| -      | -       | B8       | PLLV<br>SSQ | G           | Digital Ground<br>for PLL           |                              |                      |                       |                       |                       |  |  |  |  |

Table 8. Device pin description (continued)

#### 7.9.5 Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

#### 7.9.6 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

## 7.9.7 Electrical sensitivity

#### Table 30. Static latch-up data

| Symbol | Parameter             | Conditions                                    | Class <sup>(1)</sup> |

|--------|-----------------------|-----------------------------------------------|----------------------|

| LU     | Static latch-up class | $T_A = +25 \ ^{\circ}C$ conforming to JESD78A | II class A           |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

| mecnanical data |       |        |                    |        |                       |        |  |  |  |

|-----------------|-------|--------|--------------------|--------|-----------------------|--------|--|--|--|

| Dim.            |       | mm     |                    |        | inches <sup>(1)</sup> |        |  |  |  |

| A               | -     | -      | 1.600              | -      | -                     | 0.0630 |  |  |  |

| A1              | 0.050 | -      | 0.150              | 0.0020 | -                     | 0.0059 |  |  |  |

| A2              | 1.350 | 1.400  | 1.450              | 0.0531 | 0.0551                | 0.0571 |  |  |  |

| b               | 0.170 | 0.220  | 0.270              | 0.0067 | 0.0087                | 0.0106 |  |  |  |

| С               | 0.090 | -      | 0.200              | 0.0035 | -                     | 0.0079 |  |  |  |

| D               | -     | 14.000 | -                  | -      | 0.5512                | -      |  |  |  |

| D1              | -     | 12.000 | -                  | -      | - 0.4724              |        |  |  |  |

| D2              | -     | 9.500  | -                  | -      | - 0.3740              |        |  |  |  |

| E               | -     | 14.000 | -                  | -      | 0.5512                | -      |  |  |  |

| E1              | -     | 12.000 | -                  | -      | 0.4724                | -      |  |  |  |

| E3              | -     | 9.500  | -                  | -      | 0.3740                | -      |  |  |  |

| е               | -     | 0.500  | -                  | -      | 0.0197                | -      |  |  |  |

| L               | 0.450 | 0.600  | 0.750 0.0177 0.023 |        | 0.0236                | 0.0295 |  |  |  |

| L1              | -     | 1.000  | -                  | -      | 0.0394                | -      |  |  |  |

| CCC             |       | 0.080  |                    |        | 0.0031                |        |  |  |  |

| k               | 0.0°  | -      | 7.0°               | 0.0°   | -                     | 7.0°   |  |  |  |

# Table 50. LQFP80 12 x12 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 41. LQFP80 - 80 pin, 12 x 12 mm low-profile quad flat package footprint

1. Dimensions are expressed in millimeters.

# 9.1 ECOPACK

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions, and product status are available at <u>www.st.com</u>.

# 9.2 Thermal characteristics

The average chip-junction temperature, T<sub>J</sub> must never exceed 125 °C.

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using the following equation:

$$T_{J} = T_{A} + (P_{D} \times \Theta_{JA})$$

(1)

Where:

- T<sub>A</sub> is the ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ ,

- P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the Chip Internal Power.

P<sub>I/O</sub> represents the power dissipation on input and output pins;

Most of the time for the applications  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant if the device is configured to drive continuously external modules and/or memories. The worst case  $P_{INT}$  of the STR91xFA is 500 mW ( $I_{DD} \times V_{DD}$ , or 250 mA x 2.0 V).

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$= K / (T_J + 273 °C)$$

(2)

Therefore (solving equations 1 and 2):

$P_D$

$$K = P_{D} x (T_{A} + 273 °C) + \Theta_{JA} x P_{D}^{2}$$

(3)

Where:

K is a constant for the particular part, which may be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> may be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

| Symbol        | Parameter                                                                         | Value | Unit |

|---------------|-----------------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LQFP 80 - 12 x 12 mm / 0.5 mm pitch | 41.5  | °C/W |

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LQFP128 - 14 x 14 mm / 0.4 mm pitch | 38    | °C/W |

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LFBGA 144 - 10 x 10 x 1.7 mm        | 36.5  | °C/W |

| Table 53. | Thermal | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

#### **Ordering information** 10

| Table 5                          | 54. Ordering | g info | orma | tion  | sch   | eme |   |   |   |   |   |

|----------------------------------|--------------|--------|------|-------|-------|-----|---|---|---|---|---|

| Example:<br>Family               | STR9         | 1      | 2    | F<br> | A<br> | W   | 4 | 4 | × | 6 | Т |

| ARM9 microcontroller family      |              |        |      |       |       |     |   |   |   |   |   |

| Series                           |              |        |      |       |       |     |   |   |   |   |   |

| 1 = STR9 series 1                |              |        |      |       |       |     |   |   |   |   |   |

| Feature set                      |              |        |      |       |       |     |   |   |   |   |   |

| 0 = CAN, UART, IrDA, I2C, SSP    |              |        |      |       |       |     |   |   |   |   |   |

| 1 = USB, CAN, UART, IrDA, I2C, S | SSP          |        |      |       |       |     |   |   |   |   |   |

| 2 = USB, CAN, UART, IrDA, I2C, S | SSP, ETHERI  | NET    |      |       |       |     |   |   |   |   |   |

| Memory type                      |              |        |      |       |       |     |   |   |   |   |   |

| F = Flash                        |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| Revision at product level        |              |        |      |       |       |     |   |   |   |   |   |

| A = Revison A                    |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| No. of pins                      |              |        |      |       |       |     |   |   |   |   |   |

| M = 80                           |              |        |      |       |       |     |   |   |   |   |   |

| W = 128                          |              |        |      |       |       |     |   |   |   |   |   |

| Z = 144                          |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| SRAM size                        |              |        |      |       |       |     |   |   |   |   |   |

| 3 = 64 Kbytes                    |              |        |      |       |       |     |   |   |   |   |   |

| 4 = 96 Kbytes                    |              |        |      |       |       |     |   |   |   |   |   |

| Primary memory size              |              |        |      |       |       |     |   |   |   |   |   |

| 2 = 256 Kbytes 6= 1024 Kbytes    |              |        |      |       |       |     |   |   |   |   |   |

| 4 = 512 Kbytes 7= 2048 Kbytes    |              |        |      |       |       |     |   |   |   |   |   |

| Package                          |              |        |      |       |       |     |   |   |   |   |   |

| X = plastic LQFP                 |              |        |      |       |       |     |   |   |   |   |   |

| H = LFBGA                        |              |        |      |       |       |     |   |   |   |   |   |

| Temperature range                |              |        |      |       |       |     |   |   |   |   |   |

| 6 = -40 to 85 °C                 |              |        |      |       |       |     |   |   |   |   |   |

| Shipping option                  |              |        |      |       |       |     |   |   |   |   |   |

| T = Tape and reel packing        |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

1. For a list of available options (e.g. speed, package) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved