Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 96MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 96K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-LQFP                                                                   |

| Supplier Device Package    | -                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str911fam44x6     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 3.10.8   | USB interface clock                                    | 22 |

|------|----------|--------------------------------------------------------|----|

|      | 3.10.9   | Ethernet MAC clock                                     | 22 |

|      | 3.10.10  | External RTC calibration clock                         | 22 |

|      | 3.10.11  | Operation example                                      | 23 |

| 3.11 | Flexible | e power management                                     | 23 |

|      | 3.11.1   | Run mode                                               | 23 |

|      | 3.11.2   | Idle mode                                              | 24 |

|      | 3.11.3   | Sleep mode                                             | 24 |

| 3.12 | Voltage  | e supplies                                             | 24 |

|      | 3.12.1   | Independent A/D converter supply and reference voltage | 24 |

|      | 3.12.2   | Battery supply                                         | 25 |

| 3.13 | System   | n supervisor                                           | 25 |

|      | 3.13.1   | Supply voltage brownout                                | 25 |

|      | 3.13.2   | Supply voltage dropout                                 | 26 |

|      | 3.13.3   | Watchdog timer                                         | 26 |

|      | 3.13.4   | External RESET_INn pin                                 | 26 |

|      | 3.13.5   | Power-up                                               | 26 |

|      | 3.13.6   | JTAG debug command                                     | 26 |

|      | 3.13.7   | Tamper detection                                       | 27 |

| 3.14 | Real-tir | me clock (RTC)                                         | 27 |

| 3.15 | JTAG ir  | nterface                                               | 27 |

|      | 3.15.1   | In-system-programming                                  | 28 |

|      | 3.15.2   | Boundary scan                                          | 29 |

|      | 3.15.3   | CPU debug                                              | 29 |

|      | 3.15.4   | JTAG security bit                                      | 29 |

| 3.16 | Embed    | lded trace module (ARM ETM9, v. r2p2)                  | 30 |

| 3.17 | Etherne  | et MAC interface with DMA                              | 30 |

| 3.18 | USB 2.   | 0 slave device interface with DMA                      | 31 |

|      | 3.18.1   | Packet buffer interface (PBI)                          | 32 |

|      | 3.18.2   | DMA                                                    | 32 |

|      | 3.18.3   | Suspend mode                                           | 32 |

| 3.19 | CAN 2.   | .0B interface                                          | 32 |

| 3.20 | UART i   | interfaces with DMA                                    | 33 |

|      | 3.20.1   | DMA                                                    | 33 |

| 3.21 | I2C inte | erfaces                                                | 33 |

| 3.22 | SSP int  | terfaces (SPI, SSI, and MICROWIRE) with DMA            | 34 |

|      |          |                                                        |    |

# List of figures

| Figure 1.  | STR91xFA block diagram                                                  | 14  |

|------------|-------------------------------------------------------------------------|-----|

| Figure 2.  | Clock control                                                           | 21  |

| Figure 3.  | JTAG chaining inside the STR91xFA                                       | 28  |

| Figure 4.  | EMI 16-bit multiplexed connection example                               | 40  |

| Figure 5.  | EMI 8-bit multiplexed connection example                                | 40  |

| Figure 6.  | EMI 8-bit non-multiplexed connection example                            | 41  |

| Figure 7.  | STR91xFAM 80-pin package pinout                                         | 43  |

| Figure 8.  | STR91xFAW 128-pin package pinout                                        | 44  |

| Figure 9.  | STR91xFA memory map                                                     | 57  |

| Figure 10. | Pin loading conditions                                                  | 58  |

| Figure 11. | Pin input voltage                                                       | 59  |

| Figure 12. | LVD reset delay case 1                                                  | 63  |

| Figure 13. | LVD reset delay case 2                                                  | 63  |

| Figure 14. | LVD reset delay case 3                                                  | 63  |

| Figure 15. | Sleep mode current vs temperature with LVD on                           | 65  |

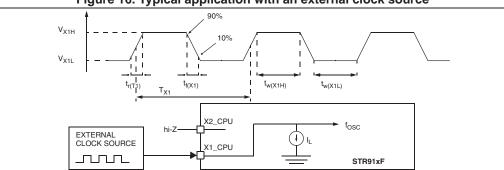

| Figure 16. | Typical application with an external clock source                       | 68  |

| Figure 17. | Typical application with a 32.768 kHz crystal                           | 69  |

| Figure 18. | Non-mux write timings                                                   | 76  |

| Figure 19. | Non-mux bus read timings                                                | 77  |

| Figure 20. | Mux write diagram                                                       | 78  |

| Figure 21. | Mux read diagram                                                        | 79  |

| Figure 22. | Page mode read diagram                                                  | 80  |

| Figure 23. | Sync burst write diagram                                                |     |

| Figure 24. | Sync burst read diagram.                                                | 83  |

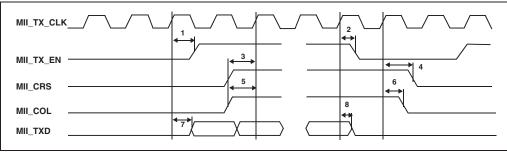

| Figure 25. | MIL_RX_CLK and MIL_TX_CLK timing diagram                                | 84  |

| Figure 26. | MDC timing diagram                                                      |     |

| Figure 27. | Ethernet MII management timing diagram                                  | 85  |

| Figure 28. | Ethernet MII transmit timing diagram                                    |     |

| Figure 29. | Ethernet MII receive timing diagram                                     |     |

| Figure 30. | SPI slave timing diagram with CPHA = 0                                  | 88  |

| Figure 31. | SPI slave timing diagram with CPHA = 1                                  | 89  |

| Figure 32. | SPI master timing diagram                                               | 89  |

| Figure 33. | ADC conversion characteristics                                          | 92  |

| Figure 34. | Device marking for revision G LQFP80 and LQFP128 packages.              | 93  |

| Figure 35. | Device marking for revision G LFBGA144 packages                         | 93  |

| Figure 36. | Device marking for revision H LQFP80 and LQFP128 packages.              | 93  |

| Figure 37. | Device marking for revision H LFBGA144 packages                         | 93  |

| Figure 38. | Device marking for revision A LQFP80 and LQFP128 packages               |     |

| Figure 39. | Device marking for revision A LFBGA144 packages                         | 94  |

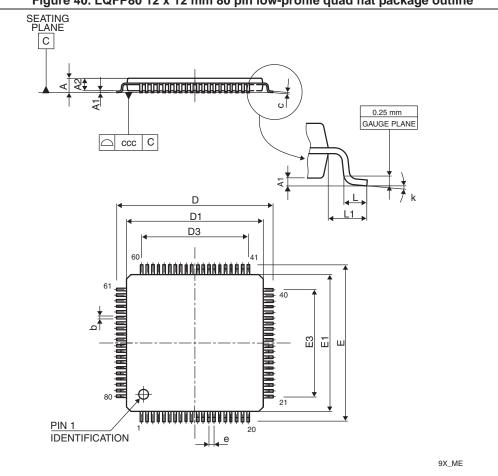

| Figure 40. | LQFP80 12 x 12 mm 80 pin low-profile quad flat package outline          | 95  |

| Figure 41. | LQFP80 - 80 pin, 12 x 12 mm low-profile quad flat package footprint     | 96  |

| Figure 42. | LQFP80 package top view                                                 |     |

| Figure 43. | LQFP128 14 x 14 mm 128 pin low-profile quad flat package outline        | 98  |

| Figure 44. | LQFP128 package top view                                                |     |

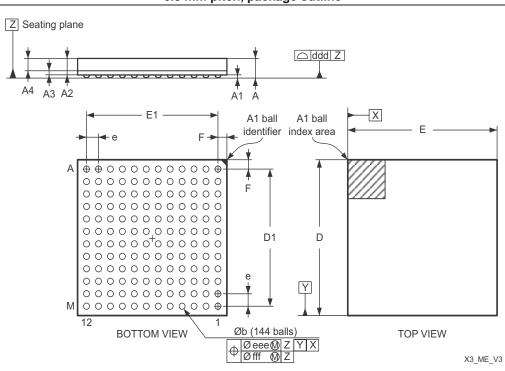

| Figure 45. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |     |

| -          | 0.8 mm pitch, package outline                                           | 101 |

| Figure 46. | LFBGA144 package top view                                               |     |

| Figure 47. | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                   | 103 |

## 3 Functional overview

## 3.1 System-in-a-package (SiP)

The STR91xFA is a SiP device, comprised of two stacked die. One die is the ARM966E-S CPU with peripheral interfaces and analog functions, and the other die is the burst Flash. The two die are connected to each other by a custom high-speed 32-bit burst memory interface and a serial JTAG test/programming interface.

## 3.2 Package choice

STR91xFA devices are available in 128-pin (14 x 14 mm) and 80-pin (12 x 12 mm) LQFP and LFBGA144 (10 x 10 mm) packages. Refer to *Table 2: Device summary on page 11* for a list of available peripherals for each of the package choices.

## 3.3 ARM966E-S CPU core

The ARM966E-S core inherently has separate instruction and data memory interfaces (Harvard architecture), allowing the CPU to simultaneously fetch an instruction, and read or write a data item through two Tightly-Coupled Memory (TCM) interfaces as shown in *Figure 1*. The result is streamlined CPU Load and Store operations and a significant reduction in cycle count per instruction. In addition to this, a 5-stage pipeline is used to increase the amount of operational parallelism, giving the most performance out of each clock cycle.

Ten DSP-enhanced instruction extensions are supported by this core, including single-cycle execution of 32x16 Multiply-Accumulate, saturating addition/subtraction, and count leading-zeros.

The ARM966E-S core is binary compatible with 32-bit ARM7 code and 16-bit Thumb<sup>®</sup> code.

## 3.4 Burst Flash memory interface

A burst Flash memory interface (*Figure 1*) has been integrated into the Instruction TCM (I-TCM) path of the ARM966E-S core. Also in this path is an 8-instruction Pre-Fetch Queue (PFQ) and a 15-entry Branch Cache (BC), enabling the ARM966E-S core to perform up to 96 MIPS while executing code directly from Flash memory. This architecture provides high performance levels without a costly instruction SRAM, instruction cache, or external SDRAM. Eliminating the instruction cache also means interrupt latency is reduced and code execution becomes more deterministic.

#### 3.4.1 Pre-fetch queue (PFQ)

As the CPU core accesses sequential instructions through the I-TCM, the PFQ always looks ahead and will pre-fetch instructions, taking advantage any idle bus cycles due to variable length instructions. The PFQ will fetch 32-bits at a time from the burst Flash memory at a rate of up to 96 MHz.

## 3.7 Non-volatile memories

There are two independent 32-bit wide burst Flash memories enabling true read-while-write operation. The Flash memories are single-voltage erase/program with 20 year minimum data retention and 100K minimum erase cycles. The primary Flash memory is much larger than the secondary Flash.

Both Flash memories are blank when devices are shipped from ST. The CPU can boot only from Flash memory (configurable selection of which Flash bank).

Flash memories are programmed half-word (16 bits) at a time, but are erased by sector or by full array.

#### 3.7.1 Primary Flash memory

Using the STR91xFA device configuration software tool and 3rd party Integrated Developer Environments, it is possible to specify that the primary Flash memory is the default memory from which the CPU boots at reset, or otherwise specify that the secondary Flash memory is the default boot memory. This choice of boot memory is non-volatile and stored in a location that can be programmed and changed only by JTAG In-System Programming. See *Section 6: Memory mapping*, for more detail.

The primary Flash memory has equal length 64K byte sectors. See *Table 3* for number of sectors per device type.

| Size of primary Flash | 256 Kbytes | 512 Kbytes | 1 Mbyte | 2 Mbytes |  |  |  |

|-----------------------|------------|------------|---------|----------|--|--|--|

| Number of sectors     | 4          | 8          | 16      | 32       |  |  |  |

| Size of each sector   | 64 K       | bytes      | 64 K    | bytes    |  |  |  |

Table 3. Sectoring of primary Flash memory

#### 3.7.2 Secondary Flash memory

The smaller of the two Flash memories can be used to implement a bootloader, capable of storing code to perform robust In-Application Programming (IAP) of the primary Flash memory. The CPU executes code from the secondary Flash, while updating code in the primary Flash memory. New code for the primary Flash memory can be downloaded over any of the interfaces on the STR91xFA (USB, Ethernet, CAN, UART, etc.)

Additionally, the secondary Flash memory may also be used to store small data sets by emulating EEPROM through firmware, eliminating the need for external EEPROM memories. This raises the data security level because passcodes and other sensitive information can be securely locked inside the STR91xFA device.

The secondary Flash memory is sectored as shown in *Table 4* according to device type.

Both the primary Flash memory and the secondary Flash memory can be programmed with code and/or data using the JTAG In-System Programming (ISP) channel, totally independent of the CPU. This is excellent for iterative code development and for manufacturing.

#### 3.10.5 Flash memory interface clock (FMICLK)

The FMICLK clock is an internal clock derived from RCLK, defaulting to RCLK frequency at power up. The clock can be optionally divided by 2. The FMICLK determines the bus bandwidth between the ARM core and the Flash memory. Typically, codes in the Flash memory can be fetched one word per FMICLK clock in burst mode. The maximum FMICLK frequency is 96 MHz.

#### 3.10.6 UART and SSP clock (BRCLK)

BRCLK is an internal clock derived from  $f_{MSTR}$  that is used to drive the two SSP peripherals and to generate the Baud rate for the three on-chip UART peripherals. The frequency can be optionally divided by 2.

#### 3.10.7 External memory interface bus clock (BCLK)

The BCLK is an internal clock that controls the EMI bus. All EMI bus signals are synchronized to the BCLK. The BCLK is derived from the HCLK and the frequency can be configured to be the same or half that of the HCLK. Refer to *Table 17 on page 66* for the maximum BCLK frequency ( $f_{BCLK}$ ). The BCLK clock is available on the LFBGA package as an output pin.

#### 3.10.8 USB interface clock

Special consideration regarding the USB interface: The clock to the USB interface must operate at 48 MHz and comes from one of three sources, selected under firmware control:

- CCU master clock output of 48 MHz.

- CCU master clock output of 96 MHz. An optional divided-by-two circuit is available to produce 48 MHz for the USB while the CPU system runs at 96MHz.

- STR91xFA pin P2.7. An external 48 MHz oscillator connected to pin P2.7 can directly source the USB while the CCU master clock can run at some frequency other than 48 or 96 MHz.

#### 3.10.9 Ethernet MAC clock

Special consideration regarding the Ethernet MAC: The external Ethernet PHY interface device requires it's own 25 MHz clock source. This clock can come from one of two sources:

- A 25 MHz clock signal coming from a dedicated output pin (P5.2) of the STR91xFA. In this case, the STR91xFA must use a 25 MHz signal on its main oscillator input in order to pass this 25 MHz clock back out to the PHY device through pin P5.2. The advantage here is that an inexpensive 25 MHz crystal may be used to source a clock to both the STR91xFA and the external PHY device.

- An external 25 MHz oscillator connected directly to the external PHY interface device. In this case, the STR91xFA can operate independent of 25 MHz.

#### 3.10.10 External RTC calibration clock

The RTC\_CLK can be enabled as an output on the JRTCK pin. The RTC\_CLK is used for RTC oscillator calibration. The RTC\_CLK is active in Sleep mode and can be used as a system wake up control clock.

#### 3.13.2 Supply voltage dropout

LVD circuitry will always cause a global reset if the CPU's  $V_{DD}$  source drops below it's fixed threshold of 1.4 V.

However, the LVD trigger threshold to cause a global reset for the I/O ring's  $V_{DDQ}$  source is set to one of two different levels, depending if  $V_{DDQ}$  will be operated in the range of 2.7 V to 3.3 V, or 3.0V to 3.6 V. If  $V_{DDQ}$  operation is at 2.7 V to 3.3 V, the LVD dropout trigger threshold is 2.4 V. If  $V_{DDQ}$  operation is 3.0 V and 3.6 V, the LVD threshold is 2.7 V. The choice of trigger level is made by STR91xFA device configuration software from STMicroelectronics or IDE from 3rd parties, and is programmed into the STR91xFA device along with other configurable items through the JTAG interface when the Flash memory is programmed.

CPU firmware may prevent some LVD resets if desired by writing a control register at runtime. Firmware may also disable the LVD completely for lowest-power operation when an external LVD device is being used.

#### 3.13.3 Watchdog timer

The STR91xFA has a 16-bit down-counter (not one of the four TIM timers) that can be used as a watchdog timer or as a general purpose free-running timer/counter. The clock source is the peripheral clock from the APB, and an 8-bit clock pre-scaler is available. When enabled by firmware as a watchdog, this timer will cause a system reset if firmware fails to periodically reload this timer before the terminal count of 0x0000 occurs, ensuring firmware sanity. The watchdog function is off by default after a reset and must be enabled by firmware.

#### 3.13.4 External RESET\_INn pin

This input signal is active-low with hystereses ( $V_{HYS}$ ). Other open-drain, active-low system reset signals on the circuit board (such as closure to ground from a push-button) may be connected directly to the RESET\_INn pin, but an external pull-up resistor to  $V_{DDQ}$  must be present as there is no internal pullup on the RESET\_INn pin.

A valid active-low input signal of  $t_{RINMIN}$  duration on the RESET\_INn pin will cause a system reset within the STR91xFA. There is also a RESET\_OUTn pin on the STR91xFA that can drive other system components on the circuit board. RESET\_OUTn is active-low and has the same timing of the Power-On-Reset (POR) shown next,  $t_{POR}$ .

#### 3.13.5 Power-up

The LVD circuitry will always generate a global reset when the STR91xFA powers up, meaning internal reset is active until  $V_{DDQ}$  and  $V_{DD}$  are both above the LVD thresholds. This POR condition has a duration of  $t_{POR}$ , after which the CPU will fetch its first instruction from address 0x0000.0000 in Flash memory. It is not possible for the CPU to boot from any other source other than Flash memory.

#### 3.13.6 JTAG debug command

When the STR91xFA is in JTAG debug mode, an external device which controls the JTAG interface can command a system reset to the STR91xFA over the JTAG channel.

#### 3.13.7 Tamper detection

On 128-pin and 144-ball STR91xFA devices only, there is a tamper detect input pin, TAMPER\_IN, used to detect and record the time of a tamper event on the end product such as malicious opening of an enclosure, unwanted opening of a panel, etc. The activation mode of the tamper pin detects when a signal on the tamper input pin is driven from low-to-high, or high-to-low depending on firmware configuration. Once a tamper event occurs, the RTC time (millisecond resolution) and the date are recorded in the RTC unit. Simultaneously, the SRAM standby voltage source will be cut off to invalidate all SRAM contents. Tamper detection control and status logic are part of the RTC unit.

## 3.14 Real-time clock (RTC)

The RTC combines the functions of a complete time-of-day clock (millisecond resolution) with an alarm programmable up to one month, a 9999-year calender with leap-year support, periodic interrupt generation from 1 to 512 Hz, tamper detection (described in *Section 3.13.7*), and an optional clock calibration output on the JRTCK pin. The time is in 24 hour mode, and time/calendar values are stored in binary-coded decimal format.

The RTC also provides a self-isolation mode that is automatically activated during power down. This feature allows the RTC to continue operation when  $V_{DDQ}$  and  $V_{DD}$  are absent, as long as an alternate power source, such as a battery, is connected to the VBATT input pin. The current drawn by the RTC unit on the VBATT pin is very low in this standby mode,  $I_{RTC\_STBY}$ .

## 3.15 JTAG interface

An IEEE-1149.1 JTAG interface on the STR91xFA provides In-System-Programming (ISP) of all memory, boundary scan testing of pins, and the capability to debug the CPU.

STR91xFA devices are shipped from ST with blank Flash memories. The CPU can only boot from Flash memory (selection of which Flash bank is programmable). Firmware must be initially programmed through JTAG into one of these Flash memories before the STR91xFA is used.

Six pins are used on this JTAG serial interface. The five signals JTDI, JTDO, JTMS, JTCK, and JTRSTn are all standard JTAG signals complying with the IEEE-1149.1 specification. The sixth signal, JRTCK (Return TCK), is an output from the STR91xFA and it is used to pace the JTCK clock signal coming in from the external JTAG test equipment for debugging. The frequency of the JTCK clock signal coming from the STR91xFA and is input to the at least 10 times less than the ARM966E-S CPU core operating frequency (f<sub>CPUCLK</sub>). To ensure this, the signal JRTCK is output from the STR91xFA and is input to the external JTAG test equipment to hold off transitions of JTCK until the CPU core is ready, meaning that the JTAG equipment cannot send the next rising edge of JTCK until the equipment must be able to interpret the signal JRTCK and perform this adaptive clocking function. If it is known that the CPU clock will always be at least ten times faster than the incoming JTCK clock signal, then the JRTCK signal is not needed.

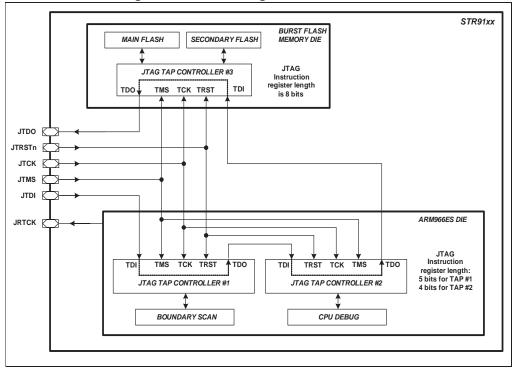

The two die inside the STR91xFA (CPU die and Flash memory die) are internally daisychained on the JTAG bus, see *Figure 3 on page 28*. The CPU die has two JTAG Test Access Ports (TAPs), one for boundary scan functions and one for ARM CPU debug. The Flash memory die has one TAP for program/erase of non-volatile memory. Because these

three TAPs are daisy-chained, only one TAP will converse on the JTAG bus at any given time while the other two TAPs are in BYPASS mode. The TAP positioning order within this JTAG chain is the boundary scan TAP first, followed by the ARM debug TAP, followed by the Flash TAP. All three TAP controllers are reset simultaneously by one of two methods:

- A chip-level global reset, caused only by a Power-On-Reset (POR) or a Low Voltage Detect (LVD).

- A reset command issued by the external JTAG test equipment. This can be the assertion of the JTAG JTRSTn input pin on the STR91xFA or a JTAG reset command shifted into the STR91xFA serially.

This means that chip-level system resets from watchdog time-out or the assertion of RESET\_INn pin do not affect the operation of any JTAG TAP controller. Only global resets effect the TAPs.

Figure 3. JTAG chaining inside the STR91xFA

#### 3.15.1 In-system-programming

The JTAG interface is used to program or erase all memory areas of the STR91xFA device. The pin RESET\_INn must be asserted during ISP to prevent the CPU from fetching invalid instructions while the Flash memories are being programmed.

Note that the 32 bytes of OTP memory locations cannot be erased by any means once programmed by JTAG ISP or the CPU.

## 3.20 UART interfaces with DMA

The STR91xFA supports three independent UART serial interfaces, designated UART0, UART1, and UART2. Each interface is very similar to the industry-standard 16C550 UART device. All three UART channels support IrDA encoding/decoding, requiring only an external LED transceiver to pins UARTx\_RX and UARTx\_Tx for communication. One UART channel (UART0) supports full modem control signals.

UART interfaces include the following features:

- Maximum baud rate of 1.5 Mbps

- Separate FIFOs for transmit and receive, each 16 deep, each FIFO can be disabled by firmware if desired

- Programmable FIFO trigger levels between 1/8 and 7/8

- Programmable baud rate generator based on CCU master clock, or CCU master clock divided by two

- Programmable serial data lengths of 5, 6, 7, or 8 bits with start bit and 1 or 2 stop bits

- Programmable selection of even, odd, or no-parity bit generation and detection

- False start-bit detection

- Line break generation and detection

- Support of IrDA SIR ENDEC functions for data rates of up to 115.2K bps

- IrDA bit duration selection of 3/16 or low-power (1.14 to 2.23 µsec)

- Channel UART0 supports modem control functions CTS, DCD, DSR, RTS, DTR, and RI

For your reference, only two standard 16550 UART features are not supported, 1.5 stop bits and independent receive clock.

#### 3.20.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service channels UART0 and UART1 for fast and direct transfers between the UART bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that UART FIFOs are enabled.

## 3.21 I<sup>2</sup>C interfaces

The STR91xFA supports two independent I2C serial interfaces, designated I2C0, and I2C1. Each interface allows direct connection to an I2C bus as either a bus master or bus slave device (firmware configurable). I2C is a two-wire communication channel, having a bidirectional data signal and a single-directional clock signal based on open-drain line drivers, requiring external pull-up resistors.

Byte-wide data is transferred between a Master device and a Slave device on two wires. More than one bus Master is allowed, but only one Master may control the bus at any given time. Data is not lost when another Master requests the use of a busy bus because I2C supports collision detection and arbitration. More than one Slave device may be present on the bus, each having a unique address. The bus Master initiates all data movement and generates the clock that permits the transfer. Once a transfer is initiated by the Master, any device that is addressed is considered a Slave. Automatic clock synchronization allows I2C devices with different bit rates to communicate on the same physical bus.

DocID13495 Rev 7

## 5.1 LFBGA144 ball connections

- In *Table 7* balls labelled NC are no connect balls. These NC balls are reserved for future devices and should NOT be connected to ground or any other signal. There are total of 9 NC (no connection) balls.

- Balls H1 and G4 are assigned as EMI bus write signals (EMI\_BWR\_WRLn and EMI\_WRHn). These two balls can also be configured by the user as EMI low or high byte select signals (EMI\_LBn and EMI\_UBn).

- The PLLGND (B8) and PLLVDDQ (C9) balls can be connected to VSSQ and VDDQ.

|    | Α              | В       | С                    | D                           | Е             | F    | G                             | н                     | J           | К                             | L                              | М            |

|----|----------------|---------|----------------------|-----------------------------|---------------|------|-------------------------------|-----------------------|-------------|-------------------------------|--------------------------------|--------------|

| 1  | P4.2           | P7.2    | NC                   | P7.0                        | VDDQ          | P7.3 | P7.4                          | EMI_WRHn<br>(EMI_UBn) | VDDQ        | PHYCLK<br>P5.2 <sup>(1)</sup> | P8.0                           | P2.2         |

| 2  | AVREF          | P4.1    | P4.0                 | P7.1                        | P2.0          | NC   | P6.2                          | P5.3                  | P8.2        | P8.3                          | VSSQ                           | P8.6         |

| 3  | AVDD           | P4.3    | AVSS                 | NC                          | P2.1          | VSS  | P6.3                          | P8.1                  | P6.1        | P2.3                          | P8.4                           | VBATT        |

| 4  | P4.6           | P4.5    | P4.4                 | VSSQ                        | P5.0          | VDD  | EMI_BWR_<br>WRLn<br>(EMI_LBn) | P6.0                  | P8.5        | VSSQ                          | P2.4                           | X2_<br>RTC   |

| 5  | P7.7           | VDDQ    | VSSQ                 | P4.7                        | P7.5          | NC   | VSSQ                          | VSS                   | P2.5        | P8.7                          | VDDQ                           | X1_<br>RTC   |

| 6  | JTMS           | JTDO    | JTDI                 | P1.7                        | P7.6          | P5.1 | P2.6                          | P9.4                  | P9.3        | P9.2                          | VDD                            | P9.0         |

| 7  | P1.5           | P1.4    | NC                   | VDD                         | VSS           | P1.6 | P6.5                          | VDDQ                  | VSSQ        | P3.0                          | USBCLK<br>_P2.7 <sup>(2)</sup> | P9.1         |

| 8  | VSSQ           | PLLVSSQ | P1.3                 | JRSTn                       | JTCK          | VSSQ | P6.4                          | EMI_BAAn              | P3.3        | EMI_<br>WAITn                 | P9.5                           | EMI_<br>BCLK |

| 9  | RESET_<br>OUTn | P1.2    | PLLVDDQ              | VDDQ                        | P6.6          | VDDQ | NC                            | P5.6                  | EMI_<br>RDn | P9.7                          | P3.4                           | P9.6         |

| 10 | X1_CPU         | P1.0    | P1.1                 | USBDN <sup>(3)</sup>        | TAMPER_<br>IN | NC   | VSS                           | P0.4                  | EMI_<br>ALE | P0.1                          | P3.5                           | P3.1         |

| 11 | X2_CPU         | JRTCK   | USBDP <sup>(2)</sup> | MII_<br>MDIO <sup>(3)</sup> | P0.6          | P0.5 | VDD                           | P5.5                  | P0.2        | P3.7                          | P0.0                           | P3.2         |

| 12 | EMI_<br>WEn    | P0.7    | RESET_<br>INn        | P6.7                        | NC            | NC   | P5.7                          | P0.3                  | P5.4        | VDDQ                          | VSSQ                           | P3.6         |

| Table 7. STR | 891x LFBGA144 ball | connections |

|--------------|--------------------|-------------|

|--------------|--------------------|-------------|

1. No PHYCLK function on STR910FAW devices.

2. No USBCLK function on STR910FAW devices.

3. NU (Not Used) on STR910FAW devices. D10 is not connected, C11 must be pulled up by a 1.5 kOhm resistor to VDDQ.

|        | Package Alternate functions |          |             |             |                                     |                              |                      |                       |                       |                       |

|--------|-----------------------------|----------|-------------|-------------|-------------------------------------|------------------------------|----------------------|-----------------------|-----------------------|-----------------------|

|        | acro                        | aye      |             | be          |                                     |                              |                      | Allemale              | Turictions            |                       |

| LQFP80 | LQFP128                     | LFBGA144 | Pin<br>name | Signal type | Default pin<br>function             | Default<br>input<br>function | Alternate<br>input 1 | Alternate<br>output 1 | Alternate<br>output 2 | Alternate<br>output 3 |

| -      | 8                           | L2       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| 16     | 24                          | K4       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| 35     | 56                          | C5       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| -      | -                           | D4       | VSSQ        | G           | Digital Ground                      |                              |                      |                       |                       |                       |

| 45     | 72                          | G5       | VSSQ        | G           | for                                 |                              |                      | N/A                   |                       |                       |

| 55     | 87                          | J7       | VSSQ        | G           | !/O and USB                         |                              |                      |                       |                       |                       |

| 25     | 40                          | A8       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| 66     | 105                         | F8       | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| 75     | 121                         | L12      | VSSQ        | G           |                                     |                              |                      |                       |                       |                       |

| 11     | 17                          | F4       | VDD         | V           |                                     |                              |                      |                       |                       |                       |

| 31     | 49                          | D7       | VDD         | V           | V Source for                        |                              |                      |                       |                       |                       |

| 50     | 81                          | L6       | VDD         | V           | CPU.<br>1.65 V - 2.0 V              |                              |                      | N/A                   |                       |                       |

| 70     | 112                         | G11      | VDD         | V           |                                     |                              |                      |                       |                       |                       |

| 10     | 16                          | F3       | VSS         | G           |                                     |                              |                      |                       |                       |                       |

| 30     | 48                          | H5       | VSS         | G           | Digital Ground                      |                              |                      |                       |                       |                       |

| 51     | 82                          | G10      | VSS         | G           | for CPU                             |                              |                      | N/A                   |                       |                       |

| 71     | 113                         | E7       | VSS         | G           |                                     |                              |                      |                       |                       |                       |

| -      | -                           | C9       | PLLV<br>DDQ | v           | V Source for<br>PLL<br>2.7 to 3.6 V |                              |                      | N/A                   |                       |                       |

| -      | -                           | B8       | PLLV<br>SSQ | G           | Digital Ground<br>for PLL           |                              |                      |                       |                       |                       |

Table 8. Device pin description (continued)

| Symbol                                | Ratings                                                              | Maximum<br>value | Unit |

|---------------------------------------|----------------------------------------------------------------------|------------------|------|

| I <sub>VDD_IO</sub> <sup>(1)</sup>    | Total current into $V_{DD_{IO}}$ power lines (source) <sup>(2)</sup> | 200              |      |

| I <sub>VSS_IO</sub> <sup>(1)</sup>    | Total current out of $V_{SS}$ ground lines (sink) $^{(2)}$           | 200              | mA   |

| I <sub>IO</sub>                       | Output current sunk by any I/O and control pin                       | 25               | ШA   |

|                                       | Output current source by any I/Os and control pin                    | - 25             |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup>  | Injected current on any pin during overload condition <sup>(4)</sup> | ± 5              |      |

| ΣΙ <sub>INJ(PIN)</sub> <sup>(3)</sup> | Absolute sum of all input currents during overload condition (4)     | ± 25             | mA   |

| Table | 10. | Current  | characteristics |

|-------|-----|----------|-----------------|

| TUDIC |     | Guillent | onaraotoristios |

1. The user can use GPIOs to source or sink current. In this case, the user must ensure that these absolute max. values are not exceeded (taking into account the RUN power consumption).

2. All 3.3 V or 5.0 V power (V<sub>DD IO</sub>, V<sub>DDA ADC</sub>, V<sub>DDA PLL</sub>) and ground (V<sub>SS-IO</sub>, V<sub>SSA\_ADC</sub>, V<sub>DDA ADC</sub>) pins must always be connected to the external 3.3 V or 5.0V supply.

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

4. When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with ΣI<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

#### Figure 16. Typical application with an external clock source

#### 7.7.3 RTC clock generated from a crystal/ceramic resonator

The RTC (Real-Time Clock) can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results obtained with typical external components specified in *Table 20 & Table 21*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Note: For CL1 and CL2 it is recommended to use high-quality ceramic capacitors in the 5 pF to 16 pF range, selected to match the requirements of the crystal or resonator. CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2.

Load capacitance CL has the following formula:

$CL = CL1 \times CL2 / (CL1 + CL2) + Cstray$

where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

Caution: Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF, and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

Conditions:  $V_{DDO}$  = 2.7 - 3.6 V,  $V_{DD}$  = 1.65 - 2 V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Symbol                  | Parameter                                  | Test                   | Va                            | Unit |     |          |

|-------------------------|--------------------------------------------|------------------------|-------------------------------|------|-----|----------|

| Symbol                  | Farameter                                  | conditions             | Min                           | Тур  | Max | Unit     |

| R <sub>F</sub>          | External feedback resistor                 |                        |                               | 22   |     | MΩ       |

| V <sub>START(RTC)</sub> | Oscillator start voltage                   |                        | $V_{DD_LVD^+}$ <sup>(1)</sup> |      |     | V        |

| g <sub>M</sub>          | Oscillator transconductance <sup>(2)</sup> | Start-up               | 1.8                           |      |     | µA/Volts |

| t <sub>STUP(RTC)</sub>  | Oscillator Start-up Time <sup>(2)</sup>    | V <sub>DD</sub> stable |                               |      | 1   | S        |

1. Refer to Table 14 for min. value of V<sub>DD LVD+</sub>

2. Data based on bench measurements, not tested in production.

#### 7.9.5 Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin) and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

#### 7.9.6 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### 7.9.7 Electrical sensitivity

#### Table 30. Static latch-up data

| Symbol | Parameter             | Conditions                                    | Class <sup>(1)</sup> |

|--------|-----------------------|-----------------------------------------------|----------------------|

| LU     | Static latch-up class | $T_A = +25 \ ^{\circ}C$ conforming to JESD78A | II class A           |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

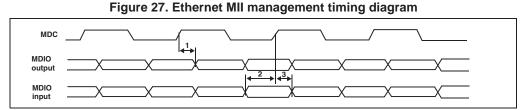

#### Ethernet MII management timings

Table 42. Ethernet MII management timing table

| Symbol | Parameter                                | Symbol                 | Va    | Unit |      |  |

|--------|------------------------------------------|------------------------|-------|------|------|--|

| Symbol | Falameter                                | Symbol                 | Min   | Мах  | Onit |  |

| 1      | MDIO delay from rising edge of MDC       | t <sub>c</sub> (MDIO)  |       | 2.83 | ns   |  |

| 2      | MDIO setup time to rising edge of MDC    | T <sub>su</sub> (MDIO) | 2.70  |      | ns   |  |

| 3      | 3 MDIO hold time from rising edge of MDC |                        | -2.03 |      | ns   |  |

#### Ethernet MII transmit timings

## 9 Package mechanical data

Figure 40. LQFP80 12 x 12 mm 80 pin low-profile quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

|      | Dimensions |             |        |                       |        |        |  |  |  |  |  |

|------|------------|-------------|--------|-----------------------|--------|--------|--|--|--|--|--|

| Ref. |            | Millimeters |        | Inches <sup>(1)</sup> |        |        |  |  |  |  |  |

|      | Min.       | Тур.        | Max.   | Min.                  | Тур.   | Max.   |  |  |  |  |  |

| A    | -          | -           | 1.600  | -                     | -      | 0.0630 |  |  |  |  |  |

| A1   | 0.050      | -           | 0.150  | 0.0020                | -      | 0.0059 |  |  |  |  |  |

| A2   | 1.350      | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |  |  |  |

| b    | 0.130      | 0.180       | 0.230  | 0.0051                | 0.0071 | 0.0091 |  |  |  |  |  |

| с    | 0.090      | -           | 0.200  | 0.0035                | -      | 0.0079 |  |  |  |  |  |

| D    | 15.800     | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |  |  |

| D1   | 13.800     | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |  |  |  |

| D3   | -          | 12.400      | -      | -                     | 0.4882 | -      |  |  |  |  |  |

| E    | 15.800     | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |  |  |  |

| E1   | 13.800     | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |  |  |  |

| E3   | -          | 12.400      | -      | -                     | 0.4882 | -      |  |  |  |  |  |

| е    | -          | 0.400       | -      | -                     | 0.0157 | -      |  |  |  |  |  |

| L    | 0.450      | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |  |  |  |

| L1   | -          | 1.000       | -      | -                     | 0.0394 | -      |  |  |  |  |  |

| k    | 0°         | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |  |  |  |  |  |

| ссс  | -          | -           | 0.080  | -                     | -      | 0.0031 |  |  |  |  |  |

# Table 51. LQFP128 - 128-pin, 14 x 14 mm low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 45. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package outline

#### **Ordering information** 10

| Table 5                          | 54. Ordering | g info | orma | tion  | sch   | eme |   |   |   |   |   |

|----------------------------------|--------------|--------|------|-------|-------|-----|---|---|---|---|---|

| Example:<br>Family               | STR9         | 1      | 2    | F<br> | A<br> | W   | 4 | 4 | × | 6 | Т |

| ARM9 microcontroller family      |              |        |      |       |       |     |   |   |   |   |   |

| Series                           |              |        |      |       |       |     |   |   |   |   |   |

| 1 = STR9 series 1                |              |        |      |       |       |     |   |   |   |   |   |

| Feature set                      |              |        |      |       |       |     |   |   |   |   |   |

| 0 = CAN, UART, IrDA, I2C, SSP    |              |        |      |       |       |     |   |   |   |   |   |

| 1 = USB, CAN, UART, IrDA, I2C, S | SSP          |        |      |       |       |     |   |   |   |   |   |

| 2 = USB, CAN, UART, IrDA, I2C, S | SSP, ETHERI  | NET    |      |       |       |     |   |   |   |   |   |

| Memory type                      |              |        |      |       |       |     |   |   |   |   |   |

| F = Flash                        |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| Revision at product level        |              |        |      |       |       |     |   |   |   |   |   |

| A = Revison A                    |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| No. of pins                      |              |        |      |       |       |     |   |   |   |   |   |

| M = 80                           |              |        |      |       |       |     |   |   |   |   |   |

| W = 128                          |              |        |      |       |       |     |   |   |   |   |   |

| Z = 144                          |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

| SRAM size                        |              |        |      |       |       |     |   |   |   |   |   |

| 3 = 64 Kbytes                    |              |        |      |       |       |     |   |   |   |   |   |

| 4 = 96 Kbytes                    |              |        |      |       |       |     |   |   |   |   |   |

| Primary memory size              |              |        |      |       |       |     |   |   |   |   |   |

| 2 = 256 Kbytes 6= 1024 Kbytes    |              |        |      |       |       |     |   |   |   |   |   |

| 4 = 512 Kbytes 7= 2048 Kbytes    |              |        |      |       |       |     |   |   |   |   |   |

| Package                          |              |        |      |       |       |     |   |   |   |   |   |

| X = plastic LQFP                 |              |        |      |       |       |     |   |   |   |   |   |

| H = LFBGA                        |              |        |      |       |       |     |   |   |   |   |   |

| Temperature range                |              |        |      |       |       |     |   |   |   |   |   |

| 6 = -40 to 85 °C                 |              |        |      |       |       |     |   |   |   |   |   |

| Shipping option                  |              |        |      |       |       |     |   |   |   |   |   |

| T = Tape and reel packing        |              |        |      |       |       |     |   |   |   |   |   |

|                                  |              |        |      |       |       |     |   |   |   |   |   |

1. For a list of available options (e.g. speed, package) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

# 11 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09-May-2007 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26-Nov-2007 | 2        | Updated Standby current in Table 15: Supply current<br>characteristics on page 64<br>Added Section 7.1: Parameter conditions on page 58<br>Added Section 7.7.2: X1_CPU external clock source on page 67<br>Updated Section 7.11: External memory bus timings on page 76<br>Added Figure 14: LVD reset delay case 3 on page 63<br>Added Table 48 and Table 49 in ADC characteristics section<br>Added min/max values for E, D, E1, D1 in Figure 43 on page 98                                                                                                                                                                                                                                                                                                        |

| 14-May-2008 | 3        | Added 1MB and 2M devices, creating merged datasheet from<br>seperate STR91xFAx32, 42, 44, 46 and 47 devices.<br>Added STR912FAW32 to Table 1: Device summary on page 1<br>Added paragraph on voltage supply shutdown in Section 3.12 on<br>page 24<br>Removed DMA feature for I2C in Section 3.21 on page 33<br>Updated Sleep mode current in Table 10: Current characteristics<br>on page 60<br>Added Table 16: Typical current consumption at 25 °C on page 65<br>Updated operating conditions for V <sub>DD</sub> and f <sub>CPUCLK</sub> in Section 7.3<br>on page 61 and Section 7.7: Clock and timing characteristics on<br>page 66<br>Changed SPI master t <sub>SU</sub> and t <sub>H to</sub> TBD in Table 46: SPI electrical<br>characteristics on page 88 |

| 17-Jul-2008 | 4        | Updated Section 3.10.6: UART and SSP clock (BRCLK) on<br>page 22<br>Updated Table 11: Operating conditions on page 61<br>Updated I <sub>SLEEP(IDDQ)</sub> in Table 15: Supply current characteristics<br>on page 64<br>Updated Table 17: Internal clock frequencies on page 66<br>Updated Table 31: I/O characteristics on page 75                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22-Dec-2008 | 5        | Updated Section 7.7.3 on page 68. Small text changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Table 55. Document revision history