Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | ARM9®                                                                              |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 96MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                         |

| Number of I/O              | 80                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 96K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                         |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 128-LQFP                                                                           |

| Supplier Device Package    | -                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str911faw44x6              |

| 9  | Package mechanical data     |    |  |  |  |  |  |

|----|-----------------------------|----|--|--|--|--|--|

|    | 9.1 ECOPACK 1               | 04 |  |  |  |  |  |

|    | 9.2 Thermal characteristics | 04 |  |  |  |  |  |

| 10 | Ordering information        | 05 |  |  |  |  |  |

| 11 | Revision history            | 06 |  |  |  |  |  |

STR91xFAxxx List of figures

# **List of figures**

| Figure 1.                | STR91xFA block diagram                                                  |     |

|--------------------------|-------------------------------------------------------------------------|-----|

| Figure 2.                | Clock control                                                           | 21  |

| Figure 3.                | JTAG chaining inside the STR91xFA                                       | 28  |

| Figure 4.                | EMI 16-bit multiplexed connection example                               | 40  |

| Figure 5.                | EMI 8-bit multiplexed connection example                                | 40  |

| Figure 6.                | EMI 8-bit non-multiplexed connection example                            | 41  |

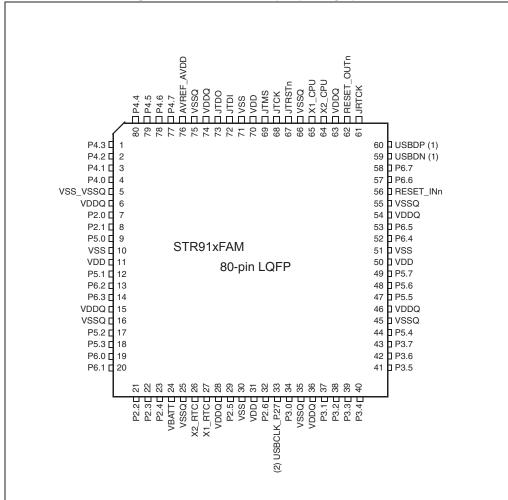

| Figure 7.                | STR91xFAM 80-pin package pinout                                         |     |

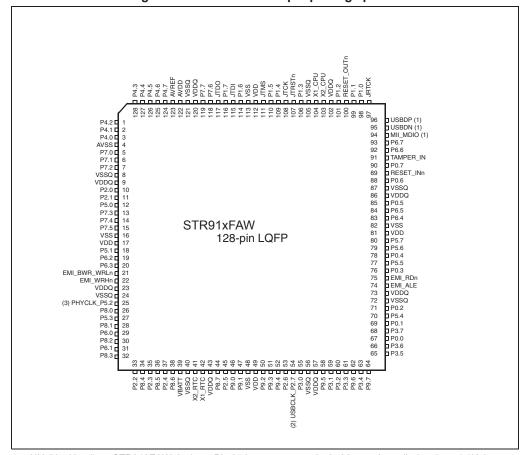

| Figure 8.                | STR91xFAW 128-pin package pinout                                        |     |

| Figure 9.                | STR91xFA memory map                                                     |     |

| Figure 10.               | Pin loading conditions                                                  |     |

| Figure 11.               | Pin input voltage                                                       |     |

| Figure 12.               | LVD reset delay case 1                                                  |     |

| Figure 13.               | LVD reset delay case 2                                                  |     |

| Figure 14.               | LVD reset delay case 3                                                  |     |

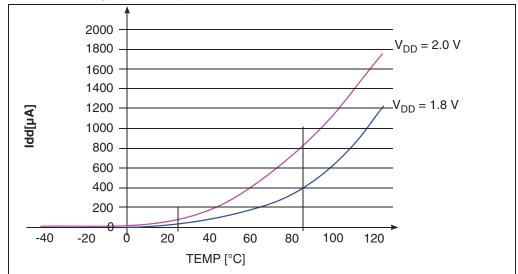

| Figure 15.               | Sleep mode current vs temperature with LVD on                           |     |

| Figure 16.               | Typical application with an external clock source                       |     |

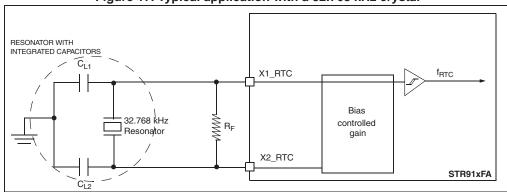

| Figure 17.               | Typical application with a 32.768 kHz crystal                           |     |

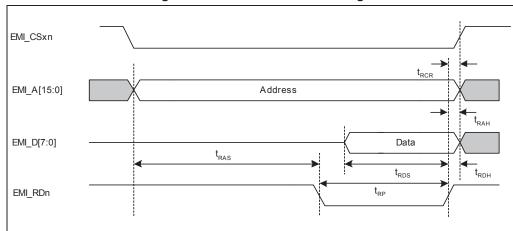

| Figure 18.               | Non-mux write timings                                                   |     |

| Figure 19.               | Non-mux bus read timings                                                |     |

| Figure 20.               | Mux write diagram                                                       |     |

| Figure 21.               | Mux read diagram                                                        |     |

| Figure 22.               | Page mode read diagram                                                  |     |

| Figure 23.               | Sync burst write diagram                                                |     |

| Figure 24.               | Sync burst read diagram.                                                |     |

| Figure 25.               | MII_RX_CLK and MII_TX_CLK timing diagram                                |     |

| Figure 26.               | MDC timing diagram                                                      |     |

| Figure 27.               | Ethernet MII management timing diagram                                  |     |

| Figure 28.               | Ethernet MII transmit timing diagram                                    |     |

| Figure 29.               | Ethernet MII receive timing diagram                                     |     |

| Figure 30.               | SPI slave timing diagram with CPHA = 0                                  |     |

| Figure 31.               | SPI slave timing diagram with CPHA = 1                                  |     |

| Figure 31.               | SPI master timing diagram                                               |     |

| Figure 32.               | ADC conversion characteristics                                          |     |

| Figure 34.               | Device marking for revision G LQFP80 and LQFP128 packages.              |     |

| Figure 35.               | Device marking for revision G LGI F 60 and LGI F 126 packages           |     |

| -                        | Device marking for revision H LQFP80 and LQFP128 packages               |     |

| Figure 36.<br>Figure 37. |                                                                         |     |

| •                        | Device marking for revision H LFBGA144 packages                         |     |

| Figure 38.               | Device marking for revision A LQFP80 and LQFP128 packages               |     |

| Figure 39.               | Device marking for revision A LFBGA144 packages                         |     |

| Figure 40.               | LQFP80 12 x 12 mm 80 pin low-profile quad flat package outline          |     |

| Figure 41.               | LQFP80 - 80 pin, 12 x 12 mm low-profile quad flat package footprint     |     |

| Figure 42.               | LQFP80 package top view                                                 |     |

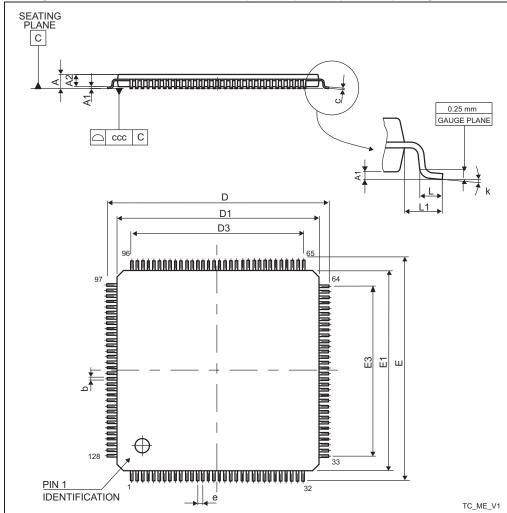

| Figure 43.               | LQFP128 14 x 14 mm 128 pin low-profile quad flat package outline        |     |

| Figure 44.               | LQFP128 package top view                                                | 100 |

| Figure 45.               | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, | 404 |

| E: 40                    | 0.8 mm pitch, package outline                                           |     |

| Figure 46.               | LFBGA144 package top view                                               |     |

| Figure 47.               | Recommended PCB design rules (0.80/0.75 mm pitch BGA)                   | 103 |

Functional overview STR91xFAxxx

### 3.10.5 Flash memory interface clock (FMICLK)

The FMICLK clock is an internal clock derived from RCLK, defaulting to RCLK frequency at power up. The clock can be optionally divided by 2. The FMICLK determines the bus bandwidth between the ARM core and the Flash memory. Typically, codes in the Flash memory can be fetched one word per FMICLK clock in burst mode. The maximum FMICLK frequency is 96 MHz.

#### 3.10.6 UART and SSP clock (BRCLK)

BRCLK is an internal clock derived from  $f_{MSTR}$  that is used to drive the two SSP peripherals and to generate the Baud rate for the three on-chip UART peripherals. The frequency can be optionally divided by 2.

# 3.10.7 External memory interface bus clock (BCLK)

The BCLK is an internal clock that controls the EMI bus. All EMI bus signals are synchronized to the BCLK. The BCLK is derived from the HCLK and the frequency can be configured to be the same or half that of the HCLK. Refer to *Table 17 on page 66* for the maximum BCLK frequency (f<sub>BCLK</sub>). The BCLK clock is available on the LFBGA package as an output pin.

#### 3.10.8 USB interface clock

Special consideration regarding the USB interface: The clock to the USB interface must operate at 48 MHz and comes from one of three sources, selected under firmware control:

- CCU master clock output of 48 MHz.

- CCU master clock output of 96 MHz. An optional divided-by-two circuit is available to produce 48 MHz for the USB while the CPU system runs at 96MHz.

- STR91xFA pin P2.7. An external 48 MHz oscillator connected to pin P2.7 can directly source the USB while the CCU master clock can run at some frequency other than 48 or 96 MHz.

#### 3.10.9 Ethernet MAC clock

Special consideration regarding the Ethernet MAC: The external Ethernet PHY interface device requires it's own 25 MHz clock source. This clock can come from one of two sources:

- A 25 MHz clock signal coming from a dedicated output pin (P5.2) of the STR91xFA. In

this case, the STR91xFA must use a 25 MHz signal on its main oscillator input in order

to pass this 25 MHz clock back out to the PHY device through pin P5.2. The advantage

here is that an inexpensive 25 MHz crystal may be used to source a clock to both the

STR91xFA and the external PHY device.

- An external 25 MHz oscillator connected directly to the external PHY interface device. In this case, the STR91xFA can operate independent of 25 MHz.

#### 3.10.10 External RTC calibration clock

The RTC\_CLK can be enabled as an output on the JRTCK pin. The RTC\_CLK is used for RTC oscillator calibration. The RTC\_CLK is active in Sleep mode and can be used as a system wake up control clock.

47/

STR91xFAxxx Functional overview

#### 3.10.11 Operation example

As an example of CCU operation, a 25 MHz crystal can be connected to the main oscillator input on pins X1\_CPU and X2\_CPU, a 32.768 kHz crystal connected to pins X1\_RTC and X2\_RTC, and the clock input of an external Ethernet PHY device is connected to STR91xFA output pin P5.2. In this case, the CCU can run the CPU at 96 MHz from PLL, the USB interface at 48 MHz, and the Ethernet interface at 25 MHz. The RTC is always running in the background at 32.768 kHz, and the CPU can go to very low power mode dynamically by running from 32.768 kHz and shutting off peripheral clocks and the PLL as needed.

# 3.11 Flexible power management

The STR91xFA offers configurable and flexible power management control that allows the user to choose the best power option to fit the application. Power consumption can be dynamically managed by firmware and hardware to match the system's requirements. Power management is provided via clock control to the CPU and individual peripherals.

Clocks to the CPU and peripherals can be individually divided and gated off as needed. In addition to individual clock divisors, the CCU master clock source going to the CPU, AHB, APB, EMI, and FMI can be divided dynamically by as much as 1024 for low power operation. Additionally, the CCU may switch its input to the 32.768 kHz RTC clock at any time for low power.

The STR91xFA supports the following three global power control modes:

- Run Mode: All clocks are on with option to gate individual clocks off via clock mask registers.

- Idle Mode: CPU and FMI clocks are off until an interrupt, reset, or wake-up occurs.

Pre-configured clock mask registers selectively allow individual peripheral clocks to continue run during Idle Mode.

- Sleep Mode: All clocks off except RTC clock. Wake up unit remains powered, PLL is forced off.

A special mode is used when JTAG debug is active which never gates off any clocks even if the CPU enters Idle or Sleep mode.

#### 3.11.1 Run mode

This is the default mode after any reset occurs. Firmware can gate off or scale any individual clock. Also available is a special Interrupt Mode which allows the CPU to automatically run full speed during an interrupt service and return back to the selected CPU clock divisor rate when the interrupt has been serviced. The advantage here is that the CPU can run at a very low frequency to conserve power until a periodic wake-up event or an asynchronous interrupt occurs at which time the CPU runs full speed immediately.

Functional overview STR91xFAxxx

#### 3.11.2 Idle mode

In this mode the CPU suspends code execution and the CPU and FMI clocks are turned off immediately after firmware sets the Idle Bit. Various peripherals continue to run based on the settings of the mask registers that exist just prior to entering Idle Mode. There are 3 ways to exit Idle Mode and return to Run Mode:

- Any reset (external reset pin, watchdog, low-voltage, power-up, JTAG debug command)

- Any interrupt (external, internal peripheral, RTC alarm or interval)

- Input from wake-up unit on GPIO pins

Note: It is possible to remain in Idle Mode for the majority of the time and the RTC can be programmed to periodically wake up to perform a brief task or check status.

#### 3.11.3 Sleep mode

In this mode all clock circuits except the RTC are turned off and main oscillator input pins X1\_CPU and X2\_CPU are disabled. The RTC clock is required for the CPU to exit Sleep Mode. The entire chip is quiescent (except for RTC and wake-up circuitry). There are three means to exit Sleep Mode and re-start the system:

- Some resets (external reset pin, low-voltage, power-up, JTAG debug command)

- RTC alarm

- Input from wake-up unit

# 3.12 Voltage supplies

The STR91xFA requires two separate operating voltage supplies. The CPU and memories operate from a 1.65V to 2.0V on the VDD pins, and the I/O ring operates at 2.7V to 3.6V on the VDDQ pins.

In Standby mode, both VDD and VDDQ must be shut down. Otherwise the specified maximum power consumption for Standby mode (I<sub>RTC\_STBY</sub>) and I<sub>SRAM\_STBY</sub>) may be exceeded. Leakage may occur if only one of the voltage supplies is off.

#### 3.12.1 Independent A/D converter supply and reference voltage

The ADC unit on 128-pin and 144-ball packages has an isolated analog voltage supply input at pin AVDD to accept a very clean voltage source, independent of the digital voltage supplies. Additionally, an isolated analog supply ground connection is provided on pin AVSS only on 128-pin and 144-ball packages for further ADC supply isolation. On 80-pin packages, the analog voltage supply is shared with the ADC reference voltage pin (as described next), and the analog ground is shared with the digital ground at a single point in the STR91xFA device on pin AVSS VSSQ.

A separate external analog reference voltage input for the ADC unit is available on 128-pin and 144-ball packages at the AVREF pin for better accuracy on low voltage inputs. For 80-pin packages, the ADC reference voltage is tied internally to the ADC unit supply voltage at pin AVREF\_AVDD, meaning the ADC reference voltage is fixed to the ADC unit supply voltage.

See *Table 11: Operating conditions*, for restrictions to the relative voltage levels of VDDQ, AVDD, AVREF, and AVREF\_AVDD.

24/108 DocID13495 Rev 7

STR91xFAxxx Functional overview

#### 3.12.2 Battery supply

An optional stand-by voltage from a battery or other source may be connected to pin VBATT to retain the contents of SRAM in the event of a loss of the main digital supplies ( $V_{DD}$  and  $V_{DDQ}$ ). The SRAM will automatically switch its supply from the internal  $V_{DD}$  source to the VBATT pin when the voltage of  $V_{DD}$  drops below the LVD threshold. In order to use the battery supply, the LVD must be enabled.

The VBATT pin also supplies power to the RTC unit, allowing the RTC to function even when the main digital supplies ( $V_{DD}$  and  $V_{DDQ}$ ) are switched off. By configuring the RTC register, it is possible to select whether or not to power from VBATT only the RTC unit, or power the RTC unit and the SRAM when the STR91xFA device is powered off.

# 3.13 System supervisor

The STR91xFA monitors several system and environmental inputs and will generate a global reset, a system reset, or an interrupt based on the nature of the input and configurable settings. A global reset clears all functions on the STR91xFA, a system reset will clear all but the Clock Control Unit (CCU) settings and the system status register. At any time, firmware may reset individual on-chip peripherals. System supervisor inputs include:

- GR: CPU voltage supply (V<sub>DD</sub>) drop out or brown out

- GR: I/O voltage supply (V<sub>DDO</sub>) drop out or brown out

- GR: Power-Up condition

- SR: Watchdog timer timeout

- SR: External reset pin (RESET\_INn)

- SR: JTAG debug reset command

Note: GR: means the input causes Global Reset, SR: means the input causes System Reset

The CPU may read a status register after a reset event to determine if the reset was caused by a watchdog timer timeout or a voltage supply drop out. This status register is cleared only by a power up reset.

#### 3.13.1 Supply voltage brownout

Each operating voltage source ( $V_{DD}$  and  $V_{DDQ}$ ) is monitored separately by the Low Voltage Detect (LVD) circuitry. The LVD will generate an early warning interrupt to the CPU when voltage sags on either  $V_{DD}$  or  $V_{DDQ}$  voltage inputs. This is an advantage for battery powered applications because the system can perform an orderly shutdown before the batteries become too weak. The voltage trip point to cause a brown out interrupt is typically 0.25V above the LVD dropout thresholds that cause a reset.

CPU firmware may prevent all brown-out interrupts by writing to interrupt mask registers at run-time.

Functional overview STR91xFAxxx

#### 3.18.1 Packet buffer interface (PBI)

The PBI manages a set of buffers inside the 2 Kbyte Packet Buffer, both for transmission and reception. The PBI will choose the proper buffer according to requests coming from the USB Serial Interface Engine (SIE) and locate it in the Packet SRAM according to addresses pointed by endpoint registers. The PBI will also auto-increment the address after each exchanged byte until the end of packet, keeping track of the number of exchanged bytes and preventing buffer overrun. Special support is provided by the PBI for isochronous and bulk transfers, implementing double-buffer usage which ensures there is always an available buffer for a USB packet while the CPU uses a different buffer.

#### 3.18.2 DMA

A programmable DMA channel may be assigned by CPU firmware to service the USB interface for fast and direct transfers between the USB bus and SRAM with little CPU involvement. This DMA channel includes the following features:

- Direct USB Packet Buffer SRAM to system SRAM transfers of receive packets, by descriptor chain for bulk or isochronous endpoints.

- Direct system SRAM to USB Packet Buffer SRAM transfers of transmit packets, by descriptor chain for bulk or isochronous endpoints.

- Linked-list descriptor chain support for multiple USB packets

#### 3.18.3 Suspend mode

CPU firmware may place the USB interface in a low-power suspend mode when required, and the USB interface will automatically wake up asynchronously upon detecting activity on the USB pins.

#### 3.19 CAN 2.0B interface

The STR91xFA provides a CAN interface complying with CAN protocol version 2.0 parts A and B. An external CAN transceiver device connected to pins CAN\_RX and CAN\_TX is required for connection to the physical CAN bus.

The CAN interface manages up to 32 Message Objects and Identifier Masks using a Message SRAM and a Message Handler. The Message Handler takes care of low-level CAN bus activity such as acceptance filtering, transfer of messages between the CAN bus and the Message SRAM, handling of transmission requests, and interrupt generation. The CPU has access to the Message SRAM via the Message Handler using a set of 38 control registers.

The follow features are supported by the CAN interface:

- Bit rates up to 1 Mbps

- Disable Automatic Retransmission mode for Time Triggered CAN applications

- 32 Message Objects

- Each Message Object has its own Identifier Mask

- Programmable FIFO mode

- Programmable loopback mode for self-test operation

The CAN interface is not supported by DMA.

STR91xFAxxx Functional overview

#### 3.20 UART interfaces with DMA

The STR91xFA supports three independent UART serial interfaces, designated UART0, UART1, and UART2. Each interface is very similar to the industry-standard 16C550 UART device. All three UART channels support IrDA encoding/decoding, requiring only an external LED transceiver to pins UARTx\_RX and UARTx\_Tx for communication. One UART channel (UART0) supports full modem control signals.

UART interfaces include the following features:

- Maximum baud rate of 1.5 Mbps

- Separate FIFOs for transmit and receive, each 16 deep, each FIFO can be disabled by firmware if desired

- Programmable FIFO trigger levels between 1/8 and 7/8

- Programmable baud rate generator based on CCU master clock, or CCU master clock divided by two

- Programmable serial data lengths of 5, 6, 7, or 8 bits with start bit and 1 or 2 stop bits

- Programmable selection of even, odd, or no-parity bit generation and detection

- False start-bit detection

- Line break generation and detection

- Support of IrDA SIR ENDEC functions for data rates of up to 115.2K bps

- IrDA bit duration selection of 3/16 or low-power (1.14 to 2.23 μsec)

- Channel UART0 supports modem control functions CTS, DCD, DSR, RTS, DTR, and RI

For your reference, only two standard 16550 UART features are not supported, 1.5 stop bits and independent receive clock.

#### 3.20.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service channels UART0 and UART1 for fast and direct transfers between the UART bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that UART FIFOs are enabled.

# 3.21 I<sup>2</sup>C interfaces

The STR91xFA supports two independent I2C serial interfaces, designated I2C0, and I2C1. Each interface allows direct connection to an I2C bus as either a bus master or bus slave device (firmware configurable). I2C is a two-wire communication channel, having a bi-directional data signal and a single-directional clock signal based on open-drain line drivers, requiring external pull-up resistors.

Byte-wide data is transferred between a Master device and a Slave device on two wires. More than one bus Master is allowed, but only one Master may control the bus at any given time. Data is not lost when another Master requests the use of a busy bus because I2C supports collision detection and arbitration. More than one Slave device may be present on the bus, each having a unique address. The bus Master initiates all data movement and generates the clock that permits the transfer. Once a transfer is initiated by the Master, any device that is addressed is considered a Slave. Automatic clock synchronization allows I2C devices with different bit rates to communicate on the same physical bus.

# 5 Pin description

Figure 7. STR91xFAM 80-pin package pinout

NU (Not Used) on STR910FAM devices. Pin 59 is not connected, pin 60 must be pulled up by a 1.5Kohm resistor to VDDQ.

<sup>2.</sup> No USBCLK function on STR910FAM devices.

Pin description STR91xFAxxx

Figure 8. STR91xFAW 128-pin package pinout

- NU (Not Used) on STR910FAW devices. Pin 95 is not connected, pin 96 must be pulled up by a 1.5Kohm resistor to VDDQ.

- 2. No USBCLK function on STR910FAW devices.

- 3. No PHYCLK function on STR910FAW devices.

# 5.1 LFBGA144 ball connections

• In *Table* 7 balls labelled NC are no connect balls. These NC balls are reserved for future devices and should NOT be connected to ground or any other signal. There are total of 9 NC (no connection) balls.

- Balls H1 and G4 are assigned as EMI bus write signals (EMI\_BWR\_WRLn and EMI\_WRHn). These two balls can also be configured by the user as EMI low or high byte select signals (EMI\_LBn and EMI\_UBn).

- The PLLGND (B8) and PLLVDDQ (C9) balls can be connected to VSSQ and VDDQ.

Table 7. STR91x LFBGA144 ball connections

|    | Α              | В       | С                    | D                    | E             | F    | G                             | Н                     | J           | K                          | L                   | М            |

|----|----------------|---------|----------------------|----------------------|---------------|------|-------------------------------|-----------------------|-------------|----------------------------|---------------------|--------------|

| 1  | P4.2           | P7.2    | NC                   | P7.0                 | VDDQ          | P7.3 | P7.4                          | EMI_WRHn<br>(EMI_UBn) | VDDQ        | PHYCLK_P5.2 <sup>(1)</sup> | P8.0                | P2.2         |

| 2  | AVREF          | P4.1    | P4.0                 | P7.1                 | P2.0          | NC   | P6.2                          | P5.3                  | P8.2        | P8.3                       | VSSQ                | P8.6         |

| 3  | AVDD           | P4.3    | AVSS                 | NC                   | P2.1          | VSS  | P6.3                          | P8.1                  | P6.1        | P2.3                       | P8.4                | VBATT        |

| 4  | P4.6           | P4.5    | P4.4                 | VSSQ                 | P5.0          | VDD  | EMI_BWR_<br>WRLn<br>(EMI_LBn) | P6.0                  | P8.5        | VSSQ                       | P2.4                | X2_<br>RTC   |

| 5  | P7.7           | VDDQ    | VSSQ                 | P4.7                 | P7.5          | NC   | VSSQ                          | VSS                   | P2.5        | P8.7                       | VDDQ                | X1_<br>RTC   |

| 6  | JTMS           | JTDO    | JTDI                 | P1.7                 | P7.6          | P5.1 | P2.6                          | P9.4                  | P9.3        | P9.2                       | VDD                 | P9.0         |

| 7  | P1.5           | P1.4    | NC                   | VDD                  | VSS           | P1.6 | P6.5                          | VDDQ                  | VSSQ        | P3.0                       | USBCLK<br>_P2.7 (2) | P9.1         |

| 8  | VSSQ           | PLLVSSQ | P1.3                 | JRSTn                | JTCK          | VSSQ | P6.4                          | EMI_BAAn              | P3.3        | EMI_<br>WAITn              | P9.5                | EMI_<br>BCLK |

| 9  | RESET_<br>OUTn | P1.2    | PLLVDDQ              | VDDQ                 | P6.6          | VDDQ | NC                            | P5.6                  | EMI_<br>RDn | P9.7                       | P3.4                | P9.6         |

| 10 | X1_CPU         | P1.0    | P1.1                 | USBDN <sup>(3)</sup> | TAMPER_<br>IN | NC   | VSS                           | P0.4                  | EMI_<br>ALE | P0.1                       | P3.5                | P3.1         |

| 11 | X2_CPU         | JRTCK   | USBDP <sup>(2)</sup> | MII_<br>MDIO (3)     | P0.6          | P0.5 | VDD                           | P5.5                  | P0.2        | P3.7                       | P0.0                | P3.2         |

| 12 | EMI_<br>WEn    | P0.7    | RESET_<br>INn        | P6.7                 | NC            | NC   | P5.7                          | P0.3                  | P5.4        | VDDQ                       | VSSQ                | P3.6         |

<sup>1.</sup> No PHYCLK function on STR910FAW devices.

<sup>2.</sup> No USBCLK function on STR910FAW devices.

<sup>3.</sup> NU (Not Used) on STR910FAW devices. D10 is not connected, C11 must be pulled up by a 1.5 kOhm resistor to VDDQ.

Table 8. Device pin description (continued)

| F      | Package Alternate functions |          | functions       |             |                            |                                   |                                 |                        |                                |                               |

|--------|-----------------------------|----------|-----------------|-------------|----------------------------|-----------------------------------|---------------------------------|------------------------|--------------------------------|-------------------------------|

| LQFP80 | LQFP128                     | LFBGA144 | Pin<br>name     | Signal type | Default pin function       | Default<br>input<br>function      | Alternate input 1               | Alternate output 1     | Alternate<br>output 2          | Alternate output 3            |

| 12     | 18                          | F6       | P5.1            | 1/0         | GPIO_5.1,<br>GP Input, HiZ | EXINT9,<br>External Intr          | UART0_RxD,<br>UART rcv data     | GPIO_5.1,<br>GP Output | CAN_TX,<br>CAN Tx data         | UART2_TX,<br>UART xmit data   |

| 17     | 25                          | K1       | PHYCLK<br>_P5.2 | I/O         | GPIO_5.2,<br>GP Input, HiZ | EXINT10,<br>External Intr         | UART2_RxD,<br>UART rcv data     | GPIO_5.2,<br>GP Output | MII_PHYCLK,<br>25Mhz to PHY    | TIM3_OCMP1,<br>Out comp/PWM   |

| 18     | 27                          | H2       | P5.3            | I/O         | GPIO_5.3,<br>GP Input, HiZ | EXINT11,<br>External Intr         | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_5.3,<br>GP Output | MII_TX_EN,<br>MAC xmit enbl    | TIM2_OCMP1,<br>Out comp/PWM   |

| 44     | 70                          | J12      | P5.4            | I/O         | GPIO_5.4,<br>GP Input, HiZ | EXINT12,<br>External Intr         | SSP0_SCLK,<br>SSP slv clk in    | GPIO_5.4,<br>GP Output | SSP0_SCLK,<br>SSP mstr clk out | EMI_CS0n,<br>EMI Chip Select  |

| 47     | 77                          | H11      | P5.5            | I/O         | GPIO_5.5,<br>GP Input, HiZ | EXINT13,<br>External Intr         | SSP0_MOSI,<br>SSP slv dat in    | GPIO_5.5,<br>GP Output | SSP0_MOSI,<br>SSP mstr dat out | EMI_CS1n,<br>EMI Chip Select  |

| 48     | 79                          | Н9       | P5.6            | I/O         | GPIO_5.6,<br>GP Input, HiZ | EXINT14,<br>External Intr         | SSP0_MISO,<br>SSP mstr dat in   | GPIO_5.6,<br>GP Output | SSP0_MISO,<br>SSP slv data out | EMI_CS2n,<br>EMI Chip Select  |

| 49     | 80                          | G12      | P5.7            | I/O         | GPIO_5.7,<br>GP Input, HiZ | EXINT15,<br>External Intr         | SSP0_NSS,<br>SSP slv select in  | GPIO_5.7,<br>GP Output | SSP0_NSS,<br>SSP mstr sel out  | EMI_CS3n,<br>EMI Chip Select  |

|        |                             |          |                 |             |                            | •                                 |                                 |                        |                                |                               |

| 19     | 29                          | H4       | P6.0            | I/O         | GPIO_6.0,<br>GP Input, HiZ | EXINT16,<br>External Intr         | TIM0_ICAP1,<br>Input Capture    | GPIO_6.0,<br>GP Output | TIM0_OCMP1,<br>Out comp/PWM    | MC_UH,<br>IMC phase U hi      |

| 20     | 31                          | J3       | P6.1            | I/O         | GPIO_6.1,<br>GP Input, HiZ | EXINT17,<br>External Intr         | TIM0_ICAP2,<br>Input Capture    | GPIO_6.1,<br>GP Output | TIM0_OCMP2,<br>Out comp        | MC_UL,<br>IMC phase U lo      |

| 13     | 19                          | G2       | P6.2            | I/O         | GPIO_6.2,<br>GP Input, HiZ | EXINT18,<br>External Intr         | TIM1_ICAP1,<br>Input Capture    | GPIO_6.2,<br>GP Output | TIM1_OCMP1,<br>Out comp/PWM    | MC_VH,<br>IMC phase V hi      |

| 14     | 20                          | G3       | P6.3            | I/O         | GPIO_6.3,<br>GP Input, HiZ | EXINT19,<br>External Intr         | TIM1_ICAP2,<br>Input Capture    | GPIO_6.3,<br>GP Output | TIM1_OCMP2,<br>Out comp        | MC_VL,<br>IMC phase V lo      |

| 52     | 83                          | G8       | P6.4            | I/O         | GPIO_6.4,<br>GP Input, HiZ | EXINT20,<br>External Intr         | TIM2_ICAP1,<br>Input Capture    | GPIO_6.4,<br>GP Output | TIM2_OCMP1,<br>Out comp/PWM    | MC_WH,<br>IMC phase W hi      |

| 53     | 84                          | G7       | P6.5            | I/O         | GPIO_6.5,<br>GP Input, HiZ | EXINT21,<br>External Intr         | TIM2_ICAP2,<br>Input Capture    | GPIO_6.5,<br>GP Output | TIM2_OCMP2,<br>Out comp        | MC_WL,<br>IMC phase W lo      |

| 57     | 92                          | E9       | P6.6            | I/O         | GPIO_6.6,<br>GP Input, HiZ | EXINT22_TRIG,<br>Ext Intr & Tach  | UART0_RxD,<br>UART rcv data     | GPIO_6.6,<br>GP Output | TIM3_OCMP1,<br>Out comp/PWM    | ETM_TRCLK,<br>ETM trace clock |

| 58     | 93                          | D12      | P6.7            | I/O         | GPIO_6.7,<br>GP Input, HiZ | EXINT23_STOP,<br>Ext Intr & Estop | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_6.7,<br>GP Output | TIM3_OCMP2,<br>Out comp        | UART0_TX,<br>UART xmit data   |

|        |                             |          |                 |             |                            |                                   |                                 |                        |                                |                               |

| -      | 5                           | D1       | P7.0            | I/O         | GPIO_7.0,<br>GP Input, HiZ | EXINT24,<br>External Intr         | TIM0_ICAP1,<br>Input Capture    | GPIO_7.0,<br>GP Output | 8b) EMI_A0,<br>16b) EMI_A16    | ETM_PCK0,<br>ETM Packet       |

| -      | 6                           | D2       | P7.1            | I/O         | GPIO_7.1,<br>GP Input, HiZ | EXINT25,<br>External Intr         | TIM0_ICAP2,<br>Input Capture    | GPIO_7.1,<br>GP Output | 8b) EMI_A1,<br>16b) EMI_A17    | ETM_PCK1,<br>ETM Packet       |

| -      | 7                           | B1       | P7.2            | I/O         | GPIO_7.2,<br>GP Input, HiZ | EXINT26,<br>External Intr         | TIM2_ICAP1,<br>Input Capture    | GPIO_7.2,<br>GP Output | 8b) EMI_A2,<br>16b) EMI_A18    | ETM_PCK2,<br>ETM Packet       |

| -      | 13                          | F1       | P7.3            | I/O         | GPIO_7.3,<br>GP Input, HiZ | EXINT27,<br>External Intr         | TIM2_ICAP2,<br>Input Capture    | GPIO_7.3,<br>GP Output | 8b) EMI_A3,<br>16b) EMI_A19    | ETM_PCK3,<br>ETM Packet       |

| -      | 14                          | G1       | P7.4            | I/O         | GPIO_7.4,<br>GP Input, HiZ | EXINT28,<br>External Intr         | UART0_RxD,<br>UART rcv data     | GPIO_7.4,<br>GP Output | 8b) EMI_A4,<br>16b) EMI_A20    | EMI_CS3n,<br>EMI Chip Select  |

| -      | 15                          | E5       | P7.5            | I/O         | GPIO_7.5,<br>GP Input, HiZ | EXINT29,<br>External Intr         | ETM_EXTRIG,<br>ETM ext. trigger | GPIO_7.5,<br>GP Output | 8b) EMI_A5,<br>16b) EMI_A21    | EMI_CS2n,<br>EMI Chip Select  |

Table 8. Device pin description (continued)

| F      | Pack    | age      |             | a           | Table 0.                            | Alternate functions          |                      |                    |                       |                    |

|--------|---------|----------|-------------|-------------|-------------------------------------|------------------------------|----------------------|--------------------|-----------------------|--------------------|

| LQFP80 | LQFP128 | LFBGA144 | Pin<br>name | Signal type | Default pin function                | Default<br>input<br>function | Alternate<br>input 1 | Alternate output 1 | Alternate<br>output 2 | Alternate output 3 |

| -      | 8       | L2       | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| 16     | 24      | K4       | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| 35     | 56      | C5       | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| -      | -       | D4       | VSSQ        | G           | Digital Ground                      |                              |                      |                    |                       |                    |

| 45     | 72      | G5       | VSSQ        | G           | for<br>!/O and USB                  |                              |                      | N/A                |                       |                    |

| 55     | 87      | J7       | VSSQ        | G           | !/O and USB                         |                              |                      |                    |                       |                    |

| 25     | 40      | A8       | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| 66     | 105     | F8       | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| 75     | 121     | L12      | VSSQ        | G           |                                     |                              |                      |                    |                       |                    |

| 11     | 17      | F4       | VDD         | ٧           |                                     |                              |                      |                    |                       |                    |

| 31     | 49      | D7       | VDD         | ٧           | V Source for                        |                              |                      | NI/A               |                       |                    |

| 50     | 81      | L6       | VDD         | ٧           | CPU.<br>1.65 V - 2.0 V              |                              |                      | N/A                |                       |                    |

| 70     | 112     | G11      | VDD         | ٧           |                                     |                              |                      |                    |                       |                    |

| 10     | 16      | F3       | VSS         | G           |                                     |                              |                      |                    |                       |                    |

| 30     | 48      | H5       | VSS         | G           | Digital Ground                      |                              |                      |                    |                       |                    |

| 51     | 82      | G10      | VSS         | G           | for CPU                             |                              |                      | N/A                |                       |                    |

| 71     | 113     | E7       | VSS         | G           |                                     |                              |                      |                    |                       |                    |

| -      | -       | C9       | PLLV<br>DDQ | ٧           | V Source for<br>PLL<br>2.7 to 3.6 V |                              |                      | N/A                |                       |                    |

| -      | -       | В8       | PLLV<br>SSQ | G           | Digital Ground for PLL              |                              |                      |                    |                       |                    |

Figure 15. Sleep mode current vs temperature with LVD on

## 7.6.1 Typical power consumption for frequencies below 10 MHz

The following conditions apply to *Table 16*:

- Program is executed from Flash. The program consists of an infinite loop.

- A standard crystal source is used.

- The PLL is off.

- All clock dividers are with their default values.

**Typical current** Symbol **Parameter Test conditions** Unit on V<sub>DD</sub> (1.8 V)  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 1 \text{ MHz}$ 2.88  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 2 \text{ MHz}$ 5.8 ΑII  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 4 MHz$ 10.91 peripherals f<sub>MSTR</sub>=f<sub>OSC</sub>=f<sub>PCLK</sub>=f<sub>HCLK</sub>=6 MHz 15.97 ON f<sub>MSTR</sub>=f<sub>OSC</sub>=f<sub>PCLK</sub>=f<sub>HCLK</sub>=8 MHz 20.68 f<sub>MSTR</sub>=f<sub>OSC</sub>=f<sub>PCLK</sub>=f<sub>HCLK</sub>=10 MHz 25.13 Run mode **IDDRUN** mΑ current  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 1 MHz$ 1.8 f<sub>MSTR</sub>=f<sub>OSC</sub>=f<sub>PCLK</sub>=f<sub>HCLK</sub>=2 MHz 3.62 ΑII f<sub>MSTR</sub>=f<sub>OSC</sub>=f<sub>PCLK</sub>=f<sub>HCLK</sub>=4 MHz 6.71 peripherals  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 6 MHz$ 9.81 OFF 12.63  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 8 MHz$  $f_{MSTR} = f_{OSC} = f_{PCLK} = f_{HCLK} = 10 \text{ MHz}$ 15.47

Table 16. Typical current consumption at 25 °C

Electrical characteristics STR91xFAxxx

# 7.7 Clock and timing characteristics

Table 17. Internal clock frequencies

| 0                      |                                                      | O THE STATE OF THE |        | l lmit                       |                                 |      |

|------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------|---------------------------------|------|

| Symbol                 | Parameter                                            | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min    | Тур                          | Max                             | Unit |

| f <sub>MSTR</sub>      | CCU Master clock                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32.768 |                              | f <sub>CPUCLKmax</sub>          | kHz  |

|                        |                                                      | Flash size ≤512 KB<br>Executing from SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                              | 96                              | MHz  |

|                        |                                                      | Flash size ≤512 KB<br>Executing from Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                              | 96                              | MHz  |

| f <sub>CPUCLK</sub>    | CPU Core frequency                                   | Flash size = 1 MB / 2<br>MB, executing from<br>SRAM or Flash<br>V <sub>DD</sub> ≥1.77 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                              | 96                              | MHz  |

|                        |                                                      | Flash size = 1 MB / 2<br>MB, executing from<br>SRAM or Flash<br>$V_{DD} \ge 1.65 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                              | 85                              | MHz  |

| f <sub>PCLK</sub>      | Peripheral clock for APB                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                              | 48                              | MHz  |

| f <sub>HCLK</sub>      | Peripheral clock for AHB                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                              | f <sub>CPUCLKmax</sub>          | MHz  |

| f <sub>OSC</sub>       | Clock input                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4      |                              | 25                              | MHz  |

|                        |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                              | f <sub>CPUCLKmax</sub>          | MHz  |

| f <sub>FMICLK</sub>    | FMI Flash bus clock<br>(internal clock)              | Flash size = 1 MB / 2<br>MB, write operation to<br>Flash memory or Flash<br>registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                              | 48                              | MHz  |

| f <sub>BCLK</sub>      | External memory bus clock                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                              | f <sub>CPUCLKmax</sub>          | MHz  |

| f <sub>RTC</sub>       | RTC clock                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32.768 |                              | kHz                             |      |

| f <sub>EMAC</sub>      | EMAC PHY clock                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25     |                              | MHz                             |      |