# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM9®                                                                              |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 96MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                         |

| Number of I/O              | 80                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 96K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                         |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 128-LQFP                                                                           |

| Supplier Device Package    | -                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str911faw44x6t             |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 7.5         |         | ectrical characteristics                               | 60   |

|-------------|---------|--------------------------------------------------------|------|

| <i>1</i> .5 | 7.5.1   |                                                        |      |

| 7.0         |         | LVD delay timing                                       |      |

| 7.6         |         | current characteristics                                |      |

|             | 7.6.1   | Typical power consumption for frequencies below 10 MHz |      |

| 7.7         | Clock a | nd timing characteristics                              |      |

|             | 7.7.1   | Main oscillator electrical characteristics             |      |

|             | 7.7.2   | X1_CPU external clock source                           | . 67 |

|             | 7.7.3   | RTC clock generated from a crystal/ceramic resonator   | . 68 |

|             | 7.7.4   | PLL electrical characteristics                         | . 69 |

| 7.8         | Memory  | characteristics                                        | 70   |

|             | 7.8.1   | SRAM characteristics                                   | . 70 |

|             | 7.8.2   | Flash memory characteristics                           | . 70 |

| 7.9         | EMC ch  | naracteristics                                         | 72   |

|             | 7.9.1   | Functional EMS (electro magnetic susceptibility)       | . 72 |

|             | 7.9.2   | Electro magnetic interference (EMI)                    | . 73 |

|             | 7.9.3   | Absolute maximum ratings (electrical sensitivity)      | . 73 |

|             | 7.9.4   | Electro-static discharge (ESD)                         | . 73 |

|             | 7.9.5   | Static latch-up                                        | . 74 |

|             | 7.9.6   | Designing hardened software to avoid noise problems    | . 74 |

|             | 7.9.7   | Electrical sensitivity                                 | . 74 |

| 7.10        | I/O cha | racteristics                                           | . 75 |

| 7.11        | Externa | I memory bus timings                                   | . 76 |

|             | 7.11.1  | Asynchronous mode                                      |      |

|             | 7.11.2  | Synchronous mode                                       | . 81 |

| 7.12        | Commu   | nication interface electrical characteristics          |      |

|             | 7.12.1  | 10/100 Ethernet MAC electrical characteristics         |      |

|             | 7.12.2  | USB electrical interface characteristics               |      |

|             | 7.12.3  | CAN interface electrical characteristics               |      |

|             | 7.12.4  | I2C electrical characteristics                         |      |

|             | 7.12.5  | SPI electrical characteristics                         |      |

| 7.13        | ADC el  | ectrical characteristics                               |      |

| 7.10        |         |                                                        | 00   |

| Devic       | e mark  | ing                                                    | 93   |

| 8.1         | STR91   | <pre></pre>                                            | 93   |

| 8.2         | STR91   | <pre>kFAx46 / STR91xFAx47</pre>                        | . 94 |

|             |         |                                                        |      |

8

| Table 49. | ADC conversion time (silicon Rev H and higher)                          | 91 |

|-----------|-------------------------------------------------------------------------|----|

| Table 50. | LQFP80 12 x12 mm low-profile quad flat package                          |    |

|           | mechanical data                                                         | 96 |

| Table 51. | LQFP128 - 128-pin, 14 x 14 mm low-profile quad flat package             |    |

|           | mechanical data                                                         | 99 |

| Table 52. | LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm, |    |

|           | 0.8 mm pitch, package mechanical data 1                                 | 02 |

| Table 53. | Thermal characteristics                                                 | 04 |

| Table 54. | Ordering information scheme                                             | 05 |

| Table 55. | Document revision history 1                                             | 06 |

## 1 Description

STR91xFA is a series of ARM<sup>®</sup>-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

# 2 Device summary

| Table 2. Device summary |          |        |                                     |                           |  |  |

|-------------------------|----------|--------|-------------------------------------|---------------------------|--|--|

| Part number             | Flash KB | RAM KB | Major peripherals                   | Package                   |  |  |

| STR910FAM32             | 256+32   | 64     | CAN, 40 I/Os                        | LQFP80,<br>12x12 mm       |  |  |

| STR910FAW32             | 256+32   | 64     | CAN, EMI, 80 I/Os                   | LQFP128,<br>14x14 mm      |  |  |

| STR910FAZ32             | 256+32   | 64     | CAN, EMI, 80 I/Os                   | LFBGA144<br>10 x 10 x 1.7 |  |  |

| STR911FAM42             | 256+32   | 96     | USB, CAN, 40 I/Os                   | LQFP80,                   |  |  |

| STR911FAM44             | 512+32   | 96     | 03B, CAN, 40 1/05                   | 12x12mm                   |  |  |

| STR911FAM46             | 1024+128 | 96     | USB, CAN, 40 I/Os                   | LQFP80,                   |  |  |

| STR911FAM47             | 2048+128 | 96     | 000, 000, 40 /03                    | 12x12mm                   |  |  |

| STR911FAW42             | 256+32   | 96     | USB, CAN, EMI, 80 I/Os              | LQFP128,                  |  |  |

| STR911FAW44             | 512+32   | 96     | 00 <b>0</b> , 04N, 2MI, 00 703      | 14x14mm                   |  |  |

| STR911FAW46             | 1024+128 | 96     | USB, CAN, EMI, 80 I/Os              | LQFP128,                  |  |  |

| STR911FAW47             | 2048+128 | 96     | 00B, CAN, EMI, 00 703               | 14x14mm                   |  |  |

| STR912FAW32             | 256+32   | 64     | Ethernet, USB, CAN, EMI,<br>80 I/Os | LQFP128                   |  |  |

| STR912FAW42             | 256+32   | 96     | Ethernet, USB, CAN, EMI,            | LQFP128                   |  |  |

| STR912FAW44             | 512+32   | 96     | 80 I/Os                             |                           |  |  |

| STR912FAW46             | 1024+128 | 96     | Ethernet, USB, CAN, EMI,            | LQFP128                   |  |  |

| STR912FAW47             | 2048+128 | 96     | 80 I/Os                             |                           |  |  |

| STR912FAZ42             | 256+32   | 96     | Ethernet, USB, CAN, EMI,            | LFBGA144                  |  |  |

| STR912FAZ44             | 512+32   | 96     | 80 I/Os                             | 10 x 10 x 1.7             |  |  |

| STR912FAZ46             | 1024+128 | 96     | Ethernet, USB, CAN, EMI,            | LFBGA144                  |  |  |

| STR912FAZ47             | 2048+128 | 96     | 80 I/Os                             | 10 x 10 x 1.7             |  |  |

Table 2. Device summary

#### 3.5 SRAM (64 Kbytes or 96 Kbytes)

A 32-bit wide SRAM resides on the CPU's Data TCM (D-TCM) interface, providing singlecycle data accesses. As shown in *Figure 1*, the D-TCM shares SRAM access with the Advanced High-performance Bus (AHB). Sharing is controlled by simple arbitration logic to allow the DMA unit on the AHB to also access the SRAM.

#### 3.5.1 Arbitration

Zero-wait state access occurs for either the D-TCM or the AHB when only one of the two is requesting SRAM. When both request SRAM simultaneously, access is granted on an interleaved basis so neither requestor is starved, granting one 32-bit word transfer to each requestor before relinquishing SRAM to the other. When neither the D-TCM or the AHB are requesting SRAM, the arbiter leaves access granted to the most recent user (if D-TCM was last to use SRAM then the D-TCM will not have to arbitrate to get access next time).

The CPU may execute code from SRAM through the AHB. There are no wait states as long as the D-TCM is not contending for SRAM access and the AHB is not sharing bandwidth with peripheral traffic. The ARM966E-S CPU core has a small pre-fetch queue built into this instruction path through the AHB to look ahead and fetch instructions during idle bus cycles.

#### 3.5.2 Battery backup

When a battery is connected to the designated battery backup pin (VBATT), SRAM contents are automatically preserved when the operating voltage on the main digital supplies (VDD and VDDQ are lost or sag below the LVD threshold. Automatic switchover to SRAM can be disabled by firmware if it is desired that the battery will power only the RTC and not the SRAM during standby.

#### 3.6 DMA data movement

DMA channels on the Advanced High-performance Bus (AHB) take full advantage of the separate data path provided by the Harvard architecture, moving data rapidly and largely independent of the instruction path. There are two DMA units, one is dedicated to move data between the Ethernet interface and SRAM, the other DMA unit has eight programmable channels with 14 request signals to service other peripherals and interfaces (USB, SSP, ADC, UART, Timers, EMI, and external request pins). Both single word and burst DMA transfers are supported. Memory-to-memory transfers are supported in addition to memory-peripheral transfers. DMA access to SRAM is shared with D-TCM accesses, and arbitration is described in *Section 3.5.1*. Efficient DMA transfers are managed by firmware using linked list descriptor tables. Of the 16 DMA request signals, two are assigned to external inputs. The DMA unit can move data between external devices and resources inside the STR91xFA through the EMI bus.

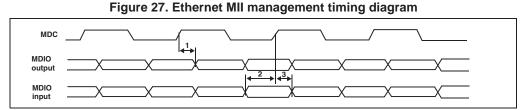

#### Ethernet MII management timings

Table 42. Ethernet MII management timing table

| Symbol | Parameter                              | Symbol                 | Va    | Unit |      |

|--------|----------------------------------------|------------------------|-------|------|------|

| Symbol |                                        |                        | Min   | Мах  | Onit |

| 1      | MDIO delay from rising edge of MDC     | t <sub>c</sub> (MDIO)  |       | 2.83 | ns   |

| 2      | MDIO setup time to rising edge of MDC  | T <sub>su</sub> (MDIO) | 2.70  |      | ns   |

| 3      | MDIO hold time from rising edge of MDC | T <sub>h</sub> (MDIO)  | -2.03 |      | ns   |

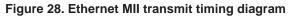

#### Ethernet MII transmit timings

### 7.13 ADC electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6 V,  $V_{DD}$  = 1.65 - 2 V,  $T_A$  = -40 / 85 °C unless otherwise specified.

| Symbol                   | Parameter <sup>(1)</sup>                 | Test<br>conditions | Value |     |                   | L Incit            |

|--------------------------|------------------------------------------|--------------------|-------|-----|-------------------|--------------------|

| Symbol                   | Farameter                                |                    | Min   | Тур | Max               | - Unit             |

| V <sub>AIN</sub>         | Input voltage range                      |                    | 0     |     | AV <sub>REF</sub> | V                  |

| RES                      | Resolution                               |                    |       |     | 10                | Bits               |

| N <sub>CH</sub>          | Number of input channels                 |                    |       |     | 8                 | N                  |

| f <sub>ADC</sub>         | ADC clock frequency                      |                    |       |     | 25                | MHz                |

| t <sub>POR(ADC)</sub>    | POR bit set to Standby mode              |                    |       |     | 500               | ms                 |

| t <sub>ck_off(ADC)</sub> | ADC clock disabled before conversion (2) |                    |       |     | 1                 | ms                 |

| t <sub>STAB</sub>        | Stabilization time                       |                    |       |     | 15                | s                  |

| C <sub>IN</sub>          | Input capacitance                        |                    |       | 5   |                   | pF                 |

| ED                       | Differential non-linearity               | (3) (4)            |       | 1   | 3                 | LSB <sup>(5)</sup> |

| EL                       | Integral non-linearity                   | (3)                |       | 3   | 6                 | LSB <sup>(5)</sup> |

| E <sub>O</sub>           | Offset error                             | (3)                |       | 3   | 6                 | LSB <sup>(5)</sup> |

| E <sub>G</sub>           | Gain error                               | (3)                |       | 0.5 | 2                 | LSB <sup>(5)</sup> |

| ET                       | Total unadjusted error                   | (3)                |       | 4   | 6                 | LSB <sup>(5)</sup> |

| I <sub>ADC</sub>         | Power consumption                        |                    |       | 4.6 |                   | mA                 |

| I <sub>VREF</sub>        | Current on VREF input pin                | (6) (7)            |       |     | 920               | A                  |

#### Table 47. General ADC electrical characteristics

1. Guaranteed by design, not tested in production.

2. The ADC clock can be disabled by setting the ADC bit in the SCU\_PCGR1 register or by setting the ACG bit in the SCU\_GPIOANA register (for Rev H and higher)

3. Conditions:  $\mathrm{AV}_{\mathrm{SS}}$  = 0 V,  $\mathrm{AV}_{\mathrm{DD}}$  = 3.3 V f\_{\mathrm{ADC}} = 25 MHz.

4. The A/D is monotonic, there are no missing codes.

5. 1 LSB =  $(AV_{DD} - AV_{SS})/1024$

6. Data based on characterization, not tested in production.

7. Conditions:  $V_{DD}$ =1.8 V,  $f_{CPU}$ =96 MHz ,  $f_{ADC}$ =24 MHz

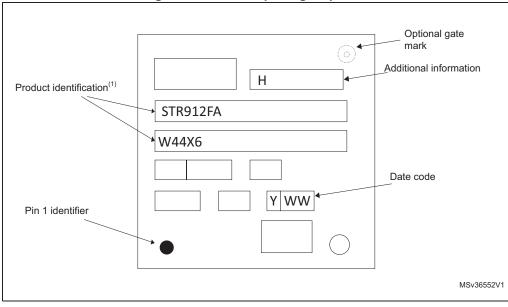

#### Marking of engineering samples for LQFP128

The following figure shows the engineering sample marking for the LQFP128 package. Only the information field containing the engineering sample marking is shown.

Figure 44. LQFP128 package top view

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID13495 Rev 7