# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                     |

| Core Processor             | ARM9®                                                                                        |

| Core Size                  | 16/32-Bit                                                                                    |

| Speed                      | 96MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                                |

| Number of I/O              | 80                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                 |

| Program Memory Type        | FLASH                                                                                        |

| EEPROM Size                | -                                                                                            |

| RAM Size                   | 96K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 2V                                                                                   |

| Data Converters            | A/D 8x10b                                                                                    |

| Oscillator Type            | Internal                                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                            |

| Mounting Type              | Surface Mount                                                                                |

| Package / Case             | 128-LQFP                                                                                     |

| Supplier Device Package    | -                                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str912faw46x6t                       |

|                            |                                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Description

STR91xFA is a series of ARM<sup>®</sup>-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

# 3 Functional overview

# 3.1 System-in-a-package (SiP)

The STR91xFA is a SiP device, comprised of two stacked die. One die is the ARM966E-S CPU with peripheral interfaces and analog functions, and the other die is the burst Flash. The two die are connected to each other by a custom high-speed 32-bit burst memory interface and a serial JTAG test/programming interface.

# 3.2 Package choice

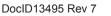

STR91xFA devices are available in 128-pin (14 x 14 mm) and 80-pin (12 x 12 mm) LQFP and LFBGA144 (10 x 10 mm) packages. Refer to *Table 2: Device summary on page 11* for a list of available peripherals for each of the package choices.

# 3.3 ARM966E-S CPU core

The ARM966E-S core inherently has separate instruction and data memory interfaces (Harvard architecture), allowing the CPU to simultaneously fetch an instruction, and read or write a data item through two Tightly-Coupled Memory (TCM) interfaces as shown in *Figure 1*. The result is streamlined CPU Load and Store operations and a significant reduction in cycle count per instruction. In addition to this, a 5-stage pipeline is used to increase the amount of operational parallelism, giving the most performance out of each clock cycle.

Ten DSP-enhanced instruction extensions are supported by this core, including single-cycle execution of 32x16 Multiply-Accumulate, saturating addition/subtraction, and count leading-zeros.

The ARM966E-S core is binary compatible with 32-bit ARM7 code and 16-bit Thumb<sup>®</sup> code.

## 3.4 Burst Flash memory interface

A burst Flash memory interface (*Figure 1*) has been integrated into the Instruction TCM (I-TCM) path of the ARM966E-S core. Also in this path is an 8-instruction Pre-Fetch Queue (PFQ) and a 15-entry Branch Cache (BC), enabling the ARM966E-S core to perform up to 96 MIPS while executing code directly from Flash memory. This architecture provides high performance levels without a costly instruction SRAM, instruction cache, or external SDRAM. Eliminating the instruction cache also means interrupt latency is reduced and code execution becomes more deterministic.

#### 3.4.1 Pre-fetch queue (PFQ)

As the CPU core accesses sequential instructions through the I-TCM, the PFQ always looks ahead and will pre-fetch instructions, taking advantage any idle bus cycles due to variable length instructions. The PFQ will fetch 32-bits at a time from the burst Flash memory at a rate of up to 96 MHz.

# **3.9** Vectored interrupt controller (VIC)

Interrupt management in the STR91xFA is implemented from daisy-chaining two standard ARM VIC units. This combined VIC has 32 prioritized interrupt request channels and generates two interrupt output signals to the CPU. The output signals are FIQ and IRQ, with FIQ having higher priority.

#### 3.9.1 FIQ handling

FIQ (Fast Interrupt reQuest) is the only non-vectored interrupt and the CPU can execute an Interrupt Service Routine (ISR) directly without having to determine/prioritize the interrupt source, minimizing ISR latency. Typically only one interrupt source is assigned to FIQ. An FIQ interrupt has its own set of banked registers to minimize the time to make a context switch. Any of the 32 interrupt request input signals coming into the VIC can be assigned to FIQ.

#### 3.9.2 IRQ handling

IRQ is a vectored interrupt and is the logical OR of all 32 interrupt request signals coming into the 32 IRQ channels. Priority of individual vectored interrupt requests is determined by hardware (IRQ channel Intr 0 is highest priority, IRQ channel Intr 31 is lowest).

However, inside the same VIC (primary or secondary VIC), CPU firmware may re-assign individual interrupt sources to individual hardware IRQ channels, meaning that firmware can effectively change interrupt priority levels as needed within the same VIC (from priority 0 to priority 16).

# Note: VIC0 (primary VIC) interrupts always have higher priority than VIC1 (secondary VIC) interrupts

When the IRQ signal is activated by an interrupt request, VIC hardware will resolve the IRQ interrupt priority, then the ISR reads the VIC to determine both the interrupt source and the vector address to jump to the service code.

The STR91xFA has a feature to reduce ISR response time for IRQ interrupts. Typically, it requires two memory accesses to read the interrupt vector address from the VIC, but the STR91xFA reduces this to a single access by adding a 16th entry in the instruction branch cache, dedicated for interrupts. This 16th cache entry always holds the instruction that reads the interrupt vector address from the VIC, eliminating one of the memory accesses typically required in traditional ARM implementations.

#### 3.9.3 Interrupt sources

The 32 interrupt request signals coming into the VIC on 32 IRQ channels are from various sources; 5 from a wake-up unit and the remaining 27 come from internal sources on the STR91xFA such as on-chip peripherals, see *Table 6*. Optionally, firmware may force an interrupt on any IRQ channel.

One of the 5 interrupt requests generated by the wake-up unit (IRQ25 in *Table 6*) is derived from the logical OR of all 32 inputs to the wake-up unit. Any of these 32 inputs may be used to wake up the CPU and cause an interrupt. These 32 inputs consist of 30 external interrupts on selected and enabled GPIO pins, plus the RTC interrupt, and the USB Resume interrupt.

| IRQ channel<br>hardware<br>priority | VIC input<br>channel | Logic block     | Interrupt source                                                         |

|-------------------------------------|----------------------|-----------------|--------------------------------------------------------------------------|

| 25                                  | VIC1.9               | Wake-Up (all)   | Logic OR of all 32 inputs of Wake-Up unit (30 pins, RTC, and USB Resume) |

| 26                                  | VIC1.10              | Wake-up Group 0 | Logic OR of 8 interrupt sources: RTC, USB Resume, pins P3.2 to P3.7      |

| 27                                  | VIC1.11              | Wake-up Group 1 | Logic OR of 8 interrupts from pins P5.0 to P5.7                          |

| 28                                  | VIC1.12              | Wake-up Group 2 | Logic OR of 8 interrupts from pins P6.0 to P6.7                          |

| 29                                  | VIC1.13              | Wake-up Group 3 | Logic OR of 8 interrupts from pins P7.0 to P7.7                          |

| 30                                  | VIC1.14              | USB             | USB Bus Resume Wake-up (also input to wake-up unit)                      |

| 31 (low priority)                   | VIC1.15              | PFQ-BC          | Special use of interrupts from Prefetch Queue and Branch Cache           |

Table 6. VIC IRQ channels (continued)

# 3.10 Clock control unit (CCU)

The CCU generates a master clock of frequency  $f_{MSTR}$ . From this master clock the CCU also generates individually scaled and gated clock sources to each of the following functional blocks within the STR91xFA.

- CPU, f<sub>CPUCLK</sub>

- Advanced High-performance Bus (AHB), f<sub>HCLK</sub>

- Advanced Peripheral Bus (APB), f<sub>PCLK</sub>

- Flash Memory Interface (FMI), f<sub>FMICLK</sub>

- External Memory Interface (EMI), f<sub>BCLK</sub>

- UART Baud Rate Generators, f<sub>BAUD</sub>

- USB, f<sub>USB</sub>

#### 3.10.1 Master clock sources

The master clock in the CCU ( $f_{MSTR}$ ) is derived from one of three clock input sources. Under firmware control, the CPU can switch between the three CCU inputs without introducing any glitches on the master clock output. Inputs to the CCU are:

- Main Oscillator (f<sub>OSC</sub>). The source for the main oscillator input is a 4 to 25 MHz external crystal connected to STR91xFA pins X1\_CPU and X2\_CPU, or an external oscillator device connected to pin X1\_CPU.

- PLL (f<sub>PLL</sub>). The PLL takes the 4 to 25 MHz oscillator clock as input and generates a

master clock output up to 96 MHz (programmable). By default, at power-up the master

clock is sourced from the main oscillator until the PLL is ready (locked) and then the

CPU may switch to the PLL source under firmware control. The CPU can switch back

to the main oscillator source at any time and turn off the PLL for low-power operation.

The PLL is always turned off in Sleep mode.

- RTC (f<sub>RTC</sub>). A 32.768 kHz external crystal can be connected to pins X1\_RTC and X2\_RTC, or an external oscillator connected to pin X1\_RTC to constantly run the real-time clock unit. This 32.768 kHz clock source can also be used as an input to the CCU to run the CPU in slow clock mode for reduced power.

The STR91xFA MAC includes the following features:

- Supports 10 and 100 Mbps rates

- Tagged MAC frame support (VLAN support)

- Half duplex (CSMA/CD) and full duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. Transmit FIFO depth is 4 words (32 bits each), and the receive FIFO is 16 words deep.

A 32-bit burst DMA channel residing on the AHB is dedicated to the Ethernet MAC for highspeed data transfers, side-stepping the CPU for minimal CPU impact during transfers. This DMA channel includes the following features:

- Direct SRAM to MAC transfers of transmit frames with the related status, by descriptor chain

- Direct MAC to SRAM transfers of receive frames with the related status, by descriptor chain

- Open and Closed descriptor chain management

# 3.18 USB 2.0 slave device interface with DMA

The STR91xFA provides a USB slave controller that implements both the OSI Physical and Data Link layers for direct bus connection by an external USB host on pins USBDP and USBPN. The USB interface detects token packets, handles data transmission and reception, and processes handshake packets as required by the USB 2.0 standard.

The USB slave interface includes the following features:

- Supports USB low and full-speed transfers (12 Mbps), certified to comply with the USB 2.0 specification

- Supports isochronous, bulk, control, and interrupt endpoints

- Configurable number of endpoints allowing a mixture of up to 20 single-buffered monodirectional endpoints or up to 10 double-buffered bidirectional endpoints

- Dedicated, dual-port 2 Kbyte USB Packet Buffer SRAM. One port of the SRAM is connected by a Packet Buffer Interface (PBI) on the USB side, and the CPU connects to the other SRAM port.

- CRC generation and checking

- NRZI encoding-decoding and bit stuffing

- USB suspend resume operations

#### 3.18.1 Packet buffer interface (PBI)

The PBI manages a set of buffers inside the 2 Kbyte Packet Buffer, both for transmission and reception. The PBI will choose the proper buffer according to requests coming from the USB Serial Interface Engine (SIE) and locate it in the Packet SRAM according to addresses pointed by endpoint registers. The PBI will also auto-increment the address after each exchanged byte until the end of packet, keeping track of the number of exchanged bytes and preventing buffer overrun. Special support is provided by the PBI for isochronous and bulk transfers, implementing double-buffer usage which ensures there is always an available buffer for a USB packet while the CPU uses a different buffer.

#### 3.18.2 DMA

A programmable DMA channel may be assigned by CPU firmware to service the USB interface for fast and direct transfers between the USB bus and SRAM with little CPU involvement. This DMA channel includes the following features:

- Direct USB Packet Buffer SRAM to system SRAM transfers of receive packets, by descriptor chain for bulk or isochronous endpoints.

- Direct system SRAM to USB Packet Buffer SRAM transfers of transmit packets, by descriptor chain for bulk or isochronous endpoints.

- Linked-list descriptor chain support for multiple USB packets

#### 3.18.3 Suspend mode

CPU firmware may place the USB interface in a low-power suspend mode when required, and the USB interface will automatically wake up asynchronously upon detecting activity on the USB pins.

## 3.19 CAN 2.0B interface

The STR91xFA provides a CAN interface complying with CAN protocol version 2.0 parts A and B. An external CAN transceiver device connected to pins CAN\_RX and CAN\_TX is required for connection to the physical CAN bus.

The CAN interface manages up to 32 Message Objects and Identifier Masks using a Message SRAM and a Message Handler. The Message Handler takes care of low-level CAN bus activity such as acceptance filtering, transfer of messages between the CAN bus and the Message SRAM, handling of transmission requests, and interrupt generation. The CPU has access to the Message SRAM via the Message Handler using a set of 38 control registers.

The follow features are supported by the CAN interface:

- Bit rates up to 1 Mbps

- Disable Automatic Retransmission mode for Time Triggered CAN applications

- 32 Message Objects

- Each Message Object has its own Identifier Mask

- Programmable FIFO mode

- Programmable loopback mode for self-test operation

The CAN interface is not supported by DMA.

# 3.26 Three-phase induction motor controller (IMC)

The STR91xFA provides an integrated controller for variable speed motor control applications.

Six PWM outputs are generated on high current drive pins P6.0 to P6.5 for controlling a three-phase AC induction motor drive circuit assembly. Rotor speed feedback is provided by capturing a tachometer input signal on pin P6.6, and an asynchronous hardware emergency stop input is available on pin P6.7 to stop the motor immediately if needed, independently of firmware.

The IMC unit has the following features:

- Three PWM outputs generated using a 10 or 16-bit PWM counter, one for each phase U, V, W. Complimentary PWM outputs are also generated for each phase.

- Choice of classic or zero-centered PWM generation modes

- 10 or 16-bit PWM counter clock is supplied through a programmable 8-bit prescaler of the APB clock.

- Programmable 6 or 10-bit dead-time generator to add delay to each of the three complimentary PWM outputs

- 8-bit repetition counter

- Automatic rotor speed measurement with 16-bit resolution. Schmitt trigger tachometer input with programmable edge detection

- Hardware asynchronous emergency stop input

- A dedicated interrupt to CPU with eight flags

- Enhanced Motor stop output polarity configuration

- Double update option when PWM counter reaches the max and min values in Zerocentered mode

- Locking feature to prevent some control register bits from being advertently modified

- Trigger output to start an ADC conversion

| STR91xx EMI_CS3n | ►    |             | 8-BIT<br>DEVICE |

|------------------|------|-------------|-----------------|

| EMI_CS2n         |      |             | DEVICE          |

| EMI_CS1n         | •    |             |                 |

| EMI_CS0n         |      |             | CHIP_SELECT     |

|                  |      |             |                 |

| EMI BWR WRLn     |      | -           |                 |

| EMI_BUXC_VICEN   |      |             | READ            |

| EMI_REM          |      | -           | READ            |

|                  |      |             |                 |

| EMI_A15          | P9.7 |             | A15             |

| EMI A14          | P9.6 |             | A14             |

| EMI_A13          | P9.5 | •           | A13             |

| EMI_A12          | P9.4 |             | A12             |

| EMI A11          | P9.3 |             | - A11           |

| EMI_A10          | P9.2 |             | A10             |

| EMI_A9           | P9.1 |             | - A9            |

| EMI_A8           | P9.0 |             | A8              |

|                  | P7.7 |             |                 |

| EMI_A7           | P7.6 |             | A7              |

| EMI_A6           | P7.5 | -           | A6              |

| EMI_A5           | D7 4 | <b>&gt;</b> | A5              |

| EMI_A4           | P7 3 |             | - A4            |

| EMI_A3           | P7.2 |             | - A3            |

| EMI_A2           | P7.1 |             | - A2            |

| EMI_A1           | P7.0 |             | - A1            |

| EMI_A0           |      |             | - A0            |

| <b>E 1 1 2</b>   | P8.7 | -           |                 |

| EMI_D7           | P8.6 |             | - D7<br>- D6    |

| EMI_D6           | P8.5 |             | D5              |

| EMI_D5<br>EMI_D4 | P8.4 |             | D5<br>D4        |

| EMI_D4<br>EMI_D3 | P8.3 | -           | D4<br>D3        |

| EMI_D3<br>EMI_D2 | P8.2 |             | D3<br>D2        |

| EMI_D2<br>EMI_D1 | P8.1 |             | D1              |

| EMI_DI<br>EMI DO | P8.0 |             |                 |

| Ettil_B0         |      |             | 20              |

Figure 6. EMI 8-bit non-multiplexed connection example

Figure 8. STR91xFAW 128-pin package pinout

1. NU (Not Used) on STR910FAW devices. Pin 95 is not connected, pin 96 must be pulled up by a 1.5Kohm resistor to VDDQ.

2. No USBCLK function on STR910FAW devices.

3. No PHYCLK function on STR910FAW devices.

# 5.2 Default pin functions

During and just after reset, all pins on ports 0-9 default to high-impedance input mode until CPU firmware assigns other functions to the pins. This initial input mode routes all pins on ports 0-9 to be read as GPIO inputs as shown in the "Default Pin Function" column of *Table 8*. Simultaneously, certain port pin signals are also routed to other functional inputs as shown in the "Default Input Function" column of *Table 8*, and these pin input functions will remain until CPU firmware makes other assignments. At any time, even after the CPU assigns pins to alternate functions, the CPU may always read the state of any pin on ports 0-9 as a GPIO input. CPU firmware may assign alternate functions to port pins as shown in columns "Alternate Input 1" or "Alternate Output 1, 2, 3" of *Table 8* by writing to control registers at run-time.

#### 5.2.1 General notes on pin usage

- Since there are no internal or programmable pull-up resistors on ports 0-9, it is advised to pull down to ground, or pull up to VDDQ (using max. 47 KΩ resistors), all unused pins on port 0-9. Another solution is to use the GPIO control registers to configure the unused pins on ports 0-9 as output low level. The purpose of this is to reduce noise susceptibility, noise generation, and minimize power consumption

- 2 All pins on ports 0 9 are 5V tolerant

- *3* Pins on ports 0,1,2,4,5,7,8,9 have 4 mA drive and 4mA sink. Ports 3 and 6 have 8 mA drive and 8 mA sink.

- 4 For 8-bit non-muxed EMI operation: Port 8 is eight bits of data, ports 7 and 9 are 16 bits of address.

- 5 For 16-bit muxed EMI operation: Ports 8 and 9 are 16 bits of muxed address and data bits, port 7 is up to eight additional bits of high-order address

- 6 Signal polarity is programmable for interrupt request inputs, EMI\_ALE, timer input capture inputs and output compare/PWM outputs, motor control tach and emergency stop inputs, and motor control phase outputs.

- 7 HiZ = High Impedance, V = Voltage Source, G = Ground, I/O = Input/Output

- 8 STR910FA devices do not support USB. On these devices USBDP and USBDN signals are "Not Used" (USBDN is not connected, USBDP must be pulled up by a 1.5K ohm resistor to VDDQ), and all functions named "USB" are not available.

- 9 STR910FA 128-pin and 144-ball devices do not support Ethernet. On these devices PHYCLK and all functions named "MII\*" are not available.

If the main Flash contents are incorrect, the CPU, while executing code from the secondary Flash, can download new data from any STR91xFA communication channel and program into primary Flash memory. Application code then starts after the new contents of primary Flash are verified.

# 6.5 STR91xFA memory map

The memory map is shown in Figure 9: STR91xFA memory map on page 57:

- Either of the two Flash memories may be placed at CPU boot address 0x0000.0000. By default, the primary Flash memory is in boot position starting at CPU address 0x0000.0000 and the secondary Flash memory may be placed at a higher address following the end of the primary Flash memory. This default option may be changed using the STR91xx device configuration software, placing the secondary Flash memory at CPU boot location 0x0000.0000, and then the primary Flash memory may be placed at a higher address.

- The local SRAM (64KB or 96KB) is aliased in three address windows. A) At 0x0400.0000 the SRAM is accessible through the CPU's D-TCM, at 0x4000.0000 the SRAM is accessible through the CPU's AHB in buffered accesses, and at 0x5000.0000 the SRAM is accessible through the CPU's AHB in non-buffered accesses. An AHB bus master other than the CPU can access SRAM in all three aliased windows, but these accesses are always non-buffered. The CPU is the only AHB master that can performed buffered writes.

- APB peripherals reside in two AHB-to-APB peripheral bridge address windows, APB0 and APB1. These peripherals are accessible with buffered AHB access if the CPU addresses them in the address range of 0x4800.0000 to 0x4FFF.FFFF, and nonbuffered access in the address range of 0x5800.0000 to 0x5FFF.FFFF.

- Individual peripherals on the APB are accessed at the listed address offset plus the base address of the appropriate AHB-to-APB bridge.

# 7.4 **RESET\_INn and power-on-reset characteristics**

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_{A}$  = -40 / 85 °C unless otherwise specified.

| Symbol              | Devementer                             | Test conditions                                                                            | Value              |     |     | Unit |

|---------------------|----------------------------------------|--------------------------------------------------------------------------------------------|--------------------|-----|-----|------|

| Symbol              | Parameter                              | Test conditions                                                                            | Min <sup>(1)</sup> | Тур | Max | Onit |

| t <sub>RINMIN</sub> | RESET_INn Valid Active Low             |                                                                                            | 100                |     |     | ns   |

| t <sub>POR</sub>    | Power-On-Reset Condition duration      | V <sub>DDQ</sub> ,V <sub>DD</sub> ramp<br>time is less than<br>10ms: 0V to V <sub>DD</sub> | 10                 |     |     | ms   |

| t <sub>RSO</sub>    | RESET_OUT Duration<br>(Watchdog reset) |                                                                                            | one PCLK           |     |     | ns   |

| Table 13. RESET | _INn and power-on-reset | characteristics |

|-----------------|-------------------------|-----------------|

|-----------------|-------------------------|-----------------|

1. Data based on bench measurements, not tested in production.

# 7.5 LVD electrical characteristics

$V_{DDQ}$  = 2.7 - 3.6V,  $V_{DD}$  = 1.65 - 2V,  $T_{A}$  = -40 / 85 °C unless otherwise specified.

| Symbol                       | Deremeter                                    | Test       |      | Unit |      |      |

|------------------------------|----------------------------------------------|------------|------|------|------|------|

| Symbol                       | Parameter                                    | conditions | Min  | Тур  | Max  | Unit |

| V <sub>DD_LVD+</sub> (1.8V)  | LVD threshold during V <sub>DD</sub> rise    |            | 1.43 | 1.50 | 1.58 | V    |

| V <sub>DD_LVD-</sub> (1.8V)  | LVD threshold during V <sub>DD</sub> fall    |            | 1.33 | 1.40 | 1.47 | V    |

| V <sub>DD_BRN</sub> (1.8V)   | V <sub>DD</sub> brown out warning threshold  |            |      | 1.65 |      | V    |

| V <sub>DDQ_LVD+</sub> (3.0V) | LVD threshold during V <sub>DDQ</sub> rise   | (1)(2)     | 2.32 | 2.45 | 2.57 | V    |

| V <sub>DDQ_LVD-</sub> (3.0V) | LVD threshold during V <sub>DDQ</sub> fall   | (1)(2)     | 2.23 | 2.35 | 2.46 | v    |

| V <sub>DDQ_BRN</sub> (3.0V)  | V <sub>DDQ</sub> brown out warning threshold | (1)(2)     |      | 2.65 |      | V    |

| V <sub>DDQ_LVD+</sub> (3.3V) | LVD threshold during V <sub>DDQ</sub> rise   | (2)(3)     | 2.61 | 2.75 | 2.89 | V    |

| V <sub>DDQ_LVD-</sub> (3.3V) | LVD threshold during V <sub>DDQ</sub> fall   | (2)(3)     | 2.52 | 2.65 | 2.78 |      |

| V <sub>DDQ_BRN</sub> (3.3V)  | V <sub>DDQ</sub> brown out warning threshold | (2)(3)     |      | 2.95 |      | V    |

Table 14. LVD electrical characteristics

1. For  $V_{DDQ}$  I/O voltage operating at 2.7 - 3.3V.

Selection of V<sub>DDQ</sub> operation range is made using configuration software from ST, or IDE from 3rd parties. The default condition is V<sub>DDQ</sub>=2.7V - 3.3V.

3. For  $V_{\text{DDQ}}$  I/O voltage operating at 3.0 - 3.6V.

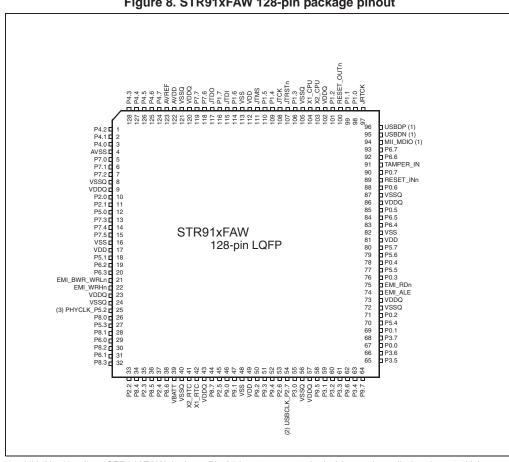

#### Non-mux read

Figure 19. Non-mux bus read timings

| Table | 34. | EMI | read | operation |

|-------|-----|-----|------|-----------|

| Symbol           | Parameter               | Va                                                 | lue                                    |

|------------------|-------------------------|----------------------------------------------------|----------------------------------------|

| Symbol Farameter |                         | Min                                                | Max                                    |

| t <sub>RCR</sub> | Read to CSn<br>inactive | 0                                                  | 1.5 ns                                 |

| t <sub>RAS</sub> | Read address setup time | ((WSTOEN) x t <sub>BCLK</sub> )- 1.5 ns            | (WSTOEN) x t <sub>BCLK</sub>           |

| t <sub>RDS</sub> | Read data setup<br>time | 12.5                                               | -                                      |

| t <sub>RDH</sub> | Read data hold<br>time  | 0                                                  | -                                      |

| t <sub>RP</sub>  | Read pulse width        | ((WSTRD-WSTOEN+1) x t <sub>BCLK</sub> )-<br>0.5 ns | ((WSTRD-WSTOEN+1) x $t_{BCLK}$ )+ 2 ns |

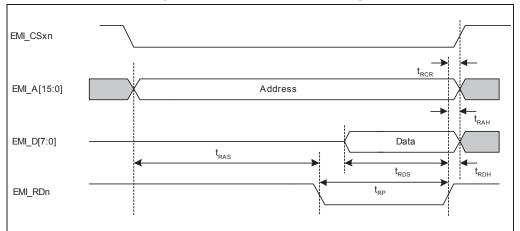

#### Sync burst read

Figure 24. Sync burst read diagram

| Table 39. Sync burst read tim |

|-------------------------------|

|-------------------------------|

| Querra had         | Demonster               | Val                           | lue                         |

|--------------------|-------------------------|-------------------------------|-----------------------------|

| Symbol             | Parameter               | Min                           | Мах                         |

| t <sub>D1BAA</sub> | BAA t <sub>D1</sub>     | 0 ns                          | 2 ns                        |

| t <sub>D2BAA</sub> | BAA t <sub>D2</sub>     | 0.5ns                         | 2.5 ns                      |

| t <sub>D1ALE</sub> | ALE t <sub>D1</sub>     | 1 ns                          | 3.5 ns                      |

| t <sub>D2ALE</sub> | ALE t <sub>D2</sub>     | (t <sub>BCLK</sub> /2)+0.5 ns | (t <sub>BCLK</sub> /2)+3 ns |

| t <sub>D1RD</sub>  | RD t <sub>D1</sub>      | 0                             | 2 ns                        |

| t <sub>D2RD</sub>  | RD t <sub>D2</sub>      | 0.5 ns                        | 2.5 ns                      |

| t <sub>D1A</sub>   | Address t <sub>D1</sub> | 2 ns                          | 4 ns                        |

| t <sub>D2A</sub>   | Address t <sub>D2</sub> | 2.5 ns                        | 3.5 ns                      |

| t <sub>D1CS</sub>  | CS t <sub>D1</sub>      | 0.5 ns                        | 3 ns                        |

| t <sub>D2CS</sub>  | CS t <sub>D2</sub>      | 1 ns                          | 3.5 ns                      |

| t <sub>WS</sub>    | WAIT set up time        | 1 ns                          | 4 ns                        |

| t <sub>DS</sub>    | Data setup time         | 4.5 ns                        | -                           |

| t <sub>DH</sub>    | Data hold time          | 0                             | -                           |

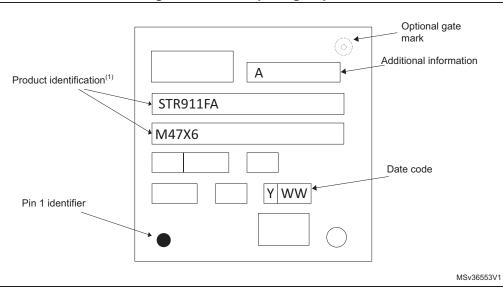

#### Marking of engineering samples for LQFP80

The following figure shows the engineering sample marking for the LQFP80 package. Only the information field containing the engineering sample marking is shown

Figure 42. LQFP80 package top view

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

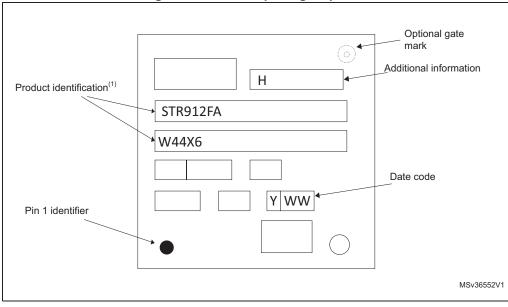

#### Marking of engineering samples for LQFP128

The following figure shows the engineering sample marking for the LQFP128 package. Only the information field containing the engineering sample marking is shown.

Figure 44. LQFP128 package top view

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol           | millimeters inches <sup>(1)</sup> |        |        |        |        |        |

|------------------|-----------------------------------|--------|--------|--------|--------|--------|

| Symbol           | Min                               | Тур    | Max    | Тур    | Min    | Max    |

| A <sup>(2)</sup> | -                                 | -      | 1.700  |        |        | 0.0669 |

| A1               | 0.210                             | -      | -      | 0.0083 |        |        |

| A2               | -                                 | 1.060  | -      |        | 0.0417 |        |

| A3               |                                   | 0.026  |        |        | 0.0010 |        |

| A4               | -                                 | 0.800  | -      | -      | 0.0315 | -      |

| b                | 0.350                             | 0.400  | 0.450  | 0.0138 | 0.0157 | 0.0177 |

| D                | 9.850                             | 10.000 | 10.150 | 0.3878 | 0.3937 | 0.3996 |

| D1               | -                                 | 8.800  | -      | -      | 0.3465 | -      |

| E                | 9.850                             | 10.000 | 10.150 | 0.3878 | 0.3937 | 0.3996 |

| E1               | -                                 | 8.800  | -      | -      | 0.3465 | -      |

| е                | -                                 | 0.800  | -      | -      | 0.0315 | -      |

| F                | -                                 | 0.600  | -      | -      | 0.0236 | -      |

| ddd              | 0.100                             |        |        |        | 0.0039 |        |

| eee              | 0.150                             |        |        |        | 0.0059 |        |

| fff              |                                   | 0.080  |        |        | 0.0031 |        |

# Table 52.LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,0.8 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. STATSChipPAC package dimensions.

# 9.1 ECOPACK

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions, and product status are available at <u>www.st.com</u>.

# 9.2 Thermal characteristics

The average chip-junction temperature, T<sub>J</sub> must never exceed 125 °C.

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using the following equation:

$$T_{J} = T_{A} + (P_{D} \times \Theta_{JA})$$

(1)

Where:

- T<sub>A</sub> is the ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ ,

- P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the Chip Internal Power.

P<sub>I/O</sub> represents the power dissipation on input and output pins;

Most of the time for the applications  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant if the device is configured to drive continuously external modules and/or memories. The worst case  $P_{INT}$  of the STR91xFA is 500 mW ( $I_{DD} \times V_{DD}$ , or 250 mA x 2.0 V).

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$= K / (T_J + 273 °C)$$

(2)

Therefore (solving equations 1 and 2):

$P_D$

$$K = P_{D} x (T_{A} + 273 °C) + \Theta_{JA} x P_{D}^{2}$$

(3)

Where:

K is a constant for the particular part, which may be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> may be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>.

| Symbol        | Parameter                                                                         | Value | Unit |

|---------------|-----------------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LQFP 80 - 12 x 12 mm / 0.5 mm pitch | 41.5  | °C/W |

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LQFP128 - 14 x 14 mm / 0.4 mm pitch | 38    | °C/W |

| $\Theta_{JA}$ | <i>Thermal resistance junction-ambient</i><br>LFBGA 144 - 10 x 10 x 1.7 mm        | 36.5  | °C/W |

| Table 53. | Thermal | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 02-Jul-2009 | 6        | Section 3.13.7: Tamper detection: Removed information about<br>"Normally Closed/Tamper Open mode".<br>Table 31: I/O characteristics: Updated V <sub>HYS</sub> row.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 3-Mar-2015  | 7        | Updated Figure 40: LQFP80 12 x 12 mm 80 pin low-profile quad<br>flat package outline on page 95, Figure 43: LQFP128 14 x 14 mm<br>128 pin low-profile quad flat package outline on page 98 and<br>Figure 45: LFBGA144 – 144-ball low profile fine pitch ball grid<br>array, 10 x 10 mm, 0.8 mm pitch, package outline on page 101<br>Updated Table 50: LQFP80 12 x12 mm low-profile quad flat<br>package mechanical data on page 96, Table 51: LQFP128 - 128-<br>pin, 14 x 14 mm low-profile quad flat package mechanical data on<br>page 99, and Table 52: LFBGA144 – 144-ball low profile fine pitch<br>ball grid array, 10 x 10 mm, 0.8 mm pitch, package mechanical<br>data on page 102<br>Added Figure 42: LQFP80 package top view on page 97,<br>Figure 43: LQFP128 14 x 14 mm 128 pin low-profile quad flat<br>package outline on page 98, Figure 44: LQFP128 package top<br>view on page 100 and Figure 45: LFBGA144 – 144-ball low profile<br>fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package<br>outline on page 101 |  |

Table 55. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID13495 Rev 7